## Genesys Logic, Inc.

# **GL880**

# PCI / CardBus 2-Port USB 2.0 Host Controller

Datasheet

Preliminary Revision 0.91

May. 29, 2003

## **Copyright:**

Copyright © 2003 Genesys Logic Incorporated. All rights reserved. No part of the materials may be reproduced in any form or by any means without prior written consent of Genesys Logic Inc.

#### **Disclaimer:**

ALL MATERIALS ARE PROVIDED "AS IS" WITHOUT EXPRESS OR IMPLIED WARRANTY OF ANY KIND. NO LICENSE OR RIGHT IS GRANTED UNDER ANY PATENT OR TRADEMARK OF GENESYS LOGIC INC.. GENESYS LOGIC HEREBY DISCLAIMS ALL WARRANTIES AND CONDITIONS IN REGARD TO MATERIALS, INCLUDING ALL WARRANTIES, IMPLIED OR EXPRESS, OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF INTELLECTUAL PROPERTY. IN NO EVENT SHALL GENESYS LOGIC BE LIABLE FOR ANY DAMAGES INCLUDING, WITHOUT LIMITATION, DAMAGES RESULTING FROM LOSS OF INFORMATION OR PROFITS. PLEASE BE ADVISED THAT THE MATERIALS MAY CONTAIN ERRORS OR OMMISIONS. GENESYS LOGIC MAY MAKE CHANGES TO THE MATERIALS OR TO THE PRODUCTS DESCRIBED THEREIN AT ANY TIME WITHOUT NOTICE.

#### **Trademarks:**

is a registrated trademark of Genesys Logic Inc.. All trademarks are the properties of their respective owners.

#### Office:

Genesys Logic, Inc.

12F, No. 205, Sec. 3, Beishin Rd., Shindian City,

Taipei, Taiwan

Tel: (886-2) 8913-1888 Fax: (886-2) 6629-6168

http://www.genesyslogic.com

## **Revision History**

| Revision | Date       | Description                                                                  |  |

|----------|------------|------------------------------------------------------------------------------|--|

| 0.90     | 09/19/2002 | First draft release                                                          |  |

| 0.91     | 05/29/2003 | Add pin diagram     Add EERPOM signals     Add pin number in pin description |  |

## **TABLE OF CONTENTS**

| CHAPTER 1 GENERAL DESCRIPTION                           | 7  |

|---------------------------------------------------------|----|

| CHAPTER 2 FEATURES                                      | 8  |

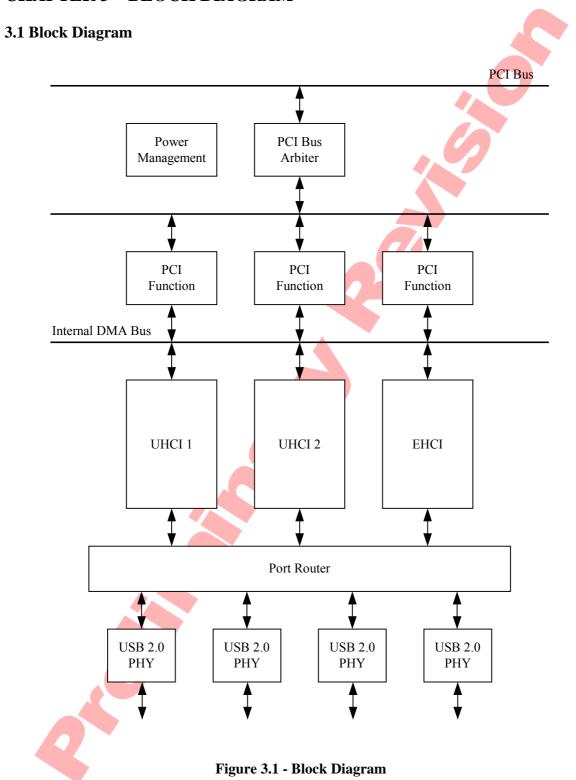

| CHAPTER 3 BLOCK DIAGRAM                                 |    |

| 3.1 BLOCK DIAGRAM                                       |    |

| 3.2 APPLICATION DIAGRAM                                 |    |

| CHAPTER 4 PIN ASSIGNMENT                                | 11 |

| 4.1 PINOUTS                                             |    |

| 4.2 PIN LIST                                            | 12 |

| 4.3 PIN DESCRIPTIONS                                    | 13 |

| CHAPTER 5 REGISTERS                                     | 16 |

| 5.1 PCI CONFIGURATION REGISTERS DESCRIPTIONS            | 16 |

| 5.1.1 Function 0/1 Universal Host Controller Interface  | 16 |

| 5.1.2 Funcion 3 Enhanced Host Controller Interface      | 21 |

| 5.2 UHCIO/UHCI1 OPERATIONAL REGISTERS DESCRIPTIONS      | 26 |

| 5.2.1 USBCMD - USB Command Registers                    |    |

| 5.2.2 USBSTS - USB Status Registers                     | 27 |

| 5.2.3 USBINTR - USB Interrupt Enable Registers          | 27 |

| 5.2.4 FRNUM - Frame Number Registers                    | 27 |

| 5.2.5 FLBASEADD - Frame List Base Address Registers     | 28 |

| 5.2.6 Start of Frame (SOF) Modify Registers             | 28 |

| 5.2.7 PORTSC - Port Status and Control Registers        | 28 |

| 5.3 EHCI OPERATIONAL REGISTERS DESCRIPTIONS             | 29 |

| 5.3.1 HCIVERSION / CAPLENGTH Registers                  | 29 |

| 5.3.2 HCSPARAMS Registers                               | 29 |

| 5.3.3 HCCPARAMS Capability Parameters Registers         | 30 |

| 5.3.4 HCSP - PORTROUTE Companion Port Route Registers . |    |

| 5.3.5 USBCMD - USB Command Registers                    |    |

| 5.3.6 USBSTS Registers                                  |    |

| 5.3.7 USBINTR - USB Interrupt Enable Registers          |    |

| 5.3.8 FRINDEX - Frame Index Registers                   |    |

|                                                         |    |

| 5.3.9 CTRLDSSEGMENT - Control Data Structure Segment Registers  | 34 |

|-----------------------------------------------------------------|----|

| 5.3.10 PERIODICLISTABASE Registers                              | 34 |

| 5.3.11 ASYNCLISTADDR Registers                                  | 35 |

| 5.3.12 CONFIGFLAG - Configure Flag Registers                    | 35 |

| 5.3.13 PORTSC1~4 - Port Status and Control Registers            | 35 |

| CHAPTER 6 FUNCTIONAL DESCRIPTION                                | 38 |

| 6.1 POWER MANAGEMENT                                            | 38 |

| 6.1.1 Power Management State and Power Management Event support | 38 |

| 6.1.2 PCI CLKRUNJ support                                       | 38 |

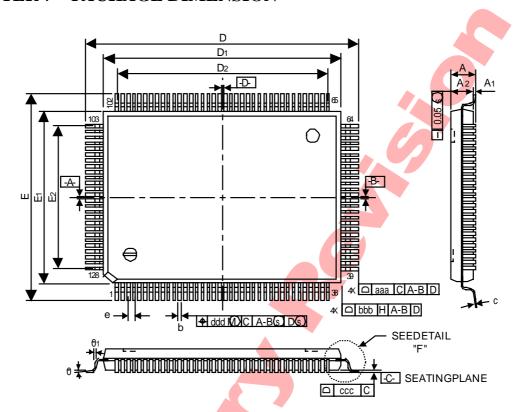

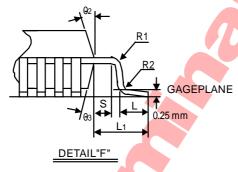

| CHAPTER 7 PACKAGE DIMENSION                                     | 39 |

#### LIST OF FIGURES

| Everypp 2.1 Dr. e. ev. Dr. en 114       |    |

|-----------------------------------------|----|

| FIGURE 3.1 - BLOCK DIAGRAM              |    |

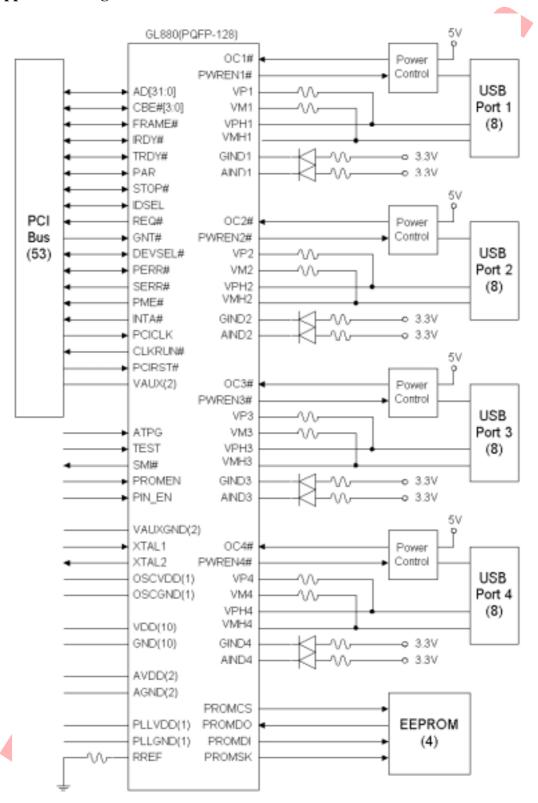

| FIGURE 3.2 - APPLICATION DIAGRAM        | 10 |

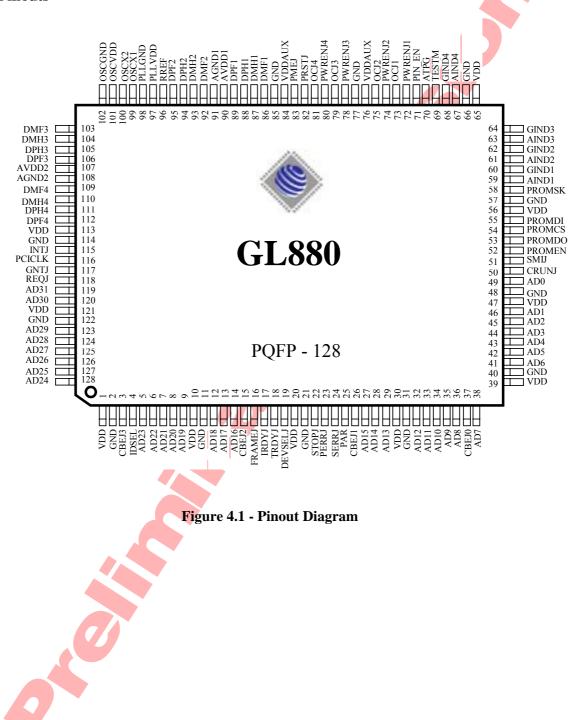

| FIGURE 4.1 - PINOUT DIAGRAM             | 11 |

| FIGURE 7.1 - GL880 128 PIN PQFP PACKAGE | 39 |

|                                         |    |

| LIST OF TABLES                          | 7  |

|                                         |    |

| TABLE 4.1 - PIN LIST                    |    |

| TABLE 4.2 DIN DESCRIPTIONS              | 13 |

#### **CHAPTER 1 GENERAL DESCRIPTION**

The GL880 is a PCI-based USB 2.0 Host Controller. It integrates 2 Universal Host Controller (for full-speed/low-speed transactions) and 1 Enhanced Host Controller (for high-speed transactions). It provides higher bandwidth (480 Mbps) and is backward compatible with USB 1.1. The GL880 supports 4 downstream facing ports with 1.5 (low-speed), 12 (full-speed) and 480 (high-speed) Mbps transaction capability. This chip also supports PCI Bus Power Management Interface Specification 1.1 and provides legacy support for all downstream facing ports. The GL880 is ready to provide a PCI 4-port USB2.0 peripheral-interface for every segments of desktop and mobile computers. Support for the GL880 is built into Microsoft Windows XP and Windows 2000.

#### **CHAPTER 2 FEATURES**

- Compliant with Universal Serial Bus Specification Revision 2.0

- Compliant with *Universal Host Controller Interface Design Guide Revision 1.1*

- Compliant with Enhanced Host Controller Interface Specification Revision 1.00

- 32-bit, 33 MHz PCI interface compliant with PCI Local Bus Specification Interface Revision 2.3

- Configurable number of downstream ports (2 to 4)

- All downstream ports integrate high-speed, full-speed, and low-speed transceivers

- Two color LED indicator for each USB port

- Power reduction mode compliant with PCI Power Management Interface Specification Reversion 1.1

- Legacy support for keyboard and mouse

- System clock @12 MHz Crystal.

- 3.3V power supply

- PCI pads with 3.3V-driving, 5V-tolerant

- 128-pin PQFP package

- 8 kV ESD protection

- 0.35 μm process, full-scan design

#### **CHAPTER 3 BLOCK DIAGRAM**

#### 3.2 Application Diagram

Figure 3.2 - Application Diagram

#### **CHAPTER 4 PIN ASSIGNMENT**

#### 4.1 Pinouts

#### 4.2 Pin List

Table 4.1 - Pin List

| Pin# | Pin Name | Type |

|------|----------|------|------|----------|------|------|----------|------|------|----------|------|

| 1    | VDD      | P    | 33   | AD11     | I/O  | 65   | VDD      | P    | 97   | PLLVDD   | P    |

| 2    | GND      | P    | 34   | AD10     | I/O  | 66   | GND      | P    | 98   | PLLGND   | P    |

| 3    | CBEJ3    | I/O  | 35   | AD9      | I/O  | 67   | AIND4    | O    | 99   | OSCX1    | I    |

| 4    | IDSEL    | I    | 36   | AD8      | I/O  | 68   | GIND4    | O    | 100  | OSCX2    | О    |

| 5    | AD23     | I/O  | 37   | CBEJ0    | I/O  | 69   | TESTM    | I    | 101  | OSCVDD   |      |

| 6    | AD22     | I/O  | 38   | AD7      | I/O  | 70   | ATPG     | I    | 102  | OSCGND   |      |

| 7    | AD21     | I/O  | 39   | VDD      | P    | 71   | PIN_EN   | I    | 103  | DMF3     | I/O  |

| 8    | AD20     | I/O  | 40   | GND      | P    | 72   | PWRENJ1  | О    | 104  | DMH3     | I/O  |

| 9    | AD19     | I/O  | 41   | AD6      | I/O  | 73   | OCJ1     | I    | 105  | DPH3     | I/O  |

| 10   | VDD      | P    | 42   | AD5      | I/O  | 74   | PWRENJ2  | О    | 106  | DPF3     | I/O  |

| 11   | GND      | P    | 43   | AD4      | I/O  | 75   | OCJ2     | Ι    | 107  | AVDD2    | P    |

| 12   | AD18     | I/O  | 44   | AD3      | I/O  | 76   | VDDAUX   | P    | 108  | AGND2    | P    |

| 13   | AD17     | I/O  | 45   | AD2      | I/O  | 77   | GND      | P    | 109  | DMF4     | I/O  |

| 14   | AD16     | I/O  | 46   | AD1      | I/O  | 78   | PWRENJ3  | О    | 110  | DMH4     | I/O  |

| 15   | CBEJ2    | I/O  | 47   | VDD      | P    | 79   | OCJ3     | I    | 111  | DPH4     | I/O  |

| 16   | FRAMEJ   | I/O  | 48   | GND      | P    | 80   | PWRENJ4  | О    | 112  | DPF4     | I/O  |

| 17   | IRDYJ    | I/O  | 49   | AD0      | I/O  | 81   | OCJ4     | I    | 113  | VDD      | P    |

| 18   | TRDYJ    | I/O  | 50   | CRUNJ    | I/O  | 82   | PRSTJ    | I    | 114  | GND      | P    |

| 19   | DEVSELJ  | I/O  | 51   | SMIJ     | О    | 83   | PMEJ     | О    | 115  | INTJ     | О    |

| 20   | VDD      | P    | 52   | PROMEN   | I    | 84   | VDDAUX   | P    | 116  | PCICLK   | I    |

| 21   | GND      | P    | 53   | PROMDO   |      | 85   | GND      | P    | 117  | GNTJ     | I    |

| 22   | STOPJ    | I/O  | 54   | PROMCS   |      | 86   | DMF1     | I/O  | 118  | REQJ     | О    |

| 23   | PERRJ    | I/O  | 55   | PROMDI   |      | 87   | DMH1     | I/O  | 119  | AD31     | I/O  |

| 24   | SERRJ    | 0    | 56   | VDD      | P    | 88   | DPH1     | I/O  | 120  | AD30     | I/O  |

| 25   | PAR      | I/O  | 57   | GND      | P    | 89   | DPF1     | I/O  | 121  | VDD      | P    |

| 26   | CBEJ1    | I/O  | 58   | PROMSK   |      | 90   | AVDD1    | P    | 122  | GND      | P    |

| 27   | AD15     | I/O  | 59   | AIND1    | О    | 91   | AGND1    | P    | 123  | AD29     | I/O  |

| 28   | AD14     | I/O  | 60   | GIND1    | О    | 92   | DMF2     | I/O  | 124  | AD28     | I/O  |

| 29   | AD13     | I/O  | 61   | AIND2    | О    | 93   | DMH2     | I/O  | 125  | AD27     | I/O  |

| 30   | VDD      | P    | 62   | GIND2    | О    | 94   | DPH2     | I/O  | 126  | AD26     | I/O  |

| 31   | GND      | P    | 63   | AIND3    | О    | 95   | DPF2     | I/O  | 127  | AD25     | I/O  |

| 32   | AD12     | I/O  | 64   | GIND3    | О    | 96   | RREF     | I/O  | 128  | AD24     | I/O  |

## **4.3 Pin Descriptions**

**Table 4.2 - Pin Descriptions**

|           | PCI Interface                                                         |      |                                                                         |  |  |  |  |

|-----------|-----------------------------------------------------------------------|------|-------------------------------------------------------------------------|--|--|--|--|

| Pin Name  | Pin#                                                                  | Type | Description                                                             |  |  |  |  |

| PRSTJ     | 82                                                                    | I    | PCI reset (active low)                                                  |  |  |  |  |

| PCICLK    | 116                                                                   | I    | PCI system clock (33 MHz)                                               |  |  |  |  |

| REQJ      | 118                                                                   | О    | PCI request (active low)                                                |  |  |  |  |

| GNTJ      | 117                                                                   | I    | PCI grant (active low, tri-state)                                       |  |  |  |  |

| AD[31:0]  | 119,120,<br>123~128,<br>5~9,12~14,<br>27~29,<br>32~36,38,<br>41~46,49 | I/O  | PCI address and data                                                    |  |  |  |  |

| PAR       | 25                                                                    | I/O  | PCI parity                                                              |  |  |  |  |

| CBEJ[3:0] | 3,15,26,<br>37                                                        | I/O  | PCI command and byte enables (active low)                               |  |  |  |  |

| FRAMEJ    | 16                                                                    | I/O  | PCI cycle frame (active low)                                            |  |  |  |  |

| IRDYJ     | 17                                                                    | I/O  | PCI initiator ready (active low)                                        |  |  |  |  |

| TRDYJ     | 18                                                                    | I/O  | PCI target ready (active low)                                           |  |  |  |  |

| STOPJ     | 22                                                                    | I/O  | PCI stop (active low)                                                   |  |  |  |  |

| IDSEL     | 4                                                                     | I    | PCI initialization device select                                        |  |  |  |  |

| DEVSELJ   | 19                                                                    | I/O  | PCI device select (active low)                                          |  |  |  |  |

| PERRJ     | 23                                                                    | I/O  | PCI parity error (active low)                                           |  |  |  |  |

| SERRJ     | 24                                                                    | 0    | PCI system error (active low, open drain)                               |  |  |  |  |

| INTJ      | 115                                                                   | 0    | PCI interrupt signal for UHCI host controller1 (active low, open drain) |  |  |  |  |

| РМЕЈ      | 83                                                                    | О    | PCI power management event (active low, open drain)                     |  |  |  |  |

| CRUNJ     | 50                                                                    | I/O  | PCI clock control (active low, open drain)                              |  |  |  |  |

| USB Interface |                   |      |                                        |  |  |  |  |

|---------------|-------------------|------|----------------------------------------|--|--|--|--|

| Pin Name      | Pin#              | Type | Description                            |  |  |  |  |

| OCJ[1:4]      | 73,75,79,<br>81   | I    | Over-current detect input (active low) |  |  |  |  |

| PWRENJ[1:4]   | 72,74,78,<br>80   | О    | Port power enable (active low)         |  |  |  |  |

| DPF[1:4]      | 89,95,106<br>,112 | I/O  | D+ for full/low speed operation        |  |  |  |  |

| DMF[1:4]      | 86,92,103<br>,109 | I/O  | D- for full/low speed operation        |  |  |  |  |

| DPH [1:4] | 88,94,105<br>,111 | I/O | D+ for high speed operation                      |

|-----------|-------------------|-----|--------------------------------------------------|

| DMH [1:4] | 87,93,104<br>,110 | I/O | D- for high speed operation                      |

| GIND[1:4] | 60,62,64,<br>68   | О   | Green LED output for port indicator (open drain) |

| AIND[1:4] | 59,61,63,<br>67   | О   | Amber LED output for port indicator (open drain) |

|          | System Interface |      |                                                                      |  |  |  |  |

|----------|------------------|------|----------------------------------------------------------------------|--|--|--|--|

| Pin Name | Pin#             | Type | Description                                                          |  |  |  |  |

| OSCX1    | 99               | I    | Crystal input (12 MHz)                                               |  |  |  |  |

| OSCX2    | 100              | О    | Crystal output (12 MHz)                                              |  |  |  |  |

| RREF     | 96               | I/O  | 510 Ohm reference resistor                                           |  |  |  |  |

| SMIJ     | 51               | О    | System management interrupt for legacy support                       |  |  |  |  |

| TESTM    | 69               | I    | Test mode (internal pull-up) 0: enter test mode; 1: normal operation |  |  |  |  |

| EEPROM Interface |      |      |                      |  |  |  |

|------------------|------|------|----------------------|--|--|--|

| Pin Name         | Pin# | Type | Description          |  |  |  |

| PROMEN           | 52   | О    | EEPROM Chip enable   |  |  |  |

| PROMDO           | 53   | I    | EEPROM Chip data in  |  |  |  |

| PROMCS           | 54   | О    | EEPROM Chip select   |  |  |  |

| PROMDI           | 55   | 0    | EEPROM Chip data out |  |  |  |

| PROMSK           | 58   | 0    | EEPROM Chip clock    |  |  |  |

| Other Interface |      |      |                        |  |  |  |

|-----------------|------|------|------------------------|--|--|--|

| Pin Name        | Pin# | Type | Description            |  |  |  |

| ATPG            | 70   | 1    | No connection          |  |  |  |

| PIN_EN          | 71   | =    | Pull up 10K Ω resistor |  |  |  |

|          | Power / Ground                                                                                  |      |                                              |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------|------|----------------------------------------------|--|--|--|--|

| Pin Name | Pin#                                                                                            | Type | Description                                  |  |  |  |  |

| VDD, GND | 1,10,20,<br>30,39,47,<br>56,65,113<br>,121/2,<br>11,21,31,<br>40,48,57,<br>66,77,85,<br>114,122 | P    | Power for digital logic part (8 VDD / 8 GND) |  |  |  |  |

| AVDD, AGND        | 90,107 /<br>91,108 | P | Power for USB transceiver part (2 AVDD / 2 AGND) |

|-------------------|--------------------|---|--------------------------------------------------|

| PLLVDD,<br>PLLGND | 97,98              | P | Power for internal PLL (1 PLLVDD / 1 PLLGND)     |

| VDDAUX            | 76,84              | P | 3.3V auxiliary power                             |

| OSCVDD            | 101                | P | Power for internal OSC VDD                       |

| OSCGND            | 102                | P | Power for internal OSC GND                       |

#### **Notation:**

odpu

| 10000 | •   |                                   |

|-------|-----|-----------------------------------|

| Type  | O   | Output                            |

|       | I   | Input                             |

|       | В   | Bi-directional                    |

|       | B/I | Bi-directional, default input     |

|       | B/O | Bi-directional, default output    |

|       | P   | Power / Ground                    |

|       | A   | Analog                            |

|       | SO  | Automatic output low when suspend |

|       | pu  | Internal pull up                  |

|       | pd  | Internal pull down                |

Open drain with internal pull up

#### **CHAPTER 5 REGISTERS**

This section lists the PCI configuration registers and operational registers for UHCI0/UHCI1/EHCI.

## **5.1 PCI Configuration Registers Descriptions**

#### 5.1.1 Function 0/1 Universal Host Controller Interface

| Register  | Address | Bit   | R/W/W1C | <b>Default Value</b> | Descriptions                                                                                                                                                                                                                                                                                                                           |

|-----------|---------|-------|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device ID | 0x02h   | 15:0  | RO      | 0x8083h              | Genesys Logic                                                                                                                                                                                                                                                                                                                          |

| T. 1 ID   | 0. 001  | 15.0  | D.O.    | 0. 17 4.01           | UHCI's device ID                                                                                                                                                                                                                                                                                                                       |

| Vendor ID | 0x00h   |       | RO      | 0x17A0h              | Genesys Logic's Vendor ID                                                                                                                                                                                                                                                                                                              |

| Command   | 0x04h   | 15:10 | RO      | 000000b              | Reserved                                                                                                                                                                                                                                                                                                                               |

|           |         | 9     | RO      | 0b                   | GL880 doesnot supprt Fast Back-to-Back cycle.                                                                                                                                                                                                                                                                                          |

|           |         | 8     | R/W     | 0b                   | SERRJ Enable: This bit is an enable bit for the SERRJ driver. 0: Disables the SERRJ driver 1: Enables the SERRJ driver                                                                                                                                                                                                                 |

|           |         | 7     | RO      | 0b                   | Reserved                                                                                                                                                                                                                                                                                                                               |

|           |         | 6     | R/W     | Ob                   | Parity Error Response: This bit controls the device's response to parity errors.  0: The device sets its Detected Parity Error status bit(bit15 in the Status register) when an error is detected, but does not assert PERRJ and continues normal operation  1: The device must take its normal action when a parity error is detected |

|           |         | 5     | RO      | 0b                   | GL880 doesnot support palette snoop cycles.                                                                                                                                                                                                                                                                                            |

|           |         | 4     | RO      | 0b                   | GL880 doesnot support Memory Write and Invalidate Command                                                                                                                                                                                                                                                                              |

|           |         | 3     | RO      | 0b                   | GL880 doesnot support Special Cycles.                                                                                                                                                                                                                                                                                                  |

|           |         | 2     | R/W     | 0ь                   | Bus Master: Controls a device's ability to act as a master on the PCI bus. 0: Disables the device from generating PCI accesses 1: Allows the device to behave as a bus master                                                                                                                                                          |

|           |         | 1     | RO      | 0b                   | UHCI0/UHCI1 doesnot support memory access.                                                                                                                                                                                                                                                                                             |

| 4         |         | 0     | R/W     | 0b                   | I/O Space Enable: Controls a device's response to I/O space accesses. 0: disables 1: enable                                                                                                                                                                                                                                            |

| Status      | 0x06h      | 15    | R/W1C  | 0b                         | Detected Parity Error:                                                                       |

|-------------|------------|-------|--------|----------------------------|----------------------------------------------------------------------------------------------|

| Status      | OXOON      | 13    | IC WIC |                            | This bit is set by GL880 whenever it detects a                                               |

|             |            |       |        |                            | parity error even if parity error handling is disabled.                                      |

|             |            | 14    | R/W1C  | 0b                         | Signaled System Error:                                                                       |

|             |            | 12    | D/W1C  | 01-                        | This bit is set whenever GL880 asserts SERRJ                                                 |

|             |            | 13    | R/W1C  | 0b                         | Received Master Abort:                                                                       |

|             |            |       |        |                            | This bit is set by GL880 whenever its transaction is terminated with Master-Abort.           |

|             |            | 12    | R/W1C  | 0b                         | Received Target Abort:                                                                       |

|             |            | 12    | K/WIC  | UU                         | This bit is set by GL880 whenever its                                                        |

|             |            |       |        |                            | transaction is terminated with Target-Abort.                                                 |

|             |            | 11    | R/W1C  | 0b                         | Signaled Target Abort:                                                                       |

|             |            | 11    | IV WIC |                            | This bit is set by GL880 whenever it terminates                                              |

|             |            |       |        |                            | a transaction with Target-Abort.                                                             |

|             |            | 10:9  | RO     | 01b                        | DEVSEL timing:                                                                               |

|             |            |       |        |                            | GL880 supports medium decode.                                                                |

|             |            | 8     | R/W1C  | 0b                         | Master Data Parity Error:                                                                    |

|             |            |       |        |                            | This bit is only implemented by bus masters. It                                              |

|             |            |       |        |                            | is set when three conditions are met:                                                        |

|             |            |       |        |                            | (1) The bus agent asserted PERRJ itself(on a                                                 |

|             |            |       |        |                            | read) or observed PERRJ asserted(on a write); (2) The agent setting the bit acted as the bus |

|             |            |       |        |                            | master for the operation in which the error                                                  |

|             |            |       |        |                            | occurred;                                                                                    |

|             |            |       |        |                            | (3) The Parity Error Response bit (Command                                                   |

|             |            |       |        |                            | register) is set.                                                                            |

|             |            | 7     | RO     | 0b                         | Fast Back-to-Back Capable:                                                                   |

|             |            | ľ     |        |                            | Fast Back-to –Back is not supported.                                                         |

|             |            | 6     | RO     | 0b                         | Reserved                                                                                     |

|             |            | 5     | RO     | 0b                         | Gl880 does not support                                                                       |

|             |            |       |        |                            | 66MHz operation.                                                                             |

|             |            | 4     | RO     | 1b                         | Capability List:                                                                             |

|             |            |       |        |                            | GL880 implement Power Management                                                             |

|             |            |       |        |                            | capability.                                                                                  |

|             |            | 3:0   | RO     | 0000b                      | Reserved                                                                                     |

| Class Code  | 0x09h      | 23:16 | RO     | 0ch                        | BaseClass:                                                                                   |

|             |            | 1.5.0 | 7.0    | 0.01                       | Serial Bus Controller Device                                                                 |

|             |            | 15:8  | RO     | 03h                        | SubClass                                                                                     |

|             |            | 7.0   | D.O.   | 001-                       | USB Device                                                                                   |

|             |            | 7:0   | RO     | 00h                        | Interface                                                                                    |

| Revision ID | 0x08h      | 7:0   | RO     | 00h                        | Universal Host Controller<br>Version 0.0                                                     |

| BIST        | 0x0fh      | 7:0   | RO     | 00h                        | BIST is not supported                                                                        |

|             |            |       |        |                            |                                                                                              |

| Header Type | uxuen      | 7:0   | RO     | 80h (UHCI0)<br>00h (UHCI1) | PCI Multi-function device                                                                    |

| Latency     | 0x0dh      | 7:3   | R/W    | 00h                        | Latency Timer for this PCI bus master                                                        |

| Timer       |            | 2:0   | RO     | 0h                         |                                                                                              |

| Cache Line  | 0x0ch      | 7:0   | RO     | 00h                        | Cache Line Size                                                                              |

| Size        | o A o o ii | 7.0   |        | 0011                       | Suche Blic Size                                                                              |

|             |            |       |        |                            |                                                                                              |

| Base                   | 0x10h   | 31:5  | R/W      | 0h    | Corresponds to I/O address signals AD[15:5]                                              |

|------------------------|---------|-------|----------|-------|------------------------------------------------------------------------------------------|

| Address                | 0711011 | 51.5  | 10 11    |       | respectively.                                                                            |

| Register               |         | 4:1   | RO       | 0000b | Reserved                                                                                 |

|                        |         | 0     | RO       | 1b    | Base address register field in this register maps to I/O space.                          |

| Subsystem ID           | 0x2eh   | 15:0  | RO       | 0000h | Indicates Subsystem ID                                                                   |

| Subsystem<br>Vender ID | 0x2ch   | 15:0  | RO       | 0000h | Indicates Subsystem Vender ID                                                            |

| Capability<br>Pointer  | 0x34h   | 7:0   | RO       | 40h   | Power Management Capability List header                                                  |

| Max_Lat                | 0x3fh   | 7:0   | RO       | 00h   | Frequency request of PCI access                                                          |

| Min_Gnt                | 0x3eh   | 7:0   | RO       | 00h   | Minimum request for burst period                                                         |

| Interrupt Pin          | 0x3dh   | 7:0   | RO       | 01h   | Routing to INTAJ                                                                         |

| Interrupt<br>Line      | 0x3ch   | 7:0   | R/W      | ffh   | Indicates interrupt line's route                                                         |

| PMC                    | 0x42h   | 15    | RO       | 0b    | Indicates whether D3cold is supported or not.                                            |

|                        |         | 14:11 | RO       | 1111b | PMEJ can be asserted from D0,D1,D2,D3hot.                                                |

|                        |         | 10    | RO       | 1b    | D2_Support:                                                                              |

|                        |         | 9     | RO       | 1b    | Support D2 Power Management State D1 Suport:                                             |

|                        |         |       |          |       | Support D1 Power Management State                                                        |

|                        |         | 8:6   | RO       | 00b   | Aux_Current                                                                              |

|                        |         |       |          |       | Indicates current requirement                                                            |

|                        |         |       |          |       | If PMEJ generation from D3cold is not supported by this host controller core, this field |

|                        |         |       |          |       | must return a value of "000b" when read.                                                 |

|                        |         |       |          |       | If PMEJ generation from D3cold is supported by                                           |

|                        |         |       |          |       | this host controller core, following assignments apply:                                  |

|                        |         |       |          |       | Bit Vaux                                                                                 |

|                        |         |       |          |       | 876 Max.CurrentRequired                                                                  |

|                        |         |       |          |       | 1 1 1 375mA                                                                              |

|                        |         |       |          |       | 1 1 0 320mA                                                                              |

|                        |         |       |          |       | 1 0 1 270mA                                                                              |

|                        |         |       |          |       | 1 0 0 220mA                                                                              |

|                        |         |       |          |       | 0 1 1 169mA<br>0 1 0 100mA                                                               |

|                        |         |       |          |       | 0 0 1 55mA                                                                               |

|                        |         |       |          |       | 0 0 0 0 0mA                                                                              |

|                        |         | 5     | RO       | 0b    | Does not required Specific Initialization before                                         |

|                        |         |       | <u> </u> |       | the generic class device driver is able to use it.                                       |

|                        |         | 4     | RO       | 0b    | Reserved                                                                                 |

|                        |         | 3     | RO       | 0b    | PME Clock:                                                                               |

|                        |         | 2:0   | RO       | 010b  | PCICLK is not required for PMEJ assertion  Version:                                      |

|                        |         | 2.0   | INO      | 0100  | PCI Power Management Interface Specification release 1.1                                 |

| Next Pointer           | 0x41h   | 7:0   | RO       | 00h   | No next item in the list                                                                 |

| Capability ID          | 0x40h   | 7:0   | RO       | 01h   | PCI Power Management Interface                                                           |

| 1 .,                   |         |       | _        |       |                                                                                          |

| PMCSR   | 0x44h  | 15    | R/W1C     | 0b    | PME Status:                                                                               |

|---------|--------|-------|-----------|-------|-------------------------------------------------------------------------------------------|

| INCSK   | UX44II | 13    | IX/ W I C | 00    | This bit is set to "1" when the function would                                            |

|         |        |       |           |       | normally assert PMEJ sugnal independent of the                                            |

|         |        |       |           |       | state of the PME En bit.                                                                  |

|         |        |       |           |       | Writing a "1" to this bit will clear it and cause                                         |

|         |        |       |           |       | the function to stop asserting a PMEJ(if                                                  |

|         |        |       |           |       | enabled). Writing a "0" has no effect.                                                    |

|         |        | 14:13 | D.O.      | 00b   | Data Scale:                                                                               |

|         |        | 14.13 | KO        | 000   |                                                                                           |

|         |        | 12:9  | RO        | 0000b | Data register is not implemented.                                                         |

|         |        | 12:9  | RO        | 00000 | Data_Select: Data register is not implemented.                                            |

|         |        | 8     | R/W       | 0b    | PME En:                                                                                   |

|         |        | 0     | IX/ VV    | 00    | Enable to assert PMEJ.                                                                    |

|         |        |       |           |       | 0b: PMEJ assertion disable                                                                |

|         |        |       |           |       | 1b: PMEJ assertion enable                                                                 |

|         |        |       |           |       | This bit default to "0" if the host controller core                                       |

|         |        |       |           |       | does not support PMEJ generation from D3cold.                                             |

|         |        |       |           |       |                                                                                           |

|         |        |       |           |       | If the host controller core supports PMEJ generation from D3cold, then this bit is sticky |

|         |        |       |           |       | and must be explicitly cleared by the OS each                                             |

|         |        |       |           |       | time it is initially loaded.                                                              |

|         |        | 7:2   | RO        | 00h   | Reserved                                                                                  |

|         |        |       |           |       |                                                                                           |

|         |        | 1:0   | R/W       | 00b   | Power State:                                                                              |

|         |        |       |           |       | Shows power state of a host controller core and                                           |

|         |        |       |           |       | sets the host controller core into a new power state.                                     |

|         |        |       |           |       | <mark>00</mark> b: D0                                                                     |

|         |        |       |           |       | 01b: D1                                                                                   |

|         |        |       |           |       | 10b: D2                                                                                   |

|         |        |       |           |       | 11b: D3hot                                                                                |

| SBRN    | 0x60h  | 7:0   | RO        | 10h   | Serial Bus Specification Release                                                          |

|         |        |       |           |       | Number 1.0                                                                                |

| UHCI    | 0xC0h- | 15    | R/W1C     | 0     | SMI Caused by End of Pass-through. Indicates                                              |

| Legacy  | 0xC1h  |       |           |       | whether the event occurred.                                                               |

| Support | (UHCI0 |       |           |       | 1: Event Occurred                                                                         |

|         | only)  |       |           |       | 0: Software clears this bit by writing a 1 to the                                         |

|         |        |       |           |       | bit location.                                                                             |

|         |        | 14    | RO        | 0     | Reserved                                                                                  |

|         |        | 13    | R/W       | 1     | PCI Interrupt Enable. Used to prevent the USB                                             |

|         |        | 13    | 13/ 1/    | 1     | controller from generating an interrupt due to                                            |

|         |        |       |           |       | transactions on its ports.                                                                |

|         |        |       |           |       | 1: Enable                                                                                 |

|         |        |       |           |       | 0: Disable                                                                                |

|         |        | 12    | RO        | 0     | SMI Caused by USB Interrupt. Indicates                                                    |

|         |        | 12    | INO.      |       | iwhether the event occurred.                                                              |

|         |        |       |           |       | 1: Event Occurred                                                                         |

|         |        |       |           |       | 0: No event occurred.                                                                     |

|         |        | 11    | R/W1C     | 0     | SMI Caused by Port 64 Write. Indicates whether                                            |

|         |        | 11    | IV W IC   | U     | the event occurred.                                                                       |

|         |        |       |           |       | 1: Event Occurred                                                                         |

|         |        |       |           |       |                                                                                           |

|         |        |       |           |       | 0: Software clears this bit by writing a 1 to the                                         |

| •       | Į      |       | <u> </u>  | L     | bit location.                                                                             |

|            |              | 10 | R/W1C  | 0 | SMI Caused by Port 64 Read. Indicates whether the event occurred.            |

|------------|--------------|----|--------|---|------------------------------------------------------------------------------|

|            |              |    |        |   | 1: Event Occurred                                                            |

|            |              |    |        |   | 0: Software clears this bit by writing a 1 to the bit location.              |

|            |              | 9  | R/W1C  | 0 | SMI Caused by Port 60 Write. Indicates whether                               |

|            |              |    |        |   | the event occurred.                                                          |

|            |              |    |        |   | 1: Event Occurred                                                            |

|            |              |    |        |   | 0: Software clears this bit by writing a 1 to the bit location.              |

|            |              | 8  | R/W1C  | 0 | SMI Caused by Port 60 Read. Indicates whether                                |

|            |              |    |        |   | the event occurred.                                                          |

|            |              |    |        |   | 1: Event Occurred                                                            |

|            |              |    |        |   | 0: Software clears this bit by writing a 1 to the bit location.              |

|            |              | 7  | R/W    | 0 | SMI at End of Pass-through Enable. May need to                               |

|            |              |    |        |   | cause SMI at the end of a pass-through.                                      |

|            |              |    |        |   | Can occur if an SMI is generated in the middle                               |

|            |              |    |        |   | of a pass through, and needs to be serviced later.  1: Enable                |

|            |              |    |        |   | 0: Disable                                                                   |

|            |              | 6  | RO     | 0 | Pass Through State.                                                          |

|            |              |    |        |   | 1: Indicates that the state machine is in the                                |

|            |              |    |        |   | middle of an A20GATE pass-through sequence.                                  |

|            |              |    |        |   | 0: If software needs to reset this bit, it should set bit 5 to 0.            |

|            |              | 5  | R/W    | 0 | A20Gate Pass-Through Enable.                                                 |

|            |              |    | 10 11  |   | 1: Allows A20GATE sequence Pass-Through                                      |

|            |              |    |        |   | function. SMI# will not be generated, even if                                |

|            |              |    |        |   | the various enable bits are set.                                             |

|            |              | 4  | D/III  |   | 0: Disable                                                                   |

|            |              | 4  | R/W    | 0 | SMI on USB IRQ Enable 1: USB interrupt will cause an SMI event.              |

|            |              |    |        |   | 0: Disable                                                                   |

|            |              | 3  | R/W    | 0 | SMI on Port 64 Writes Enable.                                                |

|            |              |    |        |   | 1: A write to port 64h will cause an SMI event.                              |

|            |              | 2  | D/III  |   | 0: Disable                                                                   |

|            |              | 2  | R/W    | 0 | SMI on Port 64 Reads Enable.  1: A read to port 64h will cause an SMI event. |

|            |              | 4  |        |   | 0: Disable                                                                   |

|            |              | 1  | R/W    | 0 | SMI on Port 60 Writes Enable.                                                |

|            |              |    |        |   | 1: A write to port 60h will cause an SMI event.                              |

|            |              |    | D /777 |   | 0: Disable                                                                   |

|            |              | 0  | R/W    | 0 | SMI on Port 60 Reads Enable.                                                 |

|            |              |    |        |   | 1: A read to port 60h will cause an SMI event. 0: Disable                    |

| Serial ROM | 0xF0h        | 4  | RO     | X | Output of Serial ROM.                                                        |

| Control    | (UHCI0 only) | 3  | R/W    | 0 | ROMDI                                                                        |

|            | 37           | 2  | R/W    | 0 | ROMCS                                                                        |

|            |              | 1  | R/W    | 0 | ROMSK                                                                        |

|            |              | 0  | R/W    | 0 | Reserved                                                                     |

## **5.1.2 Funcion 3 Enhanced Host Controller Interface**

| Register  | Address | Bit   | R/W/W1C | <b>Default Value</b> | Descriptions                                                                                                                                                                                                                                                                                                                           |

|-----------|---------|-------|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device ID | 0x02h   | 15:0  | RO      | 0x8084h              | Genesys Logic<br>UHCI's device ID                                                                                                                                                                                                                                                                                                      |

| Vendor ID | 0x00h   | 15:0  | RO      | 0x17A0h              | Genesys Logic's Vendor ID                                                                                                                                                                                                                                                                                                              |

| Command   | 0x04h   | 15:10 | RO      | 000000ь              | Reserved                                                                                                                                                                                                                                                                                                                               |

|           |         | 9     | RO      | 0b                   | GL880 doesnot supprt Fast Back-to-Back cycle.                                                                                                                                                                                                                                                                                          |

|           |         | 8     | R/W     | 0b                   | SERRJ Enable: This bit is an enable bit for the SERRJ driver. 0: Disables the SERRJ driver 1: Enables the SERRJ driver                                                                                                                                                                                                                 |

|           |         | 7     | RO      | 0b                   | Reserved                                                                                                                                                                                                                                                                                                                               |

|           |         | 6     | R/W     | ОЬ                   | Parity Error Response: This bit controls the device's response to parity errors.  0: The device sets its Detected Parity Error status bit(bit15 in the Status register) when an error is detected, but does not assert PERRJ and continues normal operation  1: The device must take its normal action when a parity error is detected |

|           |         | 5     | RO      | 0b                   | GL880 doesnot support palette snoop cycles.                                                                                                                                                                                                                                                                                            |

|           |         | 4     | RO      | 0b                   | GL880 doesnot support Memory Write and Invalidate Command                                                                                                                                                                                                                                                                              |

|           |         | 3     | RO      | 0b                   | GL880 doesnot support Special Cycles.                                                                                                                                                                                                                                                                                                  |

|           |         | 2     | R/W     | 0b                   | Bus Master: Controls a device's ability to act as a master on the PCI bus. 0: Disables the device from generating PCI accesses 1: Allows the device to behave as a bus master                                                                                                                                                          |

|           | 4       | 1     | R/W     | 0b                   | Memory Space: Controls a device's response to Memory space accesses. 0: Disables the device response 1: Allows the device to respond to Memory space accesses                                                                                                                                                                          |

|           |         | 0     | RO      | 0b                   | EHCI doesnot support IO access.                                                                                                                                                                                                                                                                                                        |

| Status    | 0x06h   | 15    | R/W1C   | 0b                   | Detected Parity Error: This bit is set by GL880 whenever it detects a parity error even if parity error handling is disabled.                                                                                                                                                                                                          |

|           |         | 14    | R/W1C   | 0b                   | Signaled System Error:<br>This bit is set whenever GL880 asserts SERRJ                                                                                                                                                                                                                                                                 |

| 4         |         | 13    | R/W1C   | 0b                   | Received Master Abort: This bit is set by GL880 whenever its transaction is terminated with Master-Abort.                                                                                                                                                                                                                              |

|           |         | 12    | R/W1C   | 0b                   | Received Target Abort: This bit is set by GL880 whenever its transaction is terminated with Target-Abort.                                                                                                                                                                                                                              |

|             | 1      | 1     |       | T      | I and the second |

|-------------|--------|-------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |        | 11    | R/W1C | 0b     | Signaled Target Abort:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |        |       |       |        | This bit is set by GL880 whenever it terminates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |        |       |       |        | a transaction with Target-Abort.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |        | 10:9  | RO    | 01b    | DEVSEL timing:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             |        |       |       |        | GL880 support medium decode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |        | 8     | R/W1C | 0b     | Master Data Parity Error:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |