# **DATA SHEET**

# gm3020-NH/gm3020-H

Sections in this document and all other related documentation that mention HDCP refer only to the gm3020-H (HDCP-enabled) chip. All other sections apply to both the gm3020-H chip and the gm3020-HN (non-HDCP) chip.

C3020-DAT-01F

October 2001

#### **Document History:**

| Revision      | Description                                                                                  | Date          |

|---------------|----------------------------------------------------------------------------------------------|---------------|

| C3020-DAT-01A | Initial Release                                                                              | June 2000     |

| C3020-DAT-01B | Correction to PWM pin-out (pins 65-67)                                                       | August 2000   |

| C3020-DAT-01C | Added Ultra-Reliable DVI™ and updated Electrical Characteristics tables                      | October 2000  |

| C3020-DAT-01D | Removed references to SXGA                                                                   | December 2000 |

| C3020-DAT-01E | Added On-chip TCLK Oscillator description in Section 5.9                                     | January 2001  |

| C3020-DAT-01F | Added gm3020-NH and gm3020-H and changed all references to TMDS to DVI and updated section 8 | October 2001  |

#### **Related Documents:**

| Doc Number    | Title             | Date          |

|---------------|-------------------|---------------|

| C3020-DSR-01C | Programming Guide | February 2001 |

|               |                   |               |

## © Copyright 2001, Genesis Microchip Inc. All Rights Reserved.

Genesis Microchip Inc. reserves the right to change or modify the information contained herein without notice. It is the customer's responsibility to obtain the most recent revision of the document. Genesis Microchip Inc. makes no warranty for the use of its products and bears no responsibility for any errors or omissions that may appear in this document

# **TABLE OF CONTENTS**

| 1. | 0          | OVERVIEW                                                | 1   |

|----|------------|---------------------------------------------------------|-----|

| 2. | FI         | EATURES & APPLICATIONS                                  | 2   |

| 2  | D          | PINOUT                                                  | 4   |

| 3. |            |                                                         |     |

|    |            | PIN DESCRIPTION                                         |     |

| 4. | 0          | PERATING MODES                                          | 10  |

|    | 4.1        | NATIVE MODE                                             | 10  |

|    | 4.2        | SLOW DCLK MODE                                          |     |

|    | 4.3        | EXPANSION MODE                                          |     |

|    | 4.4        | DOWNSCALING MODE                                        |     |

|    | 4.5        | SOURCE STAND ALONE MODE                                 |     |

|    | 4.6<br>4.7 | DESTINATION STAND ALONE MODE                            |     |

|    |            |                                                         |     |

| 5. | Fl         | UNCTIONAL BLOCK DESCRIPTION                             |     |

|    | 5.1        |                                                         |     |

|    |            | INPUT CAPTURE/TIMING MEASUREMENT BLOCKS                 |     |

|    | •          | 2.2.1. Input Capture Block                              |     |

|    | -          | 5.2.2. Input Timing Measurement Block                   |     |

|    | 5.3<br>5.4 | CLOCK SCALING BLOCK                                     |     |

|    | • • • •    | DATA PATHGAMMA TABLE                                    |     |

|    |            | 5.5.1. Expander Interpolator                            |     |

|    |            | .5.2. RGB Offset                                        |     |

|    | •          | .5.3. Panel Data Dither                                 |     |

|    |            | .5.4. Panel Background Color                            |     |

|    | 5.6        | Panel Interface                                         |     |

|    | 5.         | .6.1. TFT Panel Interface Timing Specification          | 21  |

|    | 5.         | .6.2. TFT LCD Power Sequencer                           | 24  |

|    | -          | .6.3. Panel Interface Drive Strength                    |     |

|    |            | HOST INTERFACE                                          |     |

|    |            | 7.7.1. Host interface pin connection                    |     |

|    | •          | 5.7.2. gm3020-NH/gm3020-H Serial Communication Protocol |     |

|    |            | OSD (On-Screen Display) Control                         |     |

|    |            | 8.8.1. On-Chip OSD                                      |     |

|    |            | On-chip TCLK Oscillator                                 |     |

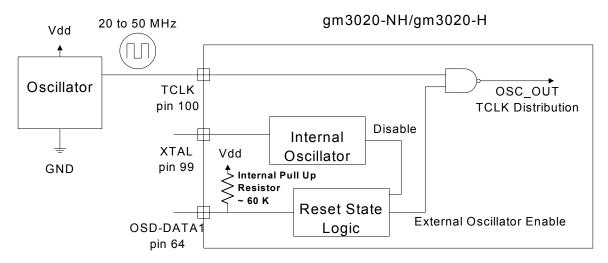

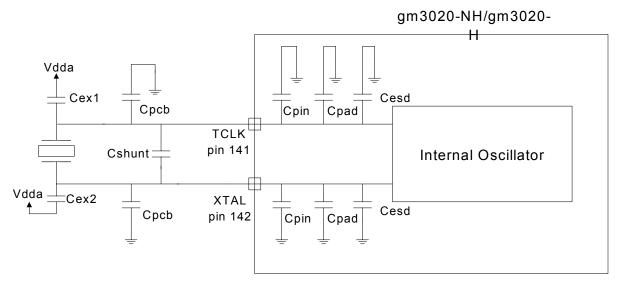

|    |            | 9.9.1. External Oscillator mode                         |     |

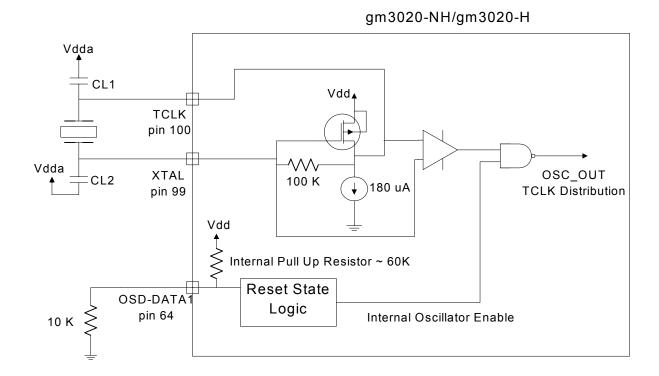

|    |            | 9.9.2. Internal Oscillator mode                         |     |

|    | 5.10       |                                                         |     |

| 6. |            | LECTRICAL CHARACTERISTICS                               |     |

| ٥. |            |                                                         |     |

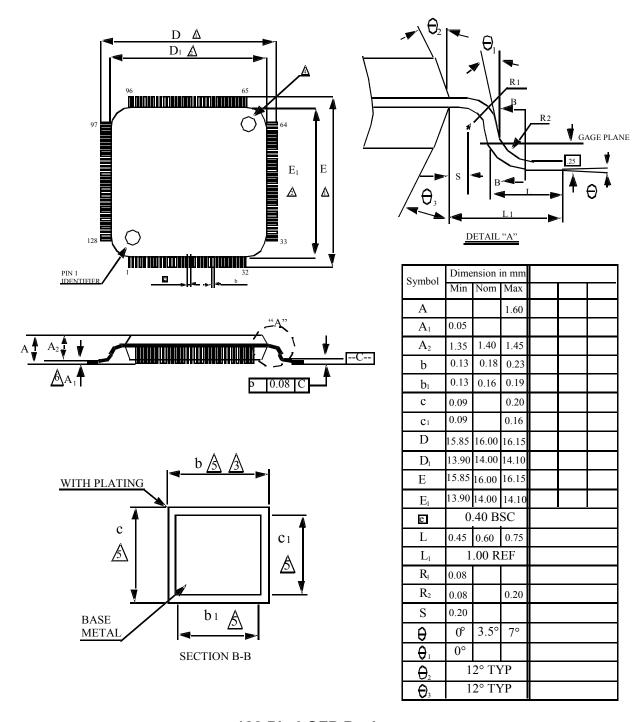

| 7. | M          | MECHANICAL SPECIFICATIONS                               | 43  |

| 0  | _          | OPPEDING INFORMATION                                    | 4.4 |

# **TABLE OF FIGURES**

| Figure 1: Single-Chip Solution for Low Cost Flat Panel Digital Interface Monitor | 3  |

|----------------------------------------------------------------------------------|----|

| Figure 2: gm3020-NH/gm3020-H Pinout                                              | 4  |

| FIGURE 3: GM3020-NH/GM3020-H BLOCK DIAGRAM                                       | 13 |

| Figure 4: Capture Window                                                         | 16 |

| FIGURE 5: CLOCK SCALING BLOCK DIAGRAM                                            | 18 |

| Figure 6: Data Path                                                              | 19 |

| FIGURE 7: TFT PANEL INTERFACE TIMING (ONE PIXEL PER CLOCK)                       | 23 |

| FIGURE 8: TFT PANEL INTERFACE DATA LATCH TIMING                                  | 24 |

| FIGURE 9: SERIAL COMMUNICATION TIMING DIAGRAM                                    | 28 |

| FIGURE 10: SERIAL HOST INTERFACE DATA TRANSFER FORMAT                            | 29 |

| FIGURE 11: On-CHIP OSD WINDOW LOCATION                                           | 32 |

| FIGURE 12: GM3020-NH/GM3020-H On-CHIP FONTS IN ROM                               | 32 |

| FIGURE 13: EXTERNAL OSD INTERFACE DATA LATCH TIMING                              | 35 |

| Figure 14: Using an External Oscillator                                          | 37 |

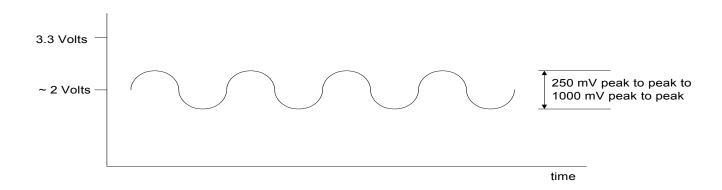

| Figure 15: Using an Internal Oscillator                                          | 38 |

| FIGURE 16: INTERNAL OSCILLATOR OUTPUT AT TCLK                                    | 38 |

| FIGURE 17: PARASITIC CAPACITANCE SOURCES                                         | 40 |

# **LIST OF TABLES**

| TABLE 1: ULTRA-RELIABLE DVI <sup>TM</sup> RECEIVER                                         | 5  |

|--------------------------------------------------------------------------------------------|----|

| TABLE 2: HOST INTERFACE (HIF), EXTERNAL ON-SCREEN DISPLAY (EOSD), AND GENERAL-PURPO (GPIO) |    |

| TABLE 3: CLOCK RECOVERY AND TIME BASE CONVERSION                                           | 7  |

| TABLE 4: TFT PANEL INTERFACE                                                               | 8  |

| TABLE 5: PIN-SCAN TEST PINS.                                                               | 9  |

| TABLE 6: POWER AND GROUND PINS                                                             | 9  |

| TABLE 7: RECEIVER CHARACTERISTICS                                                          | 14 |

| TABLE 8: INPUT TIMING PARAMETERS MEASURED BY THE STM BLOCK                                 | 16 |

| Table 9: IRQ-Generation Condition                                                          | 17 |

| TABLE 10: GM3020-NH/GM3020-H TFT PANEL INTERFACE TIMING                                    | 21 |

| TABLE 11: PANEL POWER SEQUENCE TIMING DEFINITION.                                          | 26 |

| TABLE 12: PANEL INTERFACE PAD DRIVE STRENGTH.                                              | 26 |

| TABLE 13: GM3020-NH/GM3020-H HOST INTERFACE                                                | 27 |

| TABLE 14: GM3020-NH/GM3020-H SERIAL CHANNEL SPECIFICATION                                  | 29 |

| TABLE 15: ON-CHIP CHARACTER CODE                                                           | 31 |

| TABLE 16: ON-CHIP OSD COLOR CONTROL                                                        | 31 |

| Table 17: Pin Connection Between the gm3020-H and an External OSD controller               | 34 |

| TABLE 18: EXTERNAL OSD INTERFACE TIMING PARAMETERS                                         | 36 |

| TABLE 19: TCLK SPECIFICATIONS                                                              | 36 |

| TABLE 20: DISABLING FUNCTIONAL BLOCKS                                                      | 41 |

| TABLE 21: ABSOLUTE RATINGS                                                                 | 42 |

| Table 22: Electrical Characteristics                                                       | 42 |

## 1. OVERVIEW

The Genesis Microchip gm3020-NH/gm3020-H are the industry-leading single-chip scaling solution for digital LCD monitors for resolutions up to XGA. The gm3020-NH/gm3020-H, with the superb image quality of the Genesis' patented Advanced Image Magnification algorithm and the Ultra-Reliable DVI<sup>TM</sup> receiver for a direct digital connection, integrates all the necessary components required for a high quality digital LCD controller system in a single device.

With features such as High-bandwidth Digital Content Protection (HDCP 1.0) support plus the extra security of Genesis secret key encryption (gm3020-H only), built-in 10-bit gamma correction tables, color filtering in the YUV domain, RealColor™, that allows adjustment for brightness / contrast / hue / saturation / proprietary flesh-tone, programmable PWM control for backlight brightness, and a versatile multi-language On Screen Display (OSD) controller and the Ultra-Reliable DVI™ receiver providing interoperability to all DVI compliant DVI transmitters, the gm3020-NH/gm3020-H are the optimal, low cost solution for Digital Visual Interface (DVI) compliant LCD Monitors.

October 2001 -1- C3020-DAT-01F

## 2. FEATURES & APPLICATIONS

#### **FEATURES**

#### High-quality advance image scaling engine

- Fully programmable zoom ratios.

- Independent horizontal/vertical zoom.

- Advanced zoom algorithm provides sharpest text images.

#### • Ultra-Reliable DVI™ receiver

- Single channel DVI specification 1.0 compliant.

- Supporting Ultra-Reliable DVI™ receiver.

- Single-channel DVI (1.0) compliant.

- Supporting input resolutions up to XGA 75Hz.

- Direct connection to all DVI (1.0) compliant DVI transmitters.

## High-Bandwidth Digital Content Protection (HDCP) Revision 1.0 Support (gm3020-H only)

- Added security of Genesis hardware-supported secret key encryption/decryption.

- I<sup>2</sup>C bus for HDCP support.

#### • Integrated On-Screen Display Controller

- Programmable OSD window size up to 32 by 16 characters.

- Multi-language font ROM table with 256 characters.

- Optional external OSD controller (gm3020-H only) can be supported for flexibility.

#### • Image Color Controls

- Three 256 x 10 gamma lookup tables for color matching and calibration requirements for LCD panels.

- Color temperature and brightness adjustments for reducing the difference of the color characteristics of various TFT LCD panels.

- RGB888-to-YUV444 color-space converter allows contrast/brightness/hue/saturation/fleshtone RealColor<sup>TM</sup> adjustments in YUV444 domain

#### • Integrated High Speed Digital Clock

- All output frequencies are generated from a single 50 MHz reference oscillator.

- Stand alone mode for factory testing and burnin.

#### Optimized Panel Output Clock

- Panel clock frequency is optimized to support each mode at the lowest possible frequency.

- Panel clock pad drive strength is programmable, also reducing EMI in the panel interface cable.

#### • TFT LCD Panel Support

- All panel resolutions and sizes are supported up to XGA.

- Panel interface supports one or two pixel per clock, Sync only, DE only and Sync/DE composite panels.

- Panel output data dithering gives 18-bit/pixel panels more smoothly shaded colors.

#### Four Wire Interface to Microcontroller

Simple 4 wire serial interface connects directly to monitor micro-controller.

#### Programmable PWM Outputs

One programmable duty-cycle and one fixed 50% duty-cycle PWM outputs for panel backlight brightness control.

#### • Standard 128 Pin LQFP Package

XGA operations between 0°C to 70°C

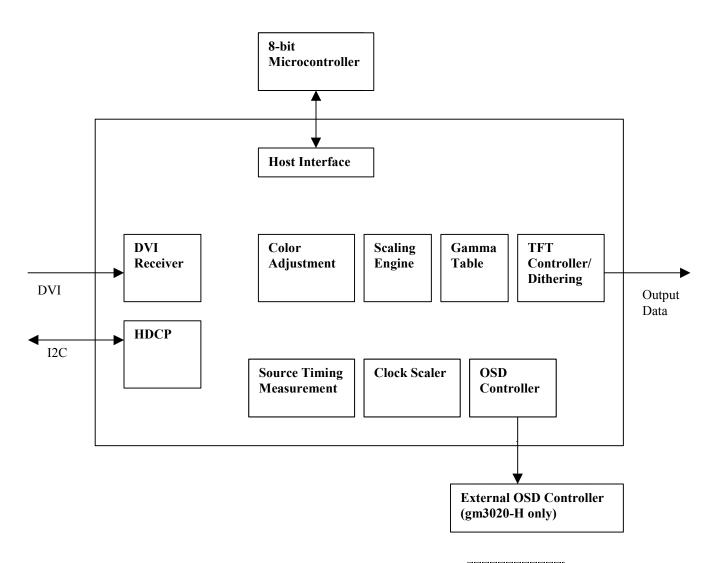

Figure 1: Single-Chip Solution for Low Cost Flat Panel Digital Interface Monitor

## 3. PINOUT

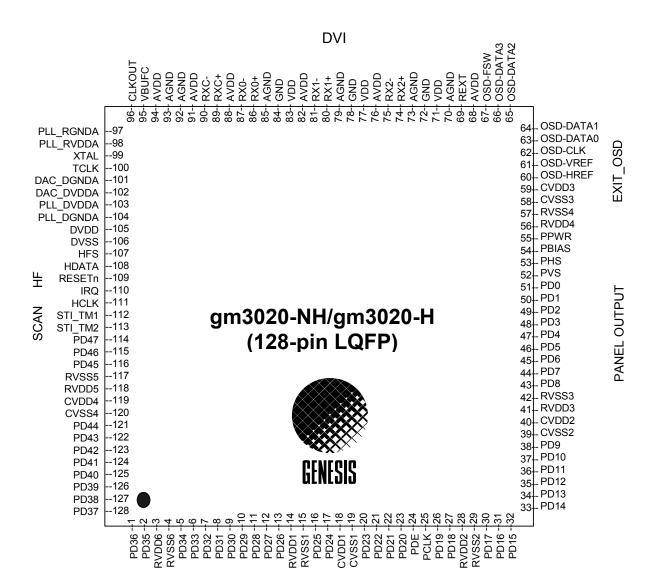

Figure 2: gm3020-NH/gm3020-H Pinout

# 3.1 Pin Description

Unless otherwise stated, unused input pins must be tied to ground, and unused output pins left open.

Table 1: Ultra-Reliable DVI™ Receiver

| Pin<br>No. | Name | In/Out | 5V Tolerant<br>Input ? | Description                                                                                                           |  |  |

|------------|------|--------|------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| 68         | AVDD |        |                        | Analog VDD for internal biasing circuits. Must be bypassed with 100pF, 1nF and 10uF capacitors in parallel to pin 70. |  |  |

| 69         | REXT | In     |                        | External termination resistor. A 1% 1K ohm resistor should be connected from this pin to pin 68.                      |  |  |

| 70         | AGND |        |                        | Analog GND for internal biasing circuits. Must be connected directly to the ground plane.                             |  |  |

| 71         | VDD  |        |                        | VDD for DVI input pair 0 logic circuits. Must be bypassed with 100pF, 1nF and 10uF capacitor to pin 72.               |  |  |

| 72         | GND  |        |                        | GND for DVI input pair 0 logic circuits. Must be connected directly to the ground plane.                              |  |  |

| 73         | AGND |        |                        | Analog GND for DVI input pair 0 input buffer. Must be connected directly to the analog ground plane.                  |  |  |

| 74         | RX2+ | In     |                        | DVI input pair 2                                                                                                      |  |  |

| 75         | RX2- | In     |                        | DVI input pair 2                                                                                                      |  |  |

| 76         | AVDD |        |                        | Analog VDD for DVI input pair 0 input buffer. Must be bypassed with 100pF capacitor to pin 73.                        |  |  |

| 77         | VDD  |        |                        | VDD for DVI input pair 1 logic circuits. Must be bypassed with100pF, 1nF and 10uF capacitor to pin 78.                |  |  |

| 78         | GND  |        |                        | GND for DVI input pair 1 input buffer. Must be connected directly to the analog ground plane.                         |  |  |

| 79         | AGND |        |                        | Analog GND for DVI input pair 1 input buffer. Must be connected directly to the analog ground plane.                  |  |  |

| 80         | RX1+ | In     |                        | DVI input pair 1                                                                                                      |  |  |

| 81         | RX1- | In     |                        | DVI input pair 1                                                                                                      |  |  |

| 82         | AVDD |        |                        | Analog VDD for DVI input pair 1 input buffer. Must be bypassed with 100pF capacitor to pin 79.                        |  |  |

| 83         | VDD  |        |                        | VDD for DVI input pair 2 logic circuits. Must                                                                         |  |  |

| 84         | GND  |        |                        | GND for DVI input pair 2 logic circuits. Must be connected directly to the ground plane.                              |  |  |

| 85         | AGND |        |                        | Analog GND for DVI input pair 2 input buffer. Must be connected directly to the analog ground plane.                  |  |  |

| 86         | RX0+ | In     |                        | DVI input pair 0                                                                                                      |  |  |

| 87         | RX0- | In     |                        | DVI input pair 0                                                                                                      |  |  |

| 88         | AVDD |        |                        | Analog VDD for DVI input pair 2 input buffer. Must be bypassed with 100pF capacitor to pin 85.                        |  |  |

| 89         | RXC+ | ln     |                        | DVI input clock pair                                                                                                  |  |  |

| 90         | RXC- | In     |                        | DVI input clock pair                                                                                                  |  |  |

| 91         | AVDD |        |                        | Analog VDD for DVI input clock pair input buffer. Must be bypassed with 100pF capacitor to pin 92.                    |  |  |

| 92         | AGND |        |                        | Analog GND for DVI input clock pair input buffer. Must be connected directly to the analog ground plane.              |  |  |

| Pin<br>No. | Name   | In/Out | 5V Tolerant<br>Input ? | Description                                                                                          |

|------------|--------|--------|------------------------|------------------------------------------------------------------------------------------------------|

| 93         | AGND   |        |                        | Analog GND for the DVI receiver internal PLL. Must be connected directly to the analog ground plane. |

| 94         | AVDD   |        |                        | Analog VDD for the DVI receiver internal PLL. Must be bypassed with a capacitor to pin 93.           |

| 95         | VBUFC  | Out    |                        | For internal test purposes only.                                                                     |

| 96         | CLKOUT | Out    |                        | For internal test purposes only.                                                                     |

Table 2: Host Interface (HIF), External On-Screen Display (EOSD), and General-Purpose I/O Bus (GPIO)

| Pin<br>No. | Name              | In/Out | 5V Tolerant<br>Input | Description                                                                                                                     |  |  |  |

|------------|-------------------|--------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 107        | HFS               | In     | 5V tolerant          | Active-high Host Frame Sync. Marks the beginning of the host interface data packet. This pin has an internal pull-down resistor |  |  |  |

| 108        | HDATA             | In/Out | 5V tolerant<br>/4mA  | Host serial interface data signal input/output.                                                                                 |  |  |  |

| 109        | RESETn            | In     | 5V tolerant          | Resets the chip when low for at least 100 ns. Active low input.                                                                 |  |  |  |

| 110        | IRQ               | Out    | 4 mA                 | Interrupt request output.                                                                                                       |  |  |  |

| 111        | HCLK              | In     | 5V tolerant          | Host Interface clock signal input.                                                                                              |  |  |  |

| 60         | OSD-<br>HREF      | Out    | 4 mA                 | HREF output for external OSD controller.  Note: This pin is a no-connect in gm3020-NH                                           |  |  |  |

|            | Serial Data<br>1  | In/Out | 5V tolerant<br>/4 mA | Used for HDCP and encrypted secret key storage. To be pulled up externally to +5V.                                              |  |  |  |

| 61         | OSD-<br>VREF      | Out    | 4 mA                 | VREF output for external OSD controller.                                                                                        |  |  |  |

|            | Serial<br>Clock 1 | In/Out | 5V tolerant<br>/4 mA | Used for HDCP and encrypted secret key storage. To be pulled up externally to +5V.                                              |  |  |  |

| 62         | OSD-CLK           | Out    | 4 mA                 | Clock output for external OSD controller                                                                                        |  |  |  |

|            | GPIO bit 0        | In/Out | 5V tolerant<br>/4 mA | General purpose I/O bus bit 0                                                                                                   |  |  |  |

| 63         | OSD-<br>DATA0     | In     | 5V tolerant          | Data input bit 0 from external OSD controller.                                                                                  |  |  |  |

|            | GPIO bit 1        | In/Out | 5V tolerant<br>/4 mA | General purpose I/O bus bit 1                                                                                                   |  |  |  |

| 64         | OSD-<br>DATA1     | In     | 5V tolerant          | Data input bit 1 from external OSD controller.                                                                                  |  |  |  |

|            | GPIO bit 2        | In/Out | 5V tolerant          | General purpose I/O bus bit 2                                                                                                   |  |  |  |

|            |                   |        | /4 mA                | When externally pulled down to ground, the internal oscillator is used; otherwise an external oscillator must be used.          |  |  |  |

| 65 | OSD-<br>DATA2 | In     | 5V tolerant          | Data input bit 2 from external OSD controller                                                                                                                           |  |  |

|----|---------------|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    | GPIO bit 3    | In/Out | 5V tolerant          | General purpose I/O bus bit 3.                                                                                                                                          |  |  |

|    | PWM0          |        | /4 mA                | This pin can also be configured as PWM output 0 for backlight brightness control. Its frequency is programmable, while its duty cycle is fixed at 50%.                  |  |  |

| 66 | OSD-<br>DATA3 | In     | 5V tolerant          | Data input bit 3 from external OSD controller.                                                                                                                          |  |  |

|    | GPIO bit 4    | In/Out | 5V tolerant          | General purpose I/O bus bit 4; this pin is internally pulled up.                                                                                                        |  |  |

|    | PWM1          |        | /4 mA                | This pin can also be configured as PWM output 1 for backlight brightness control. Its frequency is programmable, while its duty cycle is also programmable in 32 steps. |  |  |

| 67 | OSD-FSW       | ln     | 5V tolerant          | External OSD window display enable. Displays data fror external OSD controller when high.                                                                               |  |  |

|    | GPIO bit 5    | In/Out | 5V tolerant<br>/4 mA | General purpose I/O bus bit 5; this pin is internally pulled up.                                                                                                        |  |  |

Table 3: Clock Recovery and Time Base Conversion

| Pin<br>No. | Name      | In/Out | 5V Tolerant<br>Input | Description                                                                                                  |

|------------|-----------|--------|----------------------|--------------------------------------------------------------------------------------------------------------|

| 97         | PLL_RGNDA |        |                      | Analog ground for the Reference PLL. Must be directly connected to the analog ground plane.                  |

| 98         | PLL_RVDDA |        |                      | Analog power for the Reference PLL. Must be bypassed with a 0.1 uF capacitor to pin 97.                      |

| 99         | XTAL      | Out    |                      | Output for external crystal. When external oscillator is used, this pin may be left open.                    |

| 100        | TCLK      | In     | 5V tolerant          | Reference clock (TCLK) input from external 50 MHz crystal oscillator.                                        |

| 101        | DAC_DGNDA |        |                      | Analog ground for Destination DDS DAC. Must be directly connected to the analog ground plane.                |

| 102        | DAC_DVDDA |        |                      | Analog power for Destination DDS DAC. Must be bypassed with a 0.1 uF capacitor to pin 101 (DAC_DGNDA)        |

| 103        | PLL_DVDDA |        |                      | Analog power for the Destination DDS PLL. Must be bypassed with a 0.1 uF capacitor to pin 104 (PLL_DGNDA)    |

| 104        | PLL_DGNDA |        |                      | Analog ground for Destination DDS PLL. Must be directly connected to the analog ground plane.                |

| 105        | DVDD      |        |                      | Digital power for Destination DDS logic circuits. Must be bypassed with a 0.1 uF capacitor to pin 106 (DVSS) |

| 106        | DVSS      |        |                      | Digital ground for Destination DDS logic circuits. Must be directly connected to the ground plane.           |

**Table 4: TFT Panel Interface**

NOTE: Drive current of the panel output pins are programmable Pin No. Name In/ **Output Drive** Description TFT (one pixel/clock) TFT (two Out Current pixels/clock) @ 10pF 8 bit 6 bit 4 bit 8 bit 6 bit PD47 2mA~20mA Panel data output 47 OB7 114 Out OB<sub>5</sub> Out 115 PD46 2mA~20mA Panel data output 46 OB6 OB4 116 PD45 Out 2mA~20mA Panel data output 45 OB5 OB3 121 PD44 2mA~20mA Panel data output 44 OB4 OB2 122 PD43 Out 2mA~20mA Panel data output 43 OB3 OB1 PD42 Panel data output 42 OB0 123 Out 2mA~20mA OB<sub>2</sub> 124 PD41 Out 2mA~20mA Panel data output 41 OB1 125 PD40 Out 2mA~20mA Panel data output 40 OB0 PD39 OG7 OG5 126 Out 2mA~20mA Panel data output 39 PD38 Panel data output 38 OG6 OG4 127 Out 2mA~20mA 128 PD37 Out 2mA~20mA Panel data output 37 OG5 OG3 Panel data output 36 1 PD36 Out 2mA~20mA OG4 OG2 2 PD35 Out 2mA~20mA Panel data output 35 OG3 OG1 5 PD34 Out 2mA~20mA Panel data output 34 OG2 OG0 6 PD33 Out 2mA~20mA Panel data output 33 OG1 7 PD32 Out 2mA~20mA Panel data output 32 OG0 8 PD31 OR7 Out 2mA~20mA Panel data output 31 OR5 9 PD30 Panel data output 30 OR6 OR4 Out 2mA~20mA 10 PD29 Out 2mA~20mA Panel data output 29 OR5 OR3 PD28 OR4 OR2 11 Out 2mA~20mA Panel data output 28 12 PD27 Panel data output 27 OR3 OR1 Out 2mA~20mA 13 PD26 Out 2mA~20mA Panel data output 26 OR2 OR0 16 PD25 Panel data output 25 OR1 Out 2mA~20mA 17 PD24 Out 2mA~20mA Panel data output 24 OR<sub>0</sub> 20 PD23 Out 2mA~20mA Panel data output 23 В7 B5 B3 EB7 EB5 21 PD22 Out 2mA~20mA Panel data output 22 В6 B4 B2 EB6 EB4 22 PD21 Out 2mA~20mA Panel data output 21 В5 В3 В1 EB5 EB3 23 PD20 Out Panel data output 20 В4 B2 B0 EB4 EB2 2mA~20mA 26 PD19 Panel data output 19 В3 В1 EB3 EB1 Out 2mA~20mA 27 PD18 Out 2mA~20mA Panel data output 18 B2 B0 EB2 EB0 30 PD17 В1 EB1 Out 2mA~20mA Panel data output 17 B0 31 PD16 Out 2mA~20mA Panel data output 16 EB0 32 PD15 Out 2mA~20mA Panel data output 15 G7 G5 G3 EG7 EG5 Panel data output 14 33 PD14 2mA~20mA G6 G4 G2 EG6 EG4 Out 34 PD13 Out 2mA~20mA Panel data output 13 G5 G3 G1 EG5 EG3 35 PD12 Out 2mA~20mA Panel data output 12 G4 G2 G0 EG4 EG2 36 PD11 Out 2mA~20mA Panel data output 11 G3 G1 EG3 EG1 37 PD10 Out 2mA~20mA Panel data output 10 G2 G0 EG2 EG0 PD 9 38 Out 2mA~20mA Panel data output 9 G1 EG1 43 PD8 Panel data output 8 G0 EG0 Out 2mA~20mA PD 7 44 Out 2mA~20mA Panel data output 7 R7 R5 R3 ER7 ER5 45 Panel data output 6 PD<sub>6</sub> Out 2mA~20mA R6 R4 R2 ER6 ER4 46 R3 PD 5 Out 2mA~20mA Panel data output 5 R5 R1 ER5 ER3 47 PD 4 Panel data output 4 R4 R2 R0 ER2 Out 2mA~20mA ER4

| IOTE: Drive cu | urrent of the | panel out  | put pins are progr       | ammable                                                            |                       |           |             |                 |         |

|----------------|---------------|------------|--------------------------|--------------------------------------------------------------------|-----------------------|-----------|-------------|-----------------|---------|

| Pin No.        | Name          | In/<br>Out | Output Drive Description |                                                                    | TFT (one pixel/clock) |           |             | (two<br>/clock) |         |

|                |               |            | @ 10pF                   |                                                                    | 8 bit 6 bit 4 bit     |           | 4 bit       | 8 bit           | 6 bit   |

| 48             | PD 3          | Out        | 2mA~20mA                 | Panel data output 3                                                | R3                    | R1        |             | ER3             | ER1     |

| 49             | PD2           | Out        | 2mA~20mA                 | Panel data output 2                                                | R2                    | R0        |             | ER2             | ER0     |

| 50             | PD1           | Out        | 2mA~20mA                 | Panel data output 1                                                | R1                    |           |             | ER1             |         |

| 51             | PD0           | Out        | 2mA~20mA                 | Panel data output 0                                                | R0                    |           | ER0         |                 |         |

| 24             | PDE           | Out        | 2mA~20Ma                 | Panel Display Enable signal, active when flat panel data is valid. |                       |           |             |                 |         |

| 53             | PHS           | Out        | 2mA~20mA                 | This output provides the panel line clock signal.                  |                       |           |             |                 |         |

| 52             | PVS           | Out        | 2mA~20mA                 | This output provide the panel frame start signal.                  |                       |           |             |                 |         |

| 25             | PCLK          | Out        | 2mA~20mA                 | This output drives the flat panel shift clock.                     |                       |           |             |                 |         |

| 55             | PPWR          | Out        | 8 mA                     | This output controls the power to a flat panel.                    |                       |           |             |                 |         |

| 54             | PBIAS         | Out        | 8 mA                     | This output turns on/off t                                         | he panel b            | ias power | or controls | panel bac       | klight. |

## **Table 5: Pin-Scan Test Pins**

| Pin No. | Name    | In/Out | 5V Tolerant Input? | Description        |

|---------|---------|--------|--------------------|--------------------|

| 112     | STI_TM1 | In     | 5V tolerant        | Internal test pin. |

| 113     | STI_TM2 | In     | 5V tolerant        | Internal test pin. |

## **Table 6: Power and Ground Pins**

| Pin No. | Name  | Description                                                |

|---------|-------|------------------------------------------------------------|

| 14      | RVDD1 | Pad Ring VDD. Bypass with a 0.1 uF capacitor to RVSS pins. |

| 28      | RVDD2 | Pad Ring VDD. Bypass with a 0.1 uF capacitor to RVSS pins. |

| 41      | RVDD3 | Pad Ring VDD. Bypass with a 0.1 uF capacitor to RVSS pins. |

| 56      | RVDD4 | Pad Ring VDD. Bypass with a 0.1 uF capacitor to RVSS pins. |

| 118     | RVDD5 | Pad Ring VDD. Bypass with a 0.1 uF capacitor to RVSS pins. |

| 3       | RVDD6 | Pad Ring VDD. Bypass with a 0.1 uF capacitor to RVSS pins. |

| 15      | RVSS1 | Pad Ring VSS. Connect directly to ground plane.            |

| 29      | RVSS2 | Pad Ring VSS. Connect directly to ground plane.            |

| 42      | RVSS3 | Pad Ring VSS. Connect directly to ground plane.            |

| 57      | RVSS4 | Pad Ring VSS. Connect directly to ground plane.            |

| 117     | RVSS5 | Pad Ring VSS. Connect directly to ground plane.            |

| 4       | RVSS6 | Pad Ring VSS. Connect directly to ground plane.            |

| 18      | CVDD1 | Core VDD. Bypass with a 0.1 uF capacitor to CVSS pins.     |

| 40      | CVDD2 | Core VDD. Bypass with a 0.1 uF capacitor to CVSS pins.     |

| 59      | CVDD3 | Core VDD. Bypass with a 0.1 uF capacitor to CVSS pins.     |

| 119     | CVDD4 | Core VDD. Bypass with a 0.1 uF capacitor to CVSS pins.     |

| 19      | CVSS1 | Core VSS. Connect directly to ground plane.                |

| 39      | CVSS2 | Core VSS. Connect directly to ground plane.                |

| 58      | CVSS3 | Core VSS. Connect directly to ground plane.                |

| 120     | CVSS4 | Core VSS. Connect directly to ground plane.                |

## 4. OPERATING MODES

The Source Clock (SCLK) and the Destination Clock (DCLK) are defined as follows:

- The Source Clock is the pixel clock encoded in the DVI channel. It is the pixel clock of data coming from the source.

- The Destination Clock is the timing clock for panel data at the one pixel per clock rate. The actual clock to the panel (PCLK) may be one-half that frequency for double-pixel panel data formats. When its frequency differs from that of the Source Clock, the Destination Clock is generated by the Clock Generation Block.

There are six display modes: Native, Slow DCLK, Expansion, Downscaling, Source Stand Alone, and Destination Stand Alone.

Each mode is unique in terms of:

- Input video resolution vs. panel resolution

- Source Clock frequency / Panel Clock frequency ratio

- Source Hsync frequency / Panel Hsync frequency ratio

- Data source (video input, panel background color, on-chip pattern generator).

#### 4.1 Native Mode

Destination clock frequency = Source clock frequency

Panel Hsync frequency = Input Hsync frequency

Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is the same as the panel resolution and the input data clock frequency is within the panel clock frequency specification of a panel being used.

## 4.2 Slow DCLK Mode

Destination clock frequency < Source clock frequency

Panel Hsync frequency = Input Hsync frequency

Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is the same as the panel resolution, but the input data clock frequency exceeds the panel clock frequency specification of a panel being used. The panel clock is scaled to the Source clock, and the internal data buffers are used to spread the timing of the input data by making use of the large blanking period to extend the panel horizontal display time.

## 4.3 Expansion Mode

Destination clock frequency > Source clock frequency

Panel Hsync frequency > Input Hsync frequency

Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is less than the panel resolution. The panel clock (at a higher frequency than the source clock) is scaled and locked to the source clock. The input data is expanded.

## 4.4 Downscaling Mode

Destination clock frequency > Source clock frequency

Panel Hsync frequency < Input Hsync frequency

Panel Vsync frequency = Input Vsync frequency

This mode is used when the input resolution is greater than the panel resolution, and is used to provide enough of a display to enable the user to recover to a supported resolution. The input clock is operated at a frequency less than that of the input pixel rate (under-sampled horizontally) and the expander function is used to drop input lines. Expansion interpolation is not provided and must be off.

## 4.5 Source Stand Alone Mode

Destination clock = SCLK

Panel Hsync frequency = SCLK frequency / (Source Htotal register value)

Panel Vsync frequency = SCLK frequency / (Source Htotal register value \* Source Vtotal register value)

This mode is used to display the Pattern Generator data. This mode may be useful for testing an LCD panel on the manufacturing line (color temperature calibration, etc.).

### 4.6 Destination Stand Alone Mode

Destination clock = DCLK in open loop (not locked)

Panel Hsync frequency = DCLK frequency / (Destination Htotal register value)

Panel Vsync frequency = DCLK frequency / (Destination Htotal register value \* Destination Vtotal register value)

This mode is used when the input is changing or not available. The OSD may still be used as in all other display modes, and stable panel timing signals are produced. This mode may be automatically set when the gm3020-NH/gm3020-H detects input timing changes that could cause out-of-spec operation of the panel. This mode can also be used with the internal static patterns for manufacturing line burn-in testing.

## 4.7 Input Video Mode Support

The gm3020-NH/gm3020-H can support various standard VGA / VESA / Macintosh display modes, depending on the LCD panel specifications. By default, all data input is expanded to full-panel screen resolution. ModeCALC.EXE, an application running under DOS / Microsoft Windows, is available from Genesis Microchip. ModeCALC.EXE calculates and displays the mode supported based on user-supplied panel parameters.

October 2001 -12- C3020-DAT-01F

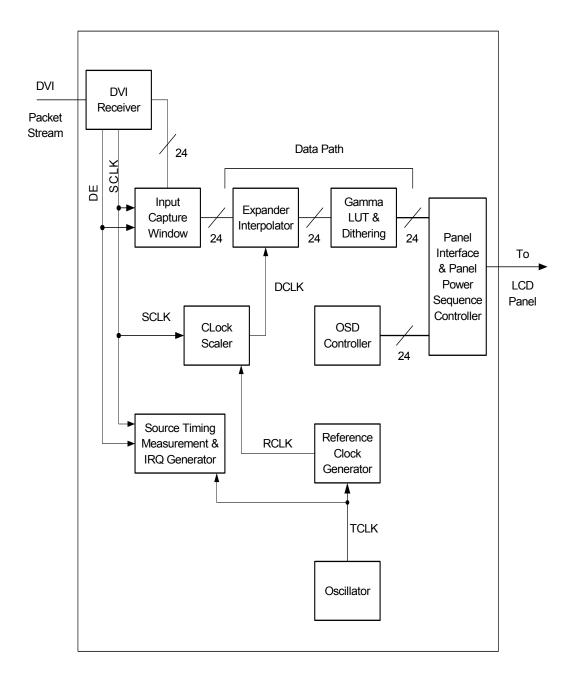

## 5. FUNCTIONAL BLOCK DESCRIPTION

The figure below shows a high-level block diagram of the gm3020-NH/gm3020-H chip.

Figure 3: gm3020-NH/gm3020-H Block Diagram

## 5.1 Ultra-Reliable DVI™ Receiver Block

The Ultra-Reliable DVI™ receiver block of the gm3020-NH/gm3020-H is compliant with DVI 1.0 specifications. It supports an input clock frequency ranging from 20 MHz - 112 MHz. The typical input clock frequency used would be up to 79MHz (XGA 75Hz).

The DE PLL re-generates an internal DE (data-enable) signal from the input DE to ensure that periodic occurrences of a DVI 1.0-induced glitch do not cause the firmware to generate unwanted timing change events.

Table 7 summarizes the characteristics of the four Receiver Pair inputs:

MIN **TYP** MAX **NOTE DC** Characteristics Differential Input Voltage 150mV 1200mV Input Common Mode Voltage AVDD-300mV AVDD-37mV Behavior when Transmitter Disable AVDD-10mV AVDD+10mV **AC Characteristics** Input clock frequency 20 MHz 112 MHz Input differential sensitivity (Peak-to-150mV peak) Max differential input (peak-to-peak) 1560 mV Allowable Intra-Pair skew at Receiver 360 ps Input clock = 112 MHzAllowable Inter-Pair skew at Receiver 5.4 ns Input clock = 112 MHzWorst case differential input clock 270 ps Input clock = 112 MHzjitter tolerance

**Table 7: Receiver Characteristics**

Through register programming, the receiver unit may be placed in three states:

- Active: The receiver block is fully on and running.

- Standby: Only the RXC channel remains active. Data and other control signals do not get decoded.

- **Off:** The receiver block is powered down.

Input clock frequency (or loss of the input clock) may be detected in active mode or in standby mode. The input DE status is detected only in active mode.

The CTL3:0 signals from the DVI channel can be output from pins by programming the EXT\_OSD\_MUX\_CONTROL register.

The internal static pattern can be displayed only if a source clock is present. The source clock may be supplied through pin pair RXC± of the DVI link, or the test bus. (Configured through register 0xF0.)

## 5.2 Input Capture/Timing Measurement Blocks

Decoded input data and timing signals are sent from the Ultra-Reliable DVI<sup>TM</sup> receiver block to the input capture block and to the input timing measurement block. Among the input timing signals, Hsync input and Vsync input from the DVI receiver block are ignored. Only the DE input is used. The Hsync and Vsync signals are synthesized from the DE input and sent to the input capture/timing measurement blocks.

#### 5.2.1. Input Capture Block

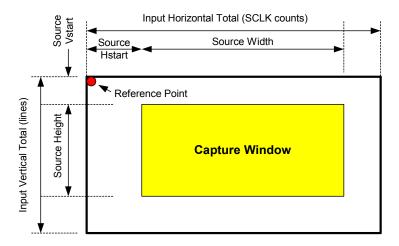

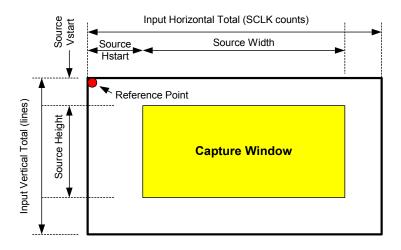

Figure 4 below shows how the window is defined. In the horizontal direction, it is defined in SCLK (input clock from the receiver block) counts and in the vertical direction, in line counts.

All parameters in Figure 4 beginning with "Source" are programmed into the gm3020-NH/gm3020-H registers. Note that horizontal / vertical totals are solely determined by the video input. In other words, the horizontal / vertical counters are cleared by the synthesized Hsync/Vsync signals. Hence, they have the prefix "Input" instead of "Source."

The reference points are as follows:

The first pixel of a line: the pixel whose SCLK rising edge sees the transition of the HSYNC polarity from low to high.

The first line of a frame: the line whose HSYNC rising edge sees the transition of the VSYNC polarity from low to high.

Note that above Hsync/Vsync signals are synthesized from the DE input from the receiver block.

**Figure 4: Capture Window**

## 5.2.2. Input Timing Measurement Block

The input timing measurement block consists of the source timing measurement (STM) block and interrupt request (IRQ) controller.

Input timing parameters are measured by the STM block and stored in the registers. Some input conditions will generate an IRQ to an external microcontroller. The IRQ-generating conditions are programmable.

#### 5.2.2.1. Source timing measurement (STM) block

The table below lists all the parameters that may be read in the source timing measurement (STM) registers of gm3020-NH/gm3020-H.

**Table 8: Input Timing Parameters Measured by the STM Block**

| Parameter                                              | Unit | Updated at:                  |

|--------------------------------------------------------|------|------------------------------|

| Unstable vertical timing                               | N/A  | Every frame                  |

| Current v-period different from the last one           |      | (This flag can be disabled.) |

| Unstable horizontal timing                             | N/A  | Every line                   |

| (Current h-period different from the last one)         |      | (This flag can be disabled.) |

| Unstable SCLK                                          | N/A  | Every 256 TCLK periods       |

|                                                        |      | (This flag can be disabled.) |

| Unstable DE(Current DE width/height different from the | N/A  | Every line horizontally,     |

| last one)                                              |      | Every frame vertically       |

| Synthesized Hsync missing                              | N/A  | Every 4096 TCLK periods      |

| Parameter                                    | Unit  | Updated at: |

|----------------------------------------------|-------|-------------|

| Synthesized Vsync missing                    | N/A   | Every 80 ms |

| Horizontal Period                            | SCLKs | Every Frame |

| (period between two synthesized Hsync)       |       |             |

| Horizontal Display Start (DE rising edge)    | SCLKs | Every Frame |

| Horizontal Display End (DE falling edge)     | SCLKs | Every Frame |

| Vertical Period                              | Lines | Every Frame |

| (period between two synthesized Vsync)       |       |             |

| Vertical Display Start (First DE of a frame) | Lines | Every Frame |

| Vertical Display End (Last DE of a frame)    | Lines | Every Frame |

#### 5.2.2.2. IRQ controller

Some input timing conditions can cause the gm3020-NH/gm3020-H chip to generate an IRQ. The IRQ-generation conditions are programmable as follows:

**Table 9: IRQ-Generation Condition**

| IRQ Event     | Remark                                                |  |

|---------------|-------------------------------------------------------|--|

| Timing Event  | Each leading edge of synthesized Vsync input          |  |

| Timing Change | Any of the following timing changes:                  |  |

|               | Unstable SCLK ( SCLK delta threshold is programmable) |  |

|               | 2. Unstable horizontal timing                         |  |

|               | 3. Unstable vertical timing                           |  |

|               | 4. Loss of synthesized Hsync or Vsync                 |  |

|               | 5. Loss of SCLK                                       |  |

Reading the IRQ status flags will not affect the STM registers.

Note that if a new IRQ event occurs while the IRQ status register is being read, the IRQ signal will become inactive for a minimum of one TCLK period and before being re-activated. The polarity of the IRQ signal is programmable.

The gm3020-NH/gm3020-H may be programmed to automatically switch to the Destination Standalone operation upon unstable input timing detection without intervention by the firmware.

## 5.3 Clock Scaling Block

The clock scaling block of the gm3020-NH/gm3020-H chip scales the input clock from the Ultra-Reliable DVI<sup>TM</sup> receiver block (SCLK) to the output clock (DCLK). The data path, OSD controller, and the panel interface run in synchronization with DCLK.

The clock scaling is performed so that the output frame period is equal to the input frame period.

Input frame period = SCLK period \* input horizontal total \* input vertical total

Output frame period = DCLK period \* output horizontal total \* output vertical total

Thus, the ratio of SCLK period to DCLK period is:

SCLK period/DCLK period = output horz. total \* output vert. total / (input horz. total \* input vert. total)

The following block diagram shows how the gm3020-NH/gm3020-H generates the DCLK from SCLK and TCLK input. The TCLK input comes from an external oscillator.

October 2001 -18- C3020-DAT-01F

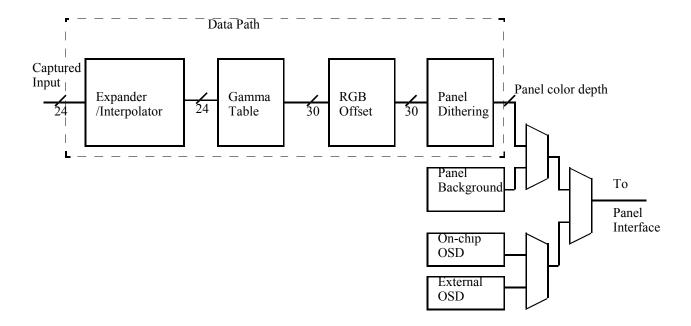

## 5.4 Data Path

The gm3020-NH/gm3020-H data path is shown in the following diagram:

Figure 6: Data Path

## 5.5 Gamma Table

This Gamma Lookup Table takes the 8-bit R, G, and B data from the DVI receiver block and produces a 10-bit output. This table can be programmed to adjust color temperature/contrast or to reduce the difference of color characteristics of various LCD TFT panels.

#### 5.5.1. Expander Interpolator

For the best display quality when the source resolution is less than the panel resolution, the gm3020-NH/gm3020-H provides an advanced data interpolator. The calculation finds the best output value for the horizontally and vertically expanded output data. The expander block takes in the 8-bit output from the input capture block and produces an 8-bit output. The vertical and horizontal expansion amounts are independently programmable.

#### 5.5.2. RGB Offset

The RGB offsets provide a simple shift (positive or negative) for each of the three color channels. This may be used as a simple brightness adjustment within a limited range. The data is clamped to zero for negative offsets, and clamped to FFh for positive offsets. This adjustment is much faster than recalculating the gamma table, and may be used with in OSD user controls to provide a quick brightness adjust. An offset range of plus 127 to minus 127 is available.

Because the gamma table output is 10 bits per channel, two 0's are appended as the least significant bits of these 8-bit RGB offsets to produce 10-bit output for each channel.

#### 5.5.3. Panel Data Dither

For TFT panels that have fewer than eight bits for each R, G, B input, the gm3020-NH/gm3020-H provides a dither pattern to more smoothly shade colors on 4 and 6 bit panels. The dithering logic is identical to that of the gmZAN1 or gmZ4.

#### 5.5.4. Panel Background Color

This provides a solid background color for a border around any partial expansion display data, or for the Destination Stand Alone Mode. The background color is most often set to black.

October 2001 -20- C3020-DAT-01F

## 5.6 Panel Interface

The gm3020-NH/gm3020-H chip interfaces directly with all of today's commonly used TFT LCD flat panels with 640x480, 800x600 and 1024x768 resolutions. The resolution and the aspect ratio are NOT limited to specific values.

All aspects of the gm3020-NH/gm3020-H panel interface are programmable. For horizontal parameters, Horizontal Display Enable Start, Horizontal Display Enable End, Horizontal Sync Start and Horizontal Sync End are programmable. Vertical Display Enable Start, Vertical Display Enable End, Vertical Sync Start and Vertical Sync Start are also fully programmable.

In order to maximize panel data setup and hold time, the panel clock (PCLK) output skew is programmable. In addition, the current drive strength of the panel interface pins are programmable.

For panel backlight brightness control, there are two PWM outputs available (as part of the GPIO bus). One PWM output has a fixed 50% duty cycle, while the second PWM output has programmable duty cycle.

The following sections describe these functions in detail.

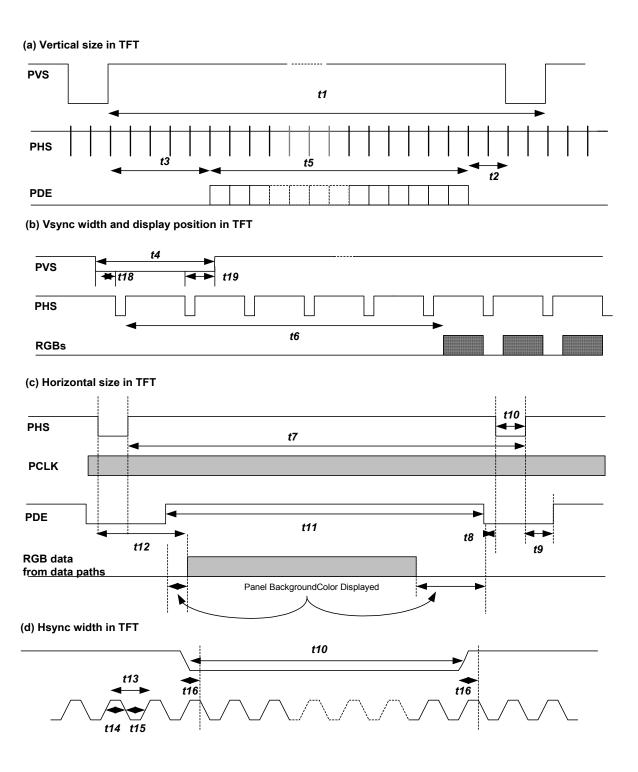

## 5.6.1. TFT Panel Interface Timing Specification

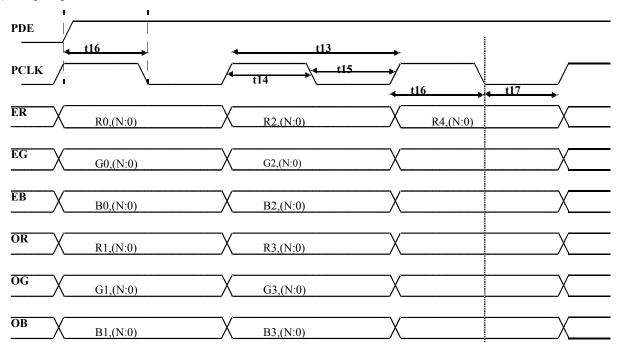

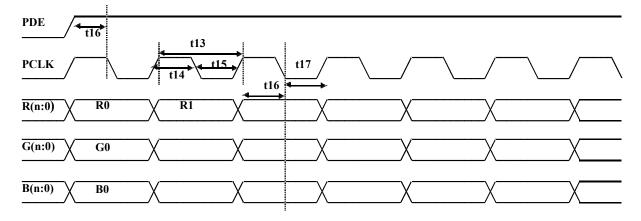

The TFT panel interface timing parameters are listed in the table below. Refer to the timing diagrams in Figure 7 (one pixel per clock) and Figure 8 for the timing parameter definitions.

Table 10: gm3020-NH/gm3020-H TFT Panel Interface Timing

Note: [] figures are for two pixels/clock mode

| Si  | gnal Name              |     | Min | Typical      | Max  | Unit *1 |

|-----|------------------------|-----|-----|--------------|------|---------|

| PVS | Period                 | t1  | 0   |              | 2048 | Lines   |

|     |                        |     |     | 16.67        | -    | ms      |

|     | Frequency              |     |     | 60           | -    | Hz      |

|     | Front porch            | t2  | 0   |              | 2048 | lines   |

|     | Back porch             | t3  | 0   |              | 2048 | lines   |

|     | Pulse width            | t4  | 0   |              | 2048 | lines   |

|     | PdispE                 | t5  | 0   | Panel height | 2048 | lines   |

|     | Disp. Start<br>From VS | t6  | 0   |              | 2048 | lines   |

|     | PVS set-up to PHS      | t18 | 1   |              | 2048 | pclk    |

|     | PVS hold from<br>PHS   | t19 | 1   |              | 2048 | pclk    |

October 2001 -21- C3020-DAT-01F

| PHS     | Period                 | t7  | 0                        |                                 | 2048 [1024]              | pclk       |

|---------|------------------------|-----|--------------------------|---------------------------------|--------------------------|------------|

| 1110    | Front porch            | t8  | 0                        |                                 | 2048                     | pclk       |

|         | Back porch             | t9  | 0                        |                                 | 2048                     | pclk       |

|         | Pulse width            | t10 | 0                        |                                 | 2048                     | pclk       |

|         | PdispE                 | t11 | 0                        | Panel width                     | 2048 [1024]              | pclk       |

|         | Disp. Start<br>from HS | t12 | 0                        | T dife! Width                   | 2048                     | pclk       |

| PCLK *4 | Frequency              | t13 |                          |                                 | 112 [56]                 | MHz        |

|         | Clock (H) *2           | t14 | DCLK/2-3<br>[DCLK – 3]   |                                 | DCLK/2 - 2<br>[DCLK - 2] | ns         |

|         | Clock (L) *2           | t15 | DCLK/2-3<br>[DCLK – 3]   |                                 | DCLK/2 - 2<br>[DCLK - 2] | ns         |

|         | Туре                   |     |                          | One pels/clock [two pels/clock] | -                        |            |

| Data    | Set up *3              | t16 | DCLK/2 - 5<br>[DCLK – 5] |                                 | DCLK/2 - 2<br>[DCLK - 2] |            |

|         | Hold *3                | t17 | DCLK/2 - 5<br>[DCLK – 5] |                                 | DCLK/2 - 2<br>[DCLK - 2] |            |

|         | Width                  |     | 12 bits<br>[24 bits]     | 18 bits<br>[36 bits]            | 24 bits<br>[48 bits]     | Bits/pixel |

#### NOTES:

- 1: The pclk is the panel shift clock.

- 2: The DCLK (Destination Clock) period. is equal to:

- pclk period in one pixel/clock mode,

- twice the pclk period in two pixels/clock mode.

The drive current of the panel interface signals is programmable as shown in Table 12. Output current is programmable from 2 mA to 20 mA in increments of 2 mA. Drive strength should be programmed to match the load presented by the cable and input of the panel.

3: The same setup/hold time specification to the pclk also applies to the PHS and the PDE signals. The setup time (t16) and the hold time (t17) listed in this table are for the case in which no clock-to-data skew is added: The PVS/PHS/PDE/ PData signals are asserted on the rising edge of the PCLK.

Note that the polarity of the PCLK and its skew are programmable. Clock to Data skew can be adjusted in sixteen 800-ps increments. In combination with the Pclk polarity inversion, the clock-to-data phase can be adjusted in total of 31 steps.

4: The polarity of the PCLK is programmable.

Figure 7: TFT Panel Interface Timing (one pixel per clock)

#### (a) Two pixel per clock mode in TFT

#### (b) One pixel per clock mode in TFT

Figure 8: TFT Panel Interface Data Latch Timing

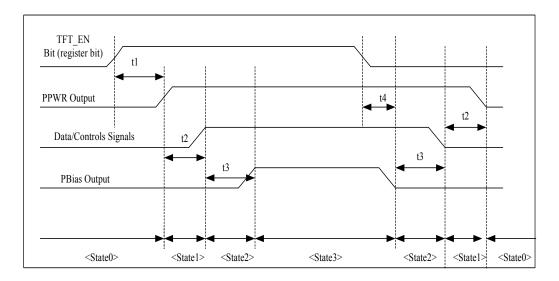

## 5.6.2. TFT LCD Power Sequencer

LCD panels require logic power, panel bias power, and control signals to be sequenced in a specific order. Otherwise, a severe damage may occur and disable the panel permanently. The gm3020-NH/gm3020-H has a built-in power sequencer, which should prevent this kind of damage.

October 2001 -24- C3020-DAT-01F

The Power Sequencer controls the power up/down sequences for LCD panels within the four states described below. Also see the timing diagram in Table 11.

#### State 0 (Power Off)

The PBIAS signal and the PPWR signal are low (inactive). The panel controls and data are forced low. This state is both the beginning and final state in power sequence.

#### State 1 (Power On)

Intermediate step 1. The PPWR is high (active), the PBIAS is low (inactive), and the panel interface is forced low (inactive).

#### **State 2 (Panel Drive Enabled)**

Intermediate step 2. The PPWR is high (active), the PBIAS is low (inactive), and the panel control and data signals are active.

#### **State 3 (Panel Fully Active)**

Final step in power up sequence with PPWR and PBIAS high (active), and the panel interface active. gm3020-NH/gm3020-H power manager is kept in this state until the internal TFT\_Enable signal is disabled and State 2 is entered.

The power sequence state can be read from a gm3020-NH/gm3020-H status register.

All of the four timing parameters ( $t1 \sim t4$ ) in Table 11 are independently programmable from one step to eight steps in length.

One-step length is TCLK \*  $2^{19}$  or about 10 ms when TCLK is 50 MHz.

October 2001 -25- C3020-DAT-01F

**Table 11: Panel Power Sequence Timing Definition**

| Timing Symbol | Description                                                                                  |

|---------------|----------------------------------------------------------------------------------------------|

| t1            | TFT_EN bit set to 1 PPWR active                                                              |

| t2            | PPWR active to Signals active (power up) or Signals inactive to PPWR inactive (power down)   |

| t3            | Signals active to PBIAS active (power up) or PBIAS inactive to Signals inactive (power down) |

| t4            | TFT_EN bit cleared to 0 to PBIAS inactive                                                    |

## 5.6.3. Panel Interface Drive Strength

The gm3020-NH/gm3020-H has programmable output pads for the TFT panel interface. Three groups of panel interface pads (panel clock, data, and control) are independently controlled by programming registers.

**Table 12: Panel Interface Pad Drive Strength**

| Value (4<br>bits) | Drive Strength                     |

|-------------------|------------------------------------|

| 0                 | Outputs are in tri-state condition |

| 1                 | 2 mA                               |

| 2                 | 4 mA                               |

| 3, 4              | 6 mA                               |

| 5, 8              | 8 mA                               |

| 6, 9              | 10 mA                              |

| 7, 10             | 12 mA                              |

| 11, 12            | 14 mA                              |

| 13                | 16 mA                              |

| 14                | 18 mA                              |

| 15                | 20 mA                              |

October 2001 -26- C3020-DAT-01F

## 5.7 Host Interface

The host interface uses a serial protocol consisting of four signals as described in this section.

## 5.7.1. Host interface pin connection

Table 13: gm3020-NH/gm3020-H Host Interface

| Signal Name | Description                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HFS         | Host Frame Sync. that enable the serial communication when driven high by the microcontroller. The gm3020-NH/gm3020-H chip has an internal pull-down resistor on chip.  Thus, the default state of this signal is low. |

| HCLK        | Serial clock driven by the microcontroller in the write operation. May be connected to an external pull-up resistor.                                                                                                   |

| HDATA       | Address is sent by the microcontroller to the gm3020-NH/gm3020-H.  Data is driven: by the microcontroller in the write operation. by the gm3020-NH/gm3020-H in the read operation.                                     |

| IRQ         | IRQ pin driven by the gm3020-NH/gm3020-H chip. The polarity is programmable.                                                                                                                                           |

| RESETn      | Sets the chip to a known state when pulled low.                                                                                                                                                                        |

The gm3020-NH/gm3020-H has an on-chip pull-down resistor in the HFS input pad. The signal stays low until driven high by the microcontroller.

RESETn must be low for at least 100 ns after the CVDD has become stable (between +3.15V and +3.45V) to reset the chip to a known state.

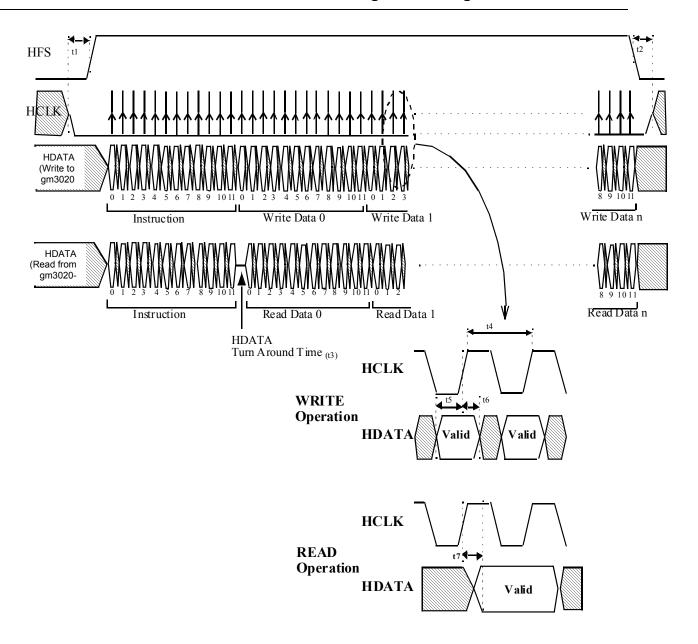

## 5.7.2. gm3020-NH/gm3020-H Serial Communication Protocol

During serial communication between the microcontroller and the gm3020-NH/gm3020-H, the microcontroller always acts as an initiator while the gm3020-NH/gm3020-H is always the target. The following timing diagram describes the protocol of the serial channel

Figure 9: Serial Communication Timing Diagram

Table 14 summarizes the serial channel specification of the gm3020-NH/gm3020-H. Refer to Figure 9 for the timing parameter definitions.

Table 14: gm3020-NH/gm3020-H Serial Channel Specification

| Parameter                                | Min.         | Тур.    | Max.         |

|------------------------------------------|--------------|---------|--------------|

| Word size (Instruction and Data)         |              | 12 bits |              |

| HCLK low to HFS high (t1)                | 100 ns       |         |              |

| HFS low to HCLK inactive (t2)            | 100 ns       |         |              |

| HDATA Write to Read Turnaround Time (t3) | 1 HCLK cycle |         | 1 HCLK cycle |

| HCLK cycle (t4)                          | 100 ns       |         |              |

| Data in setup time (t5)                  | 25 ns        |         |              |

| Data in hold time (t6)                   | 25 ns        |         |              |

| Data out valid (t7)                      | 5 ns         |         | 10 ns        |

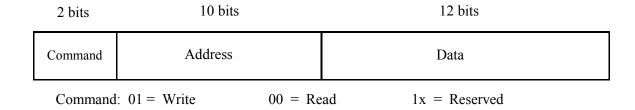

The microcontroller (Initiator) issues an instruction lasting 12 HCLKs. After the last bit of the command is transferred to the gm3020-NH/gm3020-H on the 12th clock, the microcontroller must stop driving data before the next rising edge of HCLK, at which point the gm3020-NH/gm3020-H will start driving data if it is a read operation. At the 13th rising edge of HCLK, the gm3020-NH/gm3020-H will begin driving data

The data order for address, read data or write data is:

- D11 on the first clock

- D0 on the twelfth clock

Figure 10: Serial Host Interface Data Transfer Format

## 5.8 OSD (On-Screen Display) Control

The gm3020-NH/gm3020-H chip has a built-in OSD (On-Screen Display) controller with an integrated block of font ROM. The built-in OSD controller can display an OSD window of up to 32 x 16 characters.

The gm3020-H also supports an external OSD controller as an option for monitor vendors to maintain a familiar user interface.

Regardless of whether the built-in OSD or an external OSD is enabled, the window size is not affected by the expansion operation.

## 5.8.1. **On-Chip OSD**

Features of the gm3020-NH/gm3020-H's on-chip OSD controller include: character blinking, OSD window shadowing, OSD window bordering and background transparency. In addition, the OSD window can be pixel or line doubled independently.

There are 256 built-in ROM fonts. The size of each font is 12 pixels x 16 lines.

The on-chip, 512-byte OSD SRAM is used as a display buffer. This display buffer is contiguously accessed through the 0x100-0x1ff register range of the gm3020-NH/gm3020-H. One bit in the OSD Control register selects one of two segments accessed through the 0x100-0x1ff window.

October 2001 -30- C3020-DAT-01F

**Table 15: On-chip Character Code**

| Blinking    | Foreground/              | Font Select                      |

|-------------|--------------------------|----------------------------------|

| Enable      | <b>Background Colors</b> |                                  |

| Bit 10      | Bit 9 – Bit 8            | Bit 7 – B 0                      |

| 0 = Disable | 00 = F/Bcolor 0          | Selects a font from 256-font ROM |

| 1 = Enable  | 01 = F/Bcolor 1          |                                  |

|             | 10 = F/Bcolor 2          |                                  |

|             | 11 = F/Bcolor 3          |                                  |

The blink rate is based on either a 32 or 64 frame cycle and the duty cycle may be selected as 25/75, 50/50 or 75/25.

The on-chip OSD colors are controlled by the foreground or background color selected. The foreground and background colors are stored in registers. Each location contains 12 bits that define the upper 4 bits of each 8 bit Red, Green and Blue color component. If any of the upper 4 RGB bits are set to 1, then the corresponding lower four RGB bits are all set to 1, otherwise the lower four RGB bits are set to 0.

**Table 16: On-chip OSD Color Control**

| Register<br>Index | Color Selected                                       |

|-------------------|------------------------------------------------------|

| 0xBA              | Foreground 0 <r7:4><g7:4><b7:4></b7:4></g7:4></r7:4> |

|                   | (Bits 11:8 = R7:4, Bits 7:4 = G7:4, Bits 3:0 = B7:4) |

| 0xBB              | Foreground 1 <r7:4><g7:4><b7:4></b7:4></g7:4></r7:4> |

| 0xBC              | Foreground 2 <r7:4><g7:4><b7:4></b7:4></g7:4></r7:4> |

| 0xBD              | Foreground 3 <r7:4><g7:4><b7:4></b7:4></g7:4></r7:4> |

| 0xBE              | Background 0 <r7:4><g7:4><b7:4></b7:4></g7:4></r7:4> |

| 0xBF              | Background 1 <r7:4><g7:4><b7:4></b7:4></g7:4></r7:4> |

| 0xC0              | Background 2 <r7:4><g7:4><b7:4></b7:4></g7:4></r7:4> |

| 0xC1              | Background 3 <r7:4><g7:4><b7:4></b7:4></g7:4></r7:4> |

Foreground / background colors may be independently made transparent via register 0xB9 bits7:0.

October 2001 -31- C3020-DAT-01F

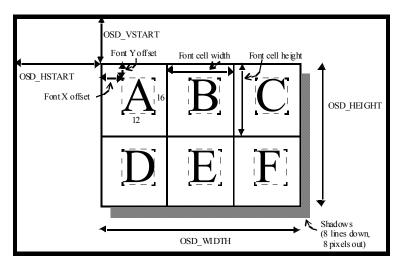

OSD HSTART: Starting pixel number 0-2047

OSD VSTART: Starting line number 0-2047

Font X offset: Location of left pixel of font inside char cell

Font Y offset: Location of top line of font inside char cell

0-63

Font Cell Width: Cell width in pixels 3-66

Font Cell Height: Cell height in lines 2-65

OSD Width: OSD Window Width in char cells 1-64

OSD Height: OSD Window Height in char cells 1-64

Figure 11: On-Chip OSD Window Location

When the OSD window shadow is enabled, a shadow region the same size as the OSD, but shifted down and to the right by eight pixels/lines is shown. Data on the panel is at half intensity in the shadow region. OSD foreground and background colors will always appear on top of the shadow region but the transparent background color will be 'lost' in the shadow since it is also half intensity.

When the OSD window border is enabled, a 1, 2, 4 or 8 pixel/line wide border is drawn around the OSD window. In this case, the OSD vertical and horizontal start positions include the thickness of the border and the actual start of the character display is offset from the start position by the thickness of the border. If the OSD window border is enabled, the OSD window shadow must be disabled. Only one may be selected at a time.

If the Cell Height or Cell Width is larger than the  $12 \times 16$  font, the extra pixels and lines in each cell will display as the background color of that cell's character code. If the Cell Height or Cell Width is smaller than the  $12 \times 16$  font, the cell will clip the right most pixels and the bottom lines of the font.

Following page:

Figure 12: gm3020-NH/gm3020-H On-chip Fonts in ROM

October 2001 -32- C3020-DAT-01F

| Index | Font         | Index | Font | Index | Font     | Index | Font        | Index | Font           | Index | Font             |

|-------|--------------|-------|------|-------|----------|-------|-------------|-------|----------------|-------|------------------|

| 00    | X            | 2C    | •    | 58    | ×        | 84    | ŧ           | B0    | 垂              | DC    | Ω                |

| 01    | ⊁            | 2D    | _    | 59    | Υ        | 85    | る           | B1    | 直              | DD    | Œ                |

| 02    | •            | 2E    |      | 5A    | Z        | 86    | h           | B2    | 画              | DE    | Ø                |

| 03    | )            | 2F    | /    | 5B    | ወ        | 87    | ኛ<br>7      | В3    | 像              | DF    | Ø                |

| 04    | Œ            | 30    | 0    | 5C    | 他        | 88    | ア           | B4    | λ              | E0    | تa`a`a`ê`e`ê`i`î |

| 05    | Ð            | 31    | 1    | 5D    |          | 89    | オ           | B5    | 力              | E1    | à                |

| 06    | 終了           | 32    | 2    | 5E    | 2        | 8A    | ク           | B6    | 信号             | E2    | ä                |

| 07    | 7            | 33    | 3    | 5F    | •        | 8B    |             | B7    | 号              | E3    | â                |

| 08    | ಠ            | 34    | 4    | 60    | $\Theta$ | 8C    | サ           | B8    | 舞音言語           | E4    | é                |

| 09    | コ            | 35    | 5    | 61    | a        | 8D    | シ           | B9    | 音              | E5    | è                |

| 0A    | Ē            | 36    | 6    | 62    | b        | 8E    | ス           | BA    | 盲              | E6    | ë                |

| 0B    | ∄            | 37    | 7    | 63    | С        | 8F    | と           | BB    | 語              | E7    | ê                |

| 0C    | Œ            | 38    | 8    | 64    | d        | 90    | タ<br>テ      | BC    | В              | E8    | ï                |

| 0D    | <del>2</del> | 39    | 9    | 65    | е        | 91    |             | BD    | 本              | E9    | î                |

| 0E    | 36           | 3A    | :    | 66    | £        | 92    | <b> </b>    | BE    | 表              | EA    | ö                |

| 0F    | 28           | 3B    | •    | 67    | 9        | 93    | ナ           | BF    | 示              | EB    | ô                |

| 10    | [            | 3C    | <    | 68    | h        | 94    | フ           | C0    | 無<br>質<br>グ    | EC    | ù                |

| 11    |              | 3D    | =    | 69    | i        | 95    | マラ          | C1    | 筫              | ED    | ü                |

| 12    |              | 3E    | >    | 6A    | j        | 96    | ラ           | C2    |                | EE    | û<br>ñ           |

| 13    |              | 3F    | ?    | 6B    | k        | 97    | リ           | C3    | ル              | EF    |                  |

| 14    |              | 40    | 0    | 6C    | 1        | 98    |             | C4    | R <sub>G</sub> | F0    | Š                |

| 15    | ⊑            | 41    | Α    | 6D    | m        | 99    | ン           | C5    | вγ             | F1    | Å                |

| 16    |              | 42    | В    | 6E    | n        | 9A    | エ           | C6    | ⊕.             | F2    | QªÅÄÄÄÉÈËÏÎ      |

| 17    |              | 43    | С    | 6F    | 0        | 9B    | ツ           | C7    | ~              | F3    | Ä                |

| 18    | ] _          | 44    | D    | 70    | р        | 9C    | ∃.          | C8    | []<br> }<br> } | F4    | Â                |

| 19    | _ {i         | 45    | Ε    | 71    | q        | 9D    | Ħ           | C9    | 고              | F5    | É                |

| 1A    | <u>,</u>     | 46    | F    | 72    | r        | 9E    | ジ<br>ズ<br>デ | CA    | ģ              | F6    | È                |

| 1B    | 덱            | 47    | G    | 73    | s        | 9F    | ズ           | CB    |                | F7    | Ë                |

| 1C    | D            | 48    | Н    | 74    | t        | A0    | ヹ           | CC    | C              | F8    | Ï                |

| 1D    | 刘            | 49    | Ι    | 75    | u        | A1    | Ť           | CD    | 9              | F9    | Î                |

| 1E    | _(           | 4A    | J    | 76    | ~        | A2    | ポ           | CE    | 保              | FA    | Ö<br>Ü           |

| 1F    | 9            | 4B    | K    | 77    | W        | A3    | 明           | CF    | 存              | FB    | ũ                |

| 20    | TM           | 4C    | L    | 78    | ×        | A4    | 色           | D0    | カ              | FC    | Ñ                |

| 21    | TM<br>       | 4D    | М    | 79    | У        | A5    | 調           | D1    | _              | FD    | Ç                |

| 22    | -            | 4E    | N    | 7A    | Z        | A6    | 整<br>赤      | D2    | 直              | FE    | æ                |

| 23    | Q            | 4F    | 0    | 7B    | +        | A7    | 乔           | D3    | <u> </u>       | FF    | Æ                |

| 24    | 0            | 50    | P    | 7C    | ŧ        | A8    | 緑           | D4    | 遵              |       |                  |

| 25    | %            | 51    | Q    | 7D    | <b>→</b> | A9    | 青           | D5    | 量              |       |                  |

| 26    | <b>&amp;</b> | 52    | R    | 7E    | Ť        | AA    | 温           | D6    | Ҡ              |       |                  |

| 27    |              | 53    | S    | 7F    | <u> </u> | AB    | 度           | D7    | ځ              |       |                  |

| 28    | (            | 54    | T    | 80    | ₹<br>\$  | AC    | 位           | D8    | Ķ              |       |                  |

| 29    | )            | 55    | U    | 81    | È        | AD    | 置           | D9    | 選量択さいで夢        |       |                  |

| 2A    | ®            | 56    | Y    | 82    | با       | AE    | 水           | DA    | <u>.</u>       |       |                  |

| 2B    | +            | 57    | W    | 83    | ť        | AF    | Ŧ           | DB    | 3              |       |                  |

### 5.8.2. External OSD Support (gm3020-H only)

The gm3020-H supports an external OSD controller for monitor vendors who wish to maintain a specific user interface, or its look and feel. Only those OSD controllers that are developed for a flat-panel monitor application and have a pixel-clock input pin are supported.

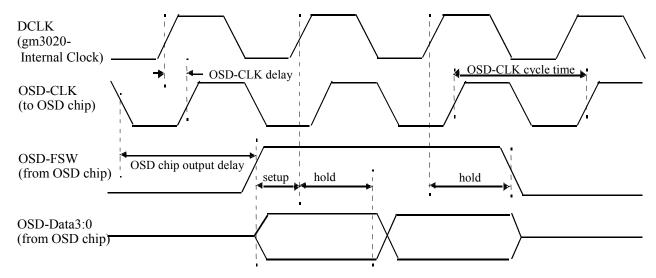

An external OSD controller is connected to the gm3020-H chip as shown in Table 17.

Table 17: Pin Connection Between the gm3020-H and an External OSD controller

| Pin Name<br>(in/out)    | External OSD<br>Controller Pin<br>(in/out) | Polarity     | Position                                                                                                                                                       |

|-------------------------|--------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSD-HREF<br>(output)    | Hsync (input)                              | Programmable | Relative to left edge of panel. Leading edge of PDE.                                                                                                           |

| OSD-VREF<br>(output)    | Vsync (input)                              | Programmable | Relative to top edge of panel. Leading edge of first PDE after vertical blanking period.                                                                       |

| OSD-CLK (output)        | Pixel Clock (input)                        |              |                                                                                                                                                                |

| OSD-FSW<br>(input)      | OSD Window<br>Indicator (output)           | Programmable | Horizontal: M OSD-CLK cycles after the HREF for N pixels. Vertical: M' HREF pulses after the VREF for N' lines. (M, N, M', N' programmed to external OSD chip) |

| OSD-DATA [3:0] (inputs) | Intensity, R, G, and B (outputs)           |              |                                                                                                                                                                |