# Pocket-Size R30XX Embedded Computer

# Galileo-3

Preliminary April 95., Rev. 0

## **FEATURES**

- Small size 2.95" x 3.95"

- · Choice of high performance IDT CPUs

- R3041, R3051, R3052, R3071, R3081

- 16 33MHz operation

- 1MB DRAM

- Expandable to 4MBytes

- 1MB Flash memory

- 120ns access time, 5 V only

- Two high-speed serial channels

- Up to 19.2Kbaud via 85C30 controller

- Fully compatible IEEE 1284 parallel port

- ECP, EPP, Byte, Nibble, and Standard Centronics

- DMA support

- 100-pin Expansion Connector

- Demultiplexed address bus

- 16-bit I/O bus

- 6 programmable I/Os or interrupt pins

- Parallel port control

- Assorted CPU control signals

- High-performance 16-bit I/O bus

- 2 DMA channels

- Glueless interface to 80186 type peripherals

- Programmable timing

- 16-32 packing and 32-16 unpacking of data for CPU accesses

- PCMCIA Support

- Through 16-bit I/O expansion port

- 16-32 bit packing and 32-16 bit unpacking of data

- Big and little endian support

- Dedicated address space and registers

- Parallel Port

- Control signals for reading and writing from a 16-bit parallel port

- Interrupt Controller

- Up to 6 external interrupts through expansion connector

- General Purpose I/O

- Six programmable I/O pins

- 24-bit Timer/Counter

- Shipped with IDT's System Integration Manager (IDT/ sim<sup>TM</sup>) monitor software in Flash for development

- Ideal for evaluation, development, and production.

- Standard PC 5V power connector

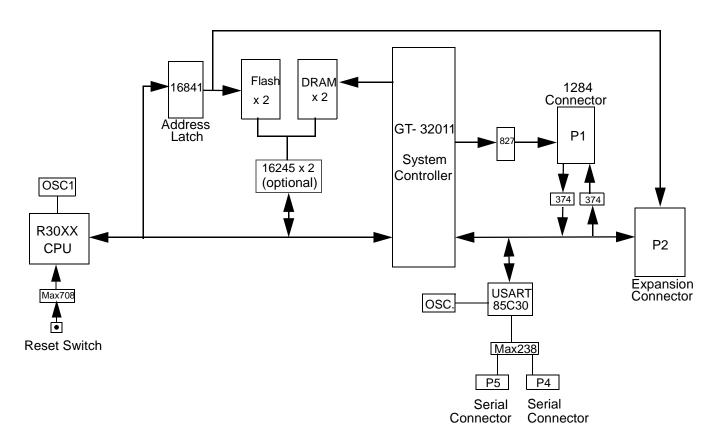

Galileo-3 Block Diagram

#### **OVERVIEW**

The Galileo-3 module is a powerful single board embedded computer in a very small size. The module includes a high-performance IDT 32-bit RISC microprocessor, Flash and DRAM memory for code and data, and external I/O interfaces. The external I/O interfaces include a 1284 compatible parallel interface, two serial interfaces, and an 80186-like 16-bit I/O bus for easy interface to peripherals.

#### **CPU**

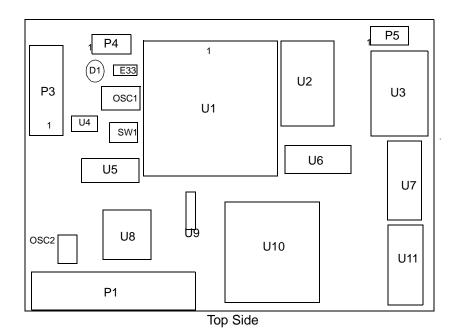

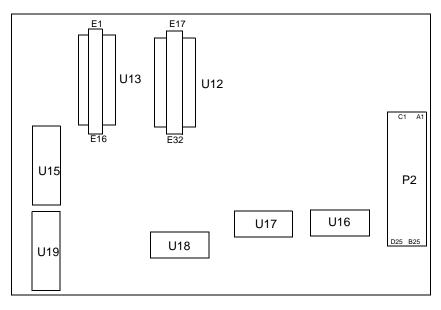

The CPU PLCC socket can accommodate any of the IDT 30XX family of CPUs. The CPU oscillator (OSC1) is socketed and can be populated with 33MHz to 66MHz oscillators for internal CPU frequencies of 16MHz to 33MHz, respectively. The board includes two 16-bit wide transceivers (FCT162245 - U12 and U13) for the R3051/R3052 processors. The transceivers can be removed when the R3041, R3071, and 3081 CPUs are used and the jumpers E1 to E32 should be assembled instead. The jumpers are 0603 type resistors 10ohms or less.

#### DRAM

The board is assembled with 1 MB of DRAM using two 256K x 16 components (U7 and U11). There is an option to assemble the board with 4 MB of DRAM by removing U7 and U11 and assembling U15 and U19 with two 1M x 16 DRAMs instead. 1K refresh mode is used for both DRAM options.

#### **Flash**

The devices used are 5V-only flash memories (type 29F400T, 256Kx16) from AMD. These have embedded Erase and Program algorithms and the data is protected from erroneous software or powerup write by an internal write protect mechanism. AMD's data sheet of this device should be carefully read before programming is attempted. Galileo-3 uses two devices in the following way: U3 is connected to D[15:0]; U2 is connected to D[31:16]; The write signal is connected in parallel to both U2 and U3, so that only 32-bit writes are supported.

The Read/Busy flash output pin can be connected to PIO[0] in the GT-32011, to enable flash status monitoring ("1"=Ready, "0"=Busy) by inserting the E33 jumper

#### **85C30 USART**

The module is assembled with an 85C30 serial communications controller, which together with the MAX238 (U5), and the two connectors P4 and P5, support two serial channels. Channel A (P4) is used by the Monitor and channel B is free. The maximum supported baud rate in the Galileo-3 is 19.2Kbaud (it must be the same speed for both ports).

#### RS232 Connectors (P4 & P5) Pin List

The connectors used are standard 5x2 Dual Row Header commonly used in PCs. Note that DTR & DSR are not used by the Monitor software.

| Name | Location |

|------|----------|

| RXD  | 2        |

| TXD  | 3        |

| DTR  | 4        |

| GND  | 5        |

| DSR  | 6        |

#### **Parallel Port**

The parallel interface is fully compatible with the IEEE 1284 standard. It supports the following modes of operation: Standard, ECP, EPP, Byte and Nibble. The connector used (P1) is the new small form factor type 1284C. Companies like 3M, AMP and Molex supply cables that can connect the Galileo-3 1284 port to a DB25 PC parallel port.

## **Address Map**

| Physical Address |           |      |                        |  |

|------------------|-----------|------|------------------------|--|

| Start            | End       | Size | Description            |  |

| 0000 0000        | 000f ffff | 1MB  | DRAM                   |  |

| 1fc0 0000        | 1fcf ffff | 1MB  | Flash                  |  |

| a900 0000        | a9ff ffff | 16MB | 8-bit I/O device space |  |

| a900 0000        |           | 1    | 85C30 channel A+B      |  |

|                  |           |      | control/status         |  |

| a900 0004        |           | 1    | 85C30 chan. A data     |  |

| a900 0008        |           | 1    | 85C30 chan. B data     |  |

| aa00 0000        |           | 1    | IEEE 1284 port         |  |

## **Power Connector**

The power connector (P3) is a standard 51/4" floppy disk or hard disk connector found on every PC power supply.

Note that the 12 Volts pin is not used by the Galileo-3 board.

| Name       | Location |

|------------|----------|

| No Connect | 1        |

| GND        | 2,3      |

| VCC-5V     | 4        |

## **Expansion Connector**

The expansion connector (P2) is used to interface to peripherals like SCSI, Ethernet, PCMCIA cards, or to proprietary logic, in a simple and straightforward manner. The expansion bus includes a buffered non-multiplexed Address bus; 16-bit Data bus; four Chip Select signals; Read and Write controls; Byte Enable; Wait; and DMA Request and Acknowledge. A complete list and the meaning of each signal is described in the GT-32011 data sheet and in the IDT R30XX data sheets.

Note the following before you design with the expansion connector:

- \* Do not use IOCS1, unless the 85C30 USART is not assembled.

- \* PIO2 is connected to the 85C30 USART interrupt request pin. Use this I/O pin only if the USART is not assembled.

- \* Do not use PIO0 if you are using the Flash busy pin for programming. If E33 jumper is removed, PIO0 can be

#### used.

- \* Do not use INT4, since it is connected to the GT-32011 interrupt pin.

- \* SYSCLK is a 33MHz clock. Make the trace length no more then 1.5". A driving buffer is a must if more then one agent is connected to this clock.

- \* The mating connector is Samtec MOLC-125-02-S-Q-LC.

# **P2 Expansion Connector Pin List**

|    | A        | В        | С        | D        |

|----|----------|----------|----------|----------|

| 1  | VCC      | VCC      | A23      | A22      |

| 2  | A21      | A20      | A19      | A18      |

| 3  | A17      | A16      | A15      | A14      |

| 4  | A13      | A12      | A11      | A10      |

| 5  | A9       | A8       | A7       | A6       |

| 6  | A5       | A4       | A3       | A2       |

| 7  | IOA1     | GND      | GND      | VCC      |

| 8  | IODATA0  | IODATA1  | IODATA2  | IODATA3  |

| 9  | IODATA4  | IODATA5  | IODATA6  | IODATA7  |

| 10 | IODATA8  | IODATA9  | IODATA10 | IODATA11 |

| 11 | IODATA12 | IODATA13 | IODATA14 | IODATA15 |

| 12 | GND      | GND      | Reserved | Reserved |

| 13 | Reserved | IOBE0*   | IOBE1*   | IOWAIT*  |

| 14 | IORD*    | IOWR*    | IOCS0*   | IOCS1*   |

| 15 | IOGPCS0* | IOGPCS1* | DMAREQ0  | DMAREQ1  |

| 16 | DMAACK0* | DMAACK1* | VCC      | PIO0     |

| 17 | PIO1     | PIO2     | PIO3     | PIO4     |

| 18 | PIO5     | Reserved | SINT0*   | SINT1*   |

| 19 | SINT2*   | INT3*    | INT4*    | INT5*    |

| 20 | GND      | SYSCLK   | GND      | RESET*   |

| 21 | Reserved | PSTROBE* | POE*     | VCC      |

| 22 | RSVD0    | RSVD1    | RSVD2    | RSVD3    |

| 23 | RSVD4    | GND      | BRCOND0  | BRCOND1  |

| 24 | SBRCOND2 | SBRCOND3 | BERR*    | GND      |

| 25 | Reserved | Reserved | Reserved | Reserved |

For more information concerning the descriptions of these pins, please consult the Galileo GT-32011 and the IDT R30XX CPU data sheets.

# Layout

(Need BOM)

**Bottom Side**