### **AP-747**

# APPLICATION NOTE

# Multi-Source Solution for Intel® 28Fxx0C3 Advanced+Boot Block and AMD\* AM29LVxxxx

October 2001

**NOTE:** This document formerly known as *Multi-Source Solution for Intel*® 28F160B3 Advanced+Boot Block and AMD\* 29LV160.

Order Number: 292295-001

1

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC

### CONTENTS

| PAGE                                           | PAGE                                                                                        |

|------------------------------------------------|---------------------------------------------------------------------------------------------|

| 1.0 INTRODUCTION4                              | FIGURES                                                                                     |

| 2.0 Intel® 3-VOLT ADVANCED+BOOT BLOCK OVERVIEW | Figure 1. Comparison of 28FxxxC3 Advanced+Boot Block 48-Lead TSOP Pinout Versus AMD 29LVxxx |

| 3.0 DEVELOPING MULTI-SOURCED DESIGNS5          | TABLES                                                                                      |

| 3.2 Pinout Differences6                        | Table 1. Feature Comparison Between Intel® C3 and LV5                                       |

| 3.3 Blocking                                   | Table 2. Comparison of Intel and AMD 48-Lead TSOP Pinout                                    |

| 3.5 Command Completion Changes11 4.0 SUMMARY11 | Example: 16M-Bit Word-Wide Memory Addressing8                                               |

| 7.0 OOMMAN                                     | Table 3. Difference Comparison of Intel and AMD                                             |

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

P.O. Box 5937

Denver, CO 80217-9808

or call 1-800-879-4725

or visit Intel's Website at http://www.intel.com/design/flash

COPYRIGHT © INTEL CORPORATION1997, 1998

CG-041493

\*Other names and brands may be claimed as the property of others.

2

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC

### **REVISION HISTORY**

| Date of<br>Revision | Version | Description          |

|---------------------|---------|----------------------|

| 10/08/01            | 1.0     | New document version |

3

### 1.0 INTRODUCTION

This application note outlines how to design a single socket to support the Intel® 3-Volt Advanced+ Boot Block (C3) and the AMD\* AM29LVxxx (LV) flash memory devices. For the sake of simplicity, only the Top-Boot-type devices are explained here. All considerations noted would be valid in a Bottom-Boot design as well. Please also see AP-657 "Designing with the Advanced+Boot Block Flash Memory Architecture." Section 2 defines the advantages in designing with the C3, while Section 3 presents a single socket, multi-source solution.

#### 2.0 Intel 3-VOLT ADVANCED+ BOOT BLOCK OVERVIEW

The Intel C3 products are available in 8-, 16-, 32-, and 64-Mbit densities. All are designed for low voltage (2.7V – 3.6V core) applications requiring code execution and data storage within the same flash devices. The C3 series consists of eight 4-Kword blocks, either at the top address range, (Top Boot) or bottom address ranges (Bottom Boot), followed by a number of 32-Kword blocks, depending density. Please see the 3-Volt Advanced+ Boot Block datasheet for details.

In addition the Intel C3 offers the following design advantages when designing a multi-source solution:

- Complete density pinout compatibility for an easy and less expensive upgrade path

- 1.65-2.5 V or 2.7-3.6 V output range levels

- 12-Volt Production Programming for fast programming during manufacturing

- 128-bit Protection Register

- Low voltage in-system flexible hardware block locking

- Program-Suspend functionality for real time applications

- Flash Data Integrator (FDI) software, plus a vast array of Intel<sup>®</sup> Memory Managers and design tools to reduce time to market

The following sections describe these features and advantages in more detail. Table 1 compares features offered by the C3 and the LV.

#### 2.1 Pinout Compatibility

The C3 products provide density upgrades with complete pinout compatibility from 8-, 16-, 32-, and 64-Mbit densities:

- The 48-ball μBGA\* CSP package—ideal for space constrained designs—is available in 8-, 16-, and 32-Mbit densities

- The 48-lead TSOP is available in 8-, 16-, 32-, and 64-Mbit densities for x16 functionality.

Pinout and package compatibility are extremely important for applications that may change their code or data requirements. Designing for compatibility reduces the impact of re-spinning the board and lengthens the application's lifetime. To accommodate changing requirements, the design should be optimized for the highest density flash device available, and use the density that is required for the present design. Note that vfBGA and uBGA packages require a complete trace redesign because pin placement and pitch differences are not compatible.

# 2.2 12-Volt Production Programming

The Intel C3 products support production programming at 12V to significantly reduce programming time in a manufacturing line. This easily can be combined with 2.7V – 3.6V in-system programming. Please refer to the 3-Volt Advanced+ Boot Block Flash Memory datasheet for details.

# 2.3 In-System Hardware Block Locking

The C3 offers in-system flexible hardware block locking for any block. In-system block locking is possible by applying GND to WP# to lock the blocks, or Vih (min) to WP# to unlock the blocks.

Am29LV800B, Am29LV160D, and Am29LV320D devices require an algorithm that uses 8.5V-12.5V levels on either the #RESET or A9/#OE pins to change locking.

Additionally, when Vpp = GND, the entire device is write protected. Am29LV800B, Am29LV160D, and Am29LV320D devices do not separate the program/erase supply from the core power supply.

4

10/15/01 12:52 PM C3 Iv3 FINAL.DOC

# 2.4 Program-Suspend to Read Functionality

The Intel C3 offers enhanced Suspend capabilities. While both the C3 and the LV offer Erase-Suspend to program or read, only C3 offers Program-Suspends to a read. This functionality can be important for real-time applications that require critical data within the maximum program time (which may be as large as  $100~\mu s$ ).

## 2.5 Memory Managers and Design Tools from Intel

Intel offers several flash memory managers to reduce design time and offer quicker time-to-market solutions including the following:

The Intel<sup>®</sup> Flash Data Integrator (FDI) software can be used for code plus data real-time solutions. The Intel<sup>®</sup>

**Virtual Small Block (VSB) File Manager** –VFM can be used for simple embedded file data storage applications.

Intel also offers a range of flash memory tools for every stage of system development that enable shorter development schedules with lower development costs.

For more information on software, please refer to the Intel Flash website at: http://developer.intel.com/design/flash.

Table 1. Feature Comparison Between Intel C3 and LV

| Feature                          | Intel 800/160/320/640 C3 | AMD LV800B/160/320D/641D        |

|----------------------------------|--------------------------|---------------------------------|

| 12-Volt Production Programming   | 8 µs word write          | 11 μs word write                |

| Lower voltage I/Os               | 1.65 V – 2.5 V or        | 2.7 V- 3.6 V                    |

|                                  | 2.7 V - 3.6 V            | 1.8 V – 2.9 V (Am29LV641D only) |

| In-system hardware block locking | 2.7 V – 3.6 V in system  | Requires 8.5-12.5 V in system   |

|                                  |                          | (except for Am29LV641D) * note  |

| Program-Suspend to read          | Yes                      | No                              |

| Erase-Suspend to read            | Yes                      | Yes                             |

| Erase-Suspend to program         | Yes                      | Yes                             |

• See AMD Spec 22367

### 3.0 DEVELOPING MULTI-SOURCED DESIGNS

This section describes the changes required to design a multi-source socket solution for C3 and LV. Similar methodologies may be applied for other densities.

Please note differences in these areas:

- Pinouts

- Blocking

- Command sets

- Timing notes

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC

# AC Specification Differences Related to Address/Data Latching

From a generic standpoint, Read and Write timing is very similar. See the specific datasheet on the particular density required for exact details.

#### 3.2 Pinout Differences

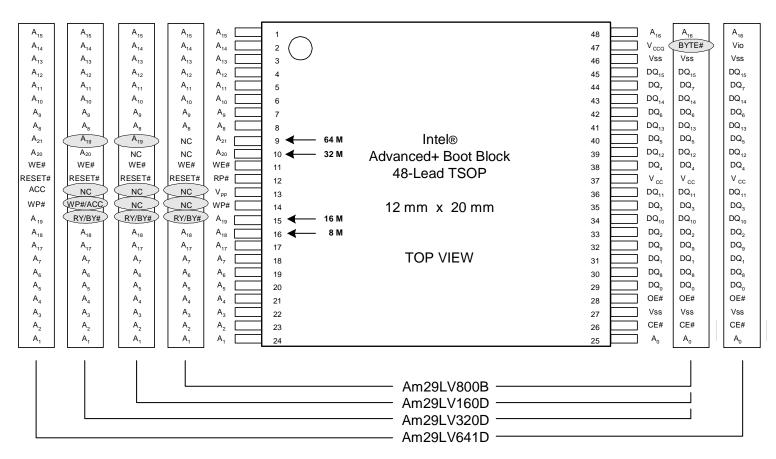

Figure 1 shows the 48-lead TSOP pinout differences between the C3 and the LV. Lower densities will have

NC (No Connects) on the upper address pins. For example, a 16-Mbit device will have NC on pins 9 and 10. NCs are not bonded to the die and have no physical connection. Pins 15 and 47 require special attention on Am29LV800B, Am29LV160D, and AM29LV320D. Note that the 28F640C3 is a direct pin-pin replacement for the Am29LV0641D.

Figure 1. Comparison of 28FxxxC3 Advanced+ Boot Block 48-Lead TSOP Pinout Versus AMD 29LVxxx

6

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC

Table 2. Comparison of Intel and AMD 48-Lead TSOP Pinout

| Pin | Intel                          | AMD LV800B/ 160D / 320D      | Replacement Issue                                    |

|-----|--------------------------------|------------------------------|------------------------------------------------------|

| 9   | NC, A21                        | A <sub>19</sub> (Address 19) | No                                                   |

| 13  | VPP                            | NC                           | No                                                   |

| 14  | WP#                            | NC, WP#/ACC                  | No                                                   |

| 15  | A19 (Address 19)               | RY/BY#                       | Yes                                                  |

| 47  | V <sub>CCQ</sub> (I/O voltage) | BYTE#                        | Must be between 2.7 V – 3.6 V multi-source solutions |

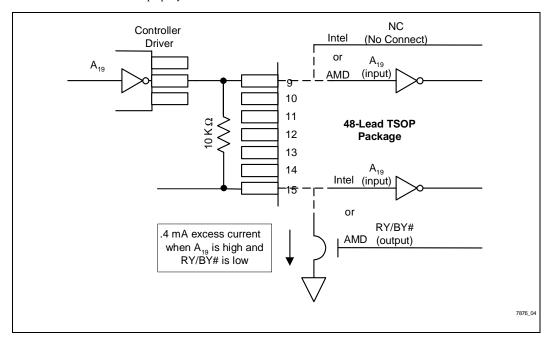

Pin 15 on Intel C3 the input address A<sub>19</sub>. On the Am<sub>29</sub>LV<sub>800</sub>B, Am<sub>29</sub>LV<sub>160</sub>D, and Am<sub>29</sub>LV<sub>320</sub>D, Pin 15 is the RY/BY# pin, an open-drain output. This change will cause bus contention if not properly handled.

Figure 2 provides a design method to alleviate this concern using a simple 10  $K\Omega$  resistor.

Figure 2. A Resistor Solution for Address A<sub>19</sub> (Intel ) and RY/BY# (AMD)

Pin 47 is the I/O supply pin on Intel C3, VCCQ. However on the Am29LV800B, Am29LV160D and Am29LV320D, it is the BYTE# pin. For a multi-source design, both must be between 2.7V-3.6V. The lower voltage  $(1.65\ V-2.5V)$  I/O capability in an Am29LV800B, Am29LV160D, and Am29LV320D is not supported.

#### 3.3 Blocking

Intel C3 devices are designed with eight 4-Kword parameter blocks; the remainder of the array is divided into 32-Kword blocks. AM29LV800B, AM29LV160D, and AM29LV320D devices are designed with an 8-Kword, two

7

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC

4-Kword, and a 16-Kword parameter blocks, with the remainder of the array divided into 32-Kword blocks (see Table Example). Note that the Am29LV800B, Am29LV160D, and Am29LV320D blocking is a subset of the C3 blocking, (except for Am29LV0641D). Although the blocking architectures are similar, software must

account for these parameter- block differences. For example, when erasing the one 16-Kword block of the LV device, four 4-Kword blocks must be erased on the C3 to account for the same address range. Note that the Am29LV0641D only has symmetrical blocks that are 32 Kwords in size.

**Example: 16M-Bit Word-Wide Memory Addressing**

| Top Boot     |             | Bottom Boot  |             |              |             |              |             |

|--------------|-------------|--------------|-------------|--------------|-------------|--------------|-------------|

| Size<br>(KW) | INTEL C3    | Size<br>(KW) | LV          | Size<br>(KW) | LV          | Size<br>(KW) | INTEL C3    |

| 4            | FF000-FFFFF | 8            | FE000-FFFFF | 32           | F8000-FFFFF | 32           | F8000-FFFFF |

| 4            | FE000-FEFFF |              |             | 32           | F0000-F7FFF | 32           | F0000-F7FFF |

| 4            | FD000-FDFFF | 4            | FD000-FDFFF | 32           | E8000-EFFFF | 32           | E8000-EFFFF |

| 4            | FC000-FCFFF | 4            | FC000-FCFFF | 32           | E0000-E7FFF | 32           | E0000-E7FFF |

| 4            | FB000-FBFFF | 16           | F8000-FBFFF | 32           | D8000-DFFFF | 32           | D8000-DFFFF |

| 4            | FA000-FAFFF |              |             | 32           | D0000-D7FFF | 32           | D0000-D7FFF |

| 4            | F9000-F9FFF |              |             | 32           | C8000-CFFFF | 32           | C8000-CFFFF |

| 4            | F8000-F8FFF |              |             | 32           | C0000-C7FFF | 32           | C0000-C7FFF |

| 32           | F0000-F7FFF | 32           | F0000-F7FFF | 32           | B8000-BFFFF | 32           | B8000-BFFFF |

| 32           | E8000-EFFFF | 32           | E8000-EFFFF | 32           | B0000-B7FFF | 32           | B0000-B7FFF |

| 32           | E0000-E7FFF | 32           | E0000-E7FFF | 32           | A8000-AFFFF | 32           | A8000-AFFFF |

| 32           | D8000-DFFFF | 32           | D8000-DFFFF | 32           | A0000-A7FFF | 32           | A0000-A7FFF |

| 32           | D0000-D7FFF | 32           | D0000-D7FFF | 32           | 98000-9FFFF | 32           | 98000-9FFFF |

| 32           | C8000-CFFFF | 32           | C8000-CFFFF | 32           | 90000-97FFF | 32           | 90000-97FFF |

| 32           | C0000-C7FFF | 32           | C0000-C7FFF | 32           | 88000-8FFFF | 32           | 88000-8FFFF |

| 32           | B8000-BFFFF | 32           | B8000-BFFFF | 32           | 80000-87FFF | 32           | 80000-87FFF |

| 32           | B0000-B7FFF | 32           | B0000-B7FFF | 32           | 78000-7FFFF | 32           | 78000-7FFFF |

| 32           | A8000-AFFFF | 32           | A8000-AFFFF | 32           | 70000-77FFF | 32           | 70000-77FFF |

| 32           | A0000-A7FFF | 32           | A0000-A7FFF | 32           | 68000-6FFFF | 32           | 68000-6FFFF |

| 32           | 98000-9FFFF | 32           | 98000-9FFFF | 32           | 60000-67FFF | 32           | 60000-67FFF |

| 32           | 90000-97FFF | 32           | 90000-97FFF | 32           | 58000-5FFFF | 32           | 58000-5FFFF |

| 32           | 88000-8FFFF | 32           | 88000-8FFFF | 32           | 50000-57FFF | 32           | 50000-57FFF |

| 32           | 80000-87FFF | 32           | 80000-87FFF | 32           | 48000-4FFFF | 32           | 48000-4FFFF |

| 32           | 78000-7FFFF | 32           | 78000-7FFFF | 32           | 40000-47FFF | 32           | 40000-47FFF |

| 32           | 70000-77FFF | 32           | 70000-77FFF | 32           | 38000-3FFFF | 32           | 38000-3FFFF |

| 32           | 68000-6FFFF | 32           | 68000-6FFFF | 32           | 30000-37FFF | 32           | 30000-37FFF |

| 32           | 60000-67FFF | 32           | 60000-67FFF | 32           | 28000-2FFFF | 32           | 28000-2FFFF |

| 32           | 58000-5FFFF | 32           | 58000-5FFFF | 32           | 20000-27FFF | 32           | 20000-27FFF |

| 32           | 50000-57FFF | 32           | 50000-57FFF | 32           | 18000-1FFFF | 32           | 18000-1FFFF |

| 32           | 48000-4FFFF | 32           | 48000-4FFFF | 32           | 10000-17FFF | 32           | 10000-17FFF |

| 32           | 40000-47FFF | 32           | 40000-47FFF | 32           | 08000-0FFFF | 32           | 08000-0FFFF |

| 32           | 38000-3FFFF | 32           | 38000-3FFFF | 16           | 04000-07FFF | 4            | 07000-07FFF |

| 32           | 30000-37FFF | 32           | 30000-37FFF |              |             | 4            | 06000-06FFF |

| 32           | 28000-2FFFF | 32           | 28000-2FFFF |              |             | 4            | 05000-05FFF |

8

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC

| 32 | 20000-27FFF | 32 | 20000-27FFF |   |             | 4 | 04000-04FFF |

|----|-------------|----|-------------|---|-------------|---|-------------|

| 32 | 18000-1FFFF | 32 | 18000-1FFFF | 4 | 03000-03FFF | 4 | 03000-03FFF |

| 32 | 10000-17FFF | 32 | 10000-17FFF | 4 | 02000-02FFF | 4 | 02000-02FFF |

| 32 | 08000-0FFFF | 32 | 08000-0FFFF | 8 | 00000-01FFF | 4 | 01000-01FFF |

| 32 | 00000-07FFF | 32 | 00000-07FFF |   |             | 4 | 00000-00FFF |

#### 3.4 Command Sets

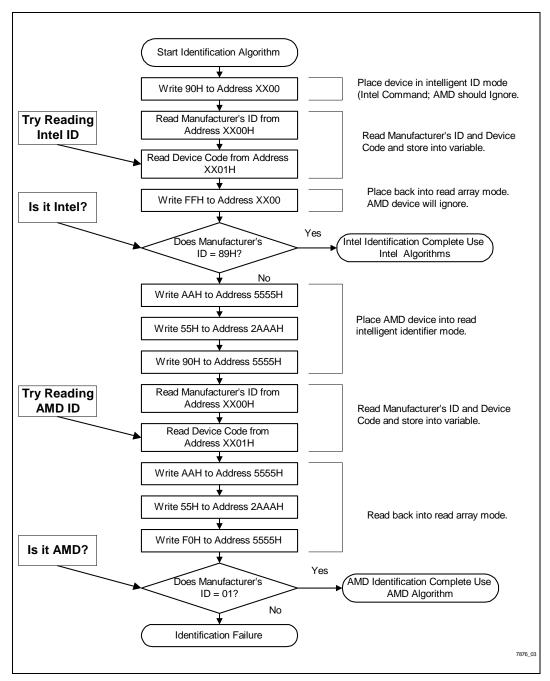

Command sets are different between the Intel C3 and all AMD LV devices. The C3 commands are 2-cycle commands, whereas LV commands vary between 2 and 6 cycles. Table 3 shows common command sequence differences between the C3 and the LV devices. To determine which command set to use in an application, the algorithm in Figure 3 can be used to identify which device is in the application through the use of manufacturer identifier codes. If the algorithm returns an identification failure, another manufacturer's device resides in the socket.

Note that this algorithm depends on the LV ignoring the C3 commands, and vice versa. In addition, Intel C3 automatically enters an "all-blocks-locked" mode after a reset, so the 60H and D0H commands must be issued to erase or program a block.

The Read Query Command (98H) could also be incorporated (if preferred) to use the "Common Flash Interface" (CFI) data. The CFI data structure contains information such as block size, density, command set and electrical specifications. Once in this mode, read cycles from addresses are shown in Default. To return to readarray mode, write the Read Array command (FFH).

Table 3. Difference Comparison of Intel and AMD Command Set

| Command         | C3 (Addr/Data)                  | LV (Addr/Data)          |

|-----------------|---------------------------------|-------------------------|

| Read Mode       | XXXXH / FFH                     | XXXH/F0H                |

| Read ID         | XXXXH/90H                       | 5555H/AAH, 2AAAH/55H    |

|                 |                                 | 5555H/90H               |

| Read Query      | XXXXH/98H                       | 55H/98H                 |

| Program         | (60H, D0H), Addr/40H, Addr/Data | 5555H/AAH, 2AAAH/55H,   |

|                 |                                 | 5555H/A0H, Addr/Data    |

| Erase           | (60H, D0H), Blk Addr/20H,       | 5555H/AAH, 2AAAH/55H,   |

|                 | Blk Addr/D0H                    | 5555H/80H, 5555H/AAH    |

|                 |                                 | 2AAAH/55H, Blk Addr/30H |

| Program Suspend | XXXXH/B0H                       | Not Available           |

| Program Resume  | XXXXH/D0H                       | Not Available           |

| Erase Suspend   | XXXXH/B0H                       | XXXXH/B0H               |

| Erase Resume    | XXXXH/D0H                       | XXXXH/30H               |

$\textbf{NOTE:} \ \ \textbf{Please refer to the appropriate datasheet for all command definitions}.$

9

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC

Figure 3. An Example of Manufacturer Identifier Algorithm

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC

# INTEL CONFIDENTIAL (until publication date)

10

# 3.5 Command Completion Changes

Intel C3 devices use a status register for checking operation status, while AM29LV800B, AM29LV160D, and AM29LV320D devices use the Ready/Busy (RY/BY#) pin to indicate if an operation has be completed. Software should be designed to comprehend this difference, based on the identification algorithm discussed in Section 3.4.

#### 4.0 SUMMARY

This application note focused on designing a multi-source solution between the Intel C3 and the LV devices. Advantages of designing with the Intel C3 include the following:

- · Pinout compatibility for easy upgrade path

- · Lower IO voltages

- 12-volt production programming for fast programming during manufacturing

- Low voltage block locking

- · Program-Suspend functionality

- Intel<sup>®</sup> Flash Data Integrator (FDI) software for code plus data real-time solutions, or

- Intel<sup>®</sup> Virtual Small Block (VSB) File Manager (VFM), for simple embedded file data storage applications.

Intel also offers a range of flash memory tools for every stage of system development that enable shorter development schedules with lower development costs.

To implement a multi-source design, users need to pay special attention to AC specifications, pinout differences, blocking differences, command-set differences, and command-completion differences.

11

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC

# APPENDIX A ADDITIONAL INFORMATION(1,2)

| Order Number | Document/Tool                                                                               |

|--------------|---------------------------------------------------------------------------------------------|

| 290580       | 3-Volt Advanced+ Boot Block Flash Memory; 28F800C3, 28F160C3, 28F320C3, 28F640C3, datasheet |

| Note 2       | Smart 3 Advanced+ Boot Block Software Algorithms (Assembly and C Drivers)                   |

| Note 2       | Schematic symbols, TimingDesigner* files, VHDL models, Verilog models, and IBIS models      |

#### NOTE:

- Please call the Intel Literature Center at (800) 548-4725 to request Intel documentation. International customers should contact their local Intel or distribution sales office.

- 2. Visit Intel's World Wide Web home page at http://www.intel.com/design/flash for technical documentation and tools.

12

10/15/01 12:52 PM C3\_lv3\_FINAL.DOC