# **GRF1000 900MHz Frequency Synthesizer with Integrated VCO**

## **General Descriptions**

The GRF1000 is a CMOS monolithic integrated circuit for CDMA systems. The circuit includes on-chip RF VCO, phase frequency detector(PFD), charge pump, and loop filter. With this product, the LO signal can be generated with only a few external elements such as bypass elements and matching elements. The circuit also includes an IF PLL and charge pump to ease board level design. Only a tank circuit and loop filter are needed to complete IF Frequency generation. The device will be provided in 20-pin QFN package.

#### **Features**

- Proprietary Fractional-N Frequency Synthesizer

- On-chip PLL Frequency Synthesizer

- On-chip RF VCO

- · On-chip Loop Filter

- 2.7V to 3.3V operation

- · 15mA typicaldrain current

- IF power-down mode

#### **Application**

AMPS and Cellular CDMA(900MHz) dual-mode system

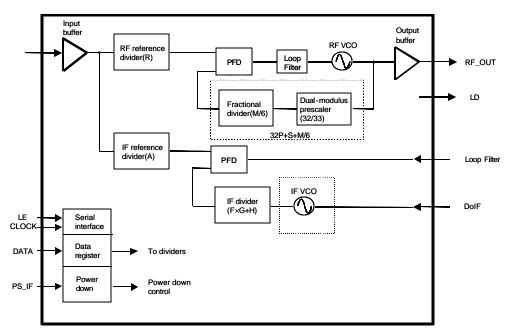

Figure 1. GRF1000 Circuit Block Diagram

# 900MHz Frequency Synthesizer with Integrated VCO

## **Function Description**

#### **Product Description**

The circuit is highly integrated CMOS PLL for generating LO signal in AMPS and cellular CDMA system around 900MHz. The circuit includes all functional blocks including RF VCO, prescaler, PFD, and loop filter. Only few external elements to match output impedance and bypass elements for power line stabilization are used to complete the PLL.

Meanwhile, the circuit includes IF VCO, IF prescaler, and PFD to support IF carrier generation. An off-chip inductor and appropriate loop filter will be used to tune the IF frequency at the desired value.

The GRF1000 frequency synthesizer has a patent pending Fractional-N architecture to support 10KHz channel spacing. The circuit supports various reference frequencies with 10KHz minimum resolution such as 19.6, 19.68, and 19.8MHz. The Fractional-N architecture has very low spurious modulation effect, which is a big problem in conventional scheme. This enables fast lock-up to reduce the power consumption and system set-up time. Another advantage of is that the occupied area of the loop filter is reduced compared to integer-N, which allows the loop filter to be included in the circuit to minimize the external noise coupling and save space on the board.

#### **IF-PLL Section**

The divide ratio can be calculated using the following equation:

$f_{VCO} = \{4 \times (A+1) + (B+1)\} \times f_{OSC} / R (B < A)$

$f_{VCO}$ : Output frequency of voltage controlled oscillator (VCO)

A : Preset divide ratio of binary 13-bit programmable counter ( $1 \le A \le 8,191$ )

B : Preset divide ratio of binary 4-bit swallow counter (0  $\leq$  B  $\leq$  15)

fosc: Reference oscillation frequency

R : Preset divide ratio of binary 15-bit programmable reference counter ( $2 \le R \le 32,767$ )

$f_{VCO} = \{32 \times P + S + (M / 6)\} \times f_{OSC} / R (S < P)$

$f_{\text{VCO}}$  : Output frequency of voltage controlled oscillator (VCO)

$\dot{P}$ : Preset divide ratio of binary 13-bit programmable counter (2  $\leq$  P  $\leq$  8,191)

S: Preset divide ratio of binary 6-bit swallow counter (0  $\leq$  S  $\leq$  63)

M : Preset 3-bit numerator of modulus counter ( $0 \le M \le 5$ )

fosc: Reference oscillation frequency

R : Preset divide ratio of binary 13-bit programmable reference counter ( $1 \le R \le 8,191$ )

#### Power down modes

The circuit includes the various power down modes to reduce the power consumption. The IF-PLL enters in power saving mode by setting  $PDN_{IF}$  pin to low. When the  $PDN_{IF}$  is high, the IF-PLL operates in normal mode. During power down mode, phase detector output(DoIF) becomes high impedance and thus IF-PLL loses lock.

A register(register 0) has a allocated bit(PDN<sub>RF</sub>) for power down of the RF-PLL. This register can be written by the serial interface. When PDN<sub>RF</sub> is low, the RF-PLL enters in power saving mode and loses lock.

#### Serial interface

The frequency setting and other auxiliary functions, such as power down, are established by the serial interface. The serial interface is a 3-wire serial interface that have CLOCK, DATA, and LE(Load ENABLE) pins.

Programmable dividers in the RF/IF PLL are separated and controlled individually. Each divider has its own register. The data pin is serially accessed in a shift register. The operation of shift register is controlled by a clock pin. On the rising edge of clock, one bit of serial data is transferred into the shift register. When LE signal is high, the data stored in the shift register is transferred to one register latch depending upon the control bit data setting.

When all bits are loaded in the shift register, the stored value in shift register is transferred to the corresponding register according to the control bits setting. The time at which data loading occurs is indicated by low-to-high transition of LE signal.

RF-PLL Section

# **Electrical specifications**

### **Maximum Ratings**

| Parameter                 | Ratings   | Unit |

|---------------------------|-----------|------|

| Supply Voltage            | -0.4 to 5 | Vdc  |

| Storage Temperature Range | -40 to 85 | °C   |

| Parameter                            | Min | Тур  | Max  | Unit   | Remarks        |

|--------------------------------------|-----|------|------|--------|----------------|

| Supply Voltage                       | 2.7 | 3.0  | 3.3  | Volt   | DC voltage     |

| Current Consumption                  |     | 15   | 18   | mA     |                |

| Frequency Range                      | 954 |      | 980  | MHz    | RF frequency   |

| Output Power                         | -3  | 0    | 3    | dBm    |                |

| Lock Time                            |     | 0.5  | 0.6  | msec   | 26MHz Band     |

| Operating Temperature                | -30 |      | 80   | °C     |                |

| Phase Noise                          |     | -111 | -108 | dBc/Hz | @100kHz offset |

|                                      |     | -133 | -130 |        | @1MHz offset   |

| 2 <sup>nd</sup> Harmonic Suppression |     |      | -20  |        |                |

| IF Input Frequency                   |     |      | 500  | MHz    |                |