# Switched Fast Ethernet Controller

GT- 48002

Preliminary Rev. 1.1 October 2, 1996

#### **FEATURES**

NOTE: Always contact Galileo Technology for possible updates before starting a design

- Member of GalNet<sup>™</sup> Architecture Family

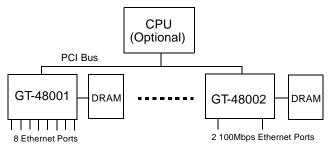

- Ideal uplink/server connect for the 10 Mbps GT-48001 Switched Ethernet Controller

- High integration, low cost, Switched Fast Ethernet Controller for 100 Base-TX, Base-T4, and Base-FX

- Provides switching functions between two 10/ 100Mbps, auto-negotiated Ethernet ports and PCI Bus

- Switch expansion via, high bandwidth PCI interface (up to 1Gbps)

- · Supports 'Store and Forward' switching approach

- · Low last-bit to first-bit delay

- Permits forwarding and filtering at full wire speed of 148,800 packets/sec on each Ethernet port

- · Advanced address recognition

- Intelligent address recognition mechanism enables forwarding rate at full wire speed

- Self-learning mechanism

- Supports up to 8K Unicast addresses and unlimited Multicast/Broadcast addresses

- Broadcast storm rate filtering

- Permits software or hardware intervention in the packet routing decision mechanisms

- Incorporates two 802.3 compliant 10/100Mbps Media Access Controllers

- Direct Interface to MII (Media Independent Interface)

- Half/Full Duplex Support (up to 200 Mbps/port)

- IEEE 802.3 100Base-TX, T4, and FX compatible

- Full MII Management Support (MDC/MDIO) via CPU access

- Auto-negotiation supported through MII Interface

- VLAN tagging support (1522 bytes)

- · High observability LED interface

- 6 parallel LED outputs per port, including internal "monostable" function to enable viewing of dynamic signals

- 3 pin serial LED interface for additional status information per port.

- · Direct support for packet buffering

- Interfaces directly to 1Mbyte or 2Mbyte 32-bit, 60ns EDO DRAM

- Up to 1K buffers, 1536-bytes each, dynamically allocated to the receive and PCI ports

- Interfaces directly with PCI Rev 2.1 for switch expansion

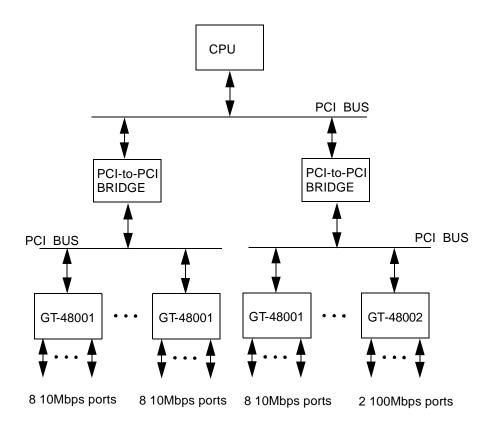

- Up to 4 GT-48001/ GT-48002 devices per PCI slot without PCI-to-PCI bridging, and up to 32 GT-48001/ GT-48002 devices in a switch

- CPU connection for management

- Connection to other media

- · Various management support features

- Repeater MIB and PCI counters, plus enhanced counter set

- Aging support

- Hardware assist for Spanning Tree algorithm(IEEE 802.1)

- Station-to-Station connectivity matrix (for RMON)

- CPU access to Address Table

- Ability to define static addresses

- Monitoring (Sniffer) mode

- 33MHz clock rate

- 5V operation

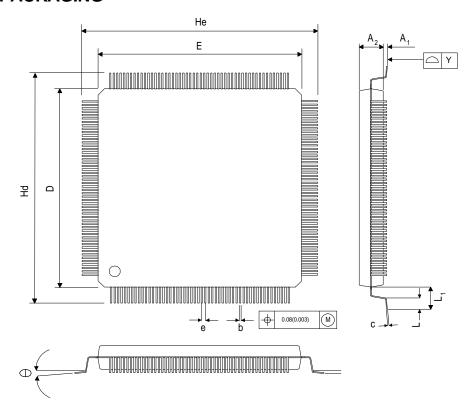

- 208 pin QFP package

#### **OVERVIEW**

#### **General Description**

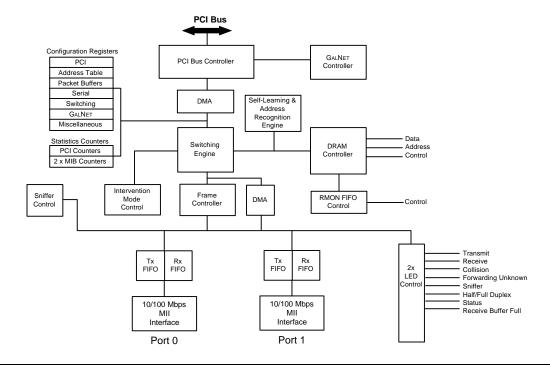

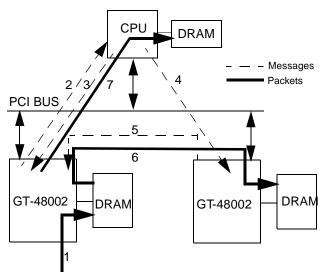

The GT-48002 is a high performance, low cost, Switched Fast Ethernet Controller. It provides the switching functions between two dedicated 10/100Mbps Ethernet ports. Switch expansion to 10Mbps Ethernet ports (using the GT-48001) or to 10/100Mbps ports (using additional GT-48002's) is enabled via a high performance, high bandwidth PCI bus.

The GT-48002 is a member of Galileo's GalNet™ switching architecture. GalNet™ enables designers to build intelligent and scalable switching hubs and lets the user boost performance cost-effectively in departments, workgroups and small data centers.

The GT-48002 uses a Store and Forward switching approach. It forwards and filters faster than than full wire speed.

#### **Serial Interface**

The GT-48002 incorporates two 10/100Mbps Ethernet ports. Two Media Independent Interfaces (MII) are provided for glueless connection to off-the-shelf PHY chips. Each port includes the Media Access Control function (MAC) and six LEDs for Link Status, Collision, Receive Transmit, Half/Full Duplex and Receive Buffer Full indications.

The GT-48002 incorporates full MII management support. The MDC/MDIO pins are directly controlled by the CPU.

## **Address Recognition**

The GT-48002 supports up to 8K different MAC addresses and unlimited Multicast/Broadcast addresses. An intelligent address recognition mechanism enables filtering and forwarding at full wire speed.

The GT-48002 provides a self address learning mechanism. Each device holds its own Address Table. The GT-48002 learns the new addresses as they arrive from the wire and updates all the Address Tables in the system.

#### **DRAM Interface**

The GT-48002 interfaces directly to a 1Mbyte or 2 Mbyte DRAM. The DRAM is used to store the incoming/outgoing packets as well as the Address Table. The on-chip DRAM controller supports EDO DRAMs.

The GT-48002 supports up to 1008 (full packet size) receive buffers. These buffers are dynamically allocated to the receive ports and the PCI port. The number of buffers can be optionally limited on a per port basis.

#### **PCI** Interface

The GT-48002 has a glueless connection to the PCI bus. The interface is compliant with PCI Rev 2.1. The GT-48002 can be either a master initiating a PCI bus operation or a target responding to a PCI bus operation. The PCI bus is used as a backplane to expand the switch allowing connection to 10Mbps Ethernet ports (using the GT-48001) or 10/100Mbps ports. Up to four GT-48001/GT-48002 devices can reside on the same PCI bus, forwarding packets from one port to the other. By using PCI-to-PCI bridge devices, the switch can be expanded to up to 32 devices

The PCI bus may also be used to connect a CPU for management / routing functions, and to connect to other LAN technologies such as ATM or FDDI. The connection to a CPU is optional.

### **Management Features**

The GT-48002 provides comprehensive management capabilities enabling the user to manage and balance the network.

The GT-48002 supports per-port statistics counters and PCI traffic counters. It implements hardware assistance for Aging, Spanning Tree algorithms and allows the CPU access to the Address Table. The GT-48002 also provides a Station-to-Station Connectivity matrix (RMON) and the ability to select a port to work in Monitoring (Sniffer) mode.

#### **Intervention Mode**

The GT-48002 incorporates an enhanced feature called 'Intervention' mode. This feature permits software or hardware intervention in the packet routing decision. Intervention is performed differently for Multicast and for Unicast packets. Multicast packets are forwarded *only* to the CPU. The CPU forwards the packets to selected ports in the GT-48002 devices.

For Unicast packets, the CPU has the ability to modify the routing decision. It can discard the packet, it can change the target port, or it can request the entire packet information.

Easy Expansion To 256-Ports and CPU Connectivity

Via the PCI Interface

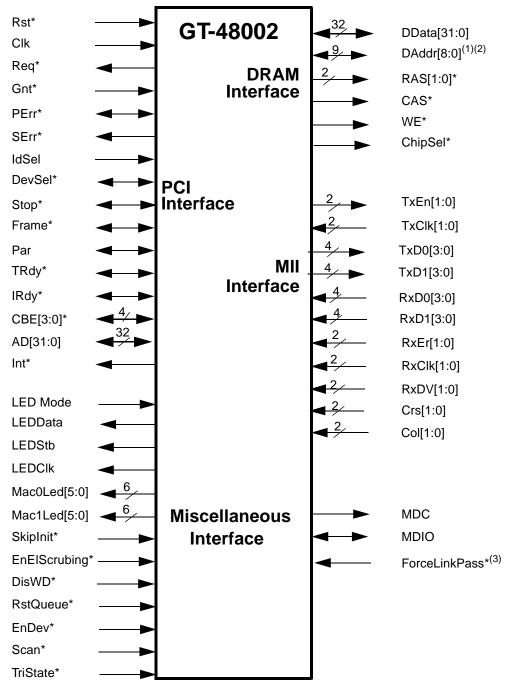

### 1 PIN INFORMATION

# 1.1 Logic Symbol

- (1) Pins[8,5:0] sampled at reset to establish Device Number and DRAM Parameters

- (2) Pins[7:6] sampled at reset to establish Half/Full Duplex Mode per port (1= full duplex)

- (3) Pin sampled at reset to force the link status of all ports to link up state (0 = force link up)

# 1.2 Pin Assignment Table

| Symbol        | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCI Interface |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Rst*          | I    | Reset: Active low. Resets the GT-48002 to its initial state. Rst* must be asserted for at least 10 PCI clock cycles. When in the reset state, all PCI output pins are tristated and all open drain signals are floated. Following Rst* deassertion, the GT-48002 clears the internal buffers and initializes the address table in the DRAM. The address table initialization takes 165,000 CLK cycles to complete. Any incoming packets during the address table initialization, are ignored. |  |

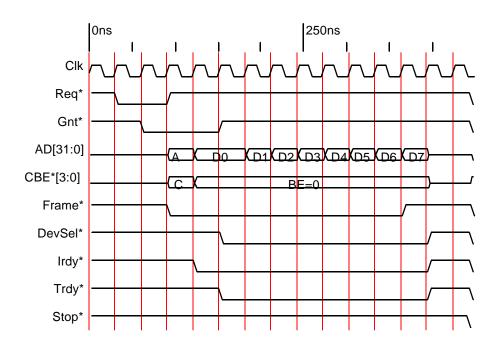

| Clk           | I    | <b>Clock:</b> Provides the timing for the GT-48002 internal units. All units except for the Serial Interfaces use this clock. It also provides the timing for the PCI-related bus transactions. The clock frequency is 33MHz                                                                                                                                                                                                                                                                  |  |

| Req*          | 0    | <b>Bus Request:</b> Asserted to indicate to the PCI bus arbiter that the GT-48002 desires use of the bus.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Gnt*          | I    | <b>Bus Grant:</b> Indicates to the GT-48002 that access to the PCI bus is granted.                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| PErr*         | I/O  | Parity Error: Asserted when a data parity error is detected on the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| SErr*         | 0    | <b>System Error:</b> Asserted when an address parity error is detected. The GT-48002 asserts the SErr* two cycles after the failing address. This output has an open-drain output driver.                                                                                                                                                                                                                                                                                                     |  |

| IDSel         | I    | <b>Initialization Device Select:</b> Acts as a chip select during PCI configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                              |  |

| DevSel*       | I/O  | <b>Device Select:</b> Asserted by the target of the current access. When the GT-48002 is a bus master, it expects the target to assert DevSel* within 5 bus cycles, confirming the access. If the target does not assert DevSel* within the required bus cycles, the GT-48002 aborts the cycle. As a target, when the GT-48002 recognizes its transaction, it asserts DevSel* in a "medium speed" (two cycles after the assertion of Frame*).                                                 |  |

| Stop*         | I/O  | <b>Stop:</b> Indicates that the current target is requesting the bus master to stop the current transaction. As a master, the GT-48002 responds to the assertion of Stop*, either disconnecting, retrying, or aborting. As a target, the GT-48002 asserts Stop* to retry.                                                                                                                                                                                                                     |  |

| Frame*        | I/O  | Cycle Frame: Asserted by the GT-48002 to indicate the beginning and duration of a master transaction. Frame* is asserted to indicate the beginning of the cycle. While Frame* is asserted, data transfer continues. Frame* is deasserted to indicate that the next data phase is the final data phase transaction. Frame* is monitored when the GT-48002 acts as a target, to detect a configuration or memory transaction.                                                                   |  |

| Par           | I/O  | <b>Parity:</b> Calculated by the GT-48002 as an even parity bit for the AD[31:0] and CBE[3:0]* lines.                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Symbol                        | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TRdy*                         | I/O  | Target Ready: Indicates the target agent's ability to complete the current data phase of the transaction. A data phase is completed cany clock when both TRdy* and IRdy* are asserted. Wait cycles are inserted until both IRdy* and TRdy* are asserted together.                                                                                                                                                           |  |

| IRdy*                         | I/O  | Initiator Ready: Indicates the bus master's ability to complete the current data phase of the transaction. A data phase is completed or any clock when both TRdy* and IRdy* are asserted. Wait cycles are inserted until both IRdy* and TRdy* are asserted together.                                                                                                                                                        |  |

| AD[31:0]                      | I/O  | Address/Data: 32-bit multiplexed PCI address and data lines. During the first clock of the transaction, AD[31:0] contains a physical byte address (32 bits). During subsequent clock cycles, AD[31:0] contains data.                                                                                                                                                                                                        |  |

| CBE[3:0]*                     | I/O  | Bus Command/Byte Enable: These signals are multiplexed on the same PCI pins. During the address phase of the transaction, CBE[3:0]* provide the Bus Command. During the data phase, they provide the Byte Enables, which determine which bytes carry valid data.                                                                                                                                                            |  |

| Int*                          | 0    | Interrupt Request Line: Int* is asserted by the GT-48002 when one (or more) of the bits in the Interrupt Cause register is set. This output has an open-drain output driver.                                                                                                                                                                                                                                                |  |

| DRAM Interface                |      |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| DData[31:0]                   | I/O  | DRAM Data: 32-bit EDO DRAM Data.                                                                                                                                                                                                                                                                                                                                                                                            |  |

| DAddr[8:0]                    | I/O  | DRAM Address Bus: In normal operation, DAddr[8:0] contain the DRAM address. During reset, these multiplexed pins are sampled by the GT-48002 to indicate the Device Number, DRAM Parameters, and the Duplex Mode (see Reset Configuration section). Values are determined by connecting the appropriate pull-up/pull-down resistors. The configuration information is accessible via the Status and Port Control registers. |  |

| RAS[1:0]*                     | 0    | Row Address Strobes: Active low. DRAM row address strobes. RAS[0]* is used for Bank0. RAS[1]* is used for Bank1.                                                                                                                                                                                                                                                                                                            |  |

| CAS*                          | 0    | <b>Column Address Strobes:</b> Active low. DRAM column address strobe.                                                                                                                                                                                                                                                                                                                                                      |  |

| WE*                           | 0    | Write Enable: Active low. DRAM write enable.                                                                                                                                                                                                                                                                                                                                                                                |  |

| ChipSel*                      | 0    | Chip Select: Active low. This pin is connected to an external FIFO device for buffering data for RMON. It is asserted by the GT-48002 to indicate that the packet's Byte Count, Destination Address and Source Address are being read from the DRAM. This information is stored in the FIFO and accessed by an external CPU for Station-to Station connectivity matrix implementation.                                      |  |

| Media Independen<br>Interface | t    |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| TxEn[1:0 ]                    | 0    | <b>Transmit Enable:</b> Active high. This output indicates that the packet is being transmitted. TxEn is synchronous to TxClk.                                                                                                                                                                                                                                                                                              |  |

| TxClk[1:0]                    | I    | <b>Transmit Clock:</b> Provides the timing reference for the transfer of TxEn, TxD signals. TxClk frequency is one fouth of the data rate (25 MHz for 100Mbps, 2.5 MHz for 10Mbps). TxClk nominal frequency should match the nominal frequency of RxClk for the same port.                                                                                                                                                  |  |

| Symbol          | Туре | Description                                                                                                                                                                                                                                                                                                     |  |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TxD0[3:0]       | 0    | <b>Transmit Data 0:</b> Outputs the Port0 Transmit Data. Synchronous to TxClk[0].                                                                                                                                                                                                                               |  |

| TxD1[3:0]       | 0    | <b>Transmit Data 1:</b> Outputs the Port1 Transmit Data. Synchronous to TxClk[1].                                                                                                                                                                                                                               |  |

| Col[1:0]        | I    | Collision detect: Active high. Indicates a collision has been detected on the wire. This input is ignored in full-duplex mode.                                                                                                                                                                                  |  |

| RxD0[3:0]       | I    | Receive Data 0: Port 0 Receive Data. Synchronous to RxClk[0].                                                                                                                                                                                                                                                   |  |

| RxD1[3:0]       | I    | Receive Data 1: Port 1 Receive Data. Synchronous to RxClk[1].                                                                                                                                                                                                                                                   |  |

| RxEr[1:0]       | 1    | <b>Receive Error</b> . Active high. Indicates that an error was detected in the received frame. This input is ignored when RxDV for the same port is inactive.                                                                                                                                                  |  |

| RxClK[1:0]      | I    | Receive Clock. Provides the timing reference for the transfer of the RxDV,RxD,RxEr signals (per port). Operates at either 25 MHz (100Mbps) or 2.5 MHz (10Mbps). The nominal frequency of RxClk (per port) should match the nominal frequency of that port's TxClk.                                              |  |

| RxDV[1:0]       | I    | Receive Data Valid: Active high. Indicates that valid data is present on the RxD lines. Synchronous to RxClk.                                                                                                                                                                                                   |  |

| CrS[1:0]        | I    | Carrier Sense: Active high. Indicates that either the transmit or receive medium is non-idle.                                                                                                                                                                                                                   |  |

| MDC             | 0    | Management Data Clock: Provides the timing reference for the transfer of the MDIO signal. This output may be connected to the PHY devices of both ports.                                                                                                                                                        |  |

| MDIO            | I/O  | Management Data Input/Output: This bidirectional line is used to transfer control information and status between the PHY and the GT-48002. It conforms with IEEE Std 802.3. This signal may be connected to the PHY devices of both ports. When not in use, this pin must be connected to a pull-down resistor. |  |

| Misc. Interface |      |                                                                                                                                                                                                                                                                                                                 |  |

| LEDMode         | I    | <b>LED Mode Select:</b> Affects Port status LED, LEDClk frequency and LED ON time values.                                                                                                                                                                                                                       |  |

|                 |      | 0 - select LED mode 0<br>1 - select LED mode 1                                                                                                                                                                                                                                                                  |  |

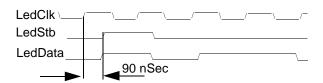

| LEDData         | 0    | LED Data: Active low. Serial data bit stream which contains the LED indicators per port. The data is shifted out using the LEDClk. LEDStb is used to mark the first data bit.                                                                                                                                   |  |

| LEDStb          | 0    | <b>LED Strobe:</b> Active high. Indicates the beginning (data bit #1) of a valid data frame on LEDData output.                                                                                                                                                                                                  |  |

| LEDCIk          | 0    | <b>LED Clock:</b> 1 MHz clock (at LED mode 0), 202 KHz clock (at LED mode 1). This output is used to clock the LEDStb and LEDData outputs. During RESET, LEDClk frequency is 33 MHz.                                                                                                                            |  |

| Mac0LED[5:0]    | 0    | MAC LED 0: Active LOW LED outputs for port 0                                                                                                                                                                                                                                                                    |  |

|                 |      | bit [0] : Port Status (operation according to LEDMode)                                                                                                                                                                                                                                                          |  |

|                 |      | bit [1]: Transmit In Progress (TxEn active)                                                                                                                                                                                                                                                                     |  |

|                 |      | bit [2] : Receive In Progress (RxDV active)                                                                                                                                                                                                                                                                     |  |

|                 |      | bit [3]: Collision (Col active)                                                                                                                                                                                                                                                                                 |  |

|                 |      | bit [4]: Full Duplex (port configured to Full Duplex)                                                                                                                                                                                                                                                           |  |

|                 |      | bit [5] : Receive Buffer Full (programmable limit exceeded)                                                                                                                                                                                                                                                     |  |

|                 |      | An external driver is required to drive the LEDs.                                                                                                                                                                                                                                                               |  |

|                 |      |                                                                                                                                                                                                                                                                                                                 |  |

| Symbol         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAC1LED[5:0]   | 0    | MAC LED 1: Active LOW LED outputs for port 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                |      | Same as MAC0LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| RstQueue*      | I    | Reset Transmit Queues: When asserted, all internal transmit and receive queues are cleared. All GT-48002 state machines are reset to their initial state. This function may be also controlled by software via the Global Control Register.                                                                                                                                                                                                                                                                                                          |  |

| ForceLinkPass* | I/O  | Force Link Pass: Active low. This pin is sampled at reset. When connected to a pullup, the link status of the ports is read through the SMI (MDC/MDIO interface) from the PHY devices (register#1, bit#2). When connected to a pull-down, the link status of all ports remains in the "link is up" state regardless of the PHY's link bit value. This pin should be connected to either a pull-up (normally) or a pull-down resistor (to force the link pass). Following Rst* deassertion, this pin becomes an output (unused - value is undefined). |  |

| EnDev*         | I    | <b>Enable Device:</b> Active low. Enables serial and PCI ports. When asserted, all serial ports and the PCI port are active. When deasserted, both the ports and the PCI interface are disabled. This function may be also controlled by software via the Control Register.                                                                                                                                                                                                                                                                          |  |

| DisWD*         | I    | <b>Disable Watchdog timer:</b> Active low. When asserted the Tx Watchdog timers operation is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| EnELScrub*     | I    | <b>Enable Empty List Scrubing:</b> Active low. When asserted, the empty list scrubbing mechanism is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                |      | For testing purposes only. Must be pulled HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SkipInit*      | I    | <b>Skip Initialization:</b> Active low. When asserted, the GT-48002 skips the Address Table initialization sequence. This pin is used only for testing and should be driven high for normal operation.                                                                                                                                                                                                                                                                                                                                               |  |

| Scan*          | I    | <b>Scan:</b> This pin together with TriState* indicates the GT-48002 mode of operation as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                |      | Scan* = 1, TriState* = 1 - Normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                |      | Scan* = 0, TriState* = 1 - Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                |      | Scan* = 1, TriState* = 0 - The GT-48002 drives all outputs and I/O pins to High impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                |      | Scan* = 0, TriState* = 0 - Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| TriState*      | I    | <b>Tri State:</b> This pin together with Scan* indicates the GT-48002 mode of operation as described above.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

#### 2 FUNCTIONAL DESCRIPTION

## 2.1 General Description

The GT-48002 provides the switching functions between two 10/100 Mbps Ethernet ports. The GT-48002 has three interfaces:

- a) Two 10/100 Mbps Ethernet ports that interface directly to the MII ports.

- b) 32-bit DRAM to store the Address Table and the incoming/outgoing packets.

- c) PCI bus for switch expansion, connectivity, and management.

The GT-48002 receives the incoming packets from the MII, searches in the Address Table the Destination Address and forwards the packet to the appropriate port. The port can be either local or in different GT-48001/2 devices that reside on the same PCI bus. In parallel, the GT-48002 checks the Source Address and updates all the Address Tables in the system accordingly.

The GT-48002 uses a simple protocol on the PCI, consisting of 5 messages. This protocol is an essential part of the GalNet<sup>TM</sup> architecture. The 5 messages are: 'new\_address', 'buffer\_request', 'start\_of\_packet', 'packet\_transfer', and 'end\_of\_packet'.

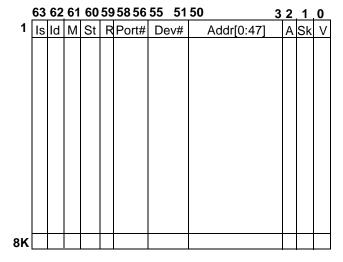

#### 2.2 Address Table

The GT-48002 supports up to 8K different MAC addresses. The Address Table is located in the DRAM and is fully controlled by the GT-48002 (i.e. a new address is automatically added to the Address Table). The CPU has the ability to insert, remove or modify the entries. Figure 1 shows the Address Table structure.

Figure 1. Address Table Structure

| Bit   | Description                                                                                                                                                |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V     | Valid - Indicates that the entry is valid<br>0 - Not Valid<br>1 - Valid                                                                                    |  |

| Sk    | Skip - Skip this entry, used to delete an entry 0 - Don't skip this entry 1 - Skip this entry                                                              |  |

| Α     | Aging - This bit is used for the Aging process Set by the GT-48002 upon receiving a packet from the station corresponding to this entry Cleared by the CPU |  |

| Addr  | Address - 48 bits of MAC address.                                                                                                                          |  |

| Dev#  | Device Number - Indicates which of a maximum of 32 devices in the system is associated with this address.                                                  |  |

| Port# | Port Number - Indicates which of the two ports in a GT-48002 is associated with this address.                                                              |  |

| R     | Reserved                                                                                                                                                   |  |

| St    | Static - Indicates whether an entry can be modified or not. 0 - The entry can be modified 1 - The entry is static. The Dev# and Port# cannot be modified   |  |

| M     | Multiple - Meaningful when bit St is set.  0 - Forward this packet only to the destination port  1 - Forward this packet to all ports (as Unknown)         |  |

| ld    | Intervention for Destination Addresses 0 - Don't activate the Intervention mode 1 - Activate the Intervention mode                                         |  |

| ls    | Intervention for Source Addresses 0 - Don't activate the Intervention mode 1 - Activate the Intervention mode                                              |  |

## 2.2.1 Learning Process

The GT-48002 has a self-learning mechanism. It learns the Ethernet addresses in real time. The GT-48002 searches for the Source Address (SA) in the Address Table and acts as follows:

1. If the SA was not found in the table (a new address), the GT-48002 waits to the end of the packet (good CRC) and updates its Address Table. It also notifies the other GT-48001/2 devices and the CPU by sending a

'new\_address' message on the PCI interface. The message contains the MAC address, the Device Number and the Port Number (the message format is described in section 2.10). In addition, the GT-48002 asserts Int\* to notify the CPU that the Address Table was modified.

- 2. If the SA was found, the GT-48002 compares the Port Number and the Device Number to the device and Port Numbers on which the packet was received. If they are different, and the St bit in the Address Table is cleared, it updates the entry with the new information and notifies the other GT-48001/2 devices and the CPU. If they are equal, no action is taken.

- 3. If the SA was found in the Address Table, the Aging bit is set.

The CPU can access the Address Table to modify, remove or to add a MAC address. This is done by performing a 'new\_address' message on the PCI.

#### 2.2.2 Address Recognition

The GT-48002 forwards the incoming packets to the appropriate ports(s) according to Destination Address (DA) as follows:

- 1. If the DA is a Unicast address and the address was found, the GT-48002 acts as follows:

- If the Port Number and the Device Number are equal to the Port/Device on which the packet was received, the packet is discarded.

- If the Port Number is different, but the Device Number is equal, the packet is forwarded to the appropriate local port.

- If the Device Number is different, the packet is forwarded to the appropriate GT-48001/2 device via the PCI bus.

- 2. If the DA is a Unicast address and the address was not found (Unknown), the GT-48002 acts as if it is a Multicast packet. This packet is forwarded to the ports (except for the port in which the packet was received) and the devices which were programmed for forwarding of unknown packets (bit 7 in the Port Control registers).

- 3. If the DA is a Multicast address, the packet is forwarded to all the local ports (except for the port in which the packet was received). It is also forwarded to all other GalNet™ devices via the PCI bus.

#### 2.2.3 Recovery Process

The purpose of the Recovery Process is to guarantee that Address Tables in all the devices will be similar.

When the packet is Unknown, the source GT-48002 sends a 'new\_address' message to all the devices. Each device searches its own table for the new address. More than one device can find the address, but only one device owns this address (i.e. the Device Number written in the Address Table for that address is equal to its own Device Number). This particular device updates the source GT-48002 Address Table with the new address (by sending it and only it a 'new\_address' message).

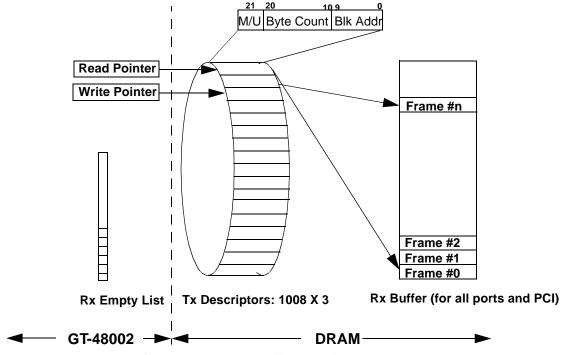

### 2.3 GT-48002 Buffers and Queues

The GT-48002 incorporates three transmit queues (for the 2 local ports and the PCI), and one common receive buffer. Figure 2 shows the GT-48002 queues. The receive buffers as well as the transmit queues are located in the DRAM. The GT-48002 includes the pointers to the transmit queues. The GT-48002 data structure components are the following:

- 1. Receive Buffer A common Rx buffer for all ports. The common Rx buffer is divided into 320 or 1008 separate buffers (depending on the DRAM size) of 1.5KBytes (1536 bytes) each. Each separate buffer contains the whole packet information.

- 2. Rx Empty List A list of 320 or 1008 bits. Each bit contains the status of its appropriate receive buffer in the DRAM (empty or occupied).

- 3. Tx Descriptors A set of 3 transmit descriptor rings. Each ring contains 1008 descriptors. The descriptor size is 1 Long Word (32-bits) and contains the Buffer Address divided by 600hex (1.5K), the Byte Count and the Packet Type (Multicast or Unicast).

- 4. Read/Write Pointers 3 pairs of pointers to the transmit descriptors.

#### 2.4 Packet Forwarding

The following chapter describes the procedures for forwarding packets between local ports, between GT-48001/2 devices, and between the CPU and a GT-48002.

#### 2.4.1 Forwarding a Unicast Packet to a Local Port

The sequence is as follows:

1. The incoming packet is fed to the Receive FIFO (there is a 20x32-bit FIFO per port) and is transferred to an empty block in the DRAM in 8 32-bit bursts.

Figure 2 - GT-48002 Buffers and Queues

- 2. In parallel, an address recognition cycle is performed for both the DA and the SA. The GT-48002 uses the DA's Port Number and Device Number to queue the packet to the appropriate port.

- 3. At the end of a good packet transfer, the packet is forwarded to the appropriate transmit queue. This is done by writing the Byte Count and the Block Address to the Tx Descriptor which is pointed to by the Write Pointer.

- 4. The Write Pointer is incremented. The GT-48002 transmits when the Write Pointer is not equal to the Read Pointer.

- 5. At the end of the packet transmit process, the GT-48002 increments the Read Pointer and clears the appropriate bit in the Empty List.

# 2.4.2 Forwarding a Unicast Packet to a Port in a Different Device

The sequence is as follows:

- 1. The incoming packet is fed to the Receive FIFO and transferred to an empty block in the DRAM in 8 32-bit bursts.

- 2. In parallel, an address recognition cycle is performed for both the DA and the SA. The GT-48002 uses the DA's Port Number and Device Number to queue the packet to the appropriate GT-48002 device and port.

- 3. At the end of a good packet transfer, the packet is entered into the PCI transmit queue (the third queue). This is done by writing the packet information to the PCI transfer request descriptor which is pointed to by the Write Pointer. When the Write Pointer is not equal to the Read Pointer, the source device sends a 'buffer\_request' message to the appropriate target device indicating that there is a packet for transmission.

- 4. The target device allocates a buffer in its DRAM and sends a 'start\_of\_packet' message to the source device.

- 5. The source device transfers the packet using PCI master operations in 8 32-bit bursts. At the end of the packet, the source device performs an additional write transaction ('end\_of\_packet' message) and places on the PCI the Byte Count, the target Port Number, the Receive Block address, and the Packet Type. It also frees its packet buffer by clearing the appropriate bit in its Empty List

- 6. The packet is entered to the appropriate transmit queue in the target device. This is done by writing the Byte Count and the Rx Buffer address to the Tx Descriptor which is pointed to by the Write Pointer.

- 7. The Write Pointer is incremented. The target GT-48002 transmits when the Write Pointer is not equal to the Read Pointer.

8. At the end of the packet transmit process, the GT-48002 increments the Read Pointer and frees its packet buffer by clearing the appropriate bit in its Empty List.

#### 2.4.3 Forwarding a Multicast Packet

The GT-48002 forwards the Multicast packets to all the ports and devices using the same mechanism as in Unicast packets. The packet is queued to all local transmit ports except for the port in which the packet arrived. All the GT-48001/2 devices in the system receive a 'buffer\_request' message, allocate a buffer in their DRAM and send back a 'start\_of\_packet' message. The packet is transferred separately to each GT-48001/2 device in the system.

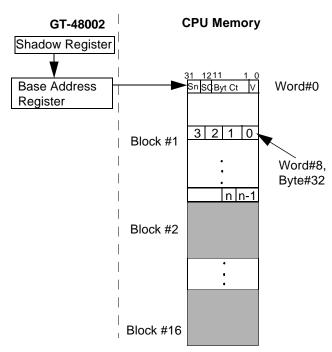

#### 2.4.4 Forwarding a Packet to the CPU

The GT-48002 forwards the packets directly to the CPU main memory. The GT-48002 contains two pointers to a sixteen block buffer area in the memory (Shadow and Base Address). Figure 3 shows the data structure in the CPU main memory.

Figure 3 - CPU Data Structure

The data structure components are the following:

- 1. Base Address Register A register that points to the beginning of a sixteen block area in the CPU main memory.

- 2. Shadow Register A second register that holds a pointer to a second sixteen block area in the CPU main memory. The value in the Shadow register propagates into the Base Address register after sixteen packets are transferred to the main memory.

- 3. Buffer Area It consists of 16 blocks of 2Kbytes each. The first word in the block contains the Byte Count (bits [11:1]), Source Channel (bit 12), Sniffer bit (bit 13) and a Valid bit (bit 0). The Source Channel, Byte Count and the Valid bit are written at the end of the packet transfer. Bit [31] is the Sniffer bit and will be set to '1' to mark a sniffer packet when the CPU is configured as the target sniffer. Words 1 to 7 are left empty for user purposes. The packet data is written starting the first byte in the 8th word (32nd byte).

The communication between the GT-48002 and the CPU follows this sequence:

- 1. CPU updates the Base Address register

- 2. CPU updates the Shadow Register. The Shadow register is loaded when the CPU writes to the same address of the Base Address register, after it was written into. (Reading the value from the Base Address register address will result with the last value written).

- 3. GT-48002 transfers 16 packets to the CPU main memory and asserts the Int\* at the end of each packet transfer

- 4. The CPU counts sixteen interrupts and updates the Shadow register.

Steps 3-4 are repeated. The packet transfer to the CPU is done as follows:

- 1. The incoming packet is fed to the Receive FIFO and is transferred to an empty block in the DRAM in 4 32-bit bursts.

- 2. In parallel, an address recognition cycle is performed for both the DA and the SA. The GT-48002 uses the DA's Port Number and Device Number to queue the packet to the appropriate device and port.

- 3. At the end of a good packet transfer, the packet is entered into the PCI transmit queue. This is done by writing the packet information to the PCI transfer request descriptor which is pointed to by the Write Pointer. When the Write Pointer is not equal to the Read Pointer, the source device transfers the packet to the appropriate block in the CPU main memory. The data is entered into the 8th word (32nd byte). Words 1 to 7 are left empty for user purposes.

4. At the end of the packet transfer, the GT-48002 writes the Byte Count and the Valid bit to the first word of the block. It also sends an interrupt via Int\* to the CPU and increments the Read Pointer and clears the appropriate bit in its Empty List.

#### 2.4.5 Receiving a Packet from the CPU

The CPU forwards a packet to the ports using the same mechanism as the other GT-48002 devices with one exception. The 'start\_of\_packet' message from the target device to the CPU is transferred directly to the CPU main memory. The GT-48002 holds a Start of Packet Base Address register which points to a buffer area in the CPU main memory. The buffer area can hold up to 32 'start\_of\_packet' messages.

## 2.5 Tx Watchdog Timer

The GT-48002 holds a Transmit Watchdog timer for each transmit queue. For 100 Mbps operation, the default value of the timer is 63msec and the range is between 10.5mSec to 168msec, in 10.5 mSec steps. For 10 Mbps operation, the default value of the timer is 630msec and the range is between 105mSec to 1680msec, in 105 mSec steps. The timer measures the time between two consecutive packets which are being served. When the timer expires, the GT-48002 clears the appropriate used blocks and sends an interrupt to the CPU by asserting Int\*.

## 2.6 GT-48002 Device Table

The GT-48002 includes a 32-bit Device Table. Each bit in the table represents a different GT-48001/2 device in the system. Upon reset, each GT-48001/2 sets all the bits to '1'. The bits are cleared either by the CPU or upon PCI master abort (meaning that the GT-48002 tried to access a non-existent device). The Device Table is used by the GT-48002 to know whether or not to transfer a multicast address or new address to the target device. Bit 0 in the Device Table register corresponds to Device#0, etc.

## 2.7 Intervention Mode

The GT-48002 supports a powerful mode named Intervention Mode, which permits software or hardware intervention in the packet routing decision mechanisms. Intervention mode handles Multicast and Unicast packets differently as shown below.

#### 2.7.1 Multicast Packets

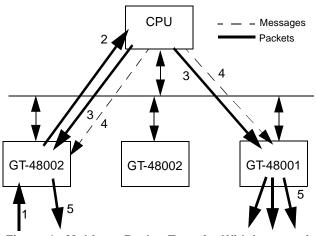

When the routing Intervention option is set for Multicast packets, all Multicast packets will be forwarded to the CPU memory. The CPU can decide to what ports the packets need to be sent. Only one packet needs to be sent to each GT-48002 device and each GT-48002 will automatically forward the packet only to the ports that the CPU tagged for that specific Multicast packet. These ports are tagged in bits [29:22] at the 'end\_of\_packet' message. The GT-48002 will enter the routing Intervention mode when bit 22 in the Global Control register is set. Figure 4 illustrates a Multicast packet transfer in routing Intervention mode.

Figure 4 - Multicast Packet Transfer With Intervention

The sequence illustrated is as follows:

- a. The Multicast packet is received and stored in the source GT-48002's DRAM (arrow #1).

- b. The GT-48002 transfers the packet to the CPU main memory (arrow #2).

- c. The CPU transfers the packet to the selected GT-48001/2 devices (arrows #3).

- d. At the end of the packet transfer, the CPU sends an 'end\_of\_packet' message to tag the selected ports in which the packets will be transmitted (arrows #4).

- e. The packet is transmitted on the selected ports (arrows #5).

#### 2.7.2 Unicast Packets

Intervention in Unicast traffic is optional per MAC address (either Source or Destination Address). The entry in the Address Table includes two Intervention bits, one for the Source Address (bit 63) and one for the Destination

Address (bit 62). The Intervention mode can be activated based on Source Addresses, Destination Addresses or both. When one of the Intervention bits is set, the GT-48002 will not forward the packet automatically to the destination device. Instead, it will send a 'buffer\_request' message to the CPU memory. The 'buffer\_request' includes information about the routing of the packet (Source and Target port/device numbers). The CPU can have the following options: it can discard the packet, it can send a 'buffer\_request' to the destination GT-48001/2 or any other device to take the packet, or it can request the entire packet information (data and headers) and modify it.

The 'buffer\_request' messages will be sent to the buffer area in the CPU main memory which contains 256 entries of dual 32-bit words. The buffer area is pointed to by a Base Address register and a Shadow register.

Figure 6 shows a Unicast packet transfer in the Intervention mode.

Figure 5 - Unicast Packet Transfer With Intervention

The sequence illustrated is as follows:

- a. The Unicast packet is received and stored in the source GT-48002's memory (arrow #1).

- b. If one of the Intervention bits is set, the GT-48002 sends a 'buffer\_request' to the CPU (arrow #2). The 'buffer\_request' includes the source port and the destination port/device.

The CPU then has the following options:

- Discard the packet (arrow #3). The CPU sends a

'start\_of\_packet' message with the Byte Count field cleared.

- Forward the packet to a destination device (arrow #4). The CPU sends a 'buffer\_request' to the destination device. The destination device allocates a buffer and sends a 'start\_of\_packet' message to the source GT-48002 (arrow #5). The source GT-48002 device transfers the packet followed by an 'end\_of\_packet' message (arrow #6).

- Take the packet. The CPU sends a 'start of packet' message. The target device in the message is the CPU number. The source GT-48002 device sends the packet followed by an 'end\_of\_packet' message directly to the CPU main memory (arrow #7).

#### 2.8 Management Support

The GT-48002 supports the following management features:

- · MIB and PCI counters

- · Station-to-Station connectivity matrix

- Monitoring (Sniffer)

- Spanning Tree

#### 2.8.1 Repeater MIB and PCI Counters

The GT-48002 incorporates a full set of MIB counters per port, as well as PCI counters. The PCI counters are global for the two ports. The CPU periodically reads the counters which are then cleared automatically by the GT-48002 following the READ operation. The Repeater MIB counters are the following:

- · Bytes Received

- Bytes Sent

- Frames Received

- Frames Sent

- Total Bytes Received (Good and Bad)

- Total Frames Received (Good and Bad)

- Multicast Frames Received

- Broadcast Frames Received

- CRC + Alignment Error

- Oversize Frames

- Fragments

- Jabber Frames

- Collision

- Late Collision

- Frames with length of 64 Bytes

- Frames with length of between 65-127 Bytes

- Frames with length of between 128-255 Bytes

- Frames with length of between 256-511 Bytes

- Frames with length of between 512-1023 Bytes

- Frames with length of between 1024-1522 Bytes

- MAC Rx Error (received packets with RxEr asserted)

- Dropped Frames

The global PCI counters are:

- · PCI Frames Received

- PCI Frames Sent

#### 2.8.2 Station-to-Station Connectivity Matrix

The GT-48002 provides a mechanism to record the Destination Address, Source Address and the Byte Count of all the forwarding packets in an external FIFO for RMON support. The FIFO is connected to the DRAM's data lines and controlled directly by the GT-48002. The GT-48002 asserts the ChipSel\* pin, and reads in two consecutive transactions the Destination Address and Source Address (a burst read of 3 32-bit words) and Byte Count (a single 32-bit read).

#### 2.8.3 Monitoring (Sniffer) Mode

The CPU can program the GT-48002 to work in Monitoring mode in one of its ports. This is done by setting bit 2 in the Port Control register. In this mode, the GT-48002 sends all receive (including local traffic) and transmit packets to the CPU or to a port in one of the GT-48001/2 devices which was assigned to be the target Sniffer. To assign a port to be the target Sniffer, you must:

- 1. Write the target Sniffer Device Number and Port Number in all GT-48001/2 devices' CPU and Sniffer Numbers Register (Offset: 0x140030).

- 2. Set bit 9 of all GT-48001/2 devices' Global Control Register to 1 to indicate a GT-48001/2 port will be used as the Sniffer.

- 3. Enable Sniffer mode in the target Sniffer device(s) ONLY by setting bit 2 in the Port Control Register.

The packets that are forwarded to the Sniffer are not in a linear order.

#### 2.8.4 Spanning Tree Support

The GT-48002 provides the required hardware assistance for Spanning Tree algorithm implementation. The Spanning Tree algorithm is performed by the CPU.

The GT-48002 holds a SpanEn bit in the Global Control register and additional SpanEn bits in each of the Port Control registers. The following table summarizes the hardware assistance for the Spanning Tree algorithm and the treatment of Bridge Protocol Data Units (BPDU).

| SpanEn<br>(Global) | SpanEn<br>(Port) | Logic<br>State                           | Remarks                                                                                                                        |

|--------------------|------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 0                  | Х                | Port<br>Enable                           | No Spanning Tree.<br>Treat BPDU as<br>regular Multicast                                                                        |

| 1                  | 1                | Blocking,<br>Listen-<br>ing,<br>Learning | Transfer BPDUs to the CPU. All receive/trans- mit packets should be rejected. Accept BPDUs from the CPU. No address learn- ing |

| 1                  | 0                | Forward                                  | Transfer BPDUs<br>to the CPU.<br>Accept all packets.<br>Address learning                                                       |

The GT-48002 does not learn during the traditional 'Learning' stage. It only starts learning during the Forward stage.

#### 2.9 Serial Interfaces

The GT-48002 interfaces directly to two MII (Media Independent Interface) ports which are compliant with the IEEE 802.3u Fast Ethernet standard. Each MII port has the following characteristics:

- Capable of supporting both 10 Mb/s and 100 Mb/s data rates in half or full duplex modes

- Data and delimiters are synchronous to clock references

- Provides independent 4-bit wide transmit and receive paths

- Uses TTL signal levels

- Provides a simple management interface (common to all ports)

- · Capable of driving a limited length of shielded

cable

#### 2.9.1 10/100 Mbps MII Compatible Interface

The GT-48002 MAC allows it to be connected to a 10 or 100Mbps network. The GT-48002 interfaces to an IEEE 802.3 10/100 Mbps MII compatible PHY device. The data path consists of a separate nibble-wide stream for both transmit and receive activities. The GT-48002 can switch automatically between 10 or 100 Mbps operation depending on the speed of the network. Data transfers are clocked by the 25 MHz transmit and receive clocks in 100 Mbps operation, or by 2.5 MHz transmit and receive clocks in 10 Mbps operation. The clock inputs are driven by the PHY, which controls the clock rate based on autonegotiation.

The GT-48002 MAC performs all of the functions of the 802.3 protocol such as frame formatting, frame stripping, collision handling, deferral to link traffic, etc. The GT-48002 ensures the any outgoing packet complies with the 802.3 specification in terms of preamble structure. The GT-48002 transmits 56 preamble bits before Start of Frame Delimiter (SFD). The MAC can also be placed in a Full-duplex mode which allows for simultaneous transmission and reception of frames.

#### 2.9.2 10/100 Mbps MII Transmission

When the GT-48002 has a frame ready for transmission, it samples the link activity. If the CrS signal is inactive (no activity on the link), and the Inter Frame Gap (IFG) counter has expired, frame transmission begins. The IFG default value is 96 bit times, and can be programmed by the CPU. The data is transmitted via pins TxD[3:0] of the transmitting port, clocked on the rising edge of TxClk. The signal TxEn is asserted at this same time. In the case of collision, the PHY asserts the CoL signal on the GT-48002 which will then stop transmitting the frame and append a jam sequence onto the link. After the end of a collided transmission, the GT-48002 will back off and attempt to retransmit once the backoff counter expires.

The GT-48002 implements the truncated exponential backoff algorithm defined by the 802.3 standard. After 16 consecutive retransmit trials, the GT-48002 resets its collision counter and restarts the backoff algorithm, and continues to try and retransmit the frame. The retransmission is done from the data already stored in the DRAM. In the case of a successful transmission, the GT-

48002 is ready to transmit any other frames queued in its transmit FIFO within the minimum IFG of the link.

The GT-48002 implements a programmable data blinder with default value of 32 bits before the end of the IFG. The IFG counter starts to time the interframe gap as soon as transmitting and carrier sense are both false. When timing the interframe gap, the IFG counter is reset if carrier is detected during the first part of the interframe gap before entering the data blinder zone. During the data blinder zone, the IFG counter will not be reset to ensure fair access to the medium.

Any one of the GT-48002 MII ports can be automatically partitioned under excessive duration or frequency of collision conditions, if the partition function is enabled in the GT-48002 control register (the default is partition disabled). The GT-48002 will continue to transmit data packets to a partitioned port, but will not respond to activity on the partitioned port's receive lines. The GT-48002 will continue to monitor the port and reconnect it once certain criteria indicating port 'wellness' are met. The criteria for partition/reconnection are specified by the 802.3 standard. Each GT-48002 port, is partitioned and/or reconnected separately and independently of other network ports.

#### 2.9.3 10/100 Mbps MII Reception

Frame reception starts with the assertion of CrS (while the GT-48002 is not transmitting) by the PHY. Once RxDV is asserted, the GT-48002 will begin sampling incoming data on pins RxDV[3:0] on the rising edge of RxClk. Reception ends when the RxDV is deasserted by the PHY. The last nibble sampled by the GT-48002 is the nibble present on RxD[3:0] on the last RxClk rising edge in which RxDV is still asserted. During reception, the RxDV is asserted. If, while RxDV is asserted, the GT-48002 detects the assertion of RxEr, it will designate this frame as a corrupted frame. While no reception is taking place, RxDV should remain deasserted.

#### 2.9.4 10/100 Mbps Full-Duplex Operation

When operating in Full-duplex mode the GT-48002 can transmit and receive frames simultaneously. In full-duplex mode, the CrS signal is associated with received frames only and has no effect on transmitted frames. The Col signal is ignored by the GT-48002 while in Full-duplex mode. Transmission starts when TxEn goes active. Transmission starts regardless of the state of CrS. Reception starts when the CrS signal is asserted indicating traffic on the receive port of the PHY.

## 2.9.5 MII Management Interface (SMI)

The GT-48002 MAC contains an MII Management Interface (SMI) to an MII compliant PHY. This allows control and status parameters to be passed between the GT-48002 and the PHY (parameters specified by the CPU) by one serial pin (MDIO) and a clocking pin (MDC), reducing the number of control pins required for PHY mode control. Typically, the GT-48002 will continuously query the PHY devices for their link status, without CPU intervention. The predefined PHY addresses for the link query are 1 and 2 (out of possible 32 addresses). This protocol conforms with the National DP83840 PHY device as well as other available PHYs.

A CPU connected to the GT-48002 can Write/Read to/ from all PHY addresses/registers, by writing and reading to/from a dedicated set of GT-48002 SMI control registers. The SMI allows the CPU to have direct control over an MII-compatible PHY device via the GT-48002 SMI control register. This allows the driver software to place the PHY in specific modes such as Full Duplex, Loopback, Power Down, 10/100 speed selection as well as control of the PHY device's Auto Negotiation function if it exists. The CPU writes commands to the GT-48002 SMI register and the GT-48002 reads or writes control/status parameters to the PHY device via a serial, bi-directional data pin called MDIO. These serial data transfers are clocked by the GT-48002 MDC clock output.

#### 2.9.6 SMI Cycles

The SMI protocol consists of a bit stream that is driven or sampled by the GT-48002 on each rising edge of the MDC clock. The bit stream format of the SMI frame is described in the table below:

|    | PRE | ST | OP | PhyAd | RegAd | TA | Data   | IDL<br>E |

|----|-----|----|----|-------|-------|----|--------|----------|

| RD | 11  | 01 | 10 | AAAAA | RRRRR | Z0 | DD(32) | Z        |

| WR | 11  | 01 | 01 | AAAAA | RRRRR | 10 | DD(32) | Z        |

PRE (Preamble) - At the beginning of each transaction, the GT-48002 sends a sequence of 32 contiguous logic one bits on MDIO with 32 corresponding cycles on MDC to provide the PHY with a pattern that it can use to establish synchronization.

ST (Start of Frame) - A Start of Frame pattern of 01

OP (Operation Code) - 10 - READ; 01 - WRITE

PhyAd (PHY Address) - A 5 bit address of the PHY device, allowing 32 unique PHY addresses. The first PHY address bit transmitted by the GT-48002 is the MSB of the address.

RegAd (Register Address) - A 5 bit address of the PHY register, allowing 32 individual registers to be addressed withing each PHY. The first register address bit transmitted by the GT-48002 is the MSB of the address. The GT-48002 always queries the PHY device for status of the link by reading register #00001 bit #2.

TA (TurnAround) - The turnaround time is a 2 bit time spacing between the Register Address field and the Data field of the SMI frame to avoid contention during a READ transaction. During a READ transaction the PHY should not drive MDIO in the first bit time and drive '0' in the second bit time. During a WRITE transaction, the GT-48002 drives a '10' pattern to fill the TA time.

Data (Data) - The data field is 16 bits long. The PHY drives the data field during READ transactions. The GT-48002 drives the data field during WRITE transactions. The first data bit transmitted and received shall be but 15 of the PHY register being addressed.

IDLE (Idle) - The IDLE condition on MDIO is a high impedance state. The MDIO driver is disabled and the PHY should pull-up the MDIO line to a logic one.

# 2.9.7 Link Detection and Link Detection Bypass (ForceLinkPass\*)

Typically, the GT-48002 will continuously query the PHY devices for their link status, without CPU intervention. The predefined PHY addresses for the link query are 1 and 2 (out of possible 32 addresses). The GT-48002 will alternately read register#1 from PHY#1 and PHY#2 and update the internal link bits according to the value of bit#2 of register#1. In the case of "link is down" (i.e. bit#2 is '0'), that port will enter link test fail state. In this state, all of the port's logic is reset. The port will exit from link test fail state only when the "link is up" i.e. bit#2 of register#1 is read from the port's PHY as '1'.

The GT-48002 offers the option to disable this link detection mechanism by forcing the link state of both ports to the link test pass state. This is done by connecting the ForceLinkPass\* input to a pull-down resistor. This pin is sampled at reset. When connected to pullup, The link status of the ports is read through the SMI from the PHY devices (register#1, bit#2). When connected to a pull-down, the link status of all ports remains in the "link is up" state regardless of the PHY's link bit value.

#### 2.9.8 LED Support

#### 2.9.8.1 LED Interface General Description

The GT-48002 supports two types of LED interfaces: a serial interface and a parallel interface. The serial LED interface is similar to the 3-pin LED interface of the GT-48001 device. The parallel interface offers the LED information directly on the device outputs. An external driver is required to drive the LEDs. The GT-48002 supports two modes of port status information display selectable via the LEDMode input.

The basic accessable data via the LED interface is:

- Port Status (two modes of operation)

- Transmit data in progress (TxEn)

- Receive data in progress (RxDV)

- Collision active (Col)

- Forwarding of Unknown packets enabled

- Port configured as Sniffer

- Full/Half Duplex

- Receive Buffer Full

#### 2.9.8.2 Detailed LED Signal Description

- 1. Primary Port Status LED: Port Status LED indicates the port status in two operation modes selectable via the LEDMode input:

- 1.1. Primary Port Status LED in Mode 0: (LEDMode input is LOW)

At this mode, the Port Status LED provides the following information:

- · if Port is disabled Port Status LED is OFF

- else if Link Integrity test failed Port Status LED blinks once

- else if Partition State detected Port Status LED blinks twice

- else Everything is OK Port Status LED is ON

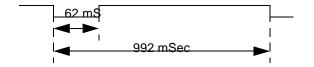

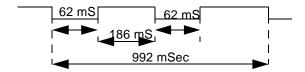

Status LED blink timing (MODE 0)

Link Integrity test failed - Status LED blinks once

\* status bit is active for 62 mS every 992 mS

Partition - Status LED blinks twice

\* status bit is activated twice every 992 mS for 62 mS each time, with a period of 186 mS between two consequtive activations.

1.2. Primary Port Status LED in Mode 1: (LEDMode input is HIGH)

At this mode, the Port Status LED initially displays the port link status information (indication type A) and then switches to reflect the port trafic (Transmit or Receive) activity (indication type B). The switching between the two types of indications is as follows:

Indication type A: The Port Status LED indicates the port link status for a period of about 3 to 3.5 seconds (active - link is up, inactive - link is down) following any of the events below:

- · RESET deassertion

- · transition from link down to link up

Following this time period, the Port Status LED will switch to indication type B. In the case that the link is down, the Port Status LED will remain inactive and will not switch to indication type b.

Indication type b: The Port Status LED indicates the port trafic (Transmit or Receive) activity which is a logical OR of the TxEn active and RxDV active dynamic signals. The "monostable" function is applied to this indication type so the LED can be viewed for a period of about 62 mS for LedMode=0 or for about 7.5 mS for LedMode=1, per each trafic activity. The Port Status LED will switch to indication type a on the following cases:

- RESET assertion

- transition from link up to link down

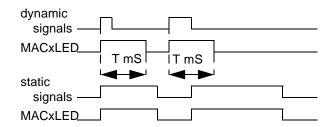

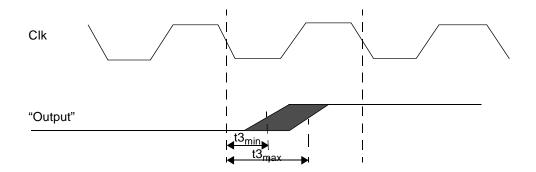

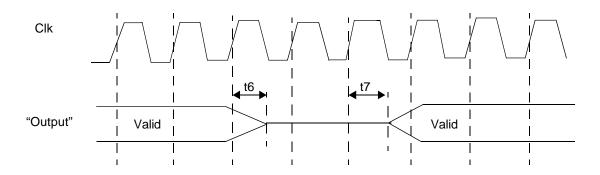

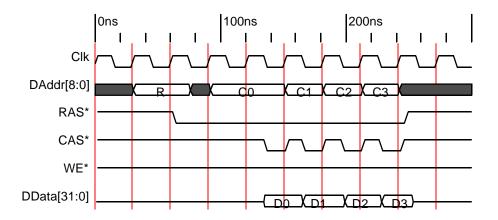

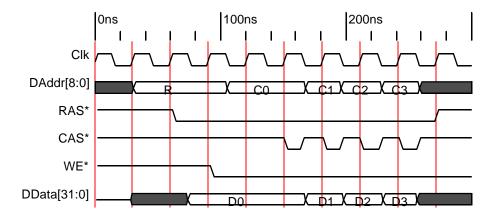

- 3. Transmit data in progress (TxEn): This signal indicates the port transmit activity (TxEn output is active)