# GENLINX ™II GS9024 Automatic Cable Equalizer

DATA SHEET

#### **FEATURES**

- · automatic cable equalization

- fully compatible with SMPTE 259M

- typically equalizes greater than 350m of high quality cable at 270Mb/s

- · signal strength indicator

- · output data muting when input data is lost

- output 'eye' monitor (OEM) with large signal amplitude and power down option

- low power: 240mW at 5V

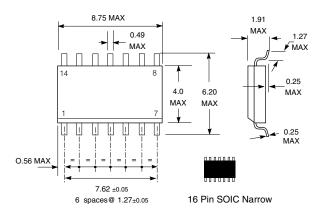

- 14 pin SOIC package

- programmable output data squelch for max cable length limiting

- · carrier detect with programmable threshold level

- serial data output "High Z" select to allow muxing of EQ inputs

### **APPLICATIONS**

Front-end cable equalization for digital video systems; Input equalization for serial digital distribution amplifiers, routers, production switchers and other receiving equipment.

#### DESCRIPTION

The GS9024 is a high performance automatic cable equalizer designed for serial digital data rates from 143Mb/s to 540Mb/s. The GS9024 receives either single-ended or differential serial data and outputs equalized differential signals at PECL levels (800mV). The GS9024 provides up to 40dB of gain at 200MHz which will typically result in equalization of greater than 350m at 270Mb/s of Belden 8281 cable.

The GS9024 incorporates an analog signal strength indicator/ carrier detect (SSI/CD) output indicating both the presence of a carrier and the amount of equalization applied to the signal. Optional external resistors allow the carrier detect threshold level to be customized to the user's requirement.

The GS9024 also features selectable High Z serial data outputs eliminating the need for input muxing circuitry in routers. In addition, the GS9024 provides an 'Output Eye Monitor' (OEM) which allows the verification of signal integrity after equalization, prior to reslicing.

The GS9024 operates from a single +5V or -5V power supply and consumes only 240mW of power. Packaged in a small 14 pin SOIC, the GS9024 is ideal for router applications where high density component placement is required.

### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE          | TEMPERATURE |  |  |

|-------------|------------------|-------------|--|--|

| GS9024-CKB  | 14 pin SOIC      | 0°C to 70°C |  |  |

| GS9024-CTB  | 14 pin SOIC Tape | 0°C to 70°C |  |  |

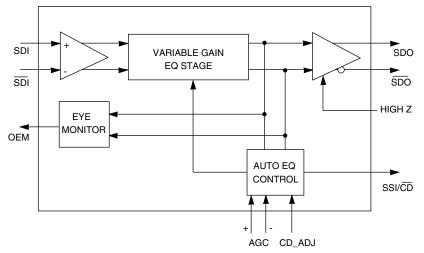

**BLOCK DIAGRAM**

Revision Date: December 1999 Document No. 521 - 70 - 05

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                            | VALUE                                |

|--------------------------------------|--------------------------------------|

| Supply Voltage                       | 5.5V                                 |

| Input Voltage Range (any input)      | $V_{CC}$ +0.5 to $V_{EE}$ -0.5V      |

| Operating Temperature Range          | $0^{\circ}C \le T_A \le 70^{\circ}C$ |

| Storage Temperature Range            | -65°C ≤ T <sub>S</sub> ≤ 150°C       |

| Lead Temperature (soldering, 10 sec) | 260°C                                |

## DC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = 5V,  $V_{EE}$  = 0V,  $T_A$  = 0°C TO 70°C unless otherwise shown.

| PARAMETER                      | SYMBOL              | CONDITIONS                         | MIN  | TYP <sup>1</sup> | MAX  | UNITS | NOTES | TEST<br>LEVEL |

|--------------------------------|---------------------|------------------------------------|------|------------------|------|-------|-------|---------------|

| Supply Voltage                 | V <sub>CC</sub>     |                                    | 4.75 | 5.0              | 5.25 | V     |       |               |

| Power Consumption              | P <sub>D</sub>      |                                    | -    | 240              | -    | mW    |       | 3             |

|                                |                     | with OEM active                    | -    | 340              | -    | mW    |       | 3             |

| Supply Current                 | $I_{\mathbb{S}}$    |                                    | -    | 44               | -    | mA    |       | 1             |

|                                |                     | with OEM active                    | -    | 58               | -    | mA    |       | 1             |

| Serial Data O/P Current        | $I_{SDO}$           | $R_L = 75\Omega$                   | -    | 11               | -    | mA    |       | 3             |

| SDI/SDI Common Mode<br>Voltage |                     |                                    | -    | 2.5              | -    | V     |       | 1             |

| AGC+/AGC- Mode<br>Voltage      |                     |                                    | -    | 2.7              | -    | V     |       | 1             |

| OEM Bias Potential             |                     |                                    | -    | 4.5              | -    | V     |       | 1             |

| SSI/CD Output Current          | I <sub>SOURCE</sub> | $C_{LMAX} = 50pF$ $R_L = \infty$   | -    | -                | 18   | μΑ    |       |               |

|                                |                     | $C_{LMAX} = 50pF$ $R_L = 5k\Omega$ | -    | -                | 110  | μΑ    |       |               |

|                                | I <sub>SINK</sub>   |                                    | -    | 1.0              | 1.5  | mA    |       |               |

| High Z Input Voltage           | V <sub>HIGH</sub>   |                                    | 2.4  | -                | -    | V     |       | 1             |

|                                | $V_{LOW}$           |                                    | -    | -                | 0.8  | V     |       | 1             |

### TEST LEVELS

- 1. 100% tested at 25°C.

- 2. Guaranteed by design.

- 3. Inferred or co-related value.

### NOTES

1. Typical values are parametric norms at 25°C.

## **AC ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 5V,  $V_{EE}$  = 0V,  $T_A$  = 0°C TO 70°C unless otherwise shown.

| PARAMETER                              | SYMBOL                          | CONDITIONS                                                    | MIN | TYP <sup>1</sup> | MAX  | UNITS  | NOTES     | TEST<br>LEVEL |

|----------------------------------------|---------------------------------|---------------------------------------------------------------|-----|------------------|------|--------|-----------|---------------|

| Data Rate                              |                                 |                                                               | 143 | -                | 540  | Mb/s   |           | 1             |

| Output Signal Swing                    | V <sub>SDO</sub>                | $R_L = 75\Omega$                                              | 700 | 850              | 1000 | mV     |           | 1             |

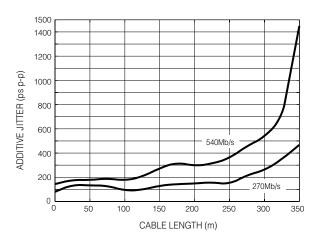

| Additive Jitter                        | tJ                              | 270Mb/s, 300m                                                 | -   | 275              | -    | ps p-p | see       | 5             |

|                                        |                                 | 540Mb/s, 100m                                                 | -   | 200              | -    | ps p-p | Fig 5     | 5             |

| Output Rise and Fall<br>Times (20-80%) | t <sub>r</sub> , t <sub>f</sub> |                                                               | 0.5 | 0.65             | -    | ns     |           | 3             |

| Output Duty Cycle<br>Distortion        |                                 |                                                               | -   | 30               | -    | ps     |           | 2             |

| Input Resistance                       | R <sub>IN</sub>                 | SDI, SDI                                                      | -   | 10               | -    | kΩ     |           | 2             |

| Input Capacitance                      | C <sub>IN</sub>                 | SDI, SDI                                                      | -   | 1.0              | -    | pF     |           | 2             |

| Carrier Detect<br>Response Time        | t <sub>CDON</sub>               | Carrier Applied $R_L = \infty$ ,<br>$C_L \le 50$ pF on SSI/CD | -   | 3                | -    | μs     |           | 2             |

|                                        | t <sub>CDOFF</sub>              | Carrier Removed $R_L = \infty$ ,<br>$C_L \le 50 pF$ on SSI/CD | -   | 30               | -    | μs     |           | 2             |

| High Z Response Time                   | t <sub>rHIGHZ</sub>             |                                                               | -   | 17               | -    | ns     |           | 2             |

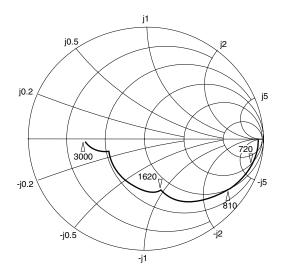

| Input Return Loss                      |                                 | at 270MHz                                                     | 15  | 20               | -    | dB     | see Fig 8 | 3             |

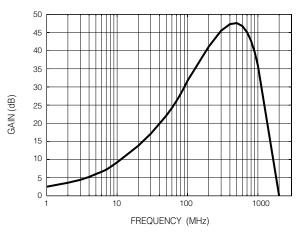

| Maximum Equalizer<br>Gain              | A <sub>EQ</sub>                 | at 200MHz                                                     | -   | 40               | -    | dB     | see Fig 4 | 3, 5          |

## TEST LEVELS

- 1. 100% tested at 25°C. 5. Evaluated usin

- 2. Guaranteed by design.

- 3. Inferred or co-related value.

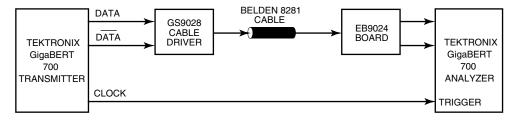

## 4. Evaluated using test setup Figure 1.

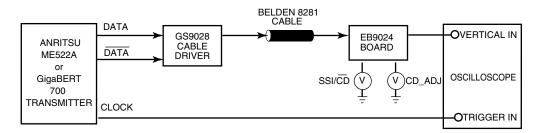

## 5. Evaluated using test setup Figure 2.

## NOTES

1. Typical values are parametric norms at 25°C.

## **TEST SETUP**

Fig. 1 Test Setup for Figure 3.

Fig. 2 Test Setup for Figures 4, 5, 6, 7, 10 and 11.

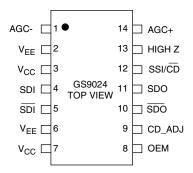

## **PIN CONNECTIONS**

## PIN DESCRIPTIONS

| NUMBER | SYMBOL     | TYPE | DESCRIPTION                                                                                                                             |

|--------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1, 14  | AGC-, AGC+ | I    | External AGC capacitor.                                                                                                                 |

| 4, 5   | SDI/SDI    | I    | Differential serial digital data inputs.                                                                                                |

| 8      | OEM        | 0    | Output 'Eye' monitor. OEM is a single ended current mode output and requires an external $50\Omega$ pullup resistor.                    |

| 9      | CD_ADJ     | I    | Carrier detect threshold adjust.                                                                                                        |

| 10, 11 | SDO/SDO    | 0    | Equalized serial digital data outputs.                                                                                                  |

| 12     | SSI/CD     | 0    | Signal strength indicator/Carrier Detect.                                                                                               |

| 13     | HIGH Z     | I    | The SDO/SDO outputs are High Z when this pin is HIGH. If High Z functionality is not used, this input can be left floating or tied LOW. |

## **TYPICAL PERFORMANCE CURVES** ( $V_S = 5V$ , $T_A = 25$ °C unless otherwise shown.)

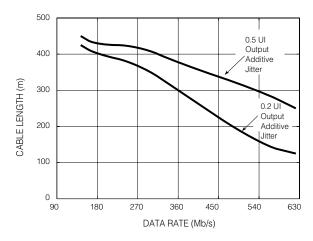

Fig. 3 Maximum Data Rate vs. Cable Length - Belden 8281n (see Test Setup in Figure 1)

Fig. 4 Equalizer Gain vs. Frequency

Fig. 5 Additive Jitter vs. Input Cable Length - Belden 8281

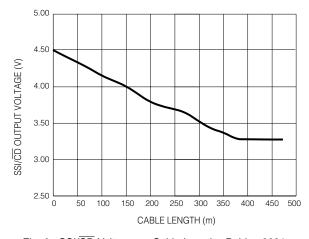

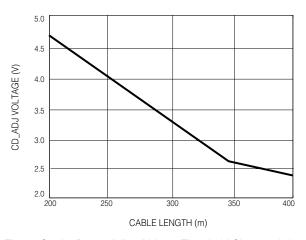

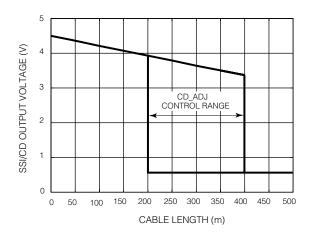

Fig. 6 SSI/ $\overline{\text{CD}}$  Voltage vs. Cable Length - Belden 8281 (CD\_ADJ = 0V)

Fig. 7 Carrier Detect Adjust Voltage Threshold Characteristics

Frequencies in MHz, impedances normalized to  $50\Omega.\,$

Fig. 8 Input Impedance

Fig. 9 Output Data Waveform at 270Mb/s, 300m

Fig. 10 Output Data Waveform at 540Mb/s, 200m

#### **DETAILED DESCRIPTION**

The GS9024 Automatic Cable Equalizer is a bipolar integrated circuit designed to equalize serial digital data signals between 30Mbps and 622Mbps. Powered from a single +5V or -5V supply, the device consumes approximately 240mW of power.

The serial data signal is connected to the input pins (SDI/ $\overline{\text{SDI}}$ ) either differentially or single ended. The input signal passes through a variable gain equalizing stage whose frequency response closely matches the inverse cable loss characteristic. In addition, the variation of the frequency response with control voltage imitates the variation of the

inverse cable loss characteristic with cable length. The gain stage provides up to 40dB of gain at 200MHz which will typically result in equalization of greater than 350m at 270Mb/s of Belden 8281 cable.

The edge energy of the equalized signal is monitored by a detector circuit which produces an error signal corresponding to the difference between the desired edge energy and the actual edge energy. This error signal is integrated by an external differential AGC filter capacitor (AGC+/AGC-) providing a steady control voltage for the gain stage. As the frequency response of the gain stage is automatically varied by the application of negative feedback, the edge energy of the equalized signal is kept at a constant level which is representative of the original edge energy at the transmitter.

The equalized signal is also DC restored, effectively restoring the logic threshold of the equalized signal to its corrective level irrespective of shifts due to ac coupling. The digital output signals have PECL voltage levels (800mV) and are available at pins SDO and SDO.

#### **OUTPUT HIGH Z**

A HIGH Z pin allows the data outputs to be put into a high impedance state, effectively disconnecting them from the output traces. This feature is ideal for input expansion in router applications as it eliminates the need for input muxes or crosspoints.

### SIGNAL STRENGTH INDICATION/CARRIER DETECT

The GS9024 incorporates an analog signal strength indicator/carrier detect (SSI/ $\overline{CD}$ ) output indicating both the presence of a carrier and the amount of equalization applied to the signal. The voltage output of this pin versus cable length (signal strength) is shown in Figure 11. With 0 m of cable (800mV input signal levels), the SSI/ $\overline{CD}$  output voltage is approximately 4.5V.

As the cable length increases, the SSI/CD voltage decreases linearly providing accurate correlation between the SSI/CD voltage and cable length.

When the signal strength decreases to the level set at the "Carrier Detect Threshold Adjust" pin, the SSI/CD voltage goes to a logic "0" state (0.8V) and can be used to drive other TTL/CMOS compatible logic inputs. In addition, when loss of carrier is detected the SDO/SDO outputs are muted (set to a known static state).

Fig. 11

### **CARRIER DETECT THRESHOLD ADJUST**

The threshold level at which loss of carrier is detected is adjustable via external resistors at the CD\_ADJ pin. The control voltage at the CD\_ADJ pin is set by a simple resistor divider circuit. The threshold level is adjustable from 200m to 350m. By default (no external resistors), the threshold is typically 320m. Connecting this pin to Ground disables the SDO/SDO muting function and allows for maximum possible cable length equalization.

This feature has been designed for use in applications such as routers where signal crosstalk and circuit noise cause the equalizer to output erroneous data when no input signal is present. The use of a Carrier Detect function with a fixed internal reference does not solve this problem since the signal to noise ratio on the circuit board could be significantly less than the default signal detection level set by the on chip reference. To alleviate this problem, the GS9024 provides a user adjustable threshold to meet the unique conditions that exist in each user's application. Override and internal default settings have also been provided to give the user total flexibility.

## **OUTPUT EYE MONITOR**

The GS9024 also provides an 'Output Eye Monitor' (OEM) which allows the verification of signal integrity after equalization, prior to reslicing. The OEM pin is an open collector current output that requires an external 50 ohm pullup resistor. When the pullup resistor is not used, the OEM block is disabled and the internal OEM circuit is powered down. The OEM provides a 0.25V p-p signal when driving a  $50\Omega$  oscilloscope input.

### I/O DESCRIPTION

#### HIGH SPEED ANALOG INPUTS (SDI/SDI)

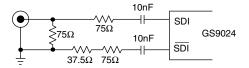

SDI/SDI are high impedance inputs which accept differential or single-ended input drive.

Figure 12 shows the recommended interface when a singleended serial digital signal is used.

Fig. 12

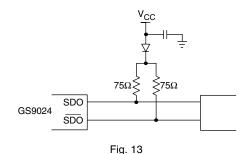

### HIGH SPEED OUTPUTS (SDO/SDO)

SDO/ $\overline{\text{SDO}}$  are current mode outputs that require external pullups (see Figure 13). The output signal swings are 800mV when  $75\Omega$  resistors are used. A diode can be placed between  $V_{CC}$  and the pullups to shift the signal levels down by approximately 0.7 volts. When the output traces are longer than 1 inch, controlled impedance traces should be used. The pullup resistors should be placed at the end of the output traces as they terminate the trace in its characteristic impedance (75 $\Omega$ ).

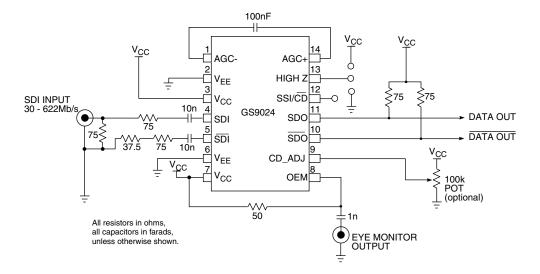

### TYPICAL APPLICATION CIRCUIT

### PACKAGE DIMENSIONS

All dimensions in millimeters.

## CAUTION

ELECTROSTATIC SENSITIVE DEVICES

DO NOT OPEN PACKAGES OR HANDLE EXCEPT AT A STATIC-FREE WORKSTATION

### DOCUMENT IDENTIFICATION

DATA SHEET

The product is in production. Gennum reserves the right to make changes at any time to improve reliability, function or design, in order to provide the best product possible.

## **REVISION NOTES:**

Added values to DC and AC Electrical Characteristics tables; changed AGC capacitor value in Application Circuit from 100pF to 100nF; changed layout of figures.

## **GENNUM CORPORATION**

MAILING ADDRESS:

P.O. Box 489, Stn. A, Burlington, Ontario, Canada L7R 3Y3 Tel. +1 (905) 632-2996 Fax. +1 (905) 632-5946

SHIPPING ADDRESS

970 Fraser Drive, Burlington, Ontario, Canada L7L 5P5

GENNUM JAPAN CORPORATION

C-101, Miyamae Village, 2-10-42 Miyamae, Suginami-ku Tokyo 168-0081, Japan

Tel. +81 (03) 3334-7700 Fax. +81 (03) 3247-8839

GENNUM UK LIMITED

25 Long Garden Walk, Farnham, Surrey, England GU9 7HX Tel. +44 (0)1252 747 000 Fax +44 (0)1252 726 523

Gennum Corporation assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

© Copyright April 1996 Gennum Corporation. All rights reserved. Printed in Canada.