### General Description

The GD16561 is a high performance low power 2.5 Gbit/s Laser Driver with optional on chip retiming of data.

The GD16561 is designed to meet and exceed ITU-T STM-16 or SONET OC-48 fiberoptic communication systems requirements.

The GD16561 is designed to sink a Modulation Current into the IOUT pin and a Pre-Bias Current into the IPRE pin. The Modulation Current is adjustable up to 60 mA by means of the pin VMOD. The Pre-Bias Current may be adjusted up to 50 mA by means of the VPRE pin.

Retiming of the data signal connected to the pins DIN, DINQ is made by means of a DFF clocked by an external clock signal at the data rate fed to the pins CKIN and CKINQ.

A Mark-Space monitor is available on the pins MARKP and MARKN. Together with the symmetry adjustment pin (SYM) this may be used to control the mark space ratio of the output signal.

The GD16561 is implemented in a Silicon Bipolar process and requires a single +5 V supply or a single -5.2 V supply.

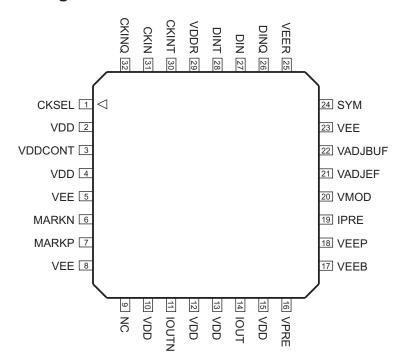

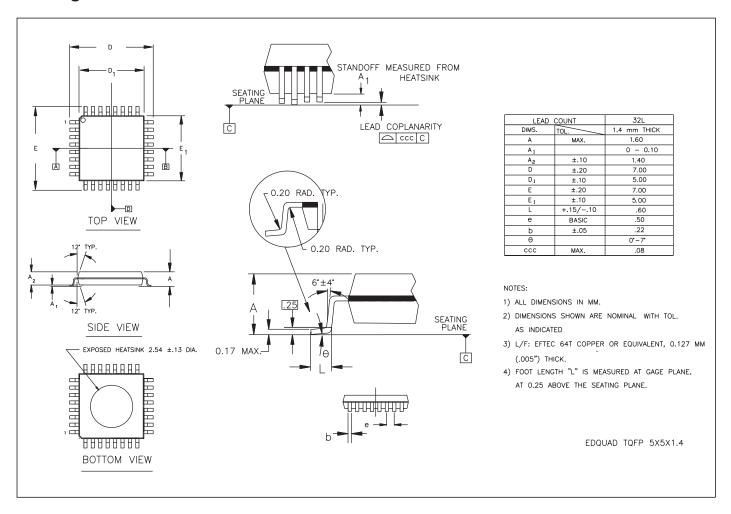

The circuit is available in a thermally enhanced 32-pin TQFP plastic package.

# 2.5 Gbit/s Retiming Laser Driver GD16561

# Preliminary

### Features

- Complies with ITU-T STM-16 and SONET OC-48 standards.

- Intended for driving a 50 Ω load, e.g. a laser diode with 50 Ω input impedance.

- Clocked or non-clocked operation.

- Large modulation current adjustment range from 5 mA to 60 mA.

- Output voltage over / under shoot less than ±2 % respectively ± 5 %.

- Rise / fall times less than 100 ps.

- Laser diode pre-bias adjustable up to 50 mA.

- Mark-Space monitor.

- Symmetry adjustment.

- Internal 50  $\Omega$  termination of data and clock inputs.

- Operates up to 3.5 Gbit/s.

- Power dissipation: 0.38 W.

Excluding Modulation Current and Pre-bias Current.

- Silicon Bipolar process.

- 32 pin thermally enhanced TQFP plastic package.

# **Applications**

- Tele Communication:

- SDH STM-16

- SONET OC-48

- Datacom up to 3.125 Gbit/s.

- Electro Absorption laser driver.

- Direct Modulation laser driver.

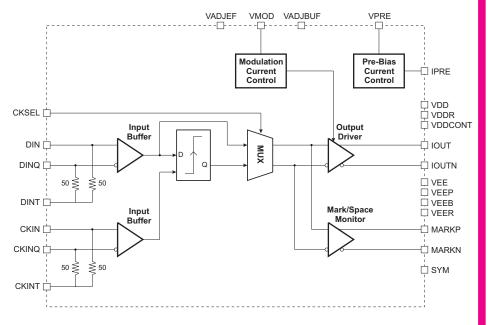

### Functional Details

GD16561 is a 2.5 Gbit/s laser driver with an optional retiming of the data signal. It is capable of driving high power laser diodes, typically having input impedance of 50  $\Omega$ , at a maximum modulation current of 60 mA and a maximum pre-bias current of 50 mA.

Data (DIN, DINQ) is input to GD16561 and retimed within a DFF clocked by an external clock (CKIN, CKINQ). Optionally the retiming may be bypassed controlled by a select pin (CKSEL).

Both the differential data (DIN, DINQ) and clock inputs (CKIN, CKINQ) are internally terminated to  $50~\Omega$ . Termination is made with a  $50~\Omega$  resistor from the two differential inputs to a common pin called DINT and CKINT respectively. The input sensitivity when driven with a single ended signal is better than 150 mV on both clock and data inputs.

The output pin (IOUT) is an open collector output designed for driving external loads with 50  $\Omega$  characteristic impedance. Because of the nature of an open collector the output therefore may be regarded as a current switch, with infinite output impedance. The characteristic impedance through the package is approximately 50  $\Omega$ . Optimum performance of GD16561 therefore is achieved if the output is terminated into a 50  $\Omega$  impedance.

The output modulation current is controlled by the pin VMOD and can be controlled in the range from 0 mA to 60 mA,

however DC-coupling of the output is only possible in the range from 5 mA to 40 mA. Operated with an AC-coupling, the output modulation current can be controlled in the range 5 mA to 60 mA.

The output voltage swing across the external load may be varied accordingly. The modulation current control on pin VMOD is implemented as a current mirror and therefore sinks a current proportional to the modulation current. The current sink into the VMOD pin is approximately 3/80 of the modulation current.

Two additional pins (VADJBUF and VADJEF) are available in order to optimise the performance of the output signal quality, specifically with respect to overshoot and undershoot. Typically best performance is obtained if these pins are connected to VMOD.

The pre-bias current is controlled by the pin VPRE and can be controlled from 0 mA to 50 mA. The pre-bias current control on pin VPRE is implemented as a current mirror and therefore sinks a current proportional to the pre-bias current. The current sink into the VPRE pin is approximately 3/500 of the pre-bias current.

An important parameter for laser drivers is voltage overshoot on the output pin (IOUT), because it determines the extinction ratio. GD16561 has been designed with special emphasis on achieving a very small voltage overshoot. For

GD16561 the voltage overshoot is less than 2 % across the full modulation current range, when driving a 50  $\Omega$  load. Similarly the voltage undershoot is less than 5 %.

A mark-space monitor is provided through the pins MARKP and MARKN. These may be connected as shown in the application diagram below, with a capacitor across the two outputs and a comparator (or Op-amp) to determine the mark density. Symmetry input (SYM) is available which may be used to control the mark-space ratio.

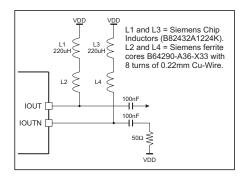

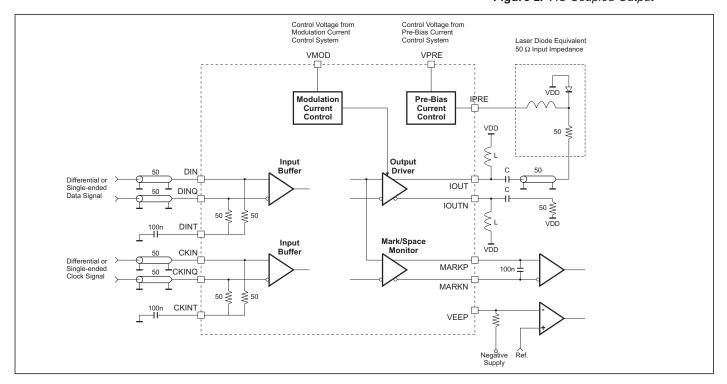

### **AC Coupled Output**

When DC coupled the output swing will be limited by IOUT output voltage specified to -2 V. For maximum output voltage swing the output should be AC coupled as shown on Figure 2 or VDD should be raised.

Figure 2. AC Coupled Output

Figure 1. Application Diagram

### Pin List

| Mnemonic:         | Pin No.:             | Pin Type:         | Description:                                                                                                                                                                                                    |  |  |

|-------------------|----------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DIN<br>DINQ       | 27<br>26             | AC IN             | Data inputs. Internally terminated in 50 $\Omega$ to DINT. Internally biased to -1.3 V                                                                                                                          |  |  |

| DINT              | 28                   | ANL IN            | Termination voltage for DIN and DINQ.                                                                                                                                                                           |  |  |

| CKIN<br>CKINQ     | 31<br>32             | AC IN             | Clock inputs. Internally terminated in 50 $\Omega$ to CKINT. Internally biased to -1.3 V.                                                                                                                       |  |  |

| CKINT             | 30                   | ANL IN            | Termination voltage for CKIN and CKINQ.                                                                                                                                                                         |  |  |

| IOUT<br>IOUTN     | 14<br>11             | OPEN<br>COLLECTOR | Laser Driver Output (2.5 Gbit/s). IOUT and IOUTN sink a modulation current, which is controlled by the pin VMOD. The current into IOUT is high when data is high on DIN.                                        |  |  |

| IPRE              | 19                   | OPEN<br>COLLECTOR | Pre-bias current output. IPRE sinks a current, which is controlled by the pin VPRE.                                                                                                                             |  |  |

| VMOD              | 20                   | ANL IN            | Modulation current control input. The control system is made as current mirror. VMOD sinks a current proportional to the modulation current. This current is approximately 3/80 times "The mod lation current". |  |  |

| VPRE              | 16                   | ANL IN            | Pre-bias current control input. The control system is made as a current mirror. VPRE sinks a current proportional to the pre-bias current. This current is approximately 3/500 times "The pre-bias current".    |  |  |

| CKSEL             | 1                    | ECL IN            | When CKSEL is low data is retimed. Otherwise data is bypassed the retiming.                                                                                                                                     |  |  |

| SYM               | 24                   | ANL IN            | SYM controls the mark-space ratio of the output. Decreasing the voltage of the SYM pin decreases the pulse width of a current high into the IOUT pin.                                                           |  |  |

| MARKP<br>MARKN    | 7<br>6               | ANL OUT           | Mark-space monitor outputs. High impedance CML outputs. The output voltage of the MARKP pin is the same polarity as the voltage on the DIN input.                                                               |  |  |

| VADJBUF<br>VADJEF | 22<br>21             | ANL IN            | Pins used to optimise the performance of the output in terms of overshoot and undershoot. Typically optimum performance will be achieved when shorted to VMOD.                                                  |  |  |

| VDD               | 2, 4, 10, 12, 13, 15 | PWR               | Ground pins for laser driver part.                                                                                                                                                                              |  |  |

| VDDCONT           | 3                    | PWR               | Ground pin for modulation current control system.                                                                                                                                                               |  |  |

| VDDR              | 29                   | PWR               | Ground pin for retiming part.                                                                                                                                                                                   |  |  |

| VEE               | 5, 8, 23             | PWR               | Negative supply pins for laser driver part.                                                                                                                                                                     |  |  |

| VEEP              | 18                   | PWR               | Negative supply pin for output driver.                                                                                                                                                                          |  |  |

| VEEB              | 17                   | PWR               | Negative supply pin for pre-bias circuitry.                                                                                                                                                                     |  |  |

| VEER              | 25                   | PWR               | Negative supply pin for retiming part.                                                                                                                                                                          |  |  |

| NC                | 9                    |                   | Not Connected.                                                                                                                                                                                                  |  |  |

| Heat sink         | Package back         |                   | Connected to VDD.                                                                                                                                                                                               |  |  |

# Package Pinout

Figure 3. Package 32 TQFP, Top View

# Maximum Ratings

These are the limits beyond which the component may be damaged. All voltages in table are referred to VDD. All currents in table are defined positive out of the pin.

| Symbol:         | Characteristic:                          | Conditions: | MIN.:                | TYP.: | MAX.: | UNIT: |

|-----------------|------------------------------------------|-------------|----------------------|-------|-------|-------|

| V <sub>EE</sub> | Power Supply                             |             | -6                   |       | 0     | V     |

| Vo              | Applied Voltage (All Outputs)            |             | V <sub>EE</sub> -0.5 |       | 2     | V     |

| V,              | Applied Voltage (All Inputs)             |             | V <sub>EE</sub> -0.5 |       | 0.5   | V     |

| I, AC IN        | Input Current (AC IN)                    |             | -1                   |       | 1     | mA    |

| I, VMOD         | Input Current (VMOD)                     |             | -4                   |       | 1     | mA    |

| I, VPRE         | Input Current (VPRE, VADJBUF and VADJEF) | Note 1      | -1                   |       | 1     | mA    |

| To              | Operating Temperature                    | Base        | -55                  |       | +125  | °C    |

| Ts              | Storage Temperature                      |             | -65                  |       | +150  | °C    |

**Note 1:** Voltage and/or current should be externally limited to specified range.

### DC Characteristics

$T_{\text{CASE}}$  = -40 °C to 85 °C, appropriate heat sinking may be required. All voltages in table are referred to VDD. All currents in table are defined positive out of the pin.

| Symbol:                  | Characteristic:                                       | Conditions:                                                                       | MIN.:           | TYP.: | MAX.:           | UNIT: |

|--------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|-------|-----------------|-------|

| V <sub>EE</sub>          | Power Supply                                          |                                                                                   | -5.5            | -5.2  | -4.7            | V     |

| I <sub>EE</sub>          | Negative Supply Current                               | $I_{OUT} = 0 \text{ A}$                                                           |                 | 75    |                 | mA    |

| P <sub>DISS</sub>        | Power Dissipation                                     | $V_{EE} = -5.0 \text{ V},$<br>$I_{OUT} = 0 \text{ A},$<br>$I_{PRE} = 0 \text{ A}$ |                 | 0.38  | 0.5             | W     |

| $V_{pp}$ AN IN           | Peak-peak Voltage when Input is Driven Single ended.  | V <sub>∨TH</sub> = −1.3 V                                                         | 150             |       | 800             | mV    |

| V VMOD                   | Voltage Range for VMOD                                |                                                                                   | V <sub>EE</sub> |       | $V_{DD}$        | V     |

| I VMOD                   | Sink Current into Pin VMOD                            |                                                                                   | -4              |       | 0               | mA    |

| V <sub>IN</sub> NN       | Input Voltage Range for VPRE, VADJBUF, VADJEF and SYM |                                                                                   | V <sub>EE</sub> |       | V <sub>DD</sub> | V     |

| I <sub>SINK</sub> NN     | Sink Current into pin VPRE, VADJBUF, VADJEF and SYM   |                                                                                   | -1              |       | 0               | mA    |

| V <sub>IN</sub> SYM      | Input Voltage Range for SYM                           |                                                                                   | V <sub>EE</sub> |       | V <sub>DD</sub> | V     |

| I <sub>LEAK</sub> SYM    | Leakage Current for CKSEL                             |                                                                                   | -1              |       | 1               | mA    |

| V <sub>IN</sub> CKSEL    | Input Voltage Range for CKSEL                         |                                                                                   | V <sub>EE</sub> |       | V <sub>DD</sub> | V     |

| I <sub>LEAK</sub> CKSEL  | Leakage Current for SYM                               |                                                                                   | -1              |       | 1               | mA    |

| V <sub>LO</sub> MARK     | Low Output Voltage for Mark-Space Monitor             |                                                                                   |                 | -2.0  |                 | V     |

| R <sub>o</sub> MARK      | Output Impedance for Mark-Space Monitor               |                                                                                   |                 | 4.0   |                 | kΩ    |

| V <sub>o</sub> IPRE      | IPRE Output Voltage                                   |                                                                                   | -2.0            |       |                 | V     |

| I IPRE                   | IPRE Current                                          |                                                                                   | -50             |       | 0               | mA    |

| V <sub>o</sub> IOUT      | IOUT Output Voltage                                   | Note 1                                                                            | -2.0            |       |                 | V     |

| I <sub>Mod,HI</sub> IOUT | IOUT High Modulation Current                          | Note 1                                                                            | -60             |       | 0               | mA    |

| I <sub>Mod,LO</sub> IOUT | IOUT Low Modulation Current                           | Note 1, 2                                                                         | -3              |       | 1               | mA    |

**Note 1:**  $R_{LOAD}$  = 50  $\Omega$  AC coupled to VDD connected to pin IOUT. Sink current is controlled by the VMOD pin, and may be adjusted in the range as specified. Notice that high modulation current means that the output voltage level is low.

Note 2: This is a leakage current. Maximum leakage current is present at max modulation current.

The leakage current decreases for smaller modulation currents.

### AC Characteristics

$T_{CASE}$  = -40 °C to 85 °C, appropriate heat sinking may be required.

| Symbol:                        | Characteristic:                 | Conditions: | MIN.: | TYP.: | MAX.: | UNIT:  |

|--------------------------------|---------------------------------|-------------|-------|-------|-------|--------|

| $f_{MAX}$ OUT                  | Data Output Frequency           |             | 2500  |       |       | Mbit/s |

| $J_{pp}$ OUT                   | Added Output Jitter             | Note 1      |       |       | 20    | ps     |

| t <sub>RISE</sub> OUT          | Output Rise Time                | Note 1      |       |       | 100   | ps     |

| $t_{\it FALL}$ OUT             | Output Fall Time                | Note 1      |       |       | 100   | ps     |

| $t_{PM}$                       | Phase Margin Clock to Data      |             | 300   |       |       | ps     |

| $t_{\mathbb{S}}$               | Data Set-up Time                |             | 60    | 30    |       | ps     |

| t <sub>H</sub>                 | Data Hold Time                  |             | 20    | 5     |       | ps     |

| $\Delta_{	extsf{CROSS\_OVER}}$ | Output Cross Over Control Range | Note 1      | ± 30  |       |       | %      |

Note 1:  $R_{LOAD}$  = 50  $\Omega$  to  $V_{DD}$  connected to pin IOUT.  $I_{LD}$  = 40 mA. Rise/Fall times at 20 – 80 % of HI/LO voltage levels.

## Package Outline

Figure 4. Package 32 pin. All dimensions are in mm.

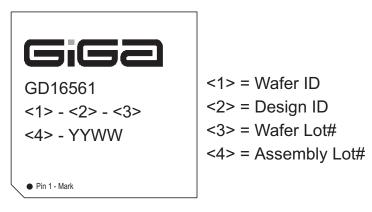

# **Device Marking**

Figure 5. Device Marking, Top View.

# **Ordering Information**

To order, please specify as shown below:

| Product Name: | Package Type:   | Temperature Range: | Option: |

|---------------|-----------------|--------------------|---------|

| GD16561-32BA  | 32L TQFP EDQUAD | -4085 °C           |         |

GD16561, Data Sheet Rev. 05 - Date: 14 March 2000

Mileparken 22, DK-2740 Skovlunde

Denmark.

Phone : +45 7010 1062

Fax : +45 7010 1063

E-mail : sales@giga.dk

Web site : http://www.giga.dk

Please check our Internet web site for latest version of this data sheet.

The information herein is assumed to be reliable. GIGA assumes no responsibility for the use of this information, and all such information shall be at the users own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. GIGA does not authorise or warrant any GIGA Product for use in life support devices and/or systems.

Distributor:

Copyright © 2000 GIGA A/S All rights reserved