# 10 Base-T NIC Module with Enhanced CMA and Resistor Network

## **EPE6167G**

- Optimized for DP83902, 905, 907, 932 PHY chips

- Robust construction allows for IR/VP processes •

- Complies with or exceeds IEEE 802.3, 10 Base-T Requirements

### Electrical Parameters @ 25° C

| Cut-off<br>Frequency<br>(MHz) |     | Insertion<br>Loss<br>(dB Max.) |     | Return<br>Loss<br>(dB Min.) |     | Attenuation<br>(dB Min.) (1) |     |             |     |             |     |             |     | Common Mode Rejection<br>(dB Min.) |     |              |     | Crosstalk<br>(dB Min.) |     |

|-------------------------------|-----|--------------------------------|-----|-----------------------------|-----|------------------------------|-----|-------------|-----|-------------|-----|-------------|-----|------------------------------------|-----|--------------|-----|------------------------|-----|

| ± 1.0<br>MHz                  |     | 1-10<br>MHz                    |     | 5-10<br>MHz                 |     | @ 20<br>MHz                  |     | @ 25<br>MHz |     | @ 30<br>MHz |     | @ 40<br>MHz |     | @ 30-100<br>MHz                    |     | @ 200<br>MHz |     | @ 1-10<br>MHz          |     |

| Xmit                          | Rcv | Xmit                           | Rcv | Xmit                        | Rcv | Xmit                         | Rcv | Xmit        | Rcv | Xmit        | Rcv | Xmit        | Rcv | Xmit                               | Rcv | Xmit         | Rcv | Xmit                   | Rcv |

| 17                            | 17  | -1                             | -1  | -15                         | -15 | -7                           | -5  | -18         | -11 | -30         | -18 | -35         | -26 | -30                                | -30 | -30          | -30 | -35                    | -35 |

Isolation: meets or exceeds 802.3 IEEE Requirements

Characteristic Filter Impedance: 100 Ω

Note: 1) Referenced to the filter output @ 5 MHz for filter only, excluding resistor network.

RX+ 14 -

## **Chip Side Media Side Package** $\Pi$ $\Pi$ $\Pi$ $\Pi$ $\Pi$ $\Pi$ $\Pi$ Pin 1 PCA EPE6167G I.D. Pad В Layout Date Code C Н F

#### (Inches) (Millimeters) Dim. Min. Max. Nom. Min. Max. Nom. .890 .910 22.61 23.11 .380 .360 9.14 9.14 BCDEF 9.65 .380 .360 9.65 .700 Typ. .015 17.78 Typ. .381 .127 2.54 .005 Typ. .510 .100 Тур. G 12.95 .490 12.45 .016 .022 .406 .559 .008 .012 .203 .305 Typ. .100 Typ. 2.54 K .635 L .025 .045 1.14 Μ .040 1.02 .100 2.54 2.54 N P Q 13.72

**Dimensions**

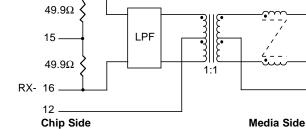

**Receive Channel**

11 Rd+

9 Rd-

10

# 10 Base-T Interface Module with Enhanced CMA and Resistor Network

**EPE6167G**

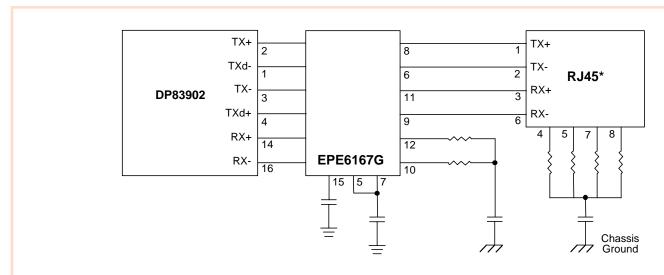

The circuit below is a guideline for interconnecting PCA's EPE6167G with Atlantic chip as a reference controller. Further details of system design, such as chip pin-out, etc. can be obtained from the specific chip manufacturer.

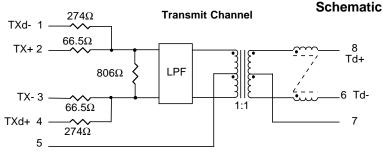

Typical insertion loss of the isolation transformer/filter is 0.7dB. This parameter covers the entire spectrum of the encoded signals in 10 Base-T protocols. However, the predistortion resistor network introduces some loss which has to be taken into account in determining how well your design meets the Standard Template requirements.

A quick calculation of the effective Thevenin's termination impedance for the filter follows:

R(termination)=  $2(66.5//274)//806\approx95$ . Thus, when measuring the return loss of these parts on the bench, it is necessary to provide a shunting resistor of approximatively  $5\Omega$  representing the four  $5\Omega$  output signal sources. This calculation assumes that the chip output driver source impedances are negligible (less than  $2\Omega$ )

The phantom resistors shown around the RJ45 connector have been known to suppress unwanted radiation that unused wires pick up from the immediate environment. Their placement and use are to be considered carefully before a design is finalized.

It is recommended that there be a neat separation of ground planes in the layout. It is generally accepted practice to limit the plane off at least 0.08 inches away from the chip side pins of EPE6167G. There need not be any ground plane beyond this point.

For best results, PCB designer should design the outgoing traces preferably to be 50  $\Omega$ , balanced and well coupled to achieve minimum radiation from these traces.

### Typical Application Circuit for UTP

Notes: \* Pin-outs shown are for NIC configurations.