## 10 Base-T Interface Module

# **EPA2013DG**

- General Purpose 10 Base-T Filter Module

- Available in SMD and DIP Packages •

- Complies with or exceeds IEEE 802.3, 10 Base-T Requirements •

### Electrical Parameters @ 25° C

| Cut-off<br>Frequency<br>(MHz) |     | Insertion<br>Loss<br>(dB Max.) |     | Return<br>Loss<br>(dB Min.) |     | Attenuation<br>(dB Min.) |     |             |     |             |     | Common Mode<br>Rejection<br>(dB Min.) |     |             |     |              | Crosstalk<br>(dB Min.) |              |     |               |     |

|-------------------------------|-----|--------------------------------|-----|-----------------------------|-----|--------------------------|-----|-------------|-----|-------------|-----|---------------------------------------|-----|-------------|-----|--------------|------------------------|--------------|-----|---------------|-----|

| ± 1.0<br>MHz                  |     | 1-10<br>MHz                    |     | 5-10<br>MHz                 |     | @ 20<br>MHz              |     | @ 25<br>MHz |     | @ 30<br>MHz |     | @ 40<br>MHz                           |     | @ 50<br>MHz |     | @ 100<br>MHz |                        | @ 200<br>MHz |     | @ 1-10<br>MHz |     |

| Xmit                          | Rcv | Xmit                           | Rcv | Xmit                        | Rcv | Xmit                     | Rcv | Xmit        | Rcv | Xmit        | Rcv | Xmit                                  | Rcv | Xmit        | Rcv | Xmit         | Rcv                    | Xmit         | Rcv | Xmit          | Rcv |

| 17                            | 17  | -1                             | -1  | -15                         | -15 | -7                       | -6  | -19         | -14 | -30         | -20 | -35                                   | -31 | -30         |     | -25          |                        |              |     | -30           | -30 |

• Isolation : meets or exceeds 802.3 IEEE Requirements • Characteristic Filter Impedance : 100  $\Omega$  • \*Referenced to the Output Level Fundamental Frequency @ 5 MHz •

#### **Schematic**

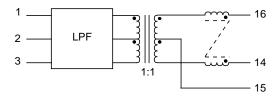

#### **Transmit Channel**

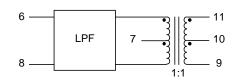

#### **Receive Channel**

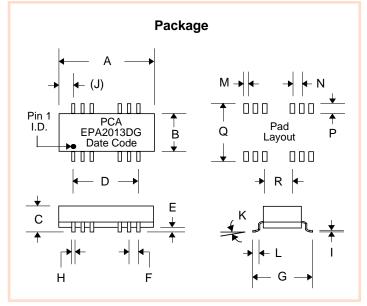

### **Dimensions**

|          |      | (Inches) |      | (Millimeters) |            |       |  |  |  |  |

|----------|------|----------|------|---------------|------------|-------|--|--|--|--|

| Dim.     | Min. | Max.     | Nom. | Min.          | Max.       | Nom.  |  |  |  |  |

| Α        | .980 | 1.00     |      | 24.89         | 25.4       |       |  |  |  |  |

| В        | .260 | .280     |      | 6.60          | 7.11       |       |  |  |  |  |

| C        | .255 | .275     |      | 6.48          | 6.99       |       |  |  |  |  |

| D        | .700 | Тур.     |      | 17.78         | Тур.       |       |  |  |  |  |

| E        | .005 | .015     |      | .127          | .381       |       |  |  |  |  |

| F        | .100 | Тур.     |      | 2.54          | Тур.       |       |  |  |  |  |

| G        | .380 | .400     |      | 9.65          | 10.16      |       |  |  |  |  |

| H        | .016 | .022     |      | .406          | .559       |       |  |  |  |  |

| 1        | .008 | .012     |      | .203          | .305       |       |  |  |  |  |

| (J)<br>K | .145 | Typ.     |      | 3.91          | Typ.<br>8° |       |  |  |  |  |

| K        | 0°   | 8°       |      | 0°            | 8°         |       |  |  |  |  |

| L        | .025 | .045     |      | .635          | 1.14       |       |  |  |  |  |

| M        |      |          | .030 |               |            | .762  |  |  |  |  |

| N        |      |          | .100 |               |            | 2.54  |  |  |  |  |

| P        |      |          | .055 |               |            | 1.40  |  |  |  |  |

| Q        |      |          | .410 |               |            | 10.41 |  |  |  |  |

| R        | .300 | Тур.     |      | 7.62          | Тур.       |       |  |  |  |  |

## 10 Base-T Interface Module

## **EPA2013DG**

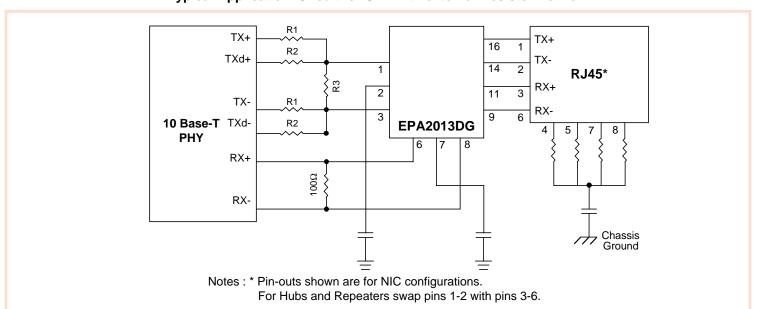

The circuit below is a guideline for interconnecting PCA's EPA2013DG with a typical 10 Base-T PHY chip over UTP cable. Further details of system design, such as chip pin-out, etc. can be obtained from the specific chip manufacturer.

Typical insertion loss of the isolation transformer/filter is 0.7dB. This parameter covers the entire spectrum of the encoded signals in 10 Base-T protocols. However, the predistortion resistor network introduces some loss which has to be taken into account in determining how well your design meets the Standard Template requirements. Additionally, the following need to be considered while selecting resistor values:

- a. The filter needs  $100\Omega$  termination, thus the Thevenin's equivalent resistance seen by the filter looking into the transmit outputs from the chip must be equal to a value close to  $100\Omega$ . The typical driver output impedance is  $5\Omega$ . Thus choose R1 and R2 values that are lowered by  $5\Omega$  on each leg. Following these guidelines will guarantee that the return loss specifications are satisfied at all extremes of cable impedance (i.e.  $85\Omega$  to  $115\Omega$ ) while the module is installed in your system.

- b. That the template requirements are satisfied under the worst case Vcc (i.e. 4.5V), will impose a further constraint on resistor selection, in that they ought to be the minimum derived from the calculations. Add R3 for more flexibility in setting voltage levels at the outputs.

Note that some systems have auto polarity detection and some do not. If not, be certain to follow the proper polarity.

It is recommended that system designers ground the chip side center taps via a low voltage capacitor. Taking the cable side center taps to chassis via capacitors, is not recommended, as this will add cost without containing EMI. This may worsen EMI, specifically if the primary "common mode termination" is pulled to ground as shown.

The pulldown resistors used around the RJ45 connector have been known to suppress unwanted radiation that unused wires pick up from the immediate environment. Their placement and use are to be considered carefully before a design is finalized.

It is recommended that there be a neat separation of ground planes in the layout. It is generally accepted practice to limit the plane off at least 0.08 inches away from the chip side pins of EPA2013DG. There need not be any ground plane beyond this point.

For best results, PCB designer should design the outgoing traces preferably to be  $50\Omega$ , balanced and well coupled to achieve minimum radiation from these traces.

#### Typical Application Circuit for UTP with external Resistor Network