# Edge4707 Quad Channel Per-Pin Precision Measurement Unit

### HIGH-PERFORMANCE PRODUCTS - ATE

**TARGET**

#### Description

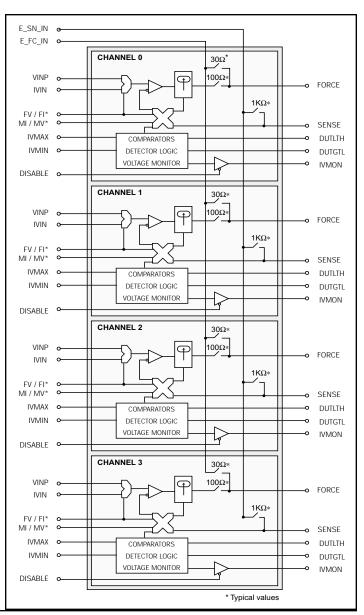

The Edge4707 is a precision measurement unit designed for automatic test equipment and instrumentation. Manufactured in a wide voltage CMOS process, it is a monolithic solution for a quad channel per pin PMU.

Each channel of the Edge4707 features a PMU that can force or measure voltage over a 15V I/O range, and supports 4 current ranges:  $2 \mu A$ ,  $200 \mu A$ ,  $20 \mu A$ , and  $2 \mu A$ .

Each channel of the Edge4707 features an on-board window comparator that provides two bits of information: DUT too high and DUT too low. There is also a monitor function which provides a real time analog signal proportional to either the measured voltage or current.

The Edge4707 is designed to be a low power, low cost, small footprint solution to allow high pin count testers to support a PMU per pin.

In addition, two independent switches per channel (for a central PMU force and sense) plus two wide voltage analog muxes per channel are included.

## **Applications**

- Automated Test Equipment

- Memory Testers

- VLSI Testers

- Mixed Signal Tester

#### Features

- FV / MI Capability

- FI / MV Capability

- FV / MV Capability

- FI / MI Capability

- 4 Current Ranges (2 μA, 20 μA, 200 μA, 2mA)

- –2V to +13V Output Range (Zero Current)

- OV to 11V Output Range (Full Scale Current)

- FV Linearity to ± .025% FSR

- Central PMU Switches

- Per Pin Super Voltage Switches

## Functional Block Diagram

TARGET

# PIN Description

| Pin Name                             | Pin #                                                                                | Description                                                                                                                                                   |

|--------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VINP[0:3]                            | C2, F5, H3, L2                                                                       | Analog voltage input which forces the output voltage (FV/MI mode) (one per channel).                                                                          |

| IVIN[0:3]                            | C1, F2, H4, J5                                                                       | Analog voltage input which forces the output current (FI/MV mode) (one per channel).                                                                          |

| FORCE[0:3]                           | C14, F12, H13, L12                                                                   | Analog output pin which forces current or voltage.                                                                                                            |

| SENSE[0:3]                           | C13, G10, H14, K11                                                                   | Analog input pin which senses voltage.                                                                                                                        |

| FV/FI*[0:3]                          | D10, B8, A6, E6                                                                      | TTL compatible input which determines whether the PMU is forcing voltage or forcing current.                                                                  |

| MI/MV*[0:3]                          | B10, A8, C6, D5                                                                      | TTL compatible input which determines whether the PMU is measuring current or measuring voltage.                                                              |

| RS0[0:3]<br>RS1[0:3]                 | B11, A9, C7, C5<br>A12, C10, D8, A5                                                  | TTL compatible current range select inputs.                                                                                                                   |

| IVMIN[0:3]<br>IVMAX[0:3]             | G5, E1, H2, K3<br>C3, E3, H1, L1                                                     | Analog input voltages which establish the lower and upper threshold level for the measurement comparator.                                                     |

| DUTLTH[0:3]<br>DUTGTL[0:3]           | P11, N9, N7, N5<br>N11, P9, P7, P5                                                   | Digital comparator output that indicates the DUT measurement is less than the upper threshold and greater than the lower threshold.                           |

| DISABLE[0:3]                         | A11, C9, D7, A4                                                                      | TTL compatible input which places the IVMON outputs in high impedance.                                                                                        |

| E_SNSEL[0:3]                         | D11, E9, B7, B5                                                                      | TTL switch select for the external SENSE switch for Channels 0–3.                                                                                             |

| E_SN_IN                              | L4                                                                                   | Analog output for external SENSE.                                                                                                                             |

| E_FC_IN                              | K5                                                                                   | Analog input for external FORCE signal.                                                                                                                       |

| E_FCSEL[0:3]                         | E10, B9, A7, D6                                                                      | TTL switch select for the external FORCE switch for Channels 0-3.                                                                                             |

| I_FCSEL[0:3]                         | C11, D9, B6, B4                                                                      | TTL switch select for internal FORCE switch for Channels 0–3.                                                                                                 |

| RA[0:3], RB[0:3]<br>RC[0:3], RD[0:3] | D13, G11, J14, K10<br>D14, G12, J13, L11<br>E12, G14, J10, M14<br>F11, G13, K12, M13 | External resistor input corresponding to Ranges A through D.                                                                                                  |

| RES_IN[0:3]                          | F10, F13, J12, L13                                                                   | External resistor input. One side of the external resistors connect to RA[0:3], RB[0:3], RC[0:3], RD[0:3]. The other side of all resistors connect to RES_IN. |

TARGET

# PIN Description (continued)

| Pin Name                 | Pin #                                 | Description                                                                                                       |

|--------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| IVMON[0:3]               | B1, E2, G4, J4                        | Analog voltage output that provides a real time monitor of either the measured voltage or measured current level. |

| COMP1[0:3]<br>COMP2[0:3] | D4, F1, J2, K4<br>E5, F3, J1, M1      | Internal compensation pins that require an external capacitor connected between the two pins.                     |

| COMP3[0:3]               | D2, F4, J3, M2                        | Internal compensation pin that requires an external capacitor connected between the pin and ground.               |

| COMP4[0:3]               | D1, G2, H5, L3                        | Internal compensation pin that requires an external capacitor connected between the pin and the RES_IN pin.       |

| Analog MUX<br>Switches   |                                       |                                                                                                                   |

| V <sub>IH[0:3]</sub>     | K9, M9, M7, M5                        | Driver High input.                                                                                                |

| VIHH[0:3]                | L10, K8, L7, K6                       | Super voltage input High.                                                                                         |

| V <sub>IL</sub> [0:3]    | L9, M8, M6, M4                        | Driver Low input.                                                                                                 |

| V <sub>ILH[O:3]</sub>    | M10, L8, L6, L5                       | Super voltage input Low.                                                                                          |

| SVSEL[0:3]               | A10, C8, E7, A3                       | Select for MUX.                                                                                                   |

| DVH[0:3]                 | P10, N8, N6, N4                       | Output High.                                                                                                      |

| DVL[0:3]                 | N10, P8, P6, P4                       | Output Low.                                                                                                       |

|                          |                                       |                                                                                                                   |

| Power Pins               |                                       |                                                                                                                   |

| VCC[1:4]                 | A1, D12, E4, E14,<br>G3, H12, K2, K13 | Positive analog power supply.                                                                                     |

| VDD                      | P3                                    | Positive digital supply.                                                                                          |

| VEE[1:4]                 | D3, E13, G1, H11,<br>K1, K14, M12, N1 | Negative analog power supply.                                                                                     |

| GND[1:4]                 | E11, F14, J11, L14                    | Ground.                                                                                                           |

TARGET

PIN Description (continued)

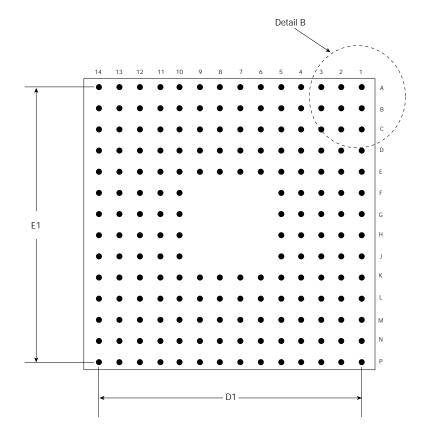

### **Bottom View**

### 12 mm X 12 mm 180 FLEXBGA

| Р | P1 <b>O</b>  | P2 <b>O</b>   | P3 <b>O</b> | P4 <b>O</b>   | P5 <b>O</b>    | P6 <b>O</b> | P7 <b>O</b>     | P8 <b>O</b>  | P9 <b>O</b>   | P10          | P11<br><b>O</b> | P12      | P13           | P14           |

|---|--------------|---------------|-------------|---------------|----------------|-------------|-----------------|--------------|---------------|--------------|-----------------|----------|---------------|---------------|

|   | N1           | N2            | VDD<br>N3   | DVL3<br>N4    | DUTGTL3<br>N5  | DVL2<br>N6  | DUTGTL2<br>N7   | DVL1<br>N8   | DUTGTL1<br>N9 | DVH0<br>N10  | DUTLTHO<br>N11  | N12      | N13           | N14           |

| N | O<br>VEE4    | 0             | 0           | O<br>DVH3     | O<br>DUTLTH3   | O<br>DVH2   | O<br>DUTLTH2    | O<br>DVH1    | O<br>DUTLTH1  | O<br>DVLO    | DUTGTLO         | 0        | 0             | 0             |

| М | M1 <b>O</b>  | M2 <b>O</b>   | M3          | M4 <b>O</b>   | M5             | M6          | M7              | M8           | M9            | M10          | M11             | M12      | M13           | M14           |

|   | COMP2_3      | COMP3_3<br>L2 | L3          | VIL3          | VIH3           | VIL2<br>L6  | VIH2            | VIL1<br>L8   | VIH1          | VILHO<br>L10 | L11             | VEE4     | RD3           | RC3           |

| L | 0            | 0             | 0           | 0             | 0              | 0           | 0               | 0            | 0             | 0            | 0               | 0        | 0             | 0             |

|   | IVMAX3<br>K1 | VINP3         | COMP4_3     | E_SN_IN<br>K4 | VILH3<br>K5    | VILH2<br>K6 | VIHH2<br>K7     | VILH1<br>K8  | VILO<br>K9    | VIHHO<br>K10 | RB3<br>K11      | FORCE3   | RESIN3        | GND4<br>K14   |

| Κ | O<br>VEE3    | O<br>VCC4     | O<br>IVMIN3 | O<br>COMP1_3  | O<br>E_FC_IN   | O<br>VIHH3  | 0               | O<br>VIHH1   | O<br>VIHO     | O<br>RA3     | O<br>SENSE3     | O<br>RD2 | O<br>VCC4     | O<br>VEE3     |

|   | J1 _         | J2            | J3          | J4            | J5             | J6          | J7              | J8           | J9            | J10          | J11             | J12      | J13           | J14           |

| J | COMP2_2      | COMP1_2       | COMP3_2     | IVMON3        | O<br>IVIN3     |             |                 |              |               | RC2          | GND3            | RESIN2   | RB2           | RA2           |

|   | H1           | H2            | H3          | H4            | H5             | A1 Ba       | H7<br>II Pad Co | orner Inc    | licator       | H10          | H11             | H12      | H13           | H14           |

| Н | O<br>IVMAX2  | O<br>IVMIN2   | VINP2       | O<br>IVIN2    | COMP4_2        |             | (No Solo        | der Ball)    |               | 0            | VEE2            | VCC3     | O<br>FORCE2   | SENSE2        |

| G | G1 <b>O</b>  | G2 <b>O</b>   | G3          | G4            | G5             | G6          | G7              |              |               | G10          | G11             | G12      | G13           | G14           |

| G | VEE2         | COMP4_1       | VCC3        | IVMON2        | IVMINO         |             |                 |              |               | SENSE1       | RA1             | RB1      | RD1           | RC1           |

| F | F1 <b>O</b>  | F2 <b>O</b>   | F3 <b>O</b> | F4 <b>O</b>   | F5<br>O        | F6          |                 |              |               | F10          | F11             | F12      | F13           | F14           |

| ' | COMP1_1      | IVIN1         | COMP2_1     | COMP3_1       | VINP1          |             |                 |              |               | RESINO       | RD0             | FORCE1   | RESIN1        | GND2          |

| Е | E1 O         | E2 <b>O</b>   | E3 <b>O</b> | E4 <b>O</b>   | E5 <b>O</b>    | E6 <b>O</b> | E7              | E8<br>O      | E9 <b>O</b>   | E10          | E11             | E12      | E13           | E14           |

| _ | IVMIN1       | IVMON1        | IVMAX1      | VCC2          | COMP2_0        | FV/FI*3     | SVSEL2          |              | E_SNSEL1      | E_FCSELO     | GND1            | RCO      | VEE1          | VCC2          |

| D | D1 <b>O</b>  | D2 <b>O</b>   | D3 <b>O</b> | D4 <b>O</b>   | D5 <b>O</b>    | D6 <b>O</b> | D7              | D8           | D9 <b>O</b>   | D10          | D11             | D12      | D13           | D14           |

|   | COMP4_0      | COMP3_0       | VEE1        | COMP1_0       | MI/MV*3        | E_FCSEL3    | DISABLE2        | RS1_2        | I_FCSEL1      | FV/FI*0      | E_SNSELO        | VCC1     | RAO           | RB0           |

| С | C1 <b>O</b>  | 0             | ြိ ဝ        | O4            | ြီ ဝ           | ဳဝ          | <b>"O</b>       | °O           | <b>°</b> O    | C10          | 0               | 0        | C13           | C14           |

|   | IVINO        | VINPO<br>B2   | IVMAX0      | B4            | RS0_3          | MI/MV*2     | RS0_2<br>B7     | SVSEL1<br>B8 | DISABLE1      | RS1_1<br>B10 | I_FCSEL0<br>B11 | B12      | SENSE0<br>B13 | FORCEO<br>B14 |

| В | B1 <b>O</b>  | 0             | ြီ          | 0             | 0              | ြီဝ         | <b>O</b>        | ဳဝ           | D 0           | 0            | O               | 0        | 0             | 0             |

|   | IVMONO<br>A1 | A2            | A3          | I_FCSEL3      | E_SNSEL3<br>A5 | I_FCSEL2    | E_SNSEL2        | FV/FI*1      | E_FCSEL1      | MI/MV*0      | RSO_0<br>A11    | A12      | A13           | A14           |

| Α | 0            | 0             | 0           | 0             | 0              | 0           | 0               | 0            | 0             | 0            | 0               | 0        | 0             | 0             |

|   | VCC1         |               | SVSEL3      | DISABLE3      | RS1_3          | FV/FI*2     | E_FCSEL2        | MI/MV*1      | RS0_1         | SVSEL0       | DISABLEO        | RS1_0    | 10            |               |

|   | 1            | 2             | 3           | 4             | 5              | 6           | 7               | 8            | 9             | 10           | 11              | 12       | 13            | 14            |

**TARGET**

PIN Description (continued)

A1 Ball Pad Indicator

# **Top View**

### 12 mm X 12 mm 180 FLEXBGA

|                  | A1                                                                       | A2                                                                  | A3                                                                 | A4                                                                            | A5                                                                             | A6                                        | A7                                                          | A8                                        | A9                                              | A10                                              | A11                                                              | A12                                                                    | A13                                                                      | A14                                                                |

|------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------|-------------------------------------------|-------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------|

| Α                | VCC1                                                                     | 0                                                                   | SVSEL3                                                             | DISABLE3                                                                      | <b>O</b> RS1 3                                                                 | FV/FI*2                                   | E FCSEL2                                                    | MI/MV*1                                   | RS0 1                                           | SVSELO                                           | DISABLEO                                                         | RS1 0                                                                  |                                                                          | O                                                                  |

|                  | B1 _                                                                     | B2                                                                  | В3                                                                 | B4                                                                            | B5                                                                             | B6                                        | B7                                                          | B8                                        | B9 _                                            | B10                                              | B11                                                              | B12                                                                    | B13                                                                      | B14                                                                |

| В                | 0                                                                        | 0                                                                   | 0                                                                  | 0                                                                             | 0                                                                              | 0                                         | 0                                                           | 0                                         | 0                                               | 0                                                | 0                                                                | 0                                                                      | 0                                                                        | 0                                                                  |

|                  | IVMONO<br>C1                                                             | C2                                                                  | C3                                                                 | I_FCSEL3                                                                      | E_SNSEL3                                                                       | I_FCSEL2<br>C6                            | E_SNSEL2                                                    | FV/FI*1<br>C8                             | E_FCSEL1                                        | MI/MV*0                                          | RS0_0<br>C11                                                     | C12                                                                    | C13                                                                      | C14                                                                |

| С                | <b>Ö</b>                                                                 | 0                                                                   | 0                                                                  | 0                                                                             | 0                                                                              | 0                                         | 0                                                           | 0                                         | 0                                               | Ö                                                | 0                                                                | 0                                                                      | 0                                                                        | 0                                                                  |

|                  | IVINO                                                                    | VINPO                                                               | IVMAXO                                                             |                                                                               | RS0_3                                                                          | MI/MV*2                                   | RS0_2                                                       | SVSEL1                                    | DISABLE1                                        | RS1_1                                            | I_FCSEL0                                                         |                                                                        | SENSE0                                                                   | FORCEO                                                             |

|                  | D1                                                                       | D2                                                                  | D3                                                                 | D4                                                                            | D5                                                                             | D6                                        | D7                                                          | D8                                        | D9                                              | D10                                              | D11                                                              | D12                                                                    | D13                                                                      | D14                                                                |

| D                | COMP4 0                                                                  | COMP3 0                                                             | VEE1                                                               | COMP1 0                                                                       | MI/MV*3                                                                        | E FCSEL3                                  | O<br>DISABLE2                                               | <b>O</b>                                  | I FCSEL1                                        | FV/FI*0                                          | E SNSELO                                                         | VCC1                                                                   | RAO                                                                      | RBO                                                                |

|                  | E1                                                                       | E2                                                                  | E3                                                                 | E4                                                                            | E5                                                                             | E_FCSEL3                                  | E7                                                          | E8                                        | E9                                              | E10                                              | E_SNSELU<br>E11                                                  | E12                                                                    | E13                                                                      | E14                                                                |

| Ε                | O<br>IVMIN1                                                              | O<br>IVMON1                                                         | O<br>IVMAX1                                                        | O<br>VCC2                                                                     | O<br>COMP2_0                                                                   | O<br>FV/FI*3                              | O<br>SVSEL2                                                 | 0                                         | O<br>E_SNSEL1                                   | O<br>E_FCSELO                                    | O<br>GND1                                                        | RCO                                                                    | O<br>VEE1                                                                | O<br>VCC2                                                          |

|                  | F1                                                                       | F2                                                                  | F3                                                                 | F4                                                                            | F5                                                                             | F6                                        | F7                                                          | F8                                        | F9                                              | F10                                              | F11                                                              | F12                                                                    | F13                                                                      | F14                                                                |

| F                | O<br>COMP1_1                                                             | O<br>IVIN1                                                          | COMP2_1                                                            | COMP3_1                                                                       | O<br>VINP1                                                                     |                                           |                                                             |                                           |                                                 | O<br>RESINO                                      | RDO                                                              | O<br>FORCE1                                                            | O<br>RESIN1                                                              | O<br>GND2                                                          |

|                  | G1                                                                       | G2                                                                  | G3                                                                 | G4                                                                            | G5                                                                             | G6 \                                      | G7                                                          |                                           |                                                 | G10                                              | G11                                                              | G12                                                                    | G13                                                                      | G14                                                                |

| G                | O<br>VEE2                                                                | COMP4_1                                                             | VCC3                                                               | O<br>IVMON2                                                                   | IVMINO                                                                         |                                           |                                                             |                                           |                                                 | SENSE1                                           | RA1                                                              | RB1                                                                    | RD1                                                                      | RC1                                                                |

|                  | H1                                                                       | H2                                                                  | H3                                                                 | H4                                                                            | H5                                                                             | H6                                        | H7                                                          |                                           |                                                 | H10                                              | H11                                                              | H12                                                                    | H13                                                                      | H14                                                                |

|                  | $\sim$                                                                   | _                                                                   |                                                                    |                                                                               |                                                                                | 11 D                                      | 11 0                                                        |                                           |                                                 |                                                  |                                                                  |                                                                        |                                                                          |                                                                    |

| Н                | O<br>IVMAX2                                                              | O<br>IVMIN2                                                         | O<br>VINP2                                                         | O<br>IVIN2                                                                    | O<br>COMP4_2                                                                   |                                           | ll Pad Co<br>(No Solo                                       | ler Ball)                                 |                                                 | 0                                                | O<br>VEE2                                                        | O<br>VCC3                                                              | O<br>FORCE2                                                              | O<br>SENSE2                                                        |

|                  | J1                                                                       | J2                                                                  | VINP2                                                              | IVIN2                                                                         | COMP4_2                                                                        |                                           |                                                             |                                           |                                                 | J10_                                             | VEE2                                                             | VCC3                                                                   | FORCE2                                                                   | SENSE2                                                             |

| H                | IVMAX2                                                                   | IVMIN2                                                              | VINP2                                                              | IVIN2                                                                         | COMP4_2                                                                        |                                           | (No Solo                                                    | ler Ball)                                 |                                                 |                                                  | VEE2                                                             | VCC3                                                                   | FORCE2                                                                   | SENSE2                                                             |

| J                | J1 O COMP2_2                                                             | IVMIN2  J2  COMP1_2  K2                                             | VINP2  J3  COMP3_2  K3                                             | IVIN2  J4  O IVMON3  K4                                                       | COMP4_2  J5  O  IVIN3  K5                                                      | J6 K6 _                                   | (No Solo                                                    | ler Ball)                                 | J9                                              | J10<br>RC2<br>K10                                | VEE2  J11  GND3  K11                                             | VCC3 J12 O RESIN2 K12                                                  | FORCE2  J13  O  RB2  K13                                                 | SENSE2  J14  O  RA2  K14                                           |

|                  | IVMAX2  J1  COMP2_2  K1  O                                               | IVMIN2  J2  COMP1_2  K2  O                                          | VINP2  J3  COMP3_2  K3  O                                          | IVIN2  J4  O IVMON3  K4  O                                                    | COMP4_2  J5  O IVIN3  K5  O                                                    | л <sub>6</sub>                            | (No Solo                                                    | ler Ball)                                 | J9 <b>К</b> 9 <b>О</b>                          | J10<br>O<br>RC2<br>K10                           | VEE2  J11  O  GND3  K11  O                                       | VCC3 J12 O RESIN2 K12 O                                                | FORCE2  J13  O  RB2  K13  O                                              | SENSE2  J14  O  RA2  K14  O                                        |

| J                | IVMAX2  J1  COMP2_2  K1  VEE3                                            | IVMIN2  J2  COMP1_2  K2  VCC4                                       | VINP2  J3  COMP3_2  K3  IVMIN3                                     | J4 O IVMON3 K4 O COMP1_3                                                      | J5 O IVIN3 K5 O E_FC_IN                                                        |                                           | (No Solo                                                    | ler Ball)  K8  O  VIHH1                   | VIH0                                            | J10<br>RC2<br>K10<br>RA3                         | VEE2 J11 O GND3 K11 O SENSE3                                     | VCC3 J12 O RESIN2 K12 O RD2                                            | FORCE2  J13  O  RB2  K13  VCC4                                           | SENSE2  J14  O  RA2  K14  O  VEE3                                  |

| J                | IVMAX2  J1  COMP2_2  K1  O                                               | IVMIN2  J2  COMP1_2  K2  O                                          | VINP2  J3  COMP3_2  K3  O                                          | IVIN2  J4  O IVMON3  K4  O                                                    | COMP4_2  J5  O IVIN3  K5  O                                                    | л <sub>6</sub>                            | (No Solo                                                    | ler Ball)                                 | J9 <b>К</b> 9 <b>О</b>                          | J10<br>O<br>RC2<br>K10                           | VEE2  J11  O  GND3  K11  O                                       | VCC3 J12 O RESIN2 K12 O                                                | FORCE2  J13  O  RB2  K13  O                                              | SENSE2  J14  O  RA2  K14  O                                        |

| J                | IVMAX2  J1  COMP2_2  K1  VEE3  L1                                        | IVMIN2  J2  COMP1_2  K2  VCC4  L2                                   | VINP2  J3  COMP3_2  K3  IVMIN3  L3                                 | IVIN2  J4  O IVMON3  K4  O COMP1_3  L4                                        | COMP4_2  J5  O IVIN3  K5  O E_FC_IN                                            | K6 O VIHH3                                | (No Solo                                                    | Ier Ball)  K8  O  VIHH1  L8               | K9 O VIHO                                       | J10 O RC2 K10 O RA3 L10                          | VEE2  J11  O  GND3  K11  O  SENSE3  L11                          | VCC3 J12 O RESIN2 K12 O RD2 L12                                        | FORCE2  J13  O  RB2  K13  O  VCC4                                        | SENSE2  J14  O  RA2  K14  O  VEE3  L14                             |

| J<br>K<br>L      | IVMAX2  J1  COMP2_2  K1  VEE3  L1  IVMAX3                                | IVMIN2  J2  COMP1_2  K2  VCC4  L2  VINP3                            | VINP2  J3  COMP3_2  K3  IVMIN3  L3  COMP4_3  M3                    | IVIN2  J4  O IVMON3  K4  O COMP1_3  L4  O E_SN_IN  M4                         | COMP4_2  J5  O  IVIN3  K5  O  E_FC_IN  L5  O  VILH3  M5                        | K6 O VIHH3 L6 O VILH2 M6 _                | (No Solo                                                    | K8 O VIHH1 L8 VILH1 M8_                   | K9 O VIHO L9 O VILO M9                          | J10 O RC2 K10 O RA3 L10 VIHHO                    | VEE2  J11  O GND3  K11  O SENSE3  L11  C RB3  M11                | VCC3  J12  O  RESIN2  K12  O  RD2  L12  FORCE3                         | FORCE2  J13  O  RB2  K13  O  VCC4  L13  O  RESIN3                        | SENSE2  J14  O  RA2  K14  O  VEE3  L14  O  GND4  M14_              |

| J                | IVMAX2  J1 O COMP2_2  K1 O VEE3  L1 O IVMAX3                             | IVMIN2  J2  COMP1_2  K2  VCC4  L2  VINP3                            | VINP2  J3  COMP3_2  K3  IVMIN3  L3  COMP4_3                        | IVIN2  J4  O IVMON3  K4  O COMP1_3  L4  O E_SN_IN                             | COMP4_2  J5  O IVIN3  K5  O E_FC_IN  L5  O VILH3                               | K6                                        | (No Solo                                                    | K8 O VIHH1 L8 O VILH1 M8 O                | K9 O VIHO L9 O VILO                             | J10 O RC2 K10 O RA3 L10 O VIHHO                  | VEE2  J11  GND3  K11  O  SENSE3  L11  O  RB3                     | VCC3  J12  O  RESIN2  K12  O  RD2  L12  O  FORCE3                      | FORCE2  J13  O  RB2  K13  O  VCC4  L13  O  RESIN3                        | SENSE2  J14  O  RA2  K14  O  VEE3  L14  O  GND4                    |

| J<br>K<br>L      | IVMAX2  J1  COMP2_2  K1  VEE3  L1  IVMAX3                                | IVMIN2  J2  COMP1_2  K2  VCC4  L2  VINP3                            | VINP2  J3  COMP3_2  K3  IVMIN3  L3  COMP4_3  M3                    | IVIN2  J4  O IVMON3  K4  O COMP1_3  L4  O E_SN_IN  M4                         | COMP4_2  J5  O  IVIN3  K5  O  E_FC_IN  L5  O  VILH3  M5                        | K6 O VIHH3 L6 O VILH2 M6 _                | (No Solo                                                    | K8 O VIHH1 L8 VILH1 M8_                   | K9 O VIHO L9 O VILO M9                          | J10 O RC2 K10 O RA3 L10 VIHHO                    | VEE2  J11  O GND3  K11  O SENSE3  L11  C RB3  M11                | VCC3  J12  O  RESIN2  K12  O  RD2  L12  FORCE3                         | FORCE2  J13  O  RB2  K13  O  VCC4  L13  O  RESIN3                        | SENSE2  J14  O  RA2  K14  O  VEE3  L14  O  GND4  M14_              |

| J<br>K<br>L      | IVMAX2  J1  COMP2_2  K1  VEE3  L1  IVMAX3  M1  COMP2_3                   | IVMIN2  J2  COMP1_2  K2  VCC4  L2  VINP3  M2  COMP3_3               | VINP2  J3  COMP3_2  K3  O  IVMIN3  L3  COMP4_3  M3  O              | IVIN2  J4  O IVMON3  K4  O COMP1_3  L4  O E_SN_IN  M4  O VIL3                 | COMP4_2  J5  O IVIN3  K5  O E_FC_IN  L5  O VILH3  M5  O VIH3                   | K6 O VIHH3 L6 O VILH2 M6 O VIL2           | (No Solo    17                                              | K8 O VIHH1 L8 O VILH1 M8 O VIL1           | K9 O VIHO L9 O VILO M9 O VIH1                   | J10                                              | VEE2  J11  O GND3  K11  O SENSE3  L11  O RB3                     | VCC3  J12  O  RESIN2  K12  O  RD2  L12  FORCE3  M12  VEE4              | FORCE2  J13  O  RB2  K13  O  VCC4  L13  O  RESIN3  M13  O  RD3           | SENSE2  J14  O  RA2  K14  O  VEE3  L14  O  GND4  M14  O  RC3       |

| J<br>K<br>L      | IVMAX2  J1 O COMP2_2  K1 O VEE3  L1 O IVMAX3  M1 O COMP2_3  N1 O VEE4    | IVMIN2  J2  O  COMP1_2  K2  VCC4  L2  VINP3  M2  COMP3_3  N2  O     | VINP2  J3  COMP3_2  K3  IVMIN3  L3  COMP4_3  M3  O  N3  O          | IVIN2  J4  O IVMON3  K4  O COMP1_3  L4  O E_SN_IN  M4  O VIL3  N4  O DVH3     | COMP4_2  J5  O IVIN3  K5  O E_FC_IN  L5  O VILH3  M5  O VIH3  N5  O DUTLTH3    | K6 O VIHH3 L6 O VILH2 M6 O VIL2 N6 O DVH2 | K7 O VIHH2 N7 O DUTLTH2                                     | K8 O VIHH1 L8 O VILH1 M8 O VIL1 N8 O DVH1 | K9 O VIHO L9 O VILO M9 O VIH1 N9 O DUTLTH1      | J10                                              | VEE2  J11  O GND3  K11  O SENSE3  L11  O RB3  M11  O DUTGTLO     | VCC3  J12  O  RESIN2  K12  O  RD2  L12  FORCE3  M12  VEE4  N12  O      | FORCE2  J13  O  RB2  K13  VCC4  L13  O  RESIN3  M13  O  RD3  N13         | SENSE2  J14  O RA2  K14  O VEE3  L14  GND4  M14  O RC3  N14  O     |

| J<br>K<br>L<br>M | IVMAX2  J1 O COMP2_2  K1 O VEE3  L1 O IVMAX3  M1 O COMP2_3  N1 O VEE4 P1 | IVMIN2  J2  O  COMP1_2  K2  VCC4  L2  VINP3  M2  COMP3_3  N2  O  P2 | VINP2  J3  O  COMP3_2  K3  O  IVMIN3  L3  O  COMP4_3  M3  O  N3  O | IVIN2  J4  O IVMON3  K4  O COMP1_3  L4  O E_SN_IN  M4  O VIL3  N4  O DVH3  P4 | COMP4_2  J5  O IVIN3  K5  O E_FC_IN  L5  O VILH3  M5  O UH3  N5  O DUTLTH3  P5 | K6 VIHH3 L6 VILH2 M6 VIL2 N6 O DVH2 P6    | (No Solo  J7  K7  O  VIHH2  M7  O  VIH2  N7  O  DUTLTH2  P7 | K8 O VIHH1 L8 O VILH1 N8 O DVH1 P8        | K9 O VIHO L9 O VILO M9 O VIH1 N9 O DUTLTH1 P9 _ | J10 RC2 K10 RA3 L10 VIHHO M10 VILHO N10 DVLO P10 | VEE2  J11  O GND3  K11  O SENSE3  L11  O RB3  M11  O DUTGTLO P11 | VCC3  J12  O  RESIN2  K12  O  RD2  L12  FORCE3  M12  VEE4  N12  O  P12 | FORCE2  J13  O  RB2  K13  VCC4  L13  O  RESIN3  M13  O  RD3  N13  O  P13 | SENSE2  J14  O RA2  K14  O VEE3  L14  GND4  M14  O RC3  N14  O P14 |

| J<br>K<br>L      | IVMAX2  J1 O COMP2_2  K1 O VEE3  L1 O IVMAX3  M1 O COMP2_3  N1 O VEE4    | IVMIN2  J2  O  COMP1_2  K2  VCC4  L2  VINP3  M2  COMP3_3  N2  O     | VINP2  J3  COMP3_2  K3  IVMIN3  L3  COMP4_3  M3  O  N3  O          | IVIN2  J4  O IVMON3  K4  O COMP1_3  L4  O E_SN_IN  M4  O VIL3  N4  O DVH3     | COMP4_2  J5  O IVIN3  K5  O E_FC_IN  L5  O VILH3  M5  O VIH3  N5  O DUTLTH3    | K6 O VIHH3 L6 O VILH2 M6 O VIL2 N6 O DVH2 | K7 O VIHH2 N7 O DUTLTH2                                     | K8 O VIHH1 L8 O VILH1 M8 O VIL1 N8 O DVH1 | K9 O VIHO L9 O VILO M9 O VIH1 N9 O DUTLTH1      | J10                                              | VEE2  J11  O GND3  K11  O SENSE3  L11  O RB3  M11  O DUTGTLO     | VCC3  J12  O  RESIN2  K12  O  RD2  L12  FORCE3  M12  VEE4  N12  O      | FORCE2  J13  O  RB2  K13  VCC4  L13  O  RESIN3  M13  O  RD3  N13         | SENSE2  J14  O RA2  K14  O VEE3  L14  GND4  M14  O RC3  N14  O     |

**TARGET**

## Circuit Description

#### Circuit Overview

The Edge4707 is a quad channel parametric test and measurement unit that can :

- Force Voltage / Measure Current

- Force Current / Measure Voltage

- Force Voltage / Measure Voltage

- Force Current / Measure Current

Each PMU channel can force or measure voltage over a 15V range and force or measure current over four distinct ranges:

- ± 2 μA

- $\pm$  20  $\mu$ A

- $\pm$  200  $\mu$ A

- ± 2 mA.

An on-board window comparator provides two bit output range classification. Also, a monitor passes a real time analog voltage which tracks either the measured current or voltage.

#### **PPMU Functionality**

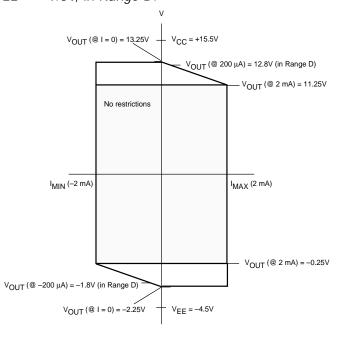

The trapezoid in Figure 1 describes the current-voltage functionality of the PMU with VCC = 15.5V and VEE = -4.5V, in Range D.

NOTE: Negative current implies current is flowing into the 4707 from DUT.

Figure 1. PMU Functionality

#### **Control Inputs**

FV/FI\* is a TTL compatible input which determines whether the PMU forces voltage or current, and MI/MV\* is a TTL compatible input which determines whether the PMU measures current or voltage. FV/FI\* and MI/MV\* are independent for each PMU. Table 1 describes the modes of operation controlled by these pins.

| FV / FI* | MI/MV* | Mode of Operation              |

|----------|--------|--------------------------------|

| 0        | 0      | Force Current, Measure Voltage |

| 0        | 1      | Force Current, Measure Current |

| 1        | 0      | Force Voltage, Measure Voltage |

| 1        | 1      | Force Voltage, Measure Current |

Table 1.

RSO and RS1 are TTL compatible inputs to an internal analog mux which selects an external resistor corresponding to a desired current range. The truth table for RSO to RS1, along with the associated external resistor values and current ranges, is shown in Table 2. RSO and RS1 are independent for each channel of the 4707.

| RS1 | RS0 | Range | Current<br>Range | "Nominal" Ext. R  |

|-----|-----|-------|------------------|-------------------|

| 0   | 0   | А     | ± 2 µA           | $RA = 1M\Omega$   |

| 0   | 1   | В     | ± 20 µA          | $RB = 100K\Omega$ |

| 1   | 0   | С     | ± 200 µA         | $RC = 10K\Omega$  |

| 1   | 1   | D     | ± 2 mA           | $RD = 1K\Omega$   |

Table 2.

#### FORCE/SENSE

FORCE is an analog output which either forces a current or forces a voltage, depending on which operating mode is selected.

SENSE is a high impedance analog input which measures the DUT voltage input in the MV operating mode.

FORCE and SENSE are brought out to separate pins to allow remote sensing.

**TARGET**

## Circuit Description (continued)

#### **IVMON**

IVMON is a real time analog voltage output which tracks the sensed parameter.

In the MV mode, the output voltage displayed at IVMON is a 1:1 mapping of the SENSE voltage. In the MI mode, IVMON follows the equation:

$$IVMON = I(measured) * REXT$$

Using nominal values for the external resistors (RA, RB, RC, and RD), a voltage at IVMON of +2V corresponds to Imax and -2V corresponds to Imin of the selected current range.

The IVMON pin can also be placed into a high impedance state by using the DISABLE input (see Table 3).

| Disable | MI / MV* | Sensed Parameter |

|---------|----------|------------------|

| 1       | Х        | High Impedance   |

| 0       | 0        | Measured Voltage |

| 0       | 1        | Measured Current |

Table 3.

#### Force Voltage Mode

In the FV mode (FV/FI $^*$  = 1), VINP is a high impedance analog voltage input that maps directly to the voltage forced at the FORCE pin.

#### Measure Current Mode

In the MI mode (MI/MV $^*$  = 1), a current monitor is connected in series with the PMU forcing amplifier. This monitor generates a voltage that is proportional to the current passing through it, and is brought out to IVMON. This voltage (corresponding to the measured current) is also tested by the on-board window comparator.

#### Force Current Mode (see page 15)

In the FI mode ( $FV/FI^* = 0$ ), IVIN is a high impedance analog voltage input that is converted into a current at the FORCE pin using the following relationship:

Forced Current = IVIN / REXT

(Positive current is defined as current flowing out of the FORCE pin.) The IVIN input voltage range and forced current (at FORCE) can be seen in Table 4.

| IVIN | Corresponding<br>Forced Current |

|------|---------------------------------|

| +2V  | lmax (full scale)               |

| OV   | 0                               |

| -2V  | lmin (full scale)               |

Table 4.

#### Measure Voltage Mode

In the MV mode (MI/MV $^*$  = 0), DUT voltage is measured via the SENSE input pin. Note that EXT\_SENSE\_SEL = 0 when the Edge4707 SENSE is used. This measured voltage is also tested with the on-board window comparator.

#### Comparator

The Edge4707 features an on-board window comparator which provides two-bit measurement range classification. IVMAX and IVMIN are high impedance analog inputs that establish the upper and lower thresholds for the window comparator.

In the MI mode, an I/V MAX input of +2V will set the upper threshold of the window comparator to a voltage corresponding to +FSC (full-scale current), and an I/V MIN input of -2V will set the lower threshold to a voltage corresponding to -FSC (positive current is defined as current flowing out of the PMU).

DUTGTL the DUTLTH are LVTTL compatible outputs which indicate the range of the measured parameter in relation to IVMIN and IVMAX. Comparator functionality is summarized in Table 5 for MI Mode and Table 6 for MV mode.

TARGET

# Circuit Description (continued)

| TEST CONDITION                        | DUT LTH | DUT GTL |

|---------------------------------------|---------|---------|

| IVMON > IVMAX<br>IVMON < IVMAX        | 0<br>1  | N/A     |

| IVMON > IVMIN<br>IVMON < IVMIN        | N/A     | 1<br>0  |

| IVMON < IVMAX<br>and<br>IVMON > IVMIN | 1       | 1       |

Table 5. MI Comparator Truth Table

| TEST CONDITION                       | DUT LTH | DUT GTL |

|--------------------------------------|---------|---------|

| SENSE > IVMAX<br>SENSE < IVMAX       | 0<br>1  | N/A     |

| SENSE > IVMIN<br>SENSE < IVMIN       | N/A     | 1<br>0  |

| SENSE < IVMAX<br>and<br>SENSE >IVMIN | 1       | 1       |

Table 6. MV Comparator Truth Table

**TARGET**

# Circuit Description (continued)

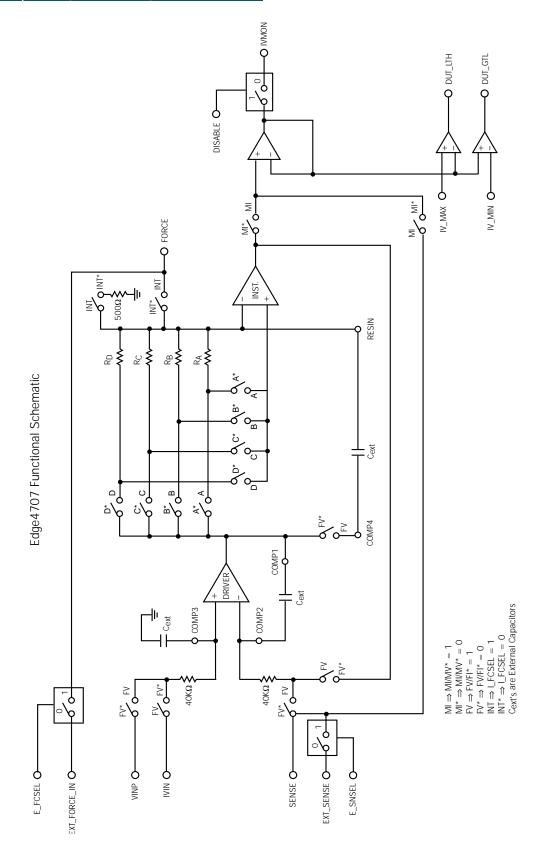

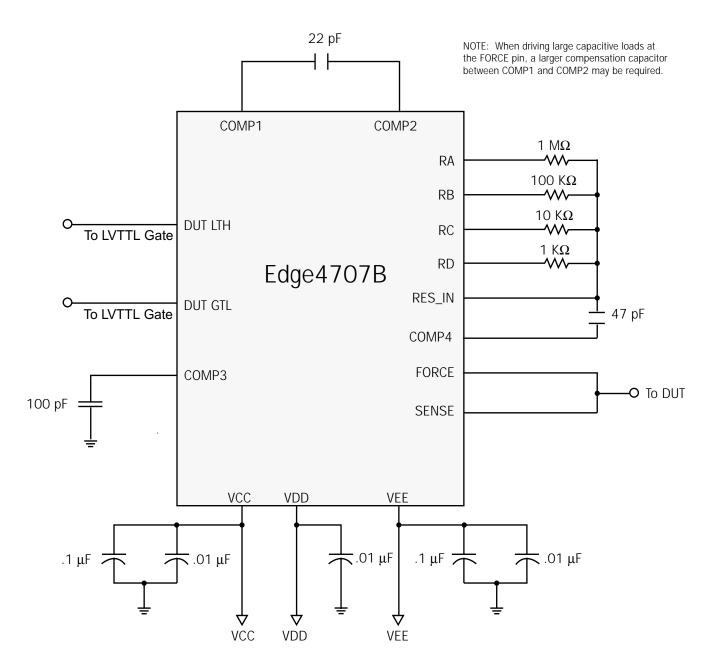

Figure 2. Edge4707 Functional Schematic

TARGET

## Circuit Description (continued)

#### **REXT Selection**

The Edge 4707 is designed for the voltage drop across RA, RB, RC, and RD to be  $\leq$  2V with the maximum current passing through them. However, these resistor values can be changed to support different applications.

Increasing the maximum current beyond the nominal range is not recommended. However, decreasing the maximum current is allowed by increasing the external resistor using the equation IMAX = 2V / REXT.

#### **Switch Operation on Force and Sense Lines**

Each channel of the Edge4707 features two switches connected to the FORCE output pin (External Force  $=30\Omega$ , Internal Force  $=100\Omega$ ) and one  $1K\Omega$  switch connected to the SENSE input pin. These switches are controlled by the TTL compatible inputs I\_FCSEL, E\_FCSEL, and E\_SNSEL. Switch operation is described in Table 7.

| Switch                            | Switch Select<br>Name | Open/Close<br>State on Switch |

|-----------------------------------|-----------------------|-------------------------------|

| 100Ω, to internal force circuitry | I_FCSEL               | 0 = Open<br>1 = Closed        |

| 30Ω, to external force circuitry  | E_FCSEL               | 0 = Open<br>1 = Closed        |

| 1KΩ, to external sense circuitry  | E_SNSEL               | 0 = Open<br>1 = Closed        |

Table 7.

These switches can be configured to route the Edge4707 for external forcing or sensing operations (see Figure 2). For external forcing operation, the switch controlled by I\_FCSEL can be used to internally isolate the PMU from the FORCE output. This enables the user to connect the FORCE pin to an external device connected to the E\_FC\_IN pin using the switch controlled by the E\_FC\_SEL input. I\_FCSEL and E\_FCSEL functionality is described in Table 8.

| I_FCSEL | E_FCSEL | FORCE             |

|---------|---------|-------------------|

| 0       | 0       | HiZ               |

| 1       | 1       | Illegal Condition |

| 1       | 0       | VINP              |

| 0       | 1       | E_FC_IN           |

Table 8.

For external sense operation, the switch controlled by E\_SNSEL can be used to internally connect the SENSE input pin to the E\_SN\_IN output pin (see Figure 2). This allows the user to use the E\_SN\_IN pin for remote sensing.

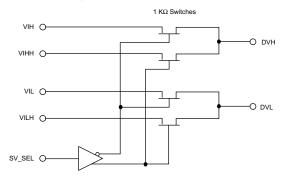

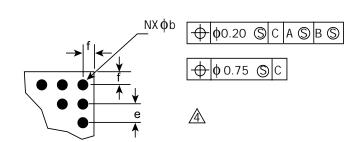

#### Analog MUX

The Edge4707 has a separate analog mux section which is intended for 12V flash programming signal muxing with lower, more standard voltages. There are five inputs for this section, all of which are brought out to external pins (see Figure 3). The two outputs, DVH and DVL, connect to driver reference voltages of the Edge720 (or other pin electronics drivers).

Figure 3. Analog MUX Section

(Typically used to provide flash programming and standard voltages to driver pin electronic references.)

The truth table for SV-SEL is shown in Table 9.

| SV_SEL |                                            |

|--------|--------------------------------------------|

| 0      | DVH = VIH<br>DVL = VIL                     |

| 1      | DVH = VIHH<br>DVL = VILH<br>(supervoltage) |

Table 9. SV-SEL Truth Table

**TARGET**

# Circuit Description (continued)

#### **Short Circuit Protection**

The Edge 4707 is designed to survive a direct short circuit to any legal voltage at the FORCE and SENSE pins, by virtue of a limited current, which results from the presence of an external current sense resistor (normally 1 K $\Omega$  to 1M $\Omega$ ) in the FORCE path.

### **Transient Clamps**

The Edge 4707 has on-board clamps to limit the voltage and current spikes that might result from either changing the current range or changing the operating mode.

**TARGET**

## **Application Information**

## **Required External Components (Per Channel)**

Actual decoupling capacitor values depend on the system environment.

**TARGET**

## Application Information (continued)

#### Calibration

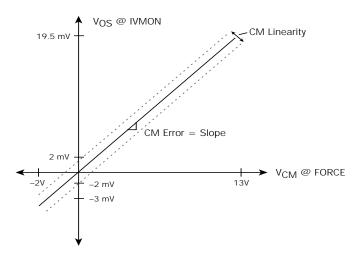

In order to attain a high degree of accuracy in a typical ATE application, offset and gain errors are accounted for through software calibration. When operating the Edge4707 in the Measure Current (MI) or Force Current (FI) modes, an additional source of error, common mode error, should be accounted for. Common mode error is a measure of how the common mode voltage,  $V_{CM}$ , at the input of the current sense amplifier affects the forced or measured current values (see Figure 4). Since this error is created by internal resistors in the current sense amplifier, it is very linear in nature.

Using the common mode error and common mode linearity specifications, one can see that with a small number of calibration steps (see Applications note E4707-A1), the effect of this error can be significantly reduced.

NOTE: In some cases, slope may be negative.

Figure 4. Graphical Representation of Common Mode Error

#### Maximum Input Voltage Range for FV Mode

In order to ensure that the full-scale output voltage range (FSV) can be achieved by the 4707, errors such as gain, linearity, and offset must be taken into account when determining the input voltage range required at VINP. The equations in Table 10 can be used to determine the input voltage range required at VINP to achieve full scale voltage (FSV) at the FORCE pin.

| VINP (Worst Case)                                      | FORCE |

|--------------------------------------------------------|-------|

| <u>FSV</u><br>Gain + V <sub>OS</sub> + LInearity Error | + FSV |

| <u>-FSV</u><br>Gain + Vos + Linearity Error            | – FSV |

Table 10.

Example: If it is desired to operate the 4707 with a FV range of –2V to 13V, the VINP input voltages in Table 11 may be required.

| VINP   | FORCE |

|--------|-------|

| 13.3V  | +13V  |

| -2.13V | -2V   |

Table 11.

**TARGET**

## Application Information (continued)

#### Maximum Input Voltage Range for FI Mode

In order to ensure that the full-scale output current range (FSC) can be achieved by the 4707, errors such as gain, linearity, common mode, and offset must be taken into account when determining the input voltage range required at IVIN. The equations in Table 12 can be used to determine the input voltage range required at IVIN to achieve full scale current (FSC) at the FORCE pin.

| IVIN (Worst Case)                                                          | Corresponding<br>Forced Current |

|----------------------------------------------------------------------------|---------------------------------|

| 2V Gain + Vos + Common Mode Error + Linearity Error                        | + FSC                           |

| $\frac{-2V}{Gain}$ + V <sub>OS</sub> + Common Mode Error + Linearity Error | - FSC                           |

Table 12.

Example: To guarantee that the 4707 is capable of forcing  $\pm$  2 mA with REXT = 1K $\Omega$  (Range D), the input voltages in Table 13 may be required.

| IVIN   | Corresponding<br>Forced Current |

|--------|---------------------------------|

| 2.15V  | 2 mA                            |

| -2.15V | – 2 mA                          |

Table 13.

TARGET

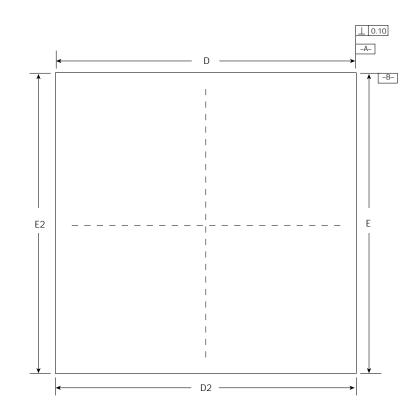

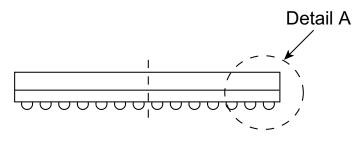

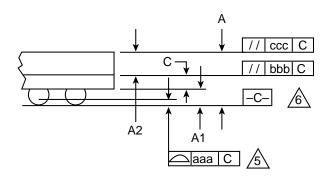

# Package Information

**Top View**

**Bottom View**

**TARGET**

## Package Information (continued)

**Side View**

Detail A Detail B

#### NOTES:

- 1. All dimensions are in millimeters.

- 2. 'e' represents the basic solder ball grid pitch.

- 3. 'M' represents the basic solder ball matrix size, and symbol 'N' is the maximum allowable number of balls after depopulating.

'b' is measurable at the maximum solder ball diameter parallel to primary datum -C-.

Dimension 'ccc' is measured parallel to primary datum –C–.

Primary datum –C– and seating plane are defined by the spherical crowns of the solder balls.

- 7. Package surface shall be matte finish charmilles 24 to 27.

- 8. Package warp shall be 0.050 mm maximum.

- 9. Substrate material base is BT resin.

- 10. The overall package thickness 'A' already considers collapse balls.

| Dimensional References |            |            |       |  |  |  |

|------------------------|------------|------------|-------|--|--|--|

| REF.                   | MIN.       | NOM.       | MAX.  |  |  |  |

| А                      | 1.30       | 1.45       | 1.55  |  |  |  |

| A1                     | 0.30       | 0.40       | 0.45  |  |  |  |

| A2                     | 0.65       | 0.70       | 0.75  |  |  |  |

| D                      | 11.80      | 12.00      | 12.20 |  |  |  |

| D1                     |            | 10.40 BSC. |       |  |  |  |

| D2                     | 11.80      | 12.00      | 12.20 |  |  |  |

| E                      | 11.80      | 12.00      | 12.20 |  |  |  |

| E1                     | 10.40 BSC. |            |       |  |  |  |

| E2                     | 11.80      | 12.00      | 12.20 |  |  |  |

| b                      | 0.50       | 0.55       | 0.60  |  |  |  |

| С                      |            | 0.35       |       |  |  |  |

| aaa                    |            |            | 0.15  |  |  |  |

| bbb                    |            |            | 0.20  |  |  |  |

| ccc                    |            |            | 0.25  |  |  |  |

| е                      | 0.725      | 0.80       | 0.875 |  |  |  |

| f                      | 0.70       | 0.80       | 0.90  |  |  |  |

| М                      | 14         |            |       |  |  |  |

| N                      | 180        |            |       |  |  |  |

| •                      |            | ·          |       |  |  |  |

**TARGET**

## **Recommended Operating Conditions**

| Parameter                                        | Symbol               | Min   | Тур  | Max   | Units |

|--------------------------------------------------|----------------------|-------|------|-------|-------|

| Positive Analog Power Supply (relative to GND)   | VCC                  | 15.25 | 15.5 | 15.75 | V     |

| Negative Analog Power Supply (relative to GND)   | VEE                  | -4.75 | -4.5 | -4.25 | V     |

| Total Analog Power Supply                        | VCC – VEE            | 19.5  | 20   | 20.5  | V     |

| Digital Power Supply (relative to GND)           | VDD                  | 3.15  | 3.3  | 3.45  | V     |

| Case Temperature                                 | TC                   | 25    |      | 65    | °C    |

| Thermal Resistance of Package (Junction to Case) | $	heta_{	extsf{JC}}$ |       | 4.1  |       | °C/W  |

## Absolute Maximum Ratings

| Parameter                                         | Symbol                             | Min      | Тур | Max       | Units |

|---------------------------------------------------|------------------------------------|----------|-----|-----------|-------|

| Positive Power Supply                             | VCC                                |          |     | 20        | V     |

| Negative Power Supply                             | VEE                                | -10      |     |           | V     |

| Total Power Supply                                | VCC – VEE                          | 0        |     | 21        | V     |

| Digital Power Supply                              | VDD                                | GND5     |     | VCC       | V     |

| Digital Inputs                                    |                                    | 5        |     | 7.0       | V     |

| Analog Inputs                                     |                                    | VEE – .5 |     | VCC + .5  | V     |

| Analog MUX Breakdown Voltage                      | VI[H, L, HH, LH] –<br>DV[L, H]     |          |     | VCC – VEE | V     |

| Current Capability of MUX                         | I <sub>MUX</sub>                   | -4.8     |     | 4.8       | mA    |

| External Force and Sense Switch Breakdown Voltage | E_FC_IN - FORCE<br>E_SN_IN - FORCE |          |     | VCC – VEE | V     |

| Storage Temperature                               |                                    | -55      |     | +125      | °C    |

| Junction Temperature                              |                                    | -65      |     | +125      | °C    |

| Soldering Temperature                             |                                    |          |     | 260       | °C    |

Stresses above listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

TARGET

## DC Characteristics

## **Power Supplies**

| Parameter                                                                                    | Symbol            | Min | Тур               | Max           | Units          |

|----------------------------------------------------------------------------------------------|-------------------|-----|-------------------|---------------|----------------|

| Power Supply Consumption (Note 1) Positive Supply Negative Supply Digital Supply (Quiescent) | ICC<br>IEE<br>IDD |     |                   | 30<br>30<br>1 | mA<br>mA<br>mA |

| Power Supply Rejection Ratio (Notes 2, 3) 1 MHz 500 kHz 100 kHz                              | PSRR              |     | 8.5<br>14.5<br>29 |               | dB<br>dB<br>dB |

## **Force Voltage**

| Parameter                                                                                                                              | Symbol                              | Min                      | Тур               | Max                      | Units             |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------|-------------------|--------------------------|-------------------|

| Input Voltage Range @ VINP                                                                                                             | VVINP                               | VEE + 2                  |                   | VCC - 1.75               | V                 |

| Input Bias Current                                                                                                                     | I <sub>VINP</sub>                   | -1                       | 0                 | 1                        | μΑ                |

| Output Forcing Voltage (positive full scale current through REXT)                                                                      | VFORCE                              | VEE + 2.25               |                   | VCC - 4.25               | V                 |

| Output Forcing Voltage (zero current through REXT) Output Forcing Voltage (negative full scale current through REXT)                   | VFORCE<br>VFORCE                    | VEE + 2.25<br>VEE + 4.25 |                   | VCC - 2.25<br>VCC - 2.25 | V<br>V            |

| Voltage Accuracy Offset Gain Linearity                                                                                                 | Vos<br>FV Gain<br>FV INL            | –100<br>.985<br>–0.025   | ±.01              | 100<br>1.015<br>+0.025   | mV<br>V/V<br>%FSR |

| Temperature Dependence (Note 6) Temperature Coefficient of Offset Temperature Coefficient of Gain Temperature Coefficient of Linearity | ΔVos/ΔT<br>ΔFVGain/ΔT<br>ΔFV INL/ΔT |                          | TBD<br>TBD<br>TBD |                          | TBD<br>TBD<br>TBD |

**TARGET**

## DC Characteristics (continued)

### **Measure Current**

| Parameter                                                                                                                                                  | Symbol                               | Min                      | Тур               | Max                         | Units                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------|-------------------|-----------------------------|----------------------|

| Current Measurement Range Range A Range B Range C Range D                                                                                                  | IMEASURE                             | -2<br>-20<br>-200<br>-2  |                   | 2<br>20<br>200<br>2         | μΑ<br>μΑ<br>μΑ<br>mA |

| Current Measurement Accuracy Measure Current Offset Gain Linearity (measured at IVMON) FORCE = VEE + 4.25 to VCC - 5.25V FORCE = VCC - 5.25 to VCC - 4.25V | Vos<br>MI Gain<br>MI INL             | -150<br>.985<br>05<br>08 | ±.01              | +150<br>1.015<br>.05<br>.08 | mV<br>% FSR<br>% FSR |

| Common Mode Error                                                                                                                                          | CM Error                             | -1.5                     |                   | 1.5                         | mV/V                 |

| Common Mode Linearity                                                                                                                                      | ∆CM Error                            | 05                       |                   | .05                         | %FSR                 |

| Temperature Dependence (Note 6) Temperature Coefficient of Offset Temperature Coefficient of Gain Temperature Coefficient of Linearity                     | ΔVos/ΔT<br>ΔMI Gain/ΔT<br>ΔMI INL/ΔT |                          | TBD<br>TBD<br>TBD |                             | TBD<br>TBD<br>TBD    |

#### **Force Current**

| Parameter                                                                                                                              | Symbol                               | Min                                    | Тур               | Max                                    | Units                   |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------|-------------------|----------------------------------------|-------------------------|

| Input Voltage Range @ IVIN                                                                                                             | VIVIN                                | -2.25                                  |                   | 2.25                                   | V                       |

| Input Bias Current                                                                                                                     | IIVIN                                | -1                                     | 0                 | 1                                      | μΑ                      |

| Output Forcing Current Range A Range B Range C Range D                                                                                 | IFORCE                               | -2<br>-20<br>-200<br>-2                |                   | 2<br>20<br>200<br>2                    | μΑ<br>μΑ<br>μΑ<br>mA    |

| Compliance Voltage Range Positive Full-Scale Current through REXT Zero Current through REXT Negative Full-Scale Current through REXT   | VFORCE                               | VEE + 2.25<br>VEE + 2.25<br>VEE + 4.25 |                   | VCC - 4.25<br>VCC - 2.25<br>VCC - 2.25 | V<br>V<br>V             |

| Current Accuracy Offset Gain Linearity (measured at IVMON) FORCE = VEE + 4.25 to VCC - 5.25V FORCE = VCC - 5.25 to VCC - 4.25V         | los<br>FI Gain<br>FI INL             | -2.5<br>.985<br>05<br>08               | ±.01              | 2.5<br>1.015<br>.05<br>.08             | % FSR<br>% FSR<br>% FSR |

| Common Mode Error (Note 4)                                                                                                             | CM Error                             | -3                                     |                   | 3                                      | mV/V                    |

| Common Mode Linearity                                                                                                                  | ∆CM Error                            | 05                                     |                   | .05                                    | %FSR                    |

| Temperature Dependence (Note 6) Temperature Coefficient of Offset Temperature Coefficient of Gain Temperature Coefficient of Linearity | ΔVos/ΔT<br>ΔFI Gain/ΔT<br>ΔFI INL/ΔT |                                        | TBD<br>TBD<br>TBD |                                        | TBD<br>TBD<br>TBD       |

TARGET

## DC Characteristics (continued)

## Measure Voltage

| Parameter                                                                                                                              | Symbol                               | Min                   | Тур               | Max                  | Units             |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------|-------------------|----------------------|-------------------|

| Voltage Measurement Range                                                                                                              | Vsense                               | VEE + 2.25            |                   | VCC - 2.25           | V                 |

| Voltage Measurement Accuracy<br>Measure Voltage Offset<br>Gain<br>Linearity                                                            | Vos<br>MV Gain<br>MV INL             | –100<br>.985<br>–.025 | ±.01              | 100<br>1.015<br>.025 | mV<br>%FSR        |

| Temperature Dependence (Note 6) Temperature Coefficient of Offset Temperature Coefficient of Gain Temperature Coefficient of Linearity | ΔVos/ΔT<br>ΔMV Gain/ΔT<br>ΔMV INL/ΔT |                       | TBD<br>TBD<br>TBD |                      | TBD<br>TBD<br>TBD |

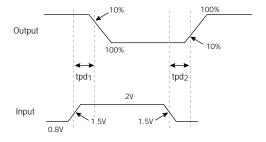

## Digital Inputs (FV/FI\*, MI/MV\*, RSO, RS1, DISABLE, I\_FCSEL, E\_FCSEL, E\_SNSEL, SV\_SEL)

| Parameter                      | Symbol | Min | Тур | Max | Units |

|--------------------------------|--------|-----|-----|-----|-------|

| Input Low Level                | VIL    |     |     | 0.8 | V     |

| Input High Level               | VIH    | 2.0 |     |     | V     |

| Input Bias Current @ OV to VDD | IIN    | -1  | 0   | 1   | μΑ    |

#### **External Force & Sense Switches**

| Parameter                                                                   | Symbol              | Min | Тур  | Max  | Units |

|-----------------------------------------------------------------------------|---------------------|-----|------|------|-------|

| On-resistance – External Force Switches                                     | R <sub>ON_FRC</sub> |     | 30   | 45   | Ω     |

| On-resistance – External Sense Switches                                     | R <sub>ON_SNS</sub> |     | 1000 | 1200 | Ω     |

| HiZ (Switch Open) Leakage Current (Note 5)<br>@ FORCE = -3 to +13V, FI Mode | ILEAK               | -10 |      | +10  | nA    |