# TinyRISC<sup>®</sup> EV4101 Microprocessor Reference Device

# **Technical Summary**

#### **Contents**

| 1  | Introd | luction                                    | 5  |

|----|--------|--------------------------------------------|----|

| 2  | Featu  | ıres                                       | 6  |

| 3  | Block  | Diagram                                    | 6  |

| 4  |        | 01 Programming Model Details               | 8  |

|    | 4.1    | DBX Overview                               | 8  |

|    | 4.2    | SerialICE Port Overview                    | 17 |

|    | 4.3    | BBCC Overview                              | 21 |

|    | 4.4    | System Configuration Register              | 22 |

|    | 4.5    |                                            | 29 |

| 5  | Instru | ction Set Summary                          | 31 |

| 6  | Signa  | al Descriptions                            | 36 |

|    | 6.1    | Bus Interface Signals                      | 37 |

|    | 6.2    | Miscellaneous Signals                      | 40 |

|    | 6.3    | Test Signals                               | 42 |

| 7  | Bus I  | nterface                                   | 44 |

|    | 7.1    | Single Word Read and Burst Read Operations | 44 |

|    | 7.2    | Single Word Writes and Burst Writes        | 46 |

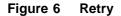

| 8  | Retry  | Support                                    | 49 |

| 9  | Bus I  | Error Support (Abort)                      | 50 |

| 10 | Burst  | Accesses                                   | 50 |

| 11 | Arbitr | ation                                      | 51 |

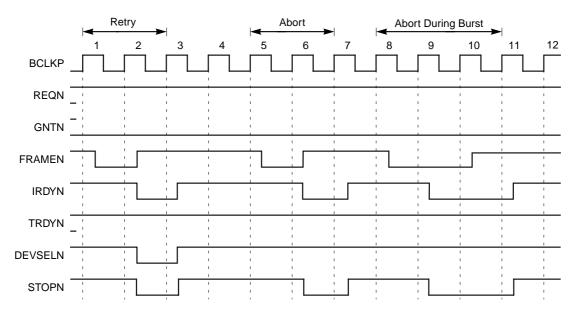

|    | 11.1   | Mode 1: REQN (Input), GNTN (Output)        | 51 |

|    | 11.2   | Mode 2: REQN (Output), GNTN (Input)        | 52 |

| 12 | Inpag  | je Support                                 | 55 |

| 13 | Bus    | Snooping Support                           | 55 |

| 14 | Spec   | ifications                                 | 56 |

|    | 14.1   | AC Timing                                  | 56 |

|    | 14.2   | Electrical Requirements                    | 58 |

| 15 | Pinou  | it, Package, and Ordering Information      | 60 |

| Figures | ,      | EVALUA Defenses De las Blada Discussi                                                   | _        |

|---------|--------|-----------------------------------------------------------------------------------------|----------|

|         | 1<br>2 | EV4101 Reference Device Block Diagram                                                   | 5<br>17  |

|         | 3      | Typical Exception Handler Flow TR4101 System with SerialICE Port                        | 17<br>17 |

|         | 3<br>4 | •                                                                                       | 44       |

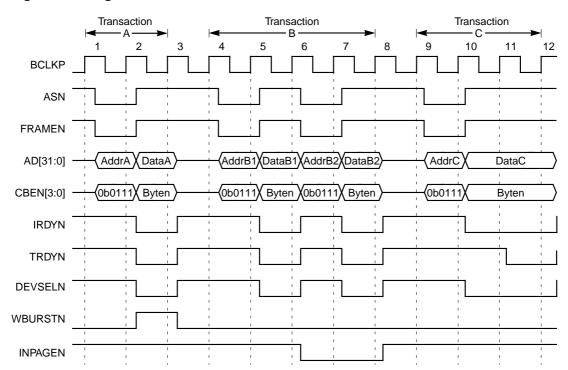

|         | 4<br>5 | Single Word Read Followed by Four-Word Burst Read Single Word and Two-Word Burst Writes | 44       |

|         | 6      | Retry                                                                                   | 50       |

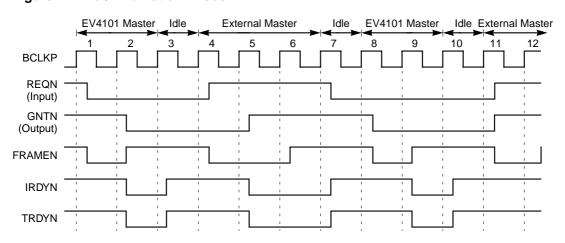

|         | 7      | Bus Arbitration: Mode 1                                                                 | 52       |

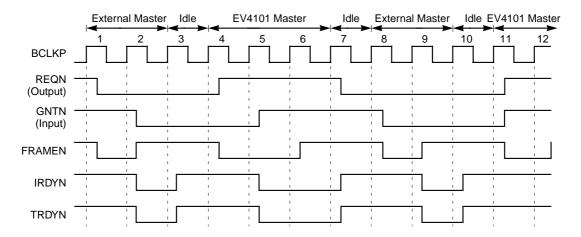

|         | 8      | Bus Arbitration: Mode 2                                                                 | 54       |

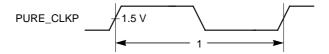

|         | 9      | Clock Timing (PURE_CLKP)                                                                | 56       |

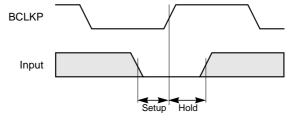

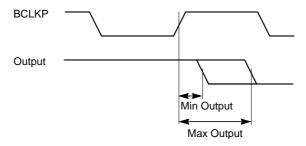

|         | 10     | Input Timing                                                                            | 56       |

|         | 11     | Output Timing                                                                           | 57       |

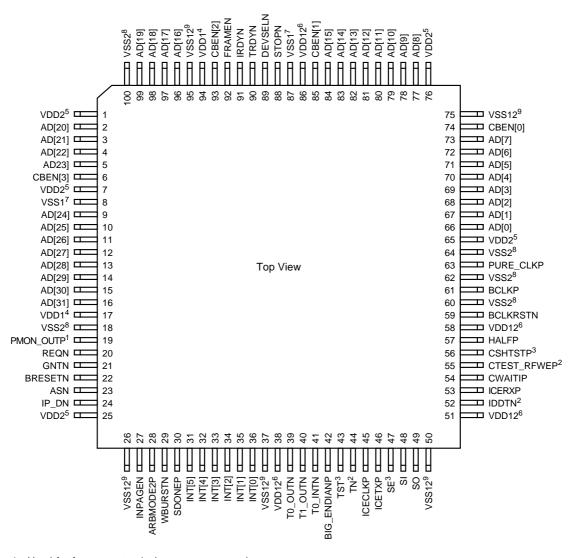

|         | 12     | 100-Pin TQFP Pinout Diagram                                                             | 64       |

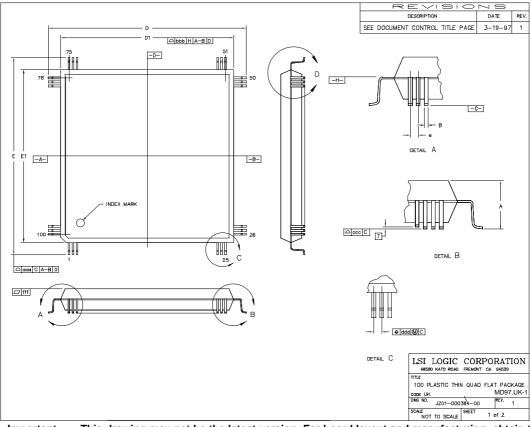

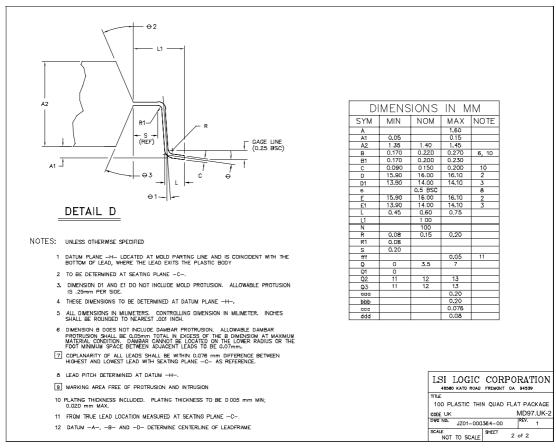

|         | 13     | 100-Lead TQFP (UK) Mechanical Drawing                                                   | 65       |

| Tables  |        |                                                                                         |          |

|         | 1      | DCS Register                                                                            | 9        |

|         | 2      | Enabling Debug Functions                                                                | 11       |

|         | 3      | BPC Register                                                                            | 12       |

|         | 4      | BDA Register                                                                            | 12       |

|         | 5      | BPCM Register                                                                           | 13       |

|         | 6      | BDAM Register                                                                           | 13       |

|         | 7      | MFD Instruction (MIPS II format)                                                        | 14       |

|         | 8      | MTD Instruction (MIPS II format)                                                        | 14       |

|         | 9      | SerialICE Port Register Addresses                                                       | 18       |

|         | 10     | Rx Status Register                                                                      | 19       |

|         | 11     | Rx Setup Register                                                                       | 20       |

|         | 12     | Rx Data Register                                                                        | 20       |

|         | 13     | Tx Status Register                                                                      | 20       |

|         | 14     | Tx Data Register                                                                        | 21       |

|         | 15     | Configuration Register                                                                  | 22       |

|         | 16     | SCR Settings for Software Cache Test Mode                                               | 26       |

|         | 17     | Data Returned from Reading Tag Ram                                                      | 26       |

|         | 18     | Timer Registers                                                                         | 30       |

|         | 19     | Mode Register                                                                           | 30       |

|         | 20     | Status Register                                                                         | 31       |

| 21 | TR4101/EV4101 Instruction Set Summary (32-bits) | 31 |

|----|-------------------------------------------------|----|

| 22 | TR4101/EV4101-Specific System Control Processor |    |

|    | (CP0) Instructions (32-bits)                    | 34 |

| 23 | Multiply/Divide Instructions (with MDU)         | 34 |

| 24 | DBX Instructions                                | 34 |

| 25 | Unimplemented MIPS II Instructions              | 34 |

| 26 | TR4101/EV4101 Instruction Set Summary (MIPS16)  | 35 |

| 27 | EV4101 PURE_CLKP Input Timing                   | 57 |

| 28 | EV4101 AC Input Timing (Alphabetical)           | 57 |

| 29 | EV4101 AC Output Timing (Alphabetical)          | 58 |

| 30 | Absolute Maximum Ratings                        | 59 |

| 31 | Recommended Operating Conditions                | 59 |

| 32 | Capacitance                                     | 59 |

| 33 | DC Characteristics                              | 60 |

| 34 | EV4101 Ordering Information                     | 61 |

| 35 | Alphabetical Pin Description Summary            | 61 |

| 36 | Alphabetical Pin List for the 100-pin TQFP      | 63 |

#### 1 Introduction

The TinyRISC EV4101 Microprocessor Reference Device is a single chip implementation of the TinyRISC TR4101 Microprocessor, a component of LSI Logic's CoreWare<sup>®</sup> Library. The EV4101 Reference Device design contains an extended bus controller (XC) module and several building blocks: instruction and data caches, a timer, a multiply divide unit (MDU), and a basic bus interface unit and cache controller (BBCC). The EV4101 also includes a hardware debug (DBX) module and SerialICE<sup>™</sup> port to enable the user to debug and download software applications through the SerialICE concept. The EV4101 is a 32-bit microprocessor that executes MIPS I, a subset of MIPS II, and a subset of the MIPS16 instructions. MIPS16 is a 16-bit wide instruction set that greatly reduces code size and thereby the amount of memory needed. Figure 1 is a block diagram of the EV4101 Reference Device.

**BBus** TR4101 BIU and Timer 0 Microprocessor **CBus** Cache Core Controller FlexLink (BBCC) Interface Timer 1 Debug D-Cache Module (DBX) Extended PCI-like I-Cache Bus Memory Set 0 Controller Interface Multiply/ (XC) Divide Unit I-Cache (MDU) Set 1 - Rx Input SerialICE Rx Interrupt - Serial Clock Port Tx Output

Figure 1 EV4101 Reference Device Block Diagram

#### 2 Features

- Includes the TR4101 microprocessor core, XC module, and BBCC,

MDU, timer, DBX module, and SerialICE port building blocks

- MIPS I, MIPS II, and MIPS16 instruction set implementation

- Low power management features

- 16 Kbyte two-way set-associative instruction cache (I-cache)

- 8 Kbyte direct-mapped data cache (D-cache)

- Four-deep write buffer

- Hardware and application software debug support with SerialICE

- 3.3-volt, 0.29-micron, cell-based G10<sup>®</sup>-p CMOS process technology

- Cache controller offers advanced instruction and data streaming

- Load scheduling support

- Two 16-bit programmable timers

- Basic PCI-like 32-bit memory interface

- Full- or half-speed bus clock options

- Dual bus arbitration configurations for either host or nonhost operation

- 66 MHz at wccom, when executing MIPS I, MIPS II, and MIPS16

- 3.3-volt operation, 5-volt tolerant inputs

- 66 MIPS peak performance and 53 MIPS sustained at 66 MHz

## 3 Block Diagram

This section describes the internal blocks in the EV4101 Reference Device, shown in Figure 1.

The TR4101 microprocessor core is the main component of the EV4101 Reference Device. The EV4101 executes all MIPS II 32-bit based instructions except for the multiprocessor support instructions. In addition, it executes all but the double word MIPS16 instructions. The microprocessor is implemented with an efficient three-stage pipeline that is extended to four stages for Load Word (LW) and Store Word (SW) type

instructions. Standard MIPS-compiled code will run without change on the TR4101. Code containing a mixture of MIPS I/II and MIPS16 executes without any prior setup of the core.

The TR4101's instruction set includes a WAITI instruction that places the TR4101 into a low-power stall condition until an interrupt is received. For even greater power management, the EV4101 has an output pin that is asserted during this time period, so that the system designer can stop the entire system clock.

The MDU module is attached to the TR4101's FlexLink interface. It is a compact, medium-performance MIPS II compatible arithmetic engine. The MDU module supports 13-cycle integer multiply and multiply accumulate, and 34-cycle divide operation.

The DBX module is attached to the TR4101's FlexLink interface. The FlexLink interface allows a number of new instructions to be added to the microprocessor's default instruction set. The DBX module facilitates debug support by allowing the programmer to insert instruction and data access breakpoints.

The SerialICE port is a full-duplex, serial, receive and transmit port. It is used with the SerialICE concept for downloading application software to the TR4101 and for debugging. The SerialICE concept uses the breakpoints in the DBX module when required in the debug session.

The BBCC is connected to the microprocessor using the CPU bus (CBus). The BBCC is a basic bus interface unit that handles instruction/data block refilling, cache control, load scheduling, and streaming. It contains the four-deep write buffer. Connected to the BBCC are a 16 Kbyte two-way set-associative I-cache and an 8 Kbyte direct-mapped D-cache. The BBCC has an advanced method of streaming data to the microprocessor. Anytime the cache is being refilled, the microprocessor can use the data during the same cycle it is written to the cache. The BBCC is programmable using a system configuration register.

There are two internal 16-bit timers that are included in the EV4101. They are connected to the BBCC using the BBus interface. Each timer has an output that can be either toggled or pulsed. Timer 1 can be placed in a bus Watchdog Mode where a bus error is signalled on excessively long transactions. When the Timer 1 is in Watchdog Mode, the EV4101 detects a bus error when a transaction exceeds the count length that is programmed into Timer 1.

The XC module handles transactions on the BBus and translates them to a PCI-like 32-bit memory interface. Where the BBus uses separate address and data buses, the EV4101 memory interface has a multiplexed address/data bus. The XC can run the memory interface at full speed, or it can divide the clock by two for a half speed system bus. The PCI bus is a multimaster bus, as is the BBus. Therefore, many of the EV4101 bus pins are bidirectional. A PCI bus master outside the EV4101 is also a master on the BBus.

# 4 EV4101 Programming Model Details

This section describes the programming model for the EV4101. It describes the programming models for the TR4101, DBX module, MDU, BBCC, and the timers. This document does not describe all the EV4101 registers. The EV4101 uses an R3000-type CP0. Refer to R3000 documents for information on the EV4101 CP0 registers. For specific information on registers resident in the TR4101, refer to the *TinyRISC TR4101 Microprocessor Core Technical Manual*, document number DB14-000059-00. For further information on the BBCC, MDU, DBX module, and SerialICE port refer to the *TinyRISC TR4101 Building Blocks Technical Manual*, document number DB14-000060-00.

#### 4.1 DBX Overview

The DBX module provides debug support in the EV4101 by providing access in real time to instruction and data access breakpoints. The DBX module is controlled by software through registers.

The DBX gives the programmer access to the DBX registers. For details on the DBX and FlexLink Interface, refer to the *TinyRISC TR4101 Microprocessor Core Technical Manual*.

To detect data and instruction addresses, the DBX monitors the CBus. Refer to the *TinyRISC TR4101 Microprocessor Core Technical Manual* for information on the CBus.

Software controls the DBX module through two new instructions, MTD (Move To Debugger) and MFD (Move From Debugger), that access the DBX registers. This software interface enables use of internal breakpoints to generate a software break to the exception handler.

For information on DBX interfaces to other elements, such as the TR4101, BBCC, and system logic, refer to the *TinyRISC TR4101 Building Blocks Technical Manual*, document number DB14-000060-00.

#### 4.1.1 Registers

Programmers access the DBX registers by using the MTD and MFD instructions. See Section 4.1.2, "Instructions." All bits are read/write, except for the Reserved bits, which are hard wired to zero. Software should, however, always write zeros to the Reserved bits.

The registers in this section have a register number for each Debug Register (dr) which are indicated in parentheses in the subsection headings.

**DCS Register (7)** – The Debug Control and Status (DCS) Register contains the status and enable bits for the debug facilities. All status bits (bits 4 through 0) are sticky, and debug events only set the bits if the enable signals are set. The bits must be cleared by using an MTD Instruction to update the DCS Register. The settings of the UD and KD bits are always the same—setting either bit sets both bits. Reset clears the DE and IBD bits. All other bits are unknown.

MTD Instructions have higher priority than status updates. The DBX updates the DCS Register with MTD data if an MTD Instruction occurs simultaneously with a status update caused by a break event.

Table 1 shows the format of the DCS Register.

#### Table 1 DCS Register

| 31 | 30 | 29 | 28  | 27 | 26 | 25  | 24  | 23 | 22  | 21 5     | 4 | 3 | 2  | 1  | 0  |

|----|----|----|-----|----|----|-----|-----|----|-----|----------|---|---|----|----|----|

| TR | UD | KD | Res | DW | DR | DAE | PCE | DE | IBD | Reserved | W | R | DA | РС | DB |

TR Trap Enable

Setting TR causes debug events to trap to the exception vector provided that internal breaking is enabled; that is, IBD is cleared. When TR is cleared, no trapping occurs, but debug status bits are still updated with debug event information.

31

| KD  | Kernel Mode Debug Event Detection Enable 29 Setting KD enables debug breaks in Kernel Mode. UD and KD always contain the same value. Setting either bit sets both bits.              |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Res | Reserved Bits 28, [21:5] These bits are hard wired to zero. Software should always write zeros to these bits.                                                                        |

| DW  | Data Write Enable  If DAE is enabled, setting DW enables data write event detection.                                                                                                 |

| DR  | Data Read Enable 26 If DAE is enabled, setting DR enables data read event detection.                                                                                                 |

| DAE | Data Access Breakpoint Enable Setting DAE enables data address breakpoint debug events.  25                                                                                          |

| PCE | Program Counter Breakpoint Enable 24 Setting PCE enables program counter breakpoint debug events.                                                                                    |

| DE  | <b>Debug Enable</b> Setting DE enables the debugger. Clearing DE disables the debugger.                                                                                              |

| IBD | Internal Break Disable Setting IBD disables internal breaks. Clearing IBD enables internal breaks. When IBD is set, the DBX does not assert the DBREAK_BBEP signal on a debug event. |

| W   | Write Reference Status  The DBX sets this bit when it has detected a data write debug condition. This bit can only be cleared by software.                                           |

| R   | Read Reference Status  The DBX sets this bit when it has detected a data read-debug condition. This bit can only be cleared by software.                                             |

**User Mode Debug Event Detection Enable**

both bits.

Setting UD enables debug breaks in User Mode. UD and KD always contain the same value. Setting either bit sets

30

UD

#### DA Data Access Debug Condition Status

The DBX sets this bit when it has detected a data access (read or write) debug condition. This bit can only be cleared by software.

#### PC Program Counter Debug Condition Status

The DBX sets this bit when it has detected a program counter debug condition. This bit can only be cleared by software.

#### DB Debug Condition Status

The DBX sets this bit when it has detected a debug event. This bit can only be cleared by software.

Table 2 shows how to enable the DBX functions.

Table 2 Enabling Debug Functions

| TR | UD | KD | DE | IBD | Action on Debug Event                   |

|----|----|----|----|-----|-----------------------------------------|

| 0  | 0  | 0  | 1  | 0   | Status update (only)                    |

| 1  | 1  | 1  | 1  | 0   | Status update and internal break (trap) |

| х  | х  | Х  | 0  | х   | None (DBX disabled)                     |

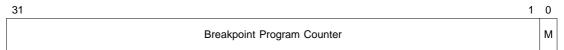

BPC Register (18) – Software uses the Breakpoint Program Counter (BPC) Register to specify a program counter breakpoint. This register is used in conjunction with the Breakpoint Program Counter Mask (BPCM) Register described later. A breakpoint is detected for any instruction in which all enabled bits in the BPC Register match the corresponding bits in the instruction fetch address. The BPC Register contents are undefined after reset.

Note that a breakpoint placed off a word boundary in MIPS II mode, or a breakpoint placed at the start of a 32-bit MIPS16 instruction will not be detected. If a break is to be generated on a 32-bit MIPS16 instruction (EXTEND or JAL/JALX), the breakpoint must be placed at the second halfword of the instruction.

The M-bit of the BPC Register is used to specify whether bits 31 to 1 of the BPC Register specifies a MIPS II address or a MIPS16 address, if M is 1 then BPC specifies a MIPS16 address; otherwise, BPC specifies a MIPS II address.

2

1

0

Table 3 shows the format of the BPC Register.

#### Table 3 BPC Register

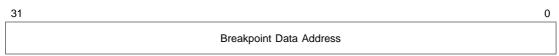

**BDA Register (19)** – Software uses the Breakpoint Data Address (BDA) Register to specify a data address breakpoint. This register is used in conjunction with the Breakpoint Data Address Mask (BDAM) Register described later. A breakpoint is detected for any data reference, including byte and halfword references in which all enabled bits in the BDA Register match the corresponding bits in the data address. The BDA Register contents are undefined after reset.

Note that it is the start address of a data element that is used in the detection; a data breakpoint placed within a word will not be detected unless the address is explicitly targeted by, for example, an LB instruction. If, however, bit 1 and bit 0 of the BDAM Register are both 0, then all accesses to the word are detected.

Table 4 shows the format of the BDA Register.

#### Table 4 BDA Register

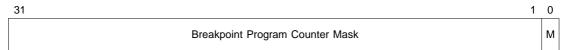

**BPCM** Register (20) – The Breakpoint Program Counter Mask (BPCM) Register masks bits in the BPC Register. Writing a 1 to bit *n* of the BPCM Register enables the bitwise comparison of bit n in the BPC Register with bit n in the instruction fetch address. Conversely, writing a 0 to bit n of the BPCM Register disables the comparison, and forces the breakpoint logic to assume a match between bit n in the BPC and bit n in the instruction fetch address, regardless of the true result. The BPCM Register contents are undefined after reset.

Likewise, the M-bit of the BPCM Register enables or disables the bitwise comparison of the M-bit in the BPC Register with the instruction fetch mode.

Table 5 shows the format of the BPCM Register.

#### Table 5 BPCM Register

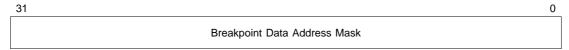

**BDAM** Register (21) – The Breakpoint Data Address Mask (BDAM) Register masks bits in the BDA Register. Writing a 1 to bit n of the BDAM Register enables the bitwise comparison of bit n in the BDA Register with bit n in the data reference address. Conversely, writing a 0 to bit n of the BDAM Register disables the comparison, and forces the breakpoint logic to assume a match between bit n in the BDA and bit n in the data reference address regardless of the true result. The BDAM Register contents are undefined after reset.

Table 6 shows the format of the BDAM Register.

#### Table 6 BDAM Register

#### 4.1.2 Instructions

The MFD and MTD instructions access the DBX registers. These instructions use the FlexLink interface of the TR4101 and are not supported by compilers or assemblers. The following macros may be used to enable the MFD and MTD instructions:

```

#define MFD(rt,dr).word0x7C000000 + (rt << 16) + (dr << 11)

#define MTD(rs,dr).word0x78000000 + (rs << 21) + (dr << 11)</pre>

```

**MFD Instruction** – The Move From Debug (MFD) Instruction loads the contents of DBX Register  $d\mathbf{r}$  into a General Register  $\mathbf{r}\mathbf{t}$ . This instruction is only valid if  $d\mathbf{r}=7$ , 18, 19, 20, or 21. All other  $d\mathbf{r}$  values are undefined. The values for each Debug Register  $d\mathbf{r}$  are indicated in parentheses in the subsection headings.

Operation: T: GPR[rt] <- DEBUG[dr]

Exceptions: None

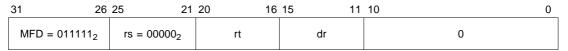

Table 7 shows the format of the MFD Instruction. The MFD Instruction is not available from MIPS16 code.

Table 7 MFD Instruction (MIPS II format)

**MTD Instruction** – The Move To Debug (MTD) Instruction loads the contents of General Register rs into a DBX Register dr. This instruction is only valid if dr = 7, 18, 19, 20, or 21. All other dr values are undefined.

Operation: T: DEBUG[dr] <- GPR[rs]

Exceptions: None

Table 8 shows the format of the MTD Instruction. The MTD Instruction is not available from MIPS16 code.

Table 8 MTD Instruction (MIPS II format)

| 31 26                     | 5 25 21 | 20 16                   | 15 11 | 10 | 0 |

|---------------------------|---------|-------------------------|-------|----|---|

| MTD = 011110 <sub>2</sub> | rs      | rt = 00000 <sub>2</sub> | dr    | 0  |   |

#### 4.1.3 Breakpoints

This section describes the operation of the DBX Building Block in more detail.

When a breakpoint occurs, the DBX sets the proper status bit. All status bits are sticky—they are not cleared by hardware, and can only be cleared by software.

Breakpoints are only detected if the TR4101 actually executes the breaking instruction, thus breakpoints can be placed freely in the code. For example, a breakpoint placed at an instruction following any MIPS16 branch will only be detected if the branch is not taken, as one would expect, from a programmer's point of view. The general rule is that breakpoints are only reported for instructions that complete their execute stage, or for instructions that would have completed the stage were it not for the Bus Error caused by the DBX.

In addition, breakpoints are reported in the order they occur in the code. A data breakpoint followed by an instruction breakpoint results in the

data breakpoint being reported first, even though the instruction fetch address following the data load/store transaction actually appears on the CBus first.

**Data Write Breakpoint** – A data write breakpoint occurs when the TR4101 writes data to an address that matches all the bits of the BDA Register not masked by the BDAM Register.

The DE, DW, and DAE bits of the DCS Register enable data write breakpoints. The BDA and BDAM registers must be properly loaded before the breakpoint is enabled. When the data write breakpoint occurs and the IBD and TR bits of the DCS Register are enabled, the TR4101 signals a DBus Error. The EPC Register then points to the offending write instruction unless the write instruction was executed in a delay slot. In this case, EPC points to the jump or branch instruction instead. The data write instruction and all previous instructions complete execution.

**Data Read Breakpoint** – A data read breakpoint occurs when the TR4101 reads data (not an instruction fetch) from an address that matches all of the bits of the BDA Register not masked by the BDAM Register.

The DE, DR, and DAE bits of the DCS Register enable data read breakpoints. The BDA and BDAM registers must be properly loaded before the breakpoint is enabled. When the data read breakpoint occurs and the IBD and TR bits of the DCS Register are enabled, the TR4101 signals a DBus Error. The EPC Register then points to the offending read instruction unless the read instruction was executed in a delay slot. In this case, EPC points to the jump or branch instruction instead. All previous instructions complete execution. The data read instruction is completed if the data is not contained in cache, and is not completed if the data is contained in cache.

**Program Counter Breakpoint** – A program counter breakpoint occurs when the TR4101 is about to execute an instruction whose address and mode matches all the bits of the BPC Register not masked by the BPCM Register.

The DE and PCE bits of the DCS Register enable this breakpoint. The BPC and BPCM registers must be properly loaded before the breakpoint is enabled. If the IBD and TR bits of the DCS Register are enabled, the DBX signals an IBus Error when the TR4101 is about to execute the offending instruction. This causes a trap to the exception handler. The EPC Register then points to the instruction unless the instruction was about to be executed in a delay slot. In this case, the EPC Register points to the jump or branch instruction instead. The offending instruction is killed, but all previous instructions complete execution.

A breakpoint placed off a word boundary in MIPS II mode or a breakpoint placed at the start of a 32-bit MIPS16 instruction will not be detected. If a break is to be generated on a 32-bit MIPS16 instruction (EXTEND or JAL/JALX), the breakpoint must be placed at the second halfword of the instruction.

Note that if the M-bit of BPCM is 1, then the M-bit of BPC must be 0 in order to detect breakpoints in MIPS II mode, and the M-bit of BPC must be 1 in order to detect breakpoints in MIPS16 mode. The M-bit of BPC and BPCM can be programmed to detect, for example, all MIPS16 instructions (BPC==BPCM==0x00000001).

**Breakpoint Placement** – When the internal trap mechanism is enabled, with TR and IBD both enabled in the DCS Register, special care needs to be taken when using program counter breakpoints and/or data breakpoints from inside the exception handler.

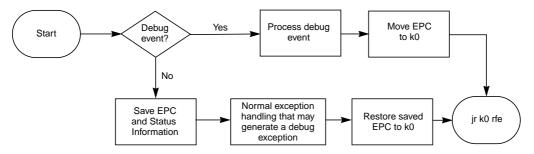

If there is a possibility of triggering a debug exception from within the exception handler, the user must ensure that the necessary machine state is saved before a debug exception might occur. This can be done by saving EPC (Exception Program Counter) contents and other important status information on entry, as shown in Figure 2. However, the user must see that no debug exception occurs in critical regions such as those that process debug events, save/restore EPC contents, and so forth.

Figure 2 Typical Exception Handler Flow

Note: jr k0 rfe are MIPS assembly language instructions typically used to return from an exception handler

#### 4.2 SerialICE Port Overview

The SerialICE port is a full-duplex, serial, receive and transmit port. It is used with the SerialICE concept for downloading application software to the TR4101 and for debugging the TR4101. The SerialICE port is designed to work with the ICEcontroller at baud rates up to 1 M baud, providing 800 kbits of data per second. Please refer to MIPS SerialICE Debugging Environment User's Guide for additional information on the SerialICE concept.

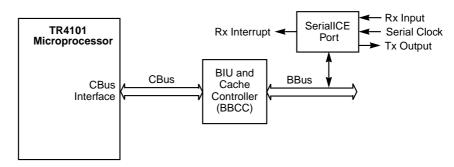

Figure 3 shows a block diagram of a TR4101 system using the SerialICE port, where the TR4101 interfaces to the SerialICE port through the BBCC using the CBus, and the BBCC interfaces to the SerialICE port using the BBus.

Figure 3 TR4101 System with SerialICE Port

The SerialICE port provides the following features:

- Full-duplex operation, fixed for 8 data bits, 1 stop bit, and no parity bit.

- Clock at 16 times the bit rate to define the receiving (Rx) and transmitting (Tx) rates. The clock is common for Rx and Tx, and may either be an external clock or be generated internally from the system clock.

- An Rx ready signal to indicate that one byte of data has been received and is in the one-byte input buffer.

- Separate status and data registers for Rx and Tx. The Rx Status Register contains one bit that indicates the received data is in the SerialICE port, and one bit that indicates an overrun in the Rx input buffer. The Tx Status Register contains one bit that indicates the SerialICE port is ready to transmit data.

- Interrupt possible when new data is received.

- Serial-receive and clock-input lines that require no active signal when the SerialICE port is unused.

#### 4.2.1 Registers

All SerialICE port registers are memory mapped, as shown in Table 9. The base address for the SerialICE port register block is in the uncached *kseg1*, and is set to 0xBFFF0200.

Table 9 SerialICE Port Register Addresses

| Address    | Access | Register                      |

|------------|--------|-------------------------------|

| 0xBFFF0200 | Read   | Receive (Rx) Status Register  |

| 0xBFFF0200 | Write  | Receive (Rx) Setup Register   |

| 0xBFFF0204 | Read   | Receive (Rx) Data Register    |

| 0xBFFF0208 | Read   | Transmit (Tx) Status Register |

| 0xBFFF020C | Write  | Transmit (Tx) Data Register   |

All register transactions are read transactions with 0 in bits [31:8], and data in bits [7:0]. The register bits are mapped with bit 31 to BDATAP[31], bit 30 to BDATAP[30], and so forth. Write transactions to read-only registers are ignored, and read transactions from write-only registers return undefined data.

All registers must be accessed using word accesses only, to avoid conflict between big endian and little endian data structures, and to avoid partial update problems.

**Receive (Rx) Status Register** – The Rx Status Register, shown in Table 10, provides status information for the Rx operation, and indicates the validity of the Rx Data Register. The register is a read-only register.

Table 10 Rx Status Register

| 31 | 2        | ! 1       | 0     |

|----|----------|-----------|-------|

|    | Reserved | RxOverrun | RxRDY |

Reserved Bits [31:2]

These bits are reserved. They are read as zeros.

#### RxOverrun Rx Overrun

This bit is set at a valid Stop bit when a new byte is received before the previously received byte has been read, as indicated by the RxRDY bit being set. The newly received byte is discarded, and the pending byte indicated by the RxRDY bit, is retained.

When the RxOverrun bit is set, it indicates that at least one byte in the serial input stream is lost. The bit is cleared when the Rx Status Register is read. This ensures that an overrun that occurs between a read of the Rx Status Register and a read of the Rx Data Register is indicated the next time the Rx Status Register is read. The RxOverrun bit is cleared at reset.

#### RxRDY Rx Byte Ready

This bit is set to 1 when a byte is received by the Rx block. It is cleared to 0 when the Rx Data Register is read, and at reset. When the bit is enabled by the RxIRXRDYPe bit in the Rx Setup Register, it is connected to Interrupt 2 in a logical OR with the external interrupt request on INT2.

**Receive (Rx) Setup Register** – The Rx Setup Register, shown in Table 11, enables or disables the use of the RxRDY bit in the Rx Status Register, for possible interrupt on Interrupt 2. The register is a write-only register.

1

0

Table 11 Rx Setup Register

| 31       | 1 | 0          |

|----------|---|------------|

| Reserved |   | RxIRXRDYPe |

Reserved Reserved Bits

[31:1]

These bits are reserved. Write transactions to these bits are ignored.

#### RxIRXRDYPe Rx IRXRDYP Enable

0

When this bit is set to 1, the RxRDY bit in the Rx Status Register is connected to Interrupt 2 in a logical OR with the external interrupt request on INT2. When the bit is cleared to 0, only the external INT2 drives the Interrupt 2 on the CPU. The bit is cleared at reset.

**Receive (Rx) Data Register** – The Rx Data Register, shown in Table 12, holds received data. The register is undefined after reset. The register is a read-only register.

Table 12 Rx Data Register

| 31       | 8 | 7      | 0 |

|----------|---|--------|---|

| Reserved |   | RxData |   |

Reserved Bits [31:8]

These bits are reserved. They are read as zeros.

RxData Received Bit Stream [7:0]

This field holds data received from the ICERXP serial input signal. Data is valid only when the RxRDY bit in the Rx Status Register is set. The register is undefined after reset.

**Transmit (Tx) Status Register** – The Tx Status register, shown in Table 13, provides status information for the Tx operation. The register is a read-only register.

#### Table 13 Tx Status Register

| 31       | 1 | 0     |

|----------|---|-------|

| Reserved |   | TxRDY |

Reserved Bits [31:1]

These bits are reserved. They are read as zeros.

TxRDY Tx Ready

This bit is set to 1 when the byte in the Tx Data Register has been transmitted and the Tx Data Register is ready for the next byte. The bit is cleared to 0 by a write to the Tx Data Register. The bit is set to 1 at reset.

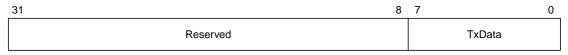

**Transmit (Tx) Data Register** – The Tx Data Register, shown in Table 14, holds transmission data. The register is a write-only register.

Table 14 Tx Data Register

Reserved Reserved Bits [31:8]

These bits are reserved. Write transactions to these bits

are ignored.

TxData Transmitted Bit Stream [7:0]

The Tx Data Register may be written with data to be transmitted on ICETXP, provided that the TxRDY bit in the Tx Status Register is set. A write to the register is ignored when the TxRDY bit is cleared.

#### 4.3 BBCC Overview

The EV4101 has a 16 Kbyte two-way set associative I-cache. Each I-cache set (8 Kbyte each) contains 512 four-word lines. The EV4101 also has a 8 Kbyte D-cache, which also consists of 512 four-word lines. Each line in the cache has a 19-bit tag and four valid bits. The D-cache is write-through. Each cache set can be individually enabled or disabled by setting the ICEN, IS1EN, and DCEN control bits of the System Configuration Register (SCR).

0

#### 4.4 System Configuration Register

An SCR exists at 0xBFFF.0000. All bits are reset to zero at power-up. All bits are readable and writable. Bit 13 (DBERR) is sticky, which means that once set, it can only be reset by software.

Table 15 **Configuration Register**

| 31  | 30    | 29     | 28     | 27 25 | 24    | 23 20 | 19 16   | 15 14 | 13    | 12 10 | 9 8   | 7     | 6 5    | 4    | 3 2    | 1     | 0    |

|-----|-------|--------|--------|-------|-------|-------|---------|-------|-------|-------|-------|-------|--------|------|--------|-------|------|

| RES | WRBUF | DSNPEN | ISNPEN | RES   | FASTP | RES   | INTCOND | RES   | DBERR | PGSZ  | CMODE | RDPRI | DRFLSZ | DCEN | IRFLSZ | IS1EN | ICEN |

31, [27:25], [23:20], [15:14] **RES** Reserved Bits These bits are reserved. For future compatibility, always

write zero to these bits.

**WRBUF** Write Buffer Depth Control 30

> When this bit is set to one, the write buffer is four deep. When this bit is zero, the write buffer is one deep.

**DSNPEN** 29 **Data Cache Snoop Enable**

> When this bit is set to one, Data Cache snooping is enabled when the EV4101 is not the bus master.

**ISNPEN** Instruction Cache Snoop Enable 28

> When this bit is set to one, Instruction Cache snooping is enabled when the EV4101 is not the bus master.

**FASTP Fast Transactions** 24

> PCI protocol requires a dead cycle on the AD bus between drivers of the AD bus. This cycle occurs after the driving of the address and the receiving of data, and again after the receiving of data on one transaction and the driving of the address for the next transaction. Setting this bit to one removes the extra cycle between transactions and between the address and data phases (the safety measure is bypassed).

#### INTCOND Interrupt/CPCOND Control

[19:16]

This field selects whether the INT[5:2] pins control the EV4101 condition bits or interrupts.

| INTCOND | Description                                                                    |

|---------|--------------------------------------------------------------------------------|

| Bit 19  | 0: INT5 Controls EV4101 Condition Bit 3<br>1: INT5 Controls EV4101 Interrupt 5 |

| Bit 18  | 0: INT4 Controls EV4101 Condition Bit 2<br>1: INT4 Controls EV4101 Interrupt 4 |

| Bit 17  | 0: INT3 Controls EV4101 Condition Bit 1<br>1: INT3 Controls EV4101 Interrupt 3 |

| Bit 16  | 0: INT2 Controls EV4101 Condition Bit 0 1: INT2 Controls EV4101 Interrupt 2    |

#### DBERR Data Bus Error

13

A one on this bit indicates that a data bus error occurred. The bit is set until the EV4101 clears it. This bit is connected to Interrupt 0 in a logical OR with the external interrupt request on INT0.

#### PGSZ[2:0] Page Size

[12:10]

This field determines the page size in words of write bursts.

| PGSZ[2:0] | Page Size (Words) |

|-----------|-------------------|

| 0b000     | 16                |

| 0b001     | 32                |

| 0b010     | 64                |

| 0b011     | 128               |

| 0b100     | 256               |

| 0b101     | 512               |

| 0b110     | 1024              |

| 0b111     | 2048              |

#### CMODE[1:0] Cache Mode

[9:8]

This field determines the cache mode.

| CMODE[1:0] | Cache Mode                        |

|------------|-----------------------------------|

| 0b00       | Normal                            |

| 0b01       | Software Test of I-Cache Data RAM |

| 0b10       | Software Test of I-Cache Tag RAM  |

| 0b11       | Software Test of D-Cache Tag RAM  |

#### RDPRI Read Priority

7

A one on this bit enables read priority.

#### DRFLSZ[1:0] Data Refill Size

[6:5]

This field determines the data refill size for cacheable data fetches only.

| DRFLSZ[1:0] | Data Refill Size(Words) |

|-------------|-------------------------|

| 0b00        | 1                       |

| 0b01        | 2                       |

| 0b10        | 4                       |

| 0b11        | 8                       |

#### DCEN D-Cache Enable

4

Setting this bit enables the D-cache.

#### IRFLSZ[1:0] Instruction Refill Size

[3:2]

This field determines the instruction refill size for cacheable instruction fetches only.

| IRFLSZ[1:0] | Instruction Refill Size (Words) |

|-------------|---------------------------------|

| 0b00        | 1                               |

| 0b01        | 2                               |

| 0b10        | 4                               |

| 0b11        | 8                               |

#### IS1EN I-Cache Set 1 Enable

1

When ICEN is set to one, a one on this bit enables I-cache Set 1.

#### ICEN I-Cache Set 0 Enable

0

A one on this bit enables I-cache Set 0.

#### 4.4.1 Locking of I-Cache Lines

The I-cache Set 0 Tag RAM contains a lock bit (in addition to the valid bits) to indicate that the line is locked. This bit can be written through Software Test mode. When the bit is set, the BBCC will not replace the line in Set 0 unless the address matches the tag in the tag RAM. By using this feature, desired lines of I-cache Set 0 can be written with important instructions and then locked. Or, the lines can be first locked and fetched by the EV4101 later when the instruction is accessed.

#### 4.4.2 Software Test Mode

Software Cache Test Mode allows the EV4101 to write and read to cache RAMs to which it would not normally have direct access: the I-cache Data RAMs and the I-cache and D-cache Tag RAMs. This mode is useful for initializing the cache RAMs on reset, or for locking code into the I-Cache Set 0.

When the SCR is written such that CMODE[1:0] indicates that the BBCC is in Software Cache Test Mode, the BBCC interprets loads and stores differently. All loads come from the appropriate cache RAM, unless the address is in the *kseg1* address space. All stores are written to the appropriate cache RAM if they are not in *kseg1*. When CMODE[1:0] indicates that the BBCC is in Software Cache Test Mode for the I-cache, the I-cache set is specified by IS1EN in the SCR.

During Software Cache Test Mode, the software test code should be in *kseg1*. The DCEN bit in the SCR must be on for Software Cache Test Mode.

Table 16 shows the settings of the System Configuration Register for the various Software Cache Test Modes.

Table 16 SCR Settings for Software Cache Test Mode

| Cache Mode<br>CMODE[1:0] | D-Cache<br>Enable<br>DCEN | I-Cache Set 1<br>Enable<br>IS1EN | Software Cache Test<br>Mode |

|--------------------------|---------------------------|----------------------------------|-----------------------------|

| 01                       | 1                         | 0                                | I-Cache Set 0 Data          |

| 01                       | 1                         | 1                                | I-Cache Set 1 Data          |

| 10                       | 1                         | 0                                | I-Cache Set 0 Tag           |

| 10                       | 1                         | 1                                | I-Cache Set 1 Tag           |

| 11                       | 1                         | _                                | D-Cache Tag                 |

ADDR[9:0] is used to index the RAMs. For the data RAMs, the lower two bits of the address are ignored. All loads and stores are interpreted as full word transactions. For the tag RAMs, the lower four bits are ignored. Loads and stores to the tag RAMs are line operations.

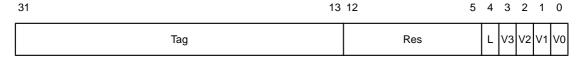

During stores to the data RAM of the I-cache, the data is on DATAP[31:0]. During stores to the tag RAM of the I-cache or D-cache, the tag originates from the upper bits of ADDR[31:2] (the tag normally used for the cache). The Lock bit originates from DATAP4, and the Valid bits originate from DATAP[3:0].

Fetches from the I-cache Data RAM are straightforward. The RAM places its 32 bits of data on DATAP[31:0]. Table 17 shows data returned from reading the tag RAM of an 8 Kbyte cache while in Software Cache Test Mode.

Table 17 Data Returned from Reading Tag Ram

The following is sample code to lock six instructions in the I-cache.

SETUP\_T0:

li t0, 0x000002fd # sw test to write tags to Set 0

```

lί

t1, 0xbfff0000 # address of Conf. Req.

SW

t0, 0(t1) # store to Conf. Req.

r0, 0(t1)

lw

# to flush Write Buffer

addi

r0, r0, 1

# force dependency on load

lί

t0, 0x80000000# tag

1i

t1, 0x1f

# lock, all words valid

li

t2, 0x13

# lock, two words valid

t1, 0x80(t0) # line 0

SW

t2, 0x90(t0) # line 1

SW

SETUP D0:

li.

t0, 0x000001fd# sw test to write data to Set 0

li

t1, 0xbfff0000# address of Conf. Reg.

t0, 0(t1) # store to Conf. Req.

SW

lw

r0, 0(t1)

# to flush Write Buffer

# force dependency on load

addi

r0, r0, 1

li

t0, 0x80000000# tag doesn't really matter

li.

t1, 0x3c0eb000# lui t6, 0xb000

li

t2, 0x8dcf0000# lw t7, 0(t6)

li.

t3, 0x21ef0001# addi t7, t7,1

t4, 0xadcf0000# sw t7, 0(t6)

lί

t5, 0x03e00008# jr ra

li

1i

t6, 0x00000000# nop

t1, 0x80(t0) # Instruction 0

SW

t2, 0x84(t0) # Instruction 1

SW

t3, 0x88(t0) # Instruction 2

SW

t4, 0x8c(t0) # Instruction 3

SW

SW

t5, 0x90(t0) # Instruction 4

t6, 0x94(t0) # Instruction 5

SW

```

#### 4.4.3 Block Refills

The BBCC can request a block refill if the fetch resides in cacheable space. If the address is cacheable then a block fetch is started by the BBCC starting with the desired word first. The IBLKSZ and DBLKSZ bits in the SCR selects block sizes of two, four, or eight. Instruction block size and data block size are controlled separately. When the end of the block is reached, the BBCC wraps around and requests the first word of the block until the entire block is refilled. The external memory system can terminate the block request at any time.

#### 4.4.4 Inpage Writes

The BBCC requests back-to-back write transactions if possible. The PGSZ field of the SCR determines the page size that is used in determining whether to prioritize the next write transaction. The EV4101 asserts a Write Burst Request if a pending write is in the same page. If the Write Burst Acknowledge is received by the EV4101, the next transaction will be the inpage write. The write transaction still appears as two separate transactions (as opposed to a burst write).

#### 4.4.5 Write Buffer

The EV4101 has a configurable depth write buffer. The WRBUF bit in the SCR configures the write buffer depth as one or four deep. If the Write Buffer depth is four, the TR4101 can execute up to four Store Word (SW) instructions and not be stalled. The SWs are held in the write buffer until the BBCC can service them.

#### 4.4.6 Read Priority

The BBCC can be configured to prioritize Load Word (LW) instructions over a SW that is already in the write buffer. If the RDPRI bit in the SCR is one, the BBCC services a LW before a SW, even if the microprocessor requested the SW earlier.

#### 4.4.7 Snooping

The BBCC can be configured to snoop when the EV4101 is not the master. Two control bits ISNPEN and DSNPEN control whether snooping is done by the BBCC. If ISNPEN is set, then the I-caches are snooped whenever the external master does a write transaction. Similarly, the SDNPEN controls data cache snooping. If the address of the write transaction matches the cache line, then the *entire* cache line is invalidated. The I-cache or D-cache snoop takes two cycles. Snooping both caches takes four cycles. The EV4101 asserts the Snoop Done output to indicate that the snoop is done and the transaction can continue.

#### 4.4.8 Bus Errors

The BBCC signals Instruction bus errors *synchronously* to the microprocessor so that the microprocessor will take an instruction bus

error exception. But, because of load scheduling and the write buffer, data bus errors are not signalled to the microprocessor as bus errors. Instead, a data bus error sets an interrupt bit in the SCR (bit 13) that is set until the microprocessor clears the bit. In the EV4101, this data bus error interrupt is tied to the microprocessor interrupt 0, Cause Register bit 10.

#### 4.5 Timer Overview

The EV4101's timer is attached internally to the BBCC's BBus. It contains two general purpose timers: Timer 0 and Timer 1. Each timer is a 16-bit down-counter with an initial count register and a current count register. A mode register defines the operation of both timers.

Both timers have a general-purpose mode where the timer counts down every cycle (internal system clock, not external bus clock). When the count reaches zero, a timer output (one for Timer 0 and one for Timer 1) will either toggle or pulse  $(H \rightarrow L \rightarrow H)$ .

When enabled through the Mode Register, the timer starts from the initial count register and counts down. Writing a zero to bit 0 or bit 8 of the Mode Register disables the respective timer and causes the timer to hold its current count value. If the counter is enabled again after it is disabled, the counter restarts from the initial count. It will not count down from the current count value.

Timer 0 has an additional sticky bit. In this mode, the timer asserts the active-LOW signal when it counts to zero. The interrupt signal can be deasserted through a microprocessor write to clear the sticky bit in the Interrupt Status Register.

Timer 1 has an additional Watchdog Mode feature. In this mode, the timer starts from the initial count value and starts counting down whenever the BBCC starts a bus cycle. If the counter reaches 0, Timer 1 signals a bus error to the BBCC and terminates the transaction. If the bus cycle ends before the timer reaches 0, the timer is disabled and holds the current count value. A new bus transaction causes the timer to restart from the initial count value.

After reset, both timers are disabled, both Initial Count registers are zero, and the timer outputs are HIGH.

All timer registers are 16 bits, and memory is mapped as shown in Table 18.

Table 18 Timer Registers

| Address     | Register                                 |

|-------------|------------------------------------------|

| 0xBFFF.0100 | Timer 0 Initial Count Register           |

| 0xBFFF.0104 | Timer 0 Current Count Register           |

| 0xBFFF.0108 | Timer 1 Initial Count Register           |

| 0xBFFF.010C | Timer 1 Current Count Register           |

| 0xBFFF.0110 | Mode Register                            |

| 0xBFFF.0114 | Interrupt Status Register (Timer 0 Only) |

Table 19 shows how the different bits in the Mode Register control the operation of the timers.

Table 19 Mode Register

| Bit              | Control        | Settings                                            |  |  |

|------------------|----------------|-----------------------------------------------------|--|--|

| 0                | Timer 0 Enable | 0 = Disable, 1 = Enable                             |  |  |

| 1                | Timer 0 Output | 0 = Toggle, 1 = Pulse                               |  |  |

| 8 Timer 1 Enable |                | 0 = Disable, 1 = Enable                             |  |  |

| 9 Timer 1 Output |                | 0 = Toggle, 1 = Pulse                               |  |  |

| 10 Timer 1 Mode  |                | 0 = General Purpose, 1 = Watchdog Mode <sup>1</sup> |  |  |

<sup>1.</sup> When Timer 1 is in the Watchdog Mode, the timeout output is a bus error pulse regardless of the output mode (bit 9).

Table 20 shows the bits in the Interrupt Status Register.

Table 20 Status Register

| Bit | Control           | Settings                                                                                                   |  |  |  |

|-----|-------------------|------------------------------------------------------------------------------------------------------------|--|--|--|

| 0   | Sticky Bit Enable | 0 = Sticky Bit Disabled, 1 = Sticky Bit Enabled                                                            |  |  |  |

| 1   | Sticky Bit        | Set to one when Timer 0 counts to zero; micro-<br>processor clears this bit from the exception<br>handler. |  |  |  |

## 5 Instruction Set Summary

Table 21 through Table 25 summarize the instruction sets for the TR4101 Microprocessor Core and the EV4101 Microprocessor Reference Device. This includes all MIPS I and MIPS II instructions; instructions are MIPS I unless otherwise marked. Table 26 lists all MIPS16 instructions.

Table 21 TR4101/EV4101 Instruction Set Summary (32-bits)

| Load/Store Instructions |                                        |       |                                        |  |  |  |

|-------------------------|----------------------------------------|-------|----------------------------------------|--|--|--|

| LB                      | Load Byte                              | LWR   | Load Word Right                        |  |  |  |

| LBU                     | Load Byte Unsigned                     | SB    | Store Byte                             |  |  |  |

| LH                      | Load Halfword                          | SH    | Store Halfword                         |  |  |  |

| LHU                     | Load Halfword Unsigned                 | SW    | Store Word                             |  |  |  |

| LW                      | Load Word                              | SWL   | Store Word Left                        |  |  |  |

| LWL                     | Load Word Left                         | SWR   | Store Word Right                       |  |  |  |

| Arithmetic              | Arithmetic Instructions: ALU Immediate |       |                                        |  |  |  |

| ADDI                    | Add Immediate                          | ORI   | OR Immediate                           |  |  |  |

| ADDIU                   | Add Immediate Unsigned                 | SLTI  | Set on Less Than Immediate             |  |  |  |

| ANDI                    | AND Immediate                          | SLTIU | Set on Less Than Immediate<br>Unsigned |  |  |  |

| LUI                     | Load Upper Immediate                   | XORI  | Exclusive OR Immediate                 |  |  |  |

| (Sheet 1 of 3)          |                                        |       |                                        |  |  |  |

Table 21 TR4101/EV4101 Instruction Set Summary (32-bits) (Cont.)

| Arithmetic           | Instructions: Three-Operand, Register-                  | Туре                 |                                             |

|----------------------|---------------------------------------------------------|----------------------|---------------------------------------------|

| ADD                  | Add                                                     | SLT                  | Set on Less Than                            |

| ADDU                 | Add Unsigned                                            | SLTU                 | Set on Less Than Unsigned                   |

| AND                  | Logical AND                                             | SUB                  | Subtract                                    |

| NOR                  | Logical NOR                                             | SUBU                 | Subtract Unsigned                           |

| OR                   | Logical OR                                              | XOR                  | Exclusive Logical OR                        |

| Jump and I           | Branch Instructions                                     |                      |                                             |

| BCzF                 | Branch on Coprocessor z False                           | BLTZAL               | Branch on Less Than Zero and Link           |

| BCzT                 | Branch on Coprocessor z True                            | BNE                  | Branch on Not Equal                         |

| BEQ                  | Branch on Equal                                         | J                    | Jump                                        |

| BGEZ                 | Branch on Greater Than or Equal to Zero                 | JAL                  | Jump and Link                               |

| BGEZAL               | Branch on Greater Than or Equal to Zero and Link        | JALR                 | Jump and Link Register                      |

| BGTZ                 | Branch on Greater Than Zero                             | JALX <sup>1</sup>    | Jump and Link Exchange                      |

| BLEZ                 | Branch on Less Than or Equal to Zero                    | JR                   | Jump Register                               |

| BLTZ                 | Branch on Less Than Zero                                |                      |                                             |

| Branch Like          | ely Instructions                                        |                      |                                             |

| BCzFL <sup>2</sup>   | Branch on Coprocessor z False Likely                    | BGTZL <sup>2</sup>   | Branch on Greater Than Zero Likely          |

| BCzTL <sup>2</sup>   | Branch on Coprocessor z True Likely                     | BLEZL <sup>2</sup>   | Branch on Less Than or Equal to Zero Likely |

| BEQL <sup>2</sup>    | Branch on Equal Likely                                  | BLTZALL <sup>2</sup> | Branch on Less Than Zero and Link Likely    |

| BGEZALL <sup>2</sup> | Branch on Greater Than or Equal to Zero and Link Likely | BLTZL <sup>2</sup>   | Branch on Less Than Zero Likely             |

| BGEZL <sup>2</sup>   | Branch on Greater Than or Equal to Zero Likely          | BNEL <sup>2</sup>    | Branch on Not Equal Likely                  |

| (Sheet 2 of          | 3)                                                      |                      |                                             |

Table 21 TR4101/EV4101 Instruction Set Summary (32-bits) (Cont.)

| Trap Instru                  | ctions                                           |                    |                                            |

|------------------------------|--------------------------------------------------|--------------------|--------------------------------------------|

| TEQ <sup>2</sup>             | Trap if Equal                                    | TLT <sup>2</sup>   | Trap if Less Than                          |

| TEQI <sup>2</sup>            | Trap if Equal Immediate                          | TLTI <sup>2</sup>  | Trap if Less Than Immediate                |

| TGE <sup>2</sup>             | Trap if Greater Than or Equal                    | TLTIU <sup>2</sup> | Trap if Less Than Immediate Unsigned       |

| TGEI <sup>2</sup>            | Trap if Greater Than or Equal Immediate          | TLTU <sup>2</sup>  | Trap if Less Than Unsigned                 |

| TGEIU <sup>2</sup>           | Trap if Greater Than or Equal Immediate Unsigned | TNE <sup>2</sup>   | Trap if Not Equal                          |

| TGEU <sup>2</sup>            | Trap if Greater Than or Equal Unsigned           | TNEI <sup>2</sup>  | Trap If Not Equal Immediate                |

| Coprocess                    | or Instructions                                  |                    |                                            |

| BCzF                         | Branch on Coprocessor z False                    | LWCz               | Load Word to Coprocessor z $(z \neq 0)$    |

| BCzT                         | Branch on Coprocessor z True                     | MTCz               | Move to Coprocessor z                      |

| COPz                         | Coprocessor Operation                            | MFCz               | Move from Coprocessor z                    |

| CTCz                         | Move Control to Coprocessor z                    | SWCz               | Store Word from Coprocessor z $(z \neq 0)$ |

| CFCz                         | Move Control from Coprocessor z                  |                    |                                            |

| Shift Instru                 | ictions                                          |                    |                                            |

| SLL                          | Shift Left Logical                               | SRAV               | Shift Right Arithmetic Variable            |

| SLLV                         | Shift Left Logical Variable                      | SRL                | Shift Right Logical                        |

| SRA                          | Shift Right Arithmetic                           | SRLV               | Shift Right Logical Variable               |

| Special Control Instructions |                                                  |                    |                                            |

| BREAK                        | Breakpoint                                       | SYSCALL            | System Call                                |

| (Sheet 3 of                  | 3)                                               |                    |                                            |

<sup>1.</sup> New 32-bit MIPS instruction.

<sup>2.</sup> MIPS II instructions.

# Table 22 TR4101/EV4101-Specific System Control Processor (CP0) Instructions (32-bits)

| MFC0 | Move from CP0 | RFE   | Restore from Exception |

|------|---------------|-------|------------------------|

| MTC0 | Move to CP0   | WAITI | Wait for Interrupt     |

#### Table 23 Multiply/Divide Instructions (with MDU)

| MULT               | Multiply                   | DIV  | Divide          |

|--------------------|----------------------------|------|-----------------|

| MULTU              | Multiply Unsigned          | DIVU | Divide Unsigned |

| MADD <sup>1</sup>  | Multiply Add               | MFHI | Move from HIGH  |

| MADDU <sup>1</sup> | Multiply Add Unsigned      | MFLO | Move from LOW   |

| MSUB <sup>1</sup>  | Multiply Subtract          | MTHI | Move to HIGH    |

| MSUBU <sup>1</sup> | Multiply Subtract Unsigned | MTLO | Move to LOW     |

<sup>1.</sup> New 32-bit MIPS instruction.

#### Table 24 DBX Instructions

| MFD <sup>1</sup> | Move from Debug | MTD <sup>1</sup> | Move to Debug |

|------------------|-----------------|------------------|---------------|

|------------------|-----------------|------------------|---------------|

<sup>1.</sup> New 32-bit MIPS instruction.

### Table 25 Unimplemented MIPS II Instructions

| COP1 | All floating point instructions | ERET | Exception Return                |

|------|---------------------------------|------|---------------------------------|

| LL   | Load Linked Word                | LDCz | Load Doubleword to Coprocessor  |

| SC   | Store Conditional Word          | SDCz | Store Doubleword to Coprocessor |

| SYNC | Synchronize Shared Memory       |      |                                 |

Table 26 TR4101/EV4101 Instruction Set Summary (MIPS16)

| Load/Stor      | Load/Store Instructions                                   |       |                                        |  |  |

|----------------|-----------------------------------------------------------|-------|----------------------------------------|--|--|

| LB             | Load Byte                                                 | LW    | Load Word                              |  |  |

| LBU            | Load Byte Unsigned                                        | SB    | Store Byte                             |  |  |

| LH             | Load Halfword                                             | SH    | Store Halfword                         |  |  |

| LHU            | Load Halfword Unsigned                                    | SW    | Store Word                             |  |  |

| Arithmetic     | Instructions: ALU Immediate                               | '     | '                                      |  |  |

| LI             | Load Immediate                                            | SLTIU | Set on Less Than Immediate<br>Unsigned |  |  |

| ADDIU          | Add Immediate Unsigned                                    | CMPI  | Compare Immediate                      |  |  |

| SLTI           | Set on Less Than Immediate                                |       |                                        |  |  |

| Arithmetic     | Arithmetic Instructions: Two/Three Operand, Register Type |       |                                        |  |  |

| ADDU           | Add Unsigned                                              | AND   | AND                                    |  |  |

| SUBU           | Subtract Unsigned                                         | OR    | OR                                     |  |  |

| SLT            | Set on Less Than                                          | XOR   | Exclusive OR                           |  |  |

| SLTU           | Set on Less Than Unsigned                                 | NOT   | NOT                                    |  |  |

| CMP            | Compare                                                   | MOVE  | Move                                   |  |  |

| NEG            | Negate                                                    |       |                                        |  |  |

| Multiply/D     | pivide Instructions (with optional                        | MDU)  |                                        |  |  |

| MULT           | Multiply                                                  | DIVU  | Divide Unsigned                        |  |  |

| MULTU          | Multiply Unsigned                                         | MFHI  | Move From HIGH                         |  |  |

| DIV            | Divide                                                    | MFLO  | Move From LOW                          |  |  |

| Jump and       | Jump and Branch Instructions                              |       |                                        |  |  |

| JAL            | Jump and Link                                             | BNEZ  | Branch on Not Equal to Zero            |  |  |

| JALX           | Jump and Link Exchange                                    | BTEQZ | Branch on T Equal to Zero              |  |  |

| JR             | Jump Register                                             | BTNEZ | Branch on T Not Equal to Zero          |  |  |

| JALR           | Jump and Link Register                                    | В     | Branch Unconditional                   |  |  |

| BEQZ           | Branch on Equal to Zero                                   |       | ·                                      |  |  |

| (Sheet 1 of 2) |                                                           |       |                                        |  |  |

Table 26 TR4101/EV4101 Instruction Set Summary (MIPS16) (Cont.)

| Shift Instructions           |                        |       |                                 |  |

|------------------------------|------------------------|-------|---------------------------------|--|

| SLL                          | Shift Left Logical     | SLLV  | Shift Left Logical Variable     |  |

| SRL                          | Shift Right Logical    | SRLV  | Shift Right Logical Variable    |  |

| SRA                          | Shift Right Arithmetic | SRAV  | Shift Right Arithmetic Variable |  |

| Special Control Instructions |                        |       |                                 |  |

| EXTEND                       | Extend                 | BREAK | Breakpoint                      |  |

| (Sheet 2 of 2)               |                        |       |                                 |  |

# 6 Signal Descriptions

This section describes the EV4101 interface. It contains the following subsections:

- Bus Interface Signals

- Miscellaneous Signals

Within each subsection, the signals are described in alphabetical order by mnemonic. Each signal definition contains the mnemonic and the full signal name. In the descriptions that follow, the verb assert means to drive TRUE or active. The verb deassert means to drive FALSE or inactive.

The direction of many of the bus pins depends on whether the EV4101 is bus master or there is an external bus master. Direction is marked as follows: im/xm = i/o, if the pin is input when the EV4101 is bus master (im = internal master) and output when there is an external bus master (xm = external master).

Similarly, the direction of the arbiter pins depends on whether the EV4101 is the bus arbiter or an external arbiter exists (see ARBMODE2P pin). Direction is marked as follows: ia/xa = i/o if the pin is input when the internal arbiter (ia) is used and output if an external arbiter (xa) is used.

## 6.1 Bus Interface Signals

### AD[31:0] Address/Data Bus

Bidirectional

AD is the multiplexed address/data for the bus transaction. This bus supplies the address during the first clock of a bus transaction, and provides the data thereafter.

### ASN Address Strobe

Output

ASN is active during the first clock cycle of every transaction. A LOW on ASN indicates a valid address is on AD[31:0].

### CBEN[3:0]

## Command/Byte Enables Bidirectional, im/xm=o/i

The Command/Byte enable signals carry command information on the first cycle of a bus transaction and carry byte enables during subsequent cycles. Valid commands that the EV4101 drives on CBEN are Memory Read (0b0110), Memory Write (0b0111), and Memory Line Read (0b1110). Valid byte enables during reads and writes are listed in the following table.

| CBEN[3:0] | Transfer Type |

|-----------|---------------|

| 0b0000    | Word          |

| 0b0001    | Tribyte       |

| 0b0011    | Halfword      |

| 0b0111    | Byte          |

| 0b1000    | Tribyte       |

| 0b1011    | Byte          |

| 0b1100    | Halfword      |

| 0b1101    | Byte          |

| 0b1110    | Byte          |

#### **DEVSELN**

#### **Device Select**

Bidirectional, im/xm=i/o

The PCI target asserts DEVSELN when it has acknowledged that it is the slave for a particular transaction. A bus error occurs if DEVSELN is not asserted within six clock cycles of the assertion of FRAMEN, resulting in an exception.

### FRAMEN Frame

## Bidirectional, im/xm=o/i

FRAMEN is asserted LOW for at least one clock cycle at the beginning of every read and write transaction. During bursts, the EV4101 extends assertion of FRAMEN, and deasserts FRAMEN during the final data transfer.

### **GNTN** Bus Grant

## Bidirectional, ia/xa=o/i

The ARBMODE2P input determines whether the EV4101 is in Arbitration Mode 1 or Arbitration Mode 2. GNTN is an output in Arbitration Mode 1, and an input in Arbitration Mode 2. In Mode 1, the EV4101 contains the bus arbiter, and asserts GNTN to indicate that an external master has control of the bus on the next transaction. (This operation follows the PCI hidden arbitration protocol, where the end of the current transaction is defined as the cycle when both FRAMEN and IRDYN are sampled deasserted.)

In Mode 2, the bus arbiter is external to the EV4101 and GNTN is an input. When the EV4101 samples the assertion of GNTN, it starts a transaction on the bus after the current transaction has been completed.

### **INPAGEN**

### Inpage Transaction

### Output

The EV4101 asserts INPAGEN when the address of the current transaction is in the same page as the address of the previous transaction. The EV4101 must be the consecutive master of both transactions. If an external master performs a transaction between the EV4101's first and second transactions, then INPAGEN is cleared during the second transaction. INPAGEN can be monitored to enable the designer to implement DRAM Row Address Strobe (RAS) parking.

#### **IRDYN**

### Initiator Data Ready

## Bidirectional, im/xm=o/i

During writes, when asserted LOW, IRDYN indicates to the target that data is valid. During reads, when asserted LOW, IRDYN indicates the EV4101 can receive data. Data is transferred when both IRDYN and TRDYN are valid.

#### REQN

### **Bus Request**

### Bidirectional, ia/xa=i/o

The ARBMODE2P input determines whether the EV4101 is in Arbitration Mode 1 or Arbitration Mode 2. REQN is an input in Arbitration Mode 1 and an output in Arbitration Mode 2. In Mode 1, the EV4101 contains the bus arbiter

and monitors REQN to determine if an external DMA device requires mastership of the bus. In Mode 2, the bus arbiter is external to the EV4101, and the EV4101 asserts REQN when it needs to perform a transaction.

## SDONEP Snoop Done

Output

The EV4101 asserts the Snoop Done signal when it has completed its snoop. When a DMA transaction is being performed on the bus, the target should monitor SDONEP, and not assert TRDYN until SDONEP is HIGH. SDONEP is generated asynchronously as the logical combination of FRAMEN and CBEN[0].

## STOPN Stop Bus Transaction

Input

This signal is used in conjunction with TRDYN and DEVSELN to inform the initiator to either abort the transaction, retry the transaction, or stop the transaction.

- The transaction is aborted when STOPN is asserted and TRDYN and DEVSELN are both deasserted, resulting in a bus error on the BBus.

- The transaction is retried when STOPN and DEVSELN are both asserted and TRDYN is deasserted. The EV4101 usually retries the same transaction after allowing other masters to acquire the bus, if requested, but it is not guaranteed to do so. The EV4101 has the option to prioritize its transactions internally, so the initial transaction that resulted in a retry may eventually be retried, but not necessarily in the following cycle. Because a retry can occur in the middle of a cache refill, the EV4101 will not perform the transaction again, unless the instruction/data is absolutely needed.

- The transaction is stopped when STOPN, TRDYN, and DEVSELN are deasserted. The target uses this mechanism to tell the master that it cannot perform a burst, or that it wants the current data transfer in the burst to be the final data transfer. If the EV4101 interfaces to a PCI target that supports bursts, then the target should issue a stop at the end of a burst line, since the EV4101 address wraps and the PCI target does not. STOPN remains asserted until FRAMEN is HIGH.

### TRDYN Target Data Ready Bidirectional, im/xm=i/o

When asserted LOW, TRDYN indicates to the initiator during writes that the target can receive data. During reads, a LOW on TRDYN indicates the target is driving valid data. Data is transferred when both IRDYN and TRDYN are asserted.

## 6.2 Miscellaneous Signals

### **ARBMODE2P Arbitration Mode**

Input

When ARBMODE2P is deasserted LOW, the EV4101 is in Arbitration Mode 1. In this mode, the bus arbiter is internal to the EV4101. When ARBMODE2P is asserted HIGH, the EV4101 is in Arbitration Mode 2, where the arbiter is external to the EV4101. This mode is used when the EV4101 is not the Central Processor, but is part of an add-on card within a host computer system.

### **BCLKP** Buffered Clock

Output

BCLKP is the buffered PURE\_CLKP output. BCLKP either operates at the full PURE\_CLKP frequency (HALFP tied LOW) or at the half PURE\_CLKP frequency (HALFP tied HIGH). AC timing information is referenced to this clock.

#### **BCLKRSTN BCLKP Reset**

Input

When BCLKRSTN is LOW, it synchronously resets BCLKP to LOW. When BCLKRSTN goes HIGH, the BCLKP starts clocking on the rising edge of PURE\_CLKP. This is used to start BCLKP on either rising edge number 1 or 2, when BCLKP is running half the frequency of PURE\_CLKP. This pin should be held HIGH during normal operation.

### **BIG ENDIANP**

## **Big/Little Endian Select**

Input