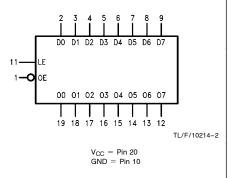

# DM74LS563 **Octal D-Type Latch with TRI-STATE® Outputs**

-v<sub>cc</sub>

— ōo

**—** Ō1

**-** 02

**-** ō3

**-** 05

**-** ō6

•LE 11

20

19

18

17

16 **-** 04

15

14

13 **-** 07

12

#### **General Description**

The 'LS563 is a high speed octal latch with buffered common Latch Enable (LE) and buffered common Output Enable (OE) inputs.

This device is functionally indentical to the 'LS573, but has inverted outputs.

Dual-In-Line Package

# **Features**

■ Inputs and Outputs on opposite sides of packages allowing easy interface with microprocessors

■ Useful as input or output port for microprocessors

- Input clamp diodes limit high speed termination effects

- Fully TTL and CMOS compatible

ŌĒ

D0 -2

D1·

D2

D3

D4

D5

D6

D7

GND 10

3

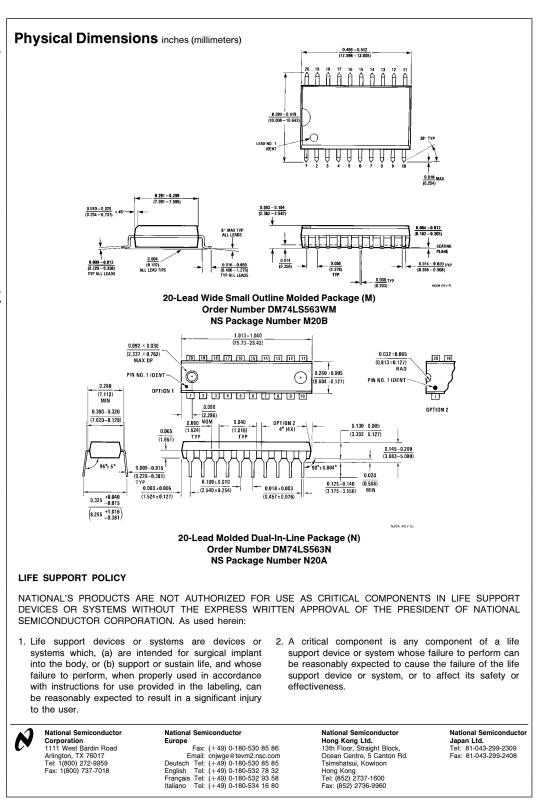

Order Number DM74LS563WM or DM74LS563N See NS Package Number M20B or N20A

| Pin<br>Names | Description                                |

|--------------|--------------------------------------------|

| D0-D7        | Data Inputs                                |

| LE           | Latch Enable Input (Active HIGH)           |

| ŌĒ           | TRI-STATE Output Enable Input (Active LOW) |

| 00-07        | TRI-STATE Latch Outputs                    |

TL/F/10214-1

#### **Function Table**

| Output<br>Enable | Latch<br>Enable | D | Output<br><del> </del> <del> O</del> |

|------------------|-----------------|---|--------------------------------------|

| L                | н               | Н | L                                    |

| L                | Н               | L | Н                                    |

| L                | L               | Х | $\overline{Q}_{O}$                   |

| Н                | Х               | Х | Z                                    |

L = Low State, H = High State, X = Don't Care,

Z = High Impedance State.

$\overline{Q}_{O}$  = Previous Condition of  $\overline{O}$ .

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

© 1995 National Semiconductor Corporation TL/F/10214

RRD-B30M105/Printed in U. S. A.

DM74LS563 Octal D-Type Latch with TRI-STATE Outputs

June 1992

#### Absolute Maximum Ratings (Note)

| Supply Voltage                       | 7V                                |

|--------------------------------------|-----------------------------------|

| Input Voltage                        | 7V                                |

| Operating Free Air Temperature Range |                                   |

| DM74LS                               | 0°C to +70°C                      |

| Storage Temperature Range            | $-65^{\circ}C$ to $+150^{\circ}C$ |

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol                                   | Parameter                          | DM74LS563 |     |      | Units |

|------------------------------------------|------------------------------------|-----------|-----|------|-------|

| Symbol                                   | Farameter                          | Min       | Nom | Max  |       |

| V <sub>CC</sub>                          | Supply Voltage                     | 4.75      | 5   | 5.25 | V     |

| VIH                                      | High Level Input Voltage           | 2         |     |      | v     |

| VIL                                      | Low Level Input Voltage            |           |     | 0.8  | v     |

| I <sub>OH</sub>                          | High Level Output Current          |           |     | -2.6 | mA    |

| I <sub>OL</sub>                          | Low Level Output Current           |           |     | 24   | mA    |

| T <sub>A</sub>                           | Free Air Operating Temperature     | 0         |     | 70   | °C    |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>Dn to LE | 0<br>0    |     |      | ns    |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>Dn to LE  | 10<br>10  |     |      | ns    |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | LE Pulse Width<br>HIGH or LOW      | 15<br>15  |     |      | ns    |

#### Electrical Characteristics over recommended operating free air temperature range (unless otherwise noted)

| Symbol           | Parameter                                                          | Conditions                                                                                                                          | Min | Typ<br>(Note 1) | Мах  | Units                    |

|------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|------|--------------------------|

| VI               | Input Clamp Voltage                                                | $V_{CC} = Min$ , $I_I = -18 \text{ mA}$                                                                                             |     |                 | -1.5 | V                        |

| V <sub>OH</sub>  | High Level Output Voltage                                          | $\label{eq:V_CC} \begin{split} V_{CC} &= \text{Min, I}_{OH} = \text{Max,} \\ V_{IL} &= \text{Max, V}_{IH} = \text{Min} \end{split}$ | 2.4 | 3.3             |      | V                        |

| V <sub>OL</sub>  | Low Level Output Voltage                                           | $\label{eq:V_CC} \begin{split} V_{CC} &= \text{Min, I}_{OL} = \text{Max,} \\ V_{IL} &= \text{Max, V}_{IH} = \text{Min} \end{split}$ |     | 0.35            | 0.5  | V                        |

|                  |                                                                    | $I_{OL} = 12 \text{ mA}, V_{CC} = Min$                                                                                              |     | 0.25            | 0.4  | ν<br>ν<br>μΑ<br>μΑ<br>μΑ |

| l <sub>l</sub>   | Input Current @ Max Input Voltage                                  | $V_{CC} = Max, V_I = 7V$                                                                                                            |     |                 | 0.1  | mA                       |

| I <sub>IH</sub>  | High Level Input Current                                           | $V_{CC} = Max, V_I = 2.7V$                                                                                                          |     |                 | 20   | μA                       |

| IIL              | Low Level Input Current                                            | $V_{CC} = Max, V_I = 0.4V$                                                                                                          |     |                 | -0.4 | mA                       |

| I <sub>OZH</sub> | Off-State Output Current with High<br>Level Output Voltage Applied | $V_{CC} = Max, V_O = 2.4V$<br>$V_{IH} = Min, V_{IL} = Max$                                                                          |     |                 | 20   | μΑ                       |

| I <sub>OZL</sub> | Off-State Output Current with Low<br>Level Output Voltage Applied  | $\label{eq:VCC} \begin{split} V_{CC} &= Max, V_O = 0.4V \\ V_{IH} &= Min, V_{IL} = Max \end{split}$                                 |     |                 | -20  | μΑ                       |

| I <sub>OS</sub>  | Short Circuit Output Current                                       | V <sub>CC</sub> = Max<br>(Note 2)                                                                                                   | -30 |                 | -130 | mA                       |

| ICC              | Supply Current                                                     | V <sub>CC</sub> = Max (Note 3)                                                                                                      |     |                 | 40   | mA                       |

Note 1: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 2: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 3:  $I_{CC}$  is measured with the DATA inputs grounded and the OUTPUT CONTROLS at 4.5V.

| Symbol                                                   | Parameter                     | R <sub>L</sub> =<br>C <sub>L</sub> = | – Units        |    |

|----------------------------------------------------------|-------------------------------|--------------------------------------|----------------|----|

|                                                          |                               | Min                                  | Max            |    |

| t <sub>PLH</sub><br>t <sub>PHL</sub>                     | Propagation Delay<br>Dn to On |                                      | 23<br>25       | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub>                     | Propagation Delay<br>LE to On |                                      | 35<br>35       | ns |

| t <sub>PZH</sub><br>t <sub>PZL</sub>                     | Output Enable Time            |                                      | 28<br>36       | ns |

| t <sub>PZL</sub><br>t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output Disable Time           |                                      | 36<br>20<br>25 |    |

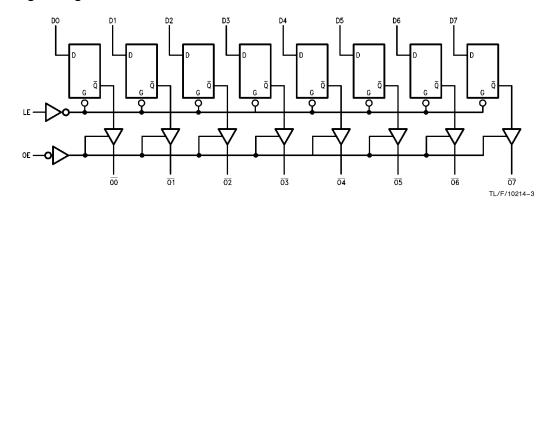

### **Functional Description**

The 'LS563 contains eight D-type latches with TRI-STATE output buffers. When the Latch Enable (LE) input is HIGH, data on the Dn inputs enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each time its D input changes. When LE is LOW the latches store the information that was present on the D in-

puts a setup time preceding the HIGH-to-LOW transition of LE. The TRI-STATE buffers are controlled by the Output Enable ( $\overline{OE}$ ) input. When  $\overline{OE}$  is LOW, the buffers are in the bi-state mode. When  $\overline{OE}$  is HIGH the buffers are in the high impedance mode but this does not interfere with entering new data into the latches.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications