# 4 Megabit CMOS EEPROM

DPE128X32V

# DENSE-PAC

#### **DESCRIPTION:**

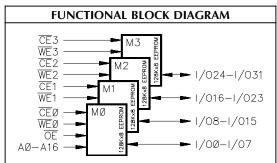

The DPE128X32V is a high-performance Electrically Erasable and Programmable Read Only Memory (EEPROM) module and may be organized as 128K X 32, 256K X 16 or 512K X 8.

The module is built with four low-power CMOS 128K X 8 EEPROMs. The four chip enables are used for individual BWDW\* selection. The DPE128X32V is ideally suited for those computer systems having 16-bit or 32-bit architectures.

The DPE128X32V contains a 128-BWDW page register to allow writing of up to 128 BWDWs simultaneously. During a write cycle, the address and 1 to 128 BWDWs of data are internally latched, freeing the address and data bus for other operations. Following the initiation of a write cycle, the module will automatically write the latched data using an internal control timer. The end of a write cycle can be detected by DATA Polling of the most significant data bit in each byte. Once the end of a write cycle has been detected, a new access for a read or write can begin.

#### **FEATURES:**

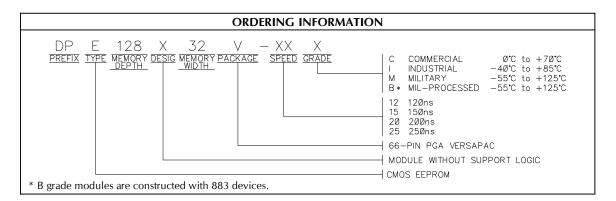

- Fast Access Times: 120, 150, 200, 250ns

- · Organizations Available:

- 128K X 32, 256K X 16 or 512K X 8

- Automatic Page Write Operation Internal Address and Data Latches Internal Control Timer

- Fast Write Cycle Times

- Page Write Cycle Time: 10ms maximum 1 to 128 BWDW\* Page Write Operation

- DATA Polling for END of Write Detection

- High Reliability CMOS Technology Endurance: 10<sup>4</sup> Cycles Data Retention: 10 years

- Single +5V Power Supply, ±10% Tolerance

- CMOS and TTL Compatible Inputs and Outputs

- Available with All Semiconductor Components used to Construct the Module Compliant to MIL-STD-883; Class B

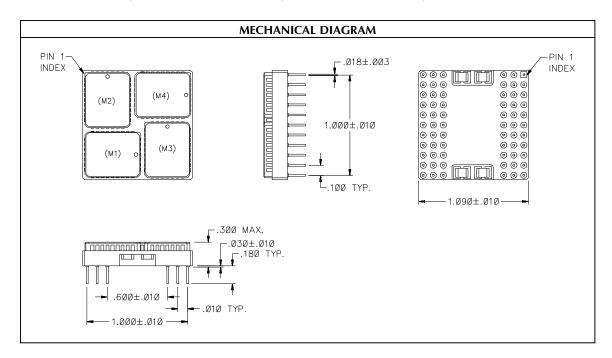

- 66-Pin PGA (Grid Array) Package

- Same Package as other Versapac Versions (SRAMs, EPROMs, and Mixed)

- \* Byte, Word or Double Word (BWDW).

| PIN NAMES                 |                |  |  |  |

|---------------------------|----------------|--|--|--|

| A0 - A16                  | Address Inputs |  |  |  |

| I/O0 - I/O31              | Data In/Out    |  |  |  |

| <u>CE</u> 0 - <u>CE</u> 3 | Chip Enables   |  |  |  |

| WE0 - WE3                 | Write Enables  |  |  |  |

| ŌĒ                        | Output Enable  |  |  |  |

| V <sub>DD</sub>           | Power (+5V)    |  |  |  |

| V <sub>SS</sub>           | Ground         |  |  |  |

| N.C.                      | No Connect     |  |  |  |

| PIN-OUT DIAGRAM                                                 |                                                                                                                                                                                                                                                                 |        |    |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----|

| 3 I/O1Ø<br>4 A13<br>5 A14<br>6 A15<br>7 A16<br>8 N.C.<br>9 I/OØ | 12   WE1   23   1/015   13   CE1   24   1/014   14   VSS   25   1/013   15   1/011   26   1/012   16   A10   27   OE   17   A11   28   N.C.   18   A12   29   WE0   19   VDD   30   1/07   20   CE0   31   1/06   21   N.C.   32   1/05   22   1/03   33   1/04 | 11 ⊕ ⊕ | 45 |

# **DPE128X32V**

## Dense-Pac Microsystems, Inc.

X = Don't Care

| RECOMMENDED OPERATING RANGE <sup>1</sup> |                          |      |      |      |      |    |

|------------------------------------------|--------------------------|------|------|------|------|----|

| Symbol                                   | Characteris              | Min. | Тур. | Max. | Unit |    |

| V <sub>DD</sub>                          | Supply Voltage           |      | 4.5  | 5.0  | 5.5  | V  |

| V <sub>IH</sub>                          | Input HIGH Voltage       |      | 2.0  |      |      | V  |

| VIL                                      | Input LOW Voltage        |      |      |      | 0.8  | V  |

|                                          |                          | С    | 0    | +25  | +70  |    |

| T <sub>A</sub>                           | Operating<br>Temperature | 1    | -40  | +25  | +85  | °C |

|                                          | remperature              | M/B  | -55  | +25  | +125 |    |

| TRUTH TABLE   |   |   |   |                 |  |

|---------------|---|---|---|-----------------|--|

| Mode          |   |   |   |                 |  |

| Standby       | Н | X | X | HIGH-Z          |  |

| Read          | L | L | Н | Dout            |  |

| Write         | L | Н | L | D <sub>IN</sub> |  |

| Write Inhibit | X | L | X | HIGH-Z          |  |

| Write Inhibit | X | X | Н | HIGH-Z          |  |

H = HIGH

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup> |                                   |               |      |  |  |

|---------------------------------------|-----------------------------------|---------------|------|--|--|

| Symbol                                | Parameter                         | Value         | Unit |  |  |

| TstG                                  | Storage Temperature               | -65 to +150   | °C   |  |  |

| T <sub>BIAS</sub>                     | Temperature Under Bias            | -65 to +135   | °C   |  |  |

| $V_{DD}$                              | Supply Voltage <sup>2</sup>       | -0.6 to +6.25 | °C   |  |  |

| V <sub>I/O</sub>                      | Input/Output Voltage <sup>2</sup> | -0.6 to +6.25 | V    |  |  |

| CAPACITANCE 3: $T_A = 25^{\circ}C$ , $F = 1.0MH$ |                   |      |      |               |

|--------------------------------------------------|-------------------|------|------|---------------|

| Symbol                                           | Parameter         | Max. | Unit | Condition     |

| CCE                                              | Chip Enable       | 30   |      |               |

| C <sub>ADR</sub>                                 | Address Input     | 70   |      |               |

| CWE                                              | Write Enable      | 70   | рF   | $V_{IN} = 0V$ |

| COE                                              | Output Enable     | 70   |      |               |

| C <sub>I/O</sub>                                 | Data Input/Output | 30   |      |               |

| AC TEST CONDITI                             | ONS        |

|---------------------------------------------|------------|

| Input Pulse Levels                          | 0V to 3.0V |

| Input Pulse Rise and Fall Times             | 5ns*       |

| Input and Output<br>Timing Reference Levels | 1.5V       |

<sup>\*</sup> Transition between 0.8V and 2.2V.

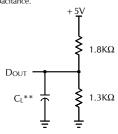

| OUTPUT LOAD |       |                        |  |

|-------------|-------|------------------------|--|

| Load        | $C_L$ | Parameters Measured    |  |

| 1           | 100pF | except t <sub>DF</sub> |  |

| 2           | 5pF   | t <sub>DF</sub>        |  |

# Figure 1. Output Load \*\* Including Probe and Jig Capacitance.

L = LOW

|                  | DC OPERATING CHARACTERISTICS: Over operating ranges |                                                                      |      |      |      |      |      |      |      |

|------------------|-----------------------------------------------------|----------------------------------------------------------------------|------|------|------|------|------|------|------|

| Symbol           | Characteristics                                     | Test Conditions                                                      | X32  |      | X16  |      | X8   |      | Unit |

| Symbol           | Characteristics                                     | rest Conditions                                                      | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| I <sub>IN</sub>  | Input<br>Leakage Current                            | $V_{IN} = V_{DD} Max.$                                               | -40  | +40  | -40  | +40  | -40  | +40  | μΑ   |

| lout             | Output<br>Leakage Current                           | $V_{OUT} = V_{DD} Max.$                                              | -10  | +10  | -20  | +20  | -40  | +40  | μΑ   |

| Icc              | Operating Supply<br>Current                         | $\overline{CE} = \overline{OE} = V_{IL},$<br>all I/O = 0mA, f = 5MHz |      | 320  |      | 170  |      | 90   | mA   |

| I <sub>SB1</sub> | V <sub>DD</sub> Standby<br>Current (TTL)            | CE = V <sub>IH</sub>                                                 |      | 12   |      | 12   |      | 12   | mA   |

| I <sub>SB2</sub> | V <sub>DD</sub> Standby<br>Current (CMOS)           | $\overline{CE} = V_{DD} - 0.3 Vdc$                                   |      | 1.2  |      | 1.2  |      | 1.2  | mA   |

| VIL              | Input Voltage Low                                   |                                                                      |      | 0.8  |      | 0.8  |      | 0.8  | V    |

| VIH              | Input Voltacge High                                 |                                                                      | 2.0  |      | 2.0  |      | 2.0  |      | V    |

| $V_{OL}$         | Output Voltage Low                                  | $I_{OUT} = 2.1 \text{mA}$                                            |      | 0.45 |      | 0.45 |      | 0.45 | V    |

| Vон              | Output Voltage High                                 | $I_{OUT} = -400\mu A$                                                | 2.4  |      | 2.4  |      | 2.4  |      | V    |

|     | AC OPERATING CONDITIONS AND CHARACTERISTICS - READ CYCLE: Over operating ranges |                                                                                 |       |      |       |      |       |      |       |      |      |

|-----|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|------|-------|------|-------|------|-------|------|------|

| No. | Symbol                                                                          | Parameter 1                                                                     | 120ns |      | 150ns |      | 200ns |      | 250ns |      | Unit |

| NO. | No. Symbol                                                                      |                                                                                 | Min.  | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max. | UIII |

| 1   | trc                                                                             | Read Cycle Time                                                                 | 120   |      | 150   |      | 200   |      | 250   |      | ns   |

| 2   | tCE                                                                             | Chip Enable to Output Valid                                                     |       | 120  |       | 150  |       | 200  |       | 250  | ns   |

| 3   | tacc                                                                            | Address Access Time                                                             |       | 120  |       | 150  |       | 200  |       | 250  | ns   |

| 4   | toe                                                                             | Output Enable Access Time                                                       |       | 50   |       | 55   |       | 55   |       | 55   | ns   |

| 5   | t <sub>DF</sub>                                                                 | Chip Enable or Output Enable to Output Float <sup>3</sup>                       |       | 50   |       | 55   |       | 55   |       | 55   | ns   |

| 6   | tон                                                                             | Output Hold from Chip Enable, Output Enable, or Address, Whichever Occurs First | 0     |      | 0     |      | 0     |      | 0     |      | ns   |

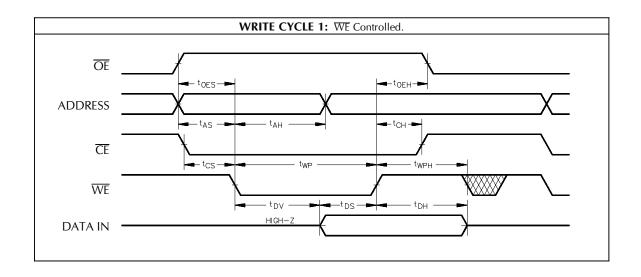

| Α   | AC OPERATING CONDITIONS AND CHARACTERISTICS - WRITE CYCLE: Over operating ranges 5, 6 |                              |      |      |      |  |

|-----|---------------------------------------------------------------------------------------|------------------------------|------|------|------|--|

| No. | Symbol                                                                                | Parameter                    | Min. | Max. | Unit |  |

| 7   | twc                                                                                   | Write Cycle Time             |      | 10   | ms   |  |

| 8   | tas                                                                                   | Address Set-up Time *        | 0    |      | ns   |  |

| 9   | t <sub>AH</sub>                                                                       | Address Hold Time            | 50   |      | ns   |  |

| 10  | tcs                                                                                   | Chip Select Set-up Time      | 0    |      | ns   |  |

| 11  | tcH                                                                                   | Chip Select Hold Time        | 0    |      | ns   |  |

| 12  | twp                                                                                   | Write Pulse Width (WE or CE) | 100  |      | ns   |  |

| 13  | t <sub>DS</sub>                                                                       | Data Set-up Time             | 50   |      | ns   |  |

| 14  | t <sub>DH</sub>                                                                       | Data Hold Time               | 0    |      | ns   |  |

| 15  | toes                                                                                  | Output Enable Set-up Time    | 0    |      | ns   |  |

| 16  | toeh                                                                                  | Output Enable Hold Time      | 0    |      | ns   |  |

| 17  | twph                                                                                  | Write Pulse Width High       | 50   |      | ns   |  |

| 18  | t <sub>BLC</sub>                                                                      | Byte Load Cycle Time         |      | 150  | μs   |  |

| 19  | twr                                                                                   | Write Recovery Time          | 0    |      | ns   |  |

<sup>\*</sup> Valid for both Read and Write Cycles.

| READ CYCLE |  |  |  |

|------------|--|--|--|

| ADDRESS    |  |  |  |

| CE         |  |  |  |

| ŌĒ         |  |  |  |

| DATA I/O   |  |  |  |

### **DEVICE OPERATION**

READ: The DPE12832V is accessed like a Static RAM. When  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  are low and WE is high, the data stored at the memory location determined by the address pins is asserted on the <u>outputs. The</u> outputs are put in the high impedance state whenever  $\overline{\text{CE}}$  or  $\overline{\text{OE}}$  is high. This dual line control gives designers flexibility in preventing bus contention.

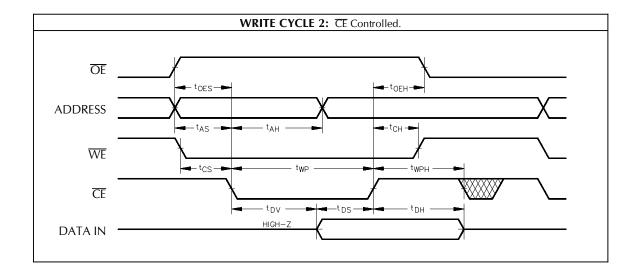

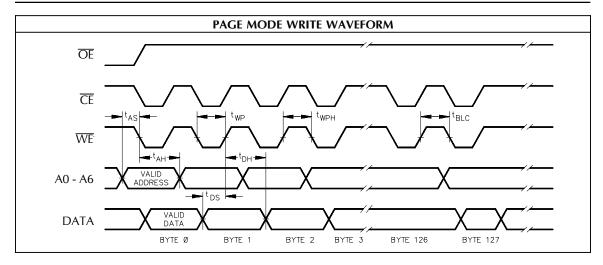

WRITE: A low pulse on the  $\overline{WE}$  or  $\overline{CE}$  input with  $\overline{CE}$  or  $\overline{WE}$  low (respectively) and  $\overline{OE}$  high initiates a write cycle. The address is latched on the falling edge of  $\overline{CE}$  or  $\overline{WE}$ . Once a \*\*BWDW Write has been started it will automatically time itself to completion. PAGE WRITE: The page write operation of the DPE12832V allows 1 to 128 BWDWs of data to be loaded into the device and then simultaneously written during the internal programming period. After the first data BWDW has been loaded into the device, successive BWDWs may be loaded in the same manner. Each new BWDW to written must have its high to low transition on  $\overline{WE}$  (or  $\overline{CE}$ ) within 150 $\mu$ s of the low to high transition is not detected within 150 $\mu$ s of the last low to high transition, the load period will end

and the internal programming period will start. A7 to A16 specify the page address. The page address must be valid during each high to low transition of WE (or CE). A0 to A6 are used to specify which BWDW within the page are to be written. The BWDWs may loaded in any order and may be changed within the same load period. Only BWDWs which are specified for writing will be written; unnecessary cycling of other BWDWs within the page does not occur.

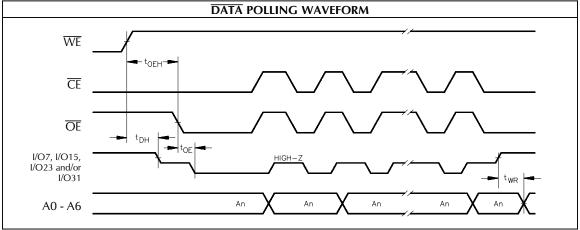

DATA POLLING: Write cycles typically are completed in less time than the maximum write cycle time of 10ms. To determine when the write is completed, a method called DATA Polling is utilized. If a read is performed on the address of the last BWDW written to the DPE12832V while a write cycle is in progress, the one's compliment of data most significant bit (I/O7, I/O15, I/O23 and I/O31) will appear on the output. When the write is completed, a read from the last address written will return valid data. A DATA Polling may begin at any time during the Write Cycle.

30A014-25 REV. D

<sup>\*\*</sup> Byte, Word, or Double Word.

### NOTES:

6

- 1. All voltages are with respect to V<sub>SS</sub>.

- 2. Stresses greater than those under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

- 3. This parameter is guaranteed and not 100% tested.

- 4. Address hold time is with respect to the falling edge of the control signal WE or CE.

- 5. WE and CE are noise protected. Less than a 15ns write pulse will not activate a write cycle.

Dense-Pac Microsystems, Inc.

7321 Lincoln Way ◆ Garden Grove, California 92841-1428

(714) 898-0007 ◆ (800) 642-4477 (Outside CA) ◆ FAX: (714) 897-1772 ◆ http://www.dense-pac.com

30A014-25 REV. D