# DNC3X3625 Hex 10/100 Mbits/s Ethernet Transceiver Macrocell

#### **Features**

#### Hex 10 Mbits/s Transceiver

- DSP based.

- Compatible with *IEEE* \* 802.3 10Base-T standard for twisted-pair cable.

- Half- and full-duplex operations.

- Autopolarity detection and correction.

- Adjustable squelch level for extended wire-length capability (two levels).

- Interfaces with *IEEE* 802.3u media independent interface (MII) or a serial 10 Mbits/s 7-pin interface.

- On-chip filtering eliminates the need for external filters.

#### Hex 100 Mbits/s Transceiver

- Compatible with IEEE 802.3u MII (clause 22), PCS/PMA (clause 24), PMD (clause 25), MII management, and autonegotiation (clause 28) specifications.

- Selectable 5-bit code-group (PDT/PDR interface) or 4-bit data nibbles (MII interface) input/output.

- Full- or half-duplex operations.

- Optional carrier integrity monitor (CIM).

- Selectable carrier sense signal generation (MCRS) asserted during either transmission or reception in half duplex (MCRS asserted during reception only in full duplex).

- Adaptive equalization and baseline wander correction.

- On-chip filtering eliminates the need for external filters.

- \* IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

#### Hex 100 Mbits/s FX Transceiver

- Compatible with IEEE 802.3u 100Base-FX standard.

- Reuses existing twisted-pair I/O pins for compatible fiber-optic transceiver pseudo-ECL (PECL) data.

- Fiber mode automatically configures port:

- FX mode enable is pin or register selectable

- Disables autonegotiation and 10Base-T.

- Enables 100Base-FX remote fault signaling.

- Disables MLT-3 encoder/decoder.

- Disables scrambler/descrambler.

#### General

- Ports individually configurable

- Autonegotiation and management:

- Fast link pulse (FLP) burst generator.

- Arbitration function.

- Accepts preamble suppression.

- Operates up to 12.5 MHz.

- Supports the MII station management protocol and frame format (clause 22): basic and extended register set.

- Supports next page.

- Provides status signals: receive activity, transmit activity, full duplex, collision/jabber, link integrity, and speed indication.

- Powerdown mode for 10 Mbits/s and 100 Mbits/s operation.

- Loopback testing for 10 Mbits/s and 100 Mbits/s operation.

- 0.25 µm low-power CMOS technology.

- Single 3.3 V power supply operation.

- 25 MHz XTAL oscillator input or 25 MHz/50 MHz/ 125 MHz clock input.

- Compatible with RMII (standard version) and SMII (standard version).

### **Table of Contents**

| Contents                                                                                      | Page |

|-----------------------------------------------------------------------------------------------|------|

| Features                                                                                      | 1    |

| Hex 10 Mbits/s Transceiver                                                                    |      |

| Hex 100 Mbits/s Transceiver                                                                   | 1    |

| Hex 100 Mbits/s FX Transceiver                                                                | 1    |

| General                                                                                       | 1    |

| Description                                                                                   |      |

| Functional Block Diagram                                                                      | 4    |

| Macrocell I/Os                                                                                |      |

| Signal Information                                                                            |      |

| Signal Descriptions                                                                           |      |

| MII Station Management                                                                        |      |

| Basic Operation                                                                               |      |

| MII Interface Design                                                                          |      |

| Absolute Maximum Ratings                                                                      |      |

| Electrical Characteristics                                                                    |      |

| Register Information                                                                          |      |

| Register Descriptions                                                                         |      |

| Application Notes: Board Layout                                                               |      |

| Tables                                                                                        | Page |

| Table 4. MII/E Dit Carial Interfess Cinnals                                                   |      |

| Table 1. MII/5-Bit Serial Interface Signals                                                   |      |

| Table 2. MII Management Signals                                                               |      |

| Table 4. Status Signals                                                                       |      |

| Table 5. Clock and Reset Signals                                                              |      |

| Table 6. Control/Status Signals                                                               |      |

| Table 7. Testability Signals                                                                  |      |

| Table 8. MII Management Frame Format                                                          |      |

| Table 9. MII Management Frames—Field Description                                              |      |

| Table 10 . Absolute Maximum Ratings                                                           |      |

| Table 11 . Operating Conditions                                                               |      |

| Table 12. Summary of Management Registers (MR)                                                | 19   |

| Table 13. MR0—Control Register Bit Descriptions                                               | 20   |

| Table 14. MR1—Status Register Bit Descriptions                                                | 21   |

| Table 15. MR2, MR3—PHY Identification Registers (1 and 2) Bit Descriptions                    | 22   |

| Table 16. MR4—Autonegotiation Advertisement Register Bit Descriptions                         | 22   |

| Table 17. MR5—Autonegotiation Link Partner Ability (Base Page) Register Bit Descriptions      | 23   |

| Table 18. MR5—Autonegotiation Link Partner (LP) Ability Register (Next Page) Bit Descriptions |      |

| Table 19. MR6—Autonegotiation Expansion Register Bit Descriptions                             |      |

| Table 20. MR7—Next Page Transmit Register Bit Descriptions                                    |      |

| Table 21. MR16—PCS Control Register Bit Descriptions                                          |      |

| Table 22. MR17—Autonegotiation Read Register A                                                |      |

| Table 23. MR18—Autonegotiation Read Register B                                                |      |

| Table 24. MR20—User-Defined Register                                                          | 27   |

# Table of Contents (continued)

| Tables (continued)                                                               | Page |

|----------------------------------------------------------------------------------|------|

| Table 26. MR28—Device-Specific Register 1 (Status Register) Bit Descriptions     | 27   |

| Table 27. MR29—Device-Specific Register 2 (100 Mbits/s Control) Bit Descriptions | 28   |

| Table 28. MR30—Device-Specific Register 3 (10 Mbits/s Control) Bit Descriptions  | 29   |

| Table 29. MR31—Device-Specific Register 4 (Quick Status) Bit Descriptions        |      |

| Figures                                                                          | Page |

| Figure 1. DNC3X3625 Functional Block Diagram                                     |      |

| Figure 2. I/Os of the DNC3X3625 Macrocell                                        | 5    |

| Figure 3. DNC MII TX Logic                                                       | 15   |

| Figure 4. DNC MII RX Logic                                                       | 15   |

| Figure 5. DNC Maintenance Logic                                                  | 15   |

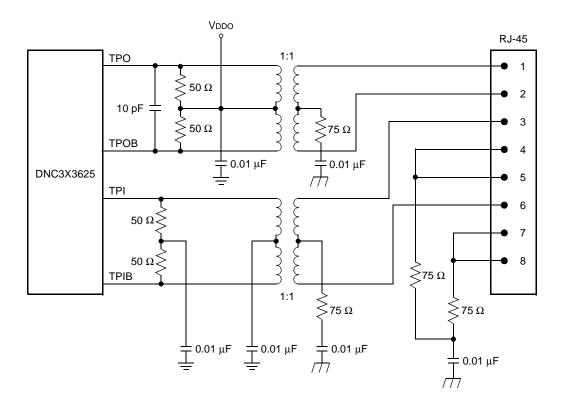

| Figure 6. Typical Application (One Channel Shown)                                | 16   |

| Figure 7. Pinout Assignment                                                      | 17   |

| Figure 8. Typical Single-Channel Twisted-Pair (TP) Interface                     | 18   |

#### **Description**

The DNC3X3625 is a twisted-pair transceiver macrocell that supports transmission and reception over category 3 unshielded twisted-pair (UTP) cable and category 5 UTP.

The DNC3X3625 has been designed specifically for applications that support both 10Base-T and 100Base-X, such as network interface cards (NICs), switches.

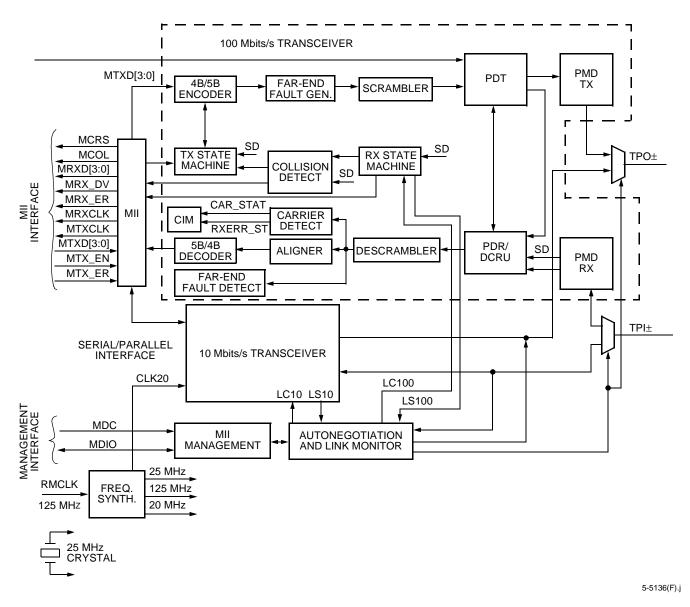

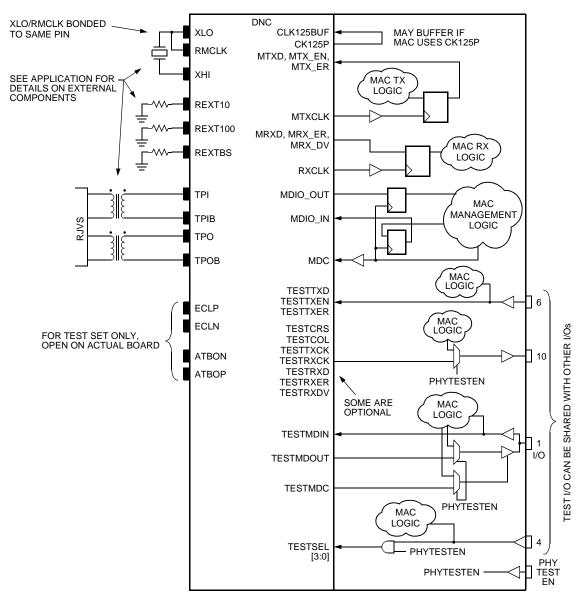

Figure 1 represents a functional block diagram of the DNC3X3625 macrocell.

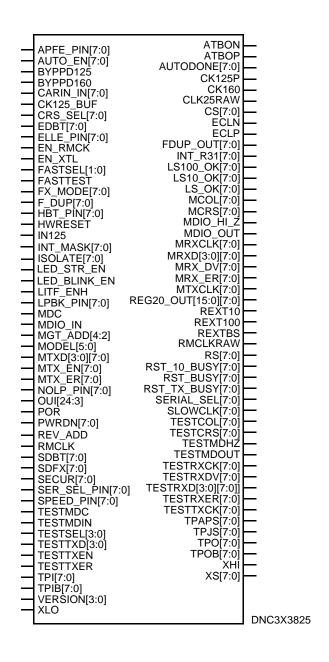

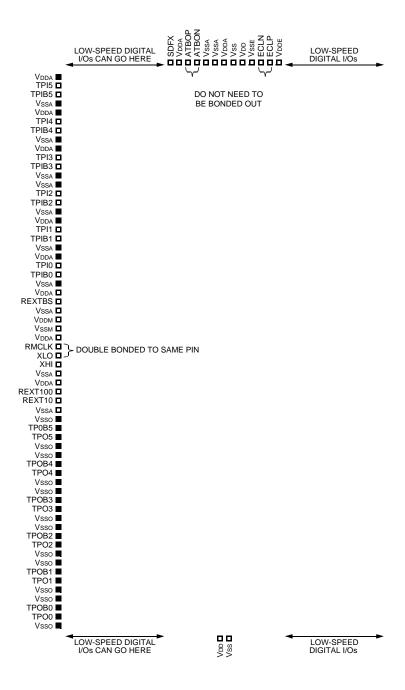

Figure 2 shows the I/Os of the DNC3X3625 macrocell.

#### **Functional Block Diagram**

Figure 1. DNC3X3625 Functional Block Diagram (1 Channel Shown)

#### **Description** (continued)

#### Macrocell I/Os

5-7541(F).a.r2

Figure 2. I/Os of the DNC3X3625 Macrocell

# **Signal Information**

# **Signal Descriptions**

Table 1. MII/5-Bit Serial Interface Signals

| Signal             | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCOL[5:0]          | 0    | <b>Collision Detect.</b> This signal signifies in half-duplex mode that a collision has occurred on the network. MCOL is asserted high whenever there is transmit and receive activity on the UTP media. MCOL is the logical AND of MTX_EN and receive activity, and is an asynchronous output. When SER_SEL_PIN is high and in 10Base-T mode, MCOL indicates the jabber timer has expired. |

| MCRS[5:0]          | 0    | Carrier Sense. When CRS_SEL is low, this signal is asserted high when either the transmit or receive medium is nonidle. This signal remains asserted throughout a collision condition. When CRS_SEL is high, MCRS is asserted on receive activity only. CRS_SEL is set via the MII management interface or the CRS_SEL signal.                                                              |

| MRXCLK<br>[5:0]    | 0    | <b>Receive Clock.</b> 25 MHz clock output in 100 Mbits/s mode, 2.5 MHz output in 10 Mbits/s nibble mode, and 10 MHz in 10 Mbits/s serial mode. MRXCLK has a worst-case 35/65 duty cycle. MRXCLK provides the timing reference for the transfer of MRX_DV, MRXD, and MRX_ER signals.                                                                                                         |

| MRXD[3:0]<br>[5:0] | 0    | Receive Data. 4-bit parallel data outputs that are synchronous to MRXCLK. When MRX_ER is asserted high in 100 Mbits/s mode, an error code will be presented on MRXD[3:0] where appropriate. The codes are as follows:                                                                                                                                                                       |

|                    |      | Packet errors: ERROR_CODES = 2h. Link errors: ERROR_CODES = 3h. (Packet and link error codes will only be repeated if registers [29.9] and [29.8] are enabled.) Premature end errors: ERROR_CODES = 4h. Code errors: ERROR_CODES = 5h.                                                                                                                                                      |

|                    |      | When SER_SEL_PIN is active-high and 10 Mbits/s mode is selected, MRXD[0] is used for data output and MRXD[3:1] are 3-stated.                                                                                                                                                                                                                                                                |

| MRX_DV<br>[5:0]    | 0    | <b>Receive Data Valid.</b> When this signal is high, it indicates the DNC3X3625 is recovering and decoding valid nibbles on MRXD[3:0], and the data is synchronous with MRXCLK. MRX_DV is synchronous with MRXCLK. This signal is not used in serial 10 Mbits/s mode.                                                                                                                       |

| MRX_ER<br>[5:0]    | 0    | <b>Receive Error.</b> When high, MRX_ER indicates the DNC3X3625 has detected a coding error in the frame presently being received. MRX_ER is synchronous with MRXCLK.                                                                                                                                                                                                                       |

| MTXCLK<br>[5:0]    | 0    | <b>Transmit Clock</b> . 25 MHz clock output in 100 Mbits/s mode, 2.5 MHz output in 10 Mbits/s MII mode, 10 MHz output in 10 Mbits/s serial mode. MTXCLK provides timing reference for the transfer of the MTX_EN, MTXD, and MTX_ER signals sampled on the rising edge of MTXCLK.                                                                                                            |

| MTXD[3:0]<br>[5:0] | I    | <b>Transmit Data.</b> 4-bit parallel input synchronous with MTXCLK. When SER_SEL_PIN is active-high and 10 Mbits/s mode is selected, only MTXD[0] is valid.                                                                                                                                                                                                                                 |

| MTX_EN<br>[5:0]    | I    | <b>Transmit Enable.</b> When driven high, this signal indicates there is valid data on MTXD[3:0]. MTX_EN is synchronous with MTXCLK. When SER_SEL_PIN is active-high and 10 Mbits/s mode is selected, this signal indicates there is valid data on MTXD[0].                                                                                                                                 |

| MTX_ER<br>[5:0]    | I    | <b>Transmit Coding Error.</b> When driven high, this signal causes the encoder to intentionally corrupt the byte being transmitted across the MII (00100 will be transmitted). When in 10 Mbits/s mode, this signal is ignored.                                                                                                                                                             |

**Table 2. MII Management Signals**

| Signal        | Туре | Name/Description                                                                                                                                                                           |  |  |  |

|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MDC           | I    | Management Data Clock. This is the timing reference for the transfer of data on the MDIO signal. This signal may be asynchronous to MRXCLK and MTXCLK. The maximum clock rate is 12.5 MHz. |  |  |  |

|               |      | When running MDC above 6.25 MHz, MDC must be synchronous with CLK25RAW and have a setup time of 15 ns and a hold time of 5 ns with respect to CLK25RAW.                                    |  |  |  |

| MDIO_IN       | I    | <b>Management Data Input.</b> Control information is driven by the station management, synchronous with MDC, onto this input.                                                              |  |  |  |

| MDIO_OUT      | 0    | <b>Management Data Output.</b> Status information is driven by the DNC3X3625, synchronous with MDC, onto this output.                                                                      |  |  |  |

| MDIO_HI_Z     | 0    | <b>Management Data Output Enable.</b> When high, this signal can be used to 3-state the MDIO bidirectional buffer (external to the DNC3X3625).                                             |  |  |  |

| INT_MASK[5:0] | I    | Interrupt Mask. When set high, no interrupt is generated under any condition. When set low, interrupts are generated according to bit [31.7]. This signal is ORed with bit [31.6].         |  |  |  |

| INT_R31[5:0]  | 0    | <b>Maskable Status Interrupt.</b> This signal will go high whenever there is a change in status as defined in Table 27.                                                                    |  |  |  |

Table 3. 10/100 Mbits/s Twisted-Pair (TP) Interface Signals

| Signal        | Туре | Name/Description                                                                                                                                                         |  |  |  |  |

|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TPI<br>[5:0]  | PADI | Received Data. Positive differential received 125 Mbaud MLT3 or 10 Mbaud Manchester data from magnetics.                                                                 |  |  |  |  |

|               |      | <b>Fiber-Optic Data Input.</b> Positive differential received 125 Mbaud pseudo-ECL data from fiber transceiver.                                                          |  |  |  |  |

| TPIB<br>[5:0] | PADI | Received Data. Negative differential received 125 Mbaud MLT3 or 10 Mbaud Manchester data from magnetics.                                                                 |  |  |  |  |

|               |      | <b>Fiber-Optic Data Input.</b> Negative differential received 125 Mbaud pseudo-ECL data from fiber transceiver.                                                          |  |  |  |  |

| TPO<br>[5:0]  | PADO | <b>Transmit Data.</b> Positive differential transmit 125 Mbaud MLT3 or 10 Mbaud Manchester data to magnetics.                                                            |  |  |  |  |

|               |      | <b>Fiber-Optic Data Output.</b> Positive differential transmit 125 Mbaud pseudo-ECL compatible data to fiber transceiver.                                                |  |  |  |  |

| TPOB<br>[5:0] | PADO | <b>Transmit Data.</b> Negative differential transmit 125 Mbaud MLT3 or 10 Mbaud Manchester data to magnetics.                                                            |  |  |  |  |

|               |      | <b>Fiber-Optic Data Output.</b> Negative differential transmit 125 Mbaud pseudo-ECL compatible data to fiber transceiver.                                                |  |  |  |  |

| REXT10        | PADO | <b>Current Setting 10 Mbits/s.</b> An external resistor (21.0 k $\Omega$ ) is placed from this signal to ground to set the 10 Mbits/s TP driver transmit output level.   |  |  |  |  |

| REXT100       | PADO | <b>Current Setting 100 Mbits/s.</b> An external resistor (21.5 k $\Omega$ ) is placed from this signal to ground to set the 100 Mbits/s TP driver transmit output level. |  |  |  |  |

| REXTBS        | PADO | Band Gap Reference for the Receive Channel. Connect this signal to a 24.9 k $\Omega$ ± 1% resistor to ground. The parasitic load capacitance should be less than 15 pF.  |  |  |  |  |

#### LEDs operate as follows:

LED\_STR\_EN = 0, LED\_BLINK\_EN = 0 => No stretching/blinking.

LED\_STR\_EN = 1, LED\_BLINK\_EN = 0 => Stretch to 42 ms, minimum.

LED\_STR\_EN = 0, LED\_BLINK\_EN = 1 => Every activity causes 42 mS ON, 42 mS OFF blink.

LED\_STR\_EN = 1, LED\_BLINK\_EN = 1 => Every activity causes 0.5 second ON, 0.5 second OFF blink.

#### **Table 4. Status Signals**

| Signal        | Туре | Name/Description                                                                                                                               |  |  |  |

|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| XS[5:0]       | 0    | <b>Transmit Status.</b> This signal indicates transmit activity. This output can be stretched or blinked per the description given above.      |  |  |  |

| RS[5:0]       | 0    | <b>Receive Status</b> . This signal indicates receive activity. This output can be stretched or blinked per the description given above.       |  |  |  |

| CS[5:0]       | 0    | <b>Collision Status</b> . This signal indicates collision occurrence. This output can be stretched or blinked per the description given above. |  |  |  |

| LS10_OK[5:0]  | 0    | Link10. This signal indicates good link status for 10 Mbits/s.                                                                                 |  |  |  |

| LS100_OK[5:0] | 0    | Link100. This signal indicates good link status for 100 Mbits/s.                                                                               |  |  |  |

| LS_OK[5:0]    | 0    | Link Status. Indicates link status.                                                                                                            |  |  |  |

| FDUP_OUT[5:0] | 0    | <b>Full-Duplex Status</b> . If this signal is high, it indicates full-duplex link, and if it is low, then the link is half duplex.             |  |  |  |

| TPJS[5:0]     | 0    | Jabber Status. Indicates that there is a jabber condition (only in 10 Mbits/s).                                                                |  |  |  |

| TPAPS[5:0]    | 0    | TP Autopolarity Status. Indicates if autopolarity has been detected and corrected.                                                             |  |  |  |

Table 5. Clock and Reset Signals

| Signal           | Туре               | Name/Description                                                                                                                                                                                                      |  |  |  |  |  |

|------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| EN_RMCK          | I                  | <b>Enable RMCLK</b> . When high, this signal selects RMCLK as the clock input. This signal and EN_XTL cannot be high simultaneously.                                                                                  |  |  |  |  |  |

| RMCLK            | PADI*              | <b>Primary Input Clock.</b> The frequency of this clock can be either 125 MHz or 50 MHz. IN125 is used to indicate the appropriate frequency. This clock input is used when EN_RMCK is high.                          |  |  |  |  |  |

| IN125            | I                  | Input Clock Frequency Select. When high, this signal will indicate that the frequency of RMCLK is 125 MHz; else the clock frequency is 50 MHz.                                                                        |  |  |  |  |  |

| EN_XTL           | I                  | <b>Enable Crystal Input</b> . This signal, when high, will select the crystal input (XLO) as the clock input. This signal and EN_RMCK cannot be high simultaneously.                                                  |  |  |  |  |  |

| XLO              | PADI <sup>†</sup>  | Crystal Oscillator Input. A 25 MHz crystal ± 25 ppm can be connected across XLO and XHI. Alternately, a 25 MHz external CMOS oscillator can be connected to this input. This clock input is used when EN_XTL is high. |  |  |  |  |  |

| XHI              | PADO<br>(optional) | <b>Crystal Oscillator Output</b> . This pad does not have to be bonded out if crystal is not used.                                                                                                                    |  |  |  |  |  |

| CLK25RAW         | 0                  | CLK25RAW. 25 MHz output clock.                                                                                                                                                                                        |  |  |  |  |  |

| RMCLKRAW         | 0                  | RMCLKRAW. Buffered version of the RMCLK. This is either 50 MHz or 125 MHz, depending on RMCLK frequency.                                                                                                              |  |  |  |  |  |

| SLOWCLK[5:0]     | 0                  | 24 Hz Clock Output. This is a 24 Hz output signal.                                                                                                                                                                    |  |  |  |  |  |

| HWRESET          | I                  | <b>Full-Chip Reset.</b> Reset is active-high. The RST_BUSY signal will go low when reset is complete. 10Base-T and 100Base-TX/-FX are in reset until enabled and take 1.3 ms to come out of reset.                    |  |  |  |  |  |

| POR              | I                  | <b>Power-On Reset.</b> If a powerup reset (PUR) cell from ASIC library is not used, then tie this input low.                                                                                                          |  |  |  |  |  |

| RST_BUSY[5:0]    | 0                  | Reset Busy. This signal indicates that the DNC3X3625 is in reset.                                                                                                                                                     |  |  |  |  |  |

| RST_10_BUSY[5:0] | 0                  | <b>10Base-T in Reset.</b> This signal indicates that the 10 Mbits/s logic is in reset.                                                                                                                                |  |  |  |  |  |

| RST_TX_BUSY[5:0] | 0                  | <b>100Base-TX Reset.</b> This signal indicates that the 100 Mbits/s logic is in reset.                                                                                                                                |  |  |  |  |  |

| BYPPD125         | I                  | This pin, when high, powers up the 125 MHz PLL permanently, allowing CK125P to be used for external logic at all times.                                                                                               |  |  |  |  |  |

| BYPPD160         | I                  | This pin, when high, powers up the 160 MHz PLL permanently, allowing CK160 to be used for external logic at all times.                                                                                                |  |  |  |  |  |

| CK125_BUF        | I                  | This pin is the feedback for CK125P. Normally this will be connected to CK125P or any external chip clock buffers for CK125P.                                                                                         |  |  |  |  |  |

| CK160            | 0                  | This is a 160 MHz output clock; this will be available if 10Base-T is enabled or BYPPD160 is high.                                                                                                                    |  |  |  |  |  |

| CK125P           | 0                  | This is a 125 MHz output clock, which must be fed back to CK125_BUF. This will be available when in 100Base-Tx mode or if BYPPD125 is high or if IN125 is high.                                                       |  |  |  |  |  |

<sup>\*</sup> Double bonded with XLO.

<sup>†</sup> Double bonded with RMCLK.

Table 6. Control/Status Signals

| Signal           | Туре | Description                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AUTO_EN[5:0]     | I    | <b>Autonegotiation Enable.</b> When this signal is high, autonegotiation is enabled. Pulsing this signal will cause autonegotiation to restart. This input has the same function as register 0, bit 12. This input and the register bit are ANDed together.                                                                                                                          |  |  |  |  |

| F_DUP[5:0]       | I    | <b>Full-Duplex Mode.</b> When this signal is set high, the PHY will be in full-duplex mode. A low on this signal will put it in half-duplex mode. This signal is ignored when autonegotiation is enabled. This is the same function as register 0, bit 8. This input and the register bit are ORed together.                                                                         |  |  |  |  |

| CRS_SEL[5:0]     | I    | Carrier Sense Select. This signal may be used to select the mode of MCRS operation. When this signal is pulled high, MCRS will be asserted on receive activity only. This is the same function as register 29, bit 10. This input and the register bit are ORed together.                                                                                                            |  |  |  |  |

| SER_SEL_PIN[5:0] | I    | <b>Serial Mode Select.</b> This signal may be used to set the SERIAL_SEL function of register 30, bit 1 by pulling it high, if station management is unavailable. This input and the register bit are ORed together.                                                                                                                                                                 |  |  |  |  |

| CARIN_IN[5:0]    | I    | Carrier Integrity Enable. If this signal is pulled high, it will enable the carrier integrity function of register 29, bit 3, if station management is unavailable. This input and the register bit are ORed together.                                                                                                                                                               |  |  |  |  |

| EDBT[5:0]        | I    | <b>Encoder/Decoder Bypass.</b> If this signal is pulled high, it will enable the encoder/decoder bypass function of register 29, bit 6, if station management is unavailable. This input and the register bit are ORed together.                                                                                                                                                     |  |  |  |  |

| SDBT[5:0]        | I    | Scrambler/Descrambler. This signal may be used to enable the scrambler/descrambler bypass function by pulling this signal high, if station management is unavailable. This is the same function as register 29, bit 4. This input and the register bit are ORed together.                                                                                                            |  |  |  |  |

| SPEED_PIN[5:0]   | I    | <b>Speed.</b> This signal can be used to select the operating speed and is the same function as register 0, bit 13:                                                                                                                                                                                                                                                                  |  |  |  |  |

|                  |      | ■ If this signal is pulled high, it will enable 100 Mbits/s operation.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                  |      | ■ If this signal is pulled low, it will enable 10 Mbits/s operation.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                  |      | This signal is ignored when autonegotiation is enabled. This signal and the register bit are ANDed.                                                                                                                                                                                                                                                                                  |  |  |  |  |

| MGT_ADD[4:2]     | I    | Management Address [4:2]. These signals set the management addresses and are decoded as follows:                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                  |      | MGT_ADD[4:2]       PHY 0, PHY 1, PHY 2, PHY 3, PHY 4, PHY 5         000       0, 1, 2, 3, 4, 5         001       8, 9, 10, 11, 12, 13         010       16, 17, 18, 19, 20, 21         011       24, 25, 26, 27, 28, 29         100       6, 7, 8, 9, 10, 11         101       12, 13, 14, 15, 16, 17         110       18, 19, 20, 21, 22, 23         111       0, 0, 0, 0, 0, 0, 0 |  |  |  |  |

| REV_ADD          | I    | Reverse Phy Address. Reverse the order of Ports for Management Access. (PHY0 is highest address, PHY5 is lowest address)                                                                                                                                                                                                                                                             |  |  |  |  |

| FX_MODE[5:0]     | I    | <b>FX_MODE</b> . When this signal is high, it puts DNC3X3625 in fiber-optic mode. This signal is ORed with register 29, bit 0 [29.0].                                                                                                                                                                                                                                                |  |  |  |  |

Table 6. Control/Status Signals (continued)

| Signal        | Туре                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|---------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| FASTTEST      | I                   | Fast Test. This signal should be low for normal operation. When high, the internal timers run faster than normal, with the speedup determined by FASTSEL[1:0]                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| FASTSEL[1:0]  | I                   | Fast Speed Select. When FASTTEST is high, the speedup of the timers (10 Mbit/s NLP link, 10 Mbit/s jabber, reset timers, autonegotiation counters) is as follows:  00 = No speedup.  01 = 16x speedup.  10 = 64x speedup.  11 = 256x speedup. (Autonegotiation does not work at this speedup.)                                                                                                                                                                               |  |  |  |  |

| LITF_ENH      | I                   | <b>Enhanced Link Integrity Test Function.</b> When this input is high, The link will be deasserted when 31 Manchester violations have occurred.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| SDFX[5:0]     | PAD<br>(optional I) | <b>SDFX.</b> Signal detect from fiber-optic receiver. This pad does not have to be bonded out if fiber mode is not used.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| SECUR[5:0]    | I                   | <b>Security.</b> When this input is high and MTX_EN is high, JAM pattern (55) is transmitted.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ISOLATE[5:0]  | I                   | <b>Isolate.</b> When this signal is high, the macrocell will come out of reset in isolate mode per the <i>IEEE</i> standard. If this is low, then the macrocell will come out of reset in normal mode. When isolated, all receive outputs are low, and all transmit requests are ignored. While isolated, the macrcell will respond to management transactions, detect, and transmit link pulses. Register 0, bit 10, is used to put the transceiver in/out of isolate mode. |  |  |  |  |

| APFE_PIN[5:0] | I                   | <b>Autopolarity Function Enable (Active Low).</b> When this signal is set low and the DNC3X3625 is operating at 10 Mbits/s, the autopolarity function will determine if the TP link is wired with a polarity reversal:                                                                                                                                                                                                                                                       |  |  |  |  |

|               |                     | ■ The DNC3X3625 will assert the autopolarity status (APS) bit (register 28, bit 6) and correct the polarity reversal.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|               |                     | ■ If this signal is set high and the DNC3X3625 is operating at 10 Mbits/s, the reversal will not be corrected.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| ELLE_PIN[5:0] | ı                   | <b>Extended Line Length Enable.</b> When this signal is set high, the receive squelch level is reduced from a nominal 435 mV to 350 mV, allowing reception of signals with lower amplitude. This is the same function as register 30, bit 4. The input and the register bit are ORed together.                                                                                                                                                                               |  |  |  |  |

| HBT_PIN[5:0]  | I                   | <b>Heartbeat Enable.</b> When asserted high, this input will enable the heartbeat function (serial mode). This is the same function as register 30, bit 5. The input and the register bit are ORed together.                                                                                                                                                                                                                                                                 |  |  |  |  |

| LPBK_PIN[5:0] | I                   | <b>Loopback.</b> When this signal is asserted high DNC3X3625 is in loopback mode. No data transmission will take place on the media and any receive data will be ignored. This is the same function as register 0, bit 14. The input and the register bit are ORed together.                                                                                                                                                                                                 |  |  |  |  |

| NOLP_PIN[5:0] | Ī                   | <b>No Link Pulse Mode.</b> Setting this signal high will allow 10 Mbits/s operation with link pulses disabled. If the DNC3X3625 is configured for 100 Mbits/s operation, this signal is ignored. This is the same function as register 30, bit 0. The input and the register bit are ORed together.                                                                                                                                                                          |  |  |  |  |

| LED_STR_EN    | I                   | <b>LED Stretch Enable.</b> This pin, when low, disables stretching. When high, the LED output is stretched to 42 ms minimum, unless LED_BLINK_EN is high. This signal is ORed with register 29, bit 7.                                                                                                                                                                                                                                                                       |  |  |  |  |

Table 6. Control/Status Signals (continued)

| Signal                  | Туре | Description                                                                                                                                                                                                                                                                                                    |

|-------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED_BLINK_EN            | I    | <b>LED Blink Enable.</b> This pin, when low, disables blinking. When high, the LED output will blink high for 42 ms and low for 42 ms whenever there is activity, unless LED_STR_EN is high, in which case the blinking is 0.5 seconds high and 0.5 seconds low. This signal is ORed with register 29, bit 11. |

| OUI[24:3]               | I    | <b>Organizationally Unique Identifier.</b> This can be programmed by the user, upon instantiation of the macro.                                                                                                                                                                                                |

| MODEL[5:0]              | I    | <b>Model Number.</b> 6-bit model number of the device. This can be programmed upon instantiation.                                                                                                                                                                                                              |

| VERSION[3:0]            | I    | <b>Revision Number.</b> The value of the present revision number. This can be programmed upon instantiation.                                                                                                                                                                                                   |

| PWRDN[5:0]              | I    | <b>Powerdown.</b> When high, this signal powers down the PHY and resets all management registers.                                                                                                                                                                                                              |

| SERIAL_SEL[5:0]         | 0    | Serial Select. When this signal is high, it indicates 10 Mbit/s serial mode. When SERIAL_SEL is low, the macro is in 100 Mbits/s or 10 Mbits/s parallel mode.                                                                                                                                                  |

| AUTODONE[5:0]           | 0    | Autonegotiation Done. This signal goes high whenever autonegotiation has completed. It will go low if autonegotiation has to restart.                                                                                                                                                                          |

| RG20_OUT[15:0]<br>[5:0] | 0    | Register 20 Access. This bus provides access to the user-defined register. A write to this register can be through MDIO.                                                                                                                                                                                       |

**Table 7. Testability Signals**

| Signal            | Туре       | Description                                                                                                                                 |  |  |  |  |

|-------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TESTSEL[3:0]      | I          | <b>Test Mode Select.</b> These pins enable the PHY to be in various test modes: scan, analog, etc. Lucent requires access to these pins for |  |  |  |  |

|                   |            | manufacturing testing. They should be held low for normal operation.                                                                        |  |  |  |  |

| TESTMDC           | I          | Test Mode Inputs. These test inputs provide a high level of controlla-                                                                      |  |  |  |  |

| TESTTXD[3:0]      |            | bility to the macrocell, either as scan inputs or as digital/analog test                                                                    |  |  |  |  |

| TESTTXER          |            | inputs/controls depending on the test mode selected by TESTSEL[3:0].                                                                        |  |  |  |  |

| TESTTXEN          |            |                                                                                                                                             |  |  |  |  |

| TESTCRS[5:0]      | 0          | Test Mode Outputs. These test output pins provide observability in the                                                                      |  |  |  |  |

| TESTCOL[5:0]      |            | form of either scan outputs or digital/analog test outputs depending on                                                                     |  |  |  |  |

| TESTRXCK[5:0]     |            | the test mode selected by TESTSEL[3:0]. The TESTRXD[3:0][5:0] a                                                                             |  |  |  |  |

| TESTTXCK[5:0]     |            | TESTRXER[5:0] must be mapped to outputs during test. The other test output should be mapped, if possible, to ease PHY debugging.            |  |  |  |  |

| TESTRXD[3:0][5:0] |            | output should be mapped, if possible, to ease 1111 debugging.                                                                               |  |  |  |  |

| TESTRXER[5:0]     |            |                                                                                                                                             |  |  |  |  |

| TESTRXDV[5:0]     |            |                                                                                                                                             |  |  |  |  |

| ATBOP             | PADO       | Analog Test Output Pins. These are used in Lucent test modes. They                                                                          |  |  |  |  |

| ATBON             | (optional) | should be connected to bond pads, but are not required to be                                                                                |  |  |  |  |

| ECLP              |            | connected to package pins.                                                                                                                  |  |  |  |  |

| ECLN              |            |                                                                                                                                             |  |  |  |  |

| TESTMDIN          | I          | Test Mode MDIN, MDOUT, and MDHZ. Input, output, and I/O control                                                                             |  |  |  |  |

| TESTMDOUT         | 0          | signals from/to a bidirectional buffer.                                                                                                     |  |  |  |  |

| TESTMDHZ          | 0          |                                                                                                                                             |  |  |  |  |

#### **MII Station Management**

#### **Basic Operation**

The primary function of station management is to transfer control and status information about the DNC3X3625 to a management entity. This function is accomplished by the MDC clock input, which has a maximum frequency of 25 MHz, along with the MDIO signal.

The MII management interface uses MDC and MDIO to physically transport information between the PHY and the station management entity.

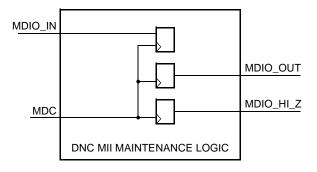

In the DNC3X3625, the MDIO pin is implemented as three signals: MDIO\_IN, MDIO\_OUT, and MDIO\_HIZ. MDIO\_IN is the information coming from the MAC and is ignored during the TA and DATA fields for MDIO reads. MDIO\_HIZ will be high except during MDIO reads, in which case MDIO\_OUT is the PHY data. Under no condition should the input MDIO\_IN be 3-stated. These can be connected to control an I/O buffer if off-chip access is required.

A specific set of registers and their contents (described in Table 9) defines the nature of the information transferred across the MDIO interface. Frames transmitted on the MII management interface will have the frame structure shown in Table 8. The order of bit transmission is from left to right. Note that reading and writing the management register must be completed without interruption. The port addresses are set by the MGT\_ADD pin (see Table 6 for more detail).

**Table 8. MII Management Frame Format**

| Read/Write<br>(R/W) | Pre | ST | OP | PHYAD | REGAD | TA | DATA           | IDLE |

|---------------------|-----|----|----|-------|-------|----|----------------|------|

| R                   | 11  | 01 | 10 | AAAAA | RRRRR | Z0 | DDDDDDDDDDDDDD | Z    |

| W                   | 11  | 01 | 01 | AAAAA | RRRRR | 10 | DDDDDDDDDDDDDD | Z    |

Table 9. MII Management Frames—Field Description

| Field  | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pre    | <b>Preamble</b> . The DNC3X3625 will accept frames with no preamble. This is indicated by a 1 in register 1, bit 6.                                                                                                                                                                                                                                                                                            |

| ST     | Start of Frame. The start of frame is indicated by a 01 pattern.                                                                                                                                                                                                                                                                                                                                               |

| OP     | <b>Operation Code</b> . The operation code for a read transaction is 10. The operation code for a write transaction is a 01.                                                                                                                                                                                                                                                                                   |

| PHYADD | <b>PHY Address</b> . The PHY address is 5 bits, allowing for 32 unique addresses. The first PHY address bit transmitted and received is the MSB of the address. A station management entity that is attached to multiple PHY entities must have prior knowledge of the appropriate PHY address for each entity.                                                                                                |

| REGAD  | <b>Register Address.</b> The register address is 5 bits, allowing for 32 unique registers within each PHY. The first register address bit transmitted and received is the MSB of the address.                                                                                                                                                                                                                  |

| TA     | <b>Turnaround</b> . The turnaround time is a 2-bit time spacing between the register address field, and the data field of a frame, to avoid drive contention on MDIO during a read transaction. During a write to the DNC3X3625, these bits are driven to 10 by the station. During a read, the MDIO is not driven during the first bit time and is driven to a 0 by the DNC3X3625 during the second bit time. |

| DATA   | <b>Data</b> . The data field is 16 bits. The first bit transmitted and received will be bit 15 of the register being addressed.                                                                                                                                                                                                                                                                                |

| IDLE   | <b>Idle Condition.</b> The IDLE condition on MDIO is a high-impedance state. All three state drivers will be disabled and the PHY's pull-up resistor will pull the MDIO line to a logic 1.                                                                                                                                                                                                                     |

### **MII Interface Design**

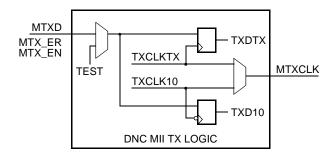

The chip layout will affect MII electrical specifications. Figures 3, 4, and 5 show the PHY logic on the interfaces. If the MAC logic follows the rules below, then the interface should function properly:

- 1. Transmit signals should change on the positive edge of TxClk.

- 2. Receive signals should be captured on the positive edge of RxClk.

- 3. Management output should change on the negative edge of MDC (and be stable on its positive edge) management inputs should be latched on the positive edge of MDC.

#### **Absolute Maximum Ratings** (TA = 25 °C)

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

**Table 10. Absolute Maximum Ratings**

| Parameter                                 | Symbol | Min  | Max       | Unit |

|-------------------------------------------|--------|------|-----------|------|

| Ambient Operating Temperature             | TA     | 0    | 70        | °C   |

| Storage Temperature                       | Tstg   | -40  | 125       | °C   |

| Power Dissipation                         | Po     | _    | 3.5       | W    |

| Voltage on Any Pin with Respect to Ground | _      | -0.5 | VDD + 0.5 | V    |

| Maximum Supply Voltage                    | _      | _    | 3.5       | V    |

**Table 11. Operating Conditions**

| Parameter                 | Symbol | Min | Тур* | Max   | Unit |

|---------------------------|--------|-----|------|-------|------|

| Operating Supply Voltage  | _      |     | 3.3  | 3.465 | V    |

| Power Dissipation:        |        |     |      |       |      |

| All Ports Autonegotiating | PD     | _   | _    | _     | mW   |

| All Ports 10Base-T Link   | PD     | _   | _    | _     | mW   |

| 10Base-T TX/RX 100%       | PD     | _   | _    | _     | mW   |

| 100Base-T TX              | PD     | _   | 2800 | _     | mW   |

<sup>\*</sup> Typical power dissipations are specified at 5 V and 25 °C. This is the power dissipated by the DNC3X3625. An additional 0.2 W of power is required for the external twisted-pair driver termination resistors.

### **Electrical Characteristics**

The following specifications apply for  $VDD = 3 V \pm 5\%$ .

Figure 3. DNC MII TX Logic

RXDTX, RXDVTX,

RXERTX

MRX\_ER,

MRX\_DV

MRX\_CLK

MRXCLK

RXER10,

RXD10, RXDV10

RXCLK10

DNC MII RX LOGIC

Figure 4. DNC MII RX Logic

Figure 5. DNC Maintenance Logic

5-7723(F).r1

5-7722(F).r2

5-7724(F)

# **Electrical Characteristics** (continued)

5-7725(F).r1

Figure 6. Typical Application (One Channel Shown)

### **Electrical Characteristics** (continued)

5-7725(F).r1

Figure 7. Pinout Assignment

5-5433(F).o

# **Electrical Characteristics** (continued)

Figure 8. Typical Single-Channel Twisted-Pair (TP) Interface

# **Register Information**

### **Register Descriptions**

The MII management 16-bit register set implemented is as follows. The PHY address pins control the management pins.

**Table 12. Summary of Management Registers (MR)**

| Register<br>Address | Symbol   | Name                                 | Default<br>(Hex Code) |

|---------------------|----------|--------------------------------------|-----------------------|

| 0                   | MR0      | Control                              | 3000h                 |

| 1                   | MR1      | Status                               | 7849h                 |

| 2                   | MR2      | PHY Identifier 1                     | TBD                   |

| 3                   | MR3      | PHY Identifier 2                     | TBD                   |

| 4                   | MR4      | Autonegotiation Advertisement        | 01E1h                 |

| 5                   | MR5      | Autonegotiation Link Partner Ability | 0000                  |

| 6                   | MR6      | Autonegotiation Expansion            | 0000                  |

| 7                   | MR7      | Next Page Transmit                   | 0000                  |

| 8—15                | MR8—MR15 | (Reserved)                           | _                     |

| 16                  | MR16     | PCS Control Register                 | 0000                  |

| 17                  | MR17     | Autonegotiation (read register A)    | 0000                  |

| 18                  | MR18     | Autonegotiation (read register B)    | 0000                  |

| 19                  | MR19     | Lucent Analog Test Register          | _                     |

| 20                  | MR20     | User-defined Register                | _                     |

| 21                  | MR21     | RXER Counter                         | 0000                  |

| 22                  | MR22     | Lucent Analog Test Registers         | _                     |

| 23                  | MR23     |                                      |                       |

| 24                  | MR24     |                                      |                       |

| 25                  | MR25     | Lucent Analog Test (Tuner) Registers | _                     |

| 26                  | MR26     |                                      |                       |

| 27                  | MR27     |                                      |                       |

| 28                  | MR28     | Device Specific 1                    | _                     |

| 29                  | MR29     | Device Specific 2                    | 2080                  |

| 30                  | MR30     | Device Specific 3                    | 0000                  |

| 31                  | MR31     | Quick Status Register                | _                     |

|                     |          |                                      |                       |

Table 13. MR0—Control Register Bit Descriptions

| Bit*             | Type <sup>†</sup> | Description                                                                                                                                                                                                                                                                                                                                                         |

|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.15 (SW_RESET)  | R/W               | <b>Reset.</b> Setting this bit to a 1 will reset the DNC3X3625. All registers will be set to their default state. This bit is self-clearing. The default is 0.                                                                                                                                                                                                      |

| 0.14 (LOOPBACK)  | R/W               | <b>Loopback.</b> When this bit is set to 1, no data transmission will take place on the media. Any receive data will be ignored. The loopback signal path will contain all circuitry up to, but not including, the PMD. The default value is a 0.                                                                                                                   |

| 0.13 (SPEED100)  | R/W               | <b>Speed Selection.</b> The value of this bit reflects the current speed of operation (1 = 100 Mbits/s; 0 = 10 Mbits/s). This bit will only affect operating speed when the autonegotiation enable bit (register 0, bit 12) is disabled (0). This bit is ignored when autonegotiation is enabled (register 0, bit 12). This bit is ANDed with the SPEED_PIN signal. |

| 0.12 (NWAY_ENA)  | R/W               | <b>Autonegotiation Enable.</b> The autonegotiation process will be enabled by setting this bit to a 1. The default state is a 1.                                                                                                                                                                                                                                    |

| 0.11 (PWRDN)     | R/W               | <b>Powerdown.</b> The DNC3X3625 may be placed in a low-power state by setting this bit to a 1, both the 10 Mbits/s transceiver and the 100 Mbits/s transceiver will be powered down. While in the powerdown state, the DNC3X3625 will respond to management transactions. The default state is a 0.                                                                 |

| 0.10 (ISOLATE)   | R/W               | <b>Isolate.</b> When this bit is set to a 1, the MII outputs will be brought to the high-impedance state. The default state is a 0.                                                                                                                                                                                                                                 |

| 0.9 (REDONWAY)   | R/W               | <b>Restart Autonegotiation.</b> Normally, the autonegotiation process is started at powerup. The process may be restarted by setting this bit to a 1. The default state is a 0. The NWAYDONE bit (register 1, bit 5) is reset when this bit goes to a 1. This bit is self-cleared when autonegotiation restarts.                                                    |

| 0.8 (FULL_DUP)   | R/W               | <b>Duplex Mode.</b> This bit reflects the mode of operation (1 = full duplex; 0 = half duplex). This bit is ignored when the autonegotiation enable bit (register 0, bit 12) is enabled. The default state is a 0. This bit is ORed with the F_DUP pin.                                                                                                             |

| 0.7 (COLTST)     | R/W               | <b>Collision Test.</b> When this bit is set to a 1, the DNC3X3625 will assert the MCOL signal in response to MTX_EN.                                                                                                                                                                                                                                                |

| 0.6:0 (RESERVED) | NA                | Reserved. All bits will read 0.                                                                                                                                                                                                                                                                                                                                     |

<sup>\*</sup> The format for the bit descriptions is as follows: the first number is the register number, the second number is the bit position in the register. † R = read, W = write, NA = not applicable.

20

Table 14. MR1—Status Register Bit Descriptions

| Bit*              | Type <sup>†</sup> | Description                                                                               |

|-------------------|-------------------|-------------------------------------------------------------------------------------------|

| 1.15 (T4ABLE)     | R                 | 100Base-T4 Ability. This bit will always be a 0.                                          |

|                   |                   | 0: Not able.                                                                              |

|                   |                   | 1: Able.                                                                                  |

| 1.14 (TXFULDUP)   | R                 | 100Base-TX Full-Duplex Ability. This bit will always be a 1.                              |

|                   |                   | 0: Not able.                                                                              |

|                   |                   | 1: Able.                                                                                  |

| 1.13 (TXHAFDUP)   | R                 | 100Base-TX Half-Duplex Ability. This bit will always be a 1.                              |

|                   |                   | 0: Not able.                                                                              |

|                   |                   | 1: Able.                                                                                  |

| 1.12 (ENFULDUP)   | R                 | 10Base-T Full-Duplex Ability. This bit will always be a 1.                                |

|                   |                   | 0: Not able.                                                                              |

|                   |                   | 1: Able.                                                                                  |

| 1.11 (ENHAFDUP)   | R                 | 10Base-T Half-Duplex Ability. This bit will always be a 1.                                |

|                   |                   | 0: Not able.                                                                              |

|                   |                   | 1: Able.                                                                                  |

| 1.10:7 (RESERVED) | R                 | Reserved. All bits will read as a 0.                                                      |

| 1.6 (NO_PA_OK)    | R                 | Suppress Preamble. When this bit is set to a 1, it indicates that the                     |

|                   |                   | DNC3X3625 accepts management frames with the preamble suppressed.                         |

| 1.5 (NWAYDONE)    | R                 | <b>Autonegotiation Complete.</b> When this bit is a 1, it indicates the autonegotiation   |

|                   |                   | process has been completed. The contents of registers MR4, MR5, MR6, and                  |

|                   |                   | MR7 are now valid. The default value is a 0. This bit is reset when autonegotia-          |

|                   |                   | tion is started.                                                                          |

| 1.4 (REM_FLT)     | R                 | <b>Remote Fault.</b> When this bit is a 1, it indicates a remote fault has been detected. |

|                   |                   | This bit will remain set until cleared by reading the register. The default is a 0.       |

| 1.3 (NWAYABLE)    | R                 | Autonegotiation Ability. When this bit is a 1, it indicates the ability to perform        |

|                   |                   | autonegotiation. The value of this bit is always a 1.                                     |

| 1.2 (LSTAT_OK)    | R                 | Link Status. When this bit is a 1, it indicates a valid link has been established.        |

|                   |                   | This bit has a latching function: a link failure will cause the bit to clear and stay     |

|                   |                   | cleared until it has been read via the management interface.                              |

| 1.1 (JABBER)      | R                 | Jabber Detect. This bit will be a 1 whenever a jabber condition is detected. It will      |

|                   |                   | remain set until it is read, and the jabber condition no longer exists.                   |

| 1.0 (EXT_ABLE)    | R                 | Extended Capability. This bit indicates that the DNC3X3625 supports the                   |

|                   |                   | extended register set (MR2 and beyond). It will always read a 1.                          |

<sup>\*</sup> The format for the bit descriptions is as follows: the first number is the register number, the second number is the bit position in the register. † R = read.

Table 15. MR2, MR3—PHY Identification Registers (1 and 2) Bit Descriptions

| Bit*                 | Type <sup>†</sup> | Description                                                                                                                                                                                                                |

|----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.15:0 (OUI[3:18])   | R                 | <b>Organizationally Unique Identifier.</b> The third through the twenty-fourth bit of the OUI assigned to the PHY manufacturer by the <i>IEEE</i> are to be placed in bits 2.15:0 and 3.15:10. This value is programmable. |

| 3.15:10 (OUI[19:24]) | R                 | <b>Organizationally Unique Identifier.</b> The remaining 6 bits of the OUI. The value for bits 24:19 is programmable.                                                                                                      |

| 3.9:4 (MODEL[5:0])   | R                 | <b>Model Number.</b> 6-bit model number of the device. The model number is programmable.                                                                                                                                   |

| 3.3:0 (VERSION[3:0]) | R                 | <b>Revision Number.</b> The value of the present revision number. The version number is programmable.                                                                                                                      |

<sup>\*</sup> The format for the bit descriptions is as follows: the first number is the register number, the second number is the bit position in the register. † R = read.

Table 16. MR4—Autonegotiation Advertisement Register Bit Descriptions

| Bit*              | Type <sup>†</sup> | Name/Description                                                                                                                                                                          |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.15 (NEXT_PAGE)  | R/W               | <b>Next Page.</b> The next page function is activated by setting this bit to a 1. This will allow the exchange of additional data. Data is carried by optional next pages of information. |

| 4.14 (ACK)        | R/W               | Acknowledge. This bit is the acknowledge bit from the link code word.                                                                                                                     |

| 4.13 (REM_FAULT)  | R/W               | <b>Remote Fault.</b> When set to 1, the DNC3X3625 indicates to the link partner a remote fault condition.                                                                                 |

| 4.12:11           | R/W               | Reserved.                                                                                                                                                                                 |

| 4.10 (PAUSE)      | R/W               | <b>Pause.</b> When set to a 1, it indicates that the DNC3X3625 wishes to exchange flow control information with its link partner.                                                         |

| 4.9 (100BASET4)   | R/W               | 100Base-T4. This bit should always be set to 0.                                                                                                                                           |

| 4.8 (100BASET_FD) | R/W               | <b>100Base-TX Full Duplex.</b> If written to 1, autonegotiation will advertise that the DNC3X3625 is capable of 100Base-TX full-duplex operation.                                         |

| 4.7 (100BASETX)   | R/W               | <b>100Base-TX.</b> If written to 1, autonegotiation will advertise that the DNC3X3625 is capable of 100Base-TX operation.                                                                 |