## Diode Terminator

# **DN5** SERIES

## Diode Terminator

Low parasitics, fast reverse recovery time, and a low forward voltage characteristic make KOA's DN5 Schottky diode network an excellent bus terminator for very high speed I/O. This network offers the designer a single package solution to address overshoot and undershoot problems, ringing, and bus reflections that are common to high speed I/O. Today these networks are commonly used to optimize bus performance in high end computers, external data storage peripherals, LAN networks, and many other applications where high transfer rates are necessary.

## **Features**

- Negligible reverse recovery time

- Low capacitance

- Low forward voltage drop

- 18-channel terminator in a single package

- Resolved bus impedance mismatch

## **Applications**

- Termination of data/control signals @ ≥ 66 MHz

- Dynamic RAM bus termination

- RISC architecture

### **Electrical Characteristics**

Supply Voltage

Channel Clamp

*Current* . . . . . . . . . . ±50mA

Package Power

*Rating* @ 70°C . . . . . . 1W

Operating

*Temperature* . . . . . . . 0°C to +70°C

Storage Temperature . . . -65°C to +150°C

Forward Voltage

(to VDD @ 50ma).... 0.55V to 0.90V

Forward Voltage

(to GND @ 50ma).... 0.55V to 0.85V

Reverse Recovery

*Time* (@ 50ma) . . . . . . <400ps

Channel Leakage

(0 < Vin < VDD) . . . . . 0.1µA to 5µA

Input Capacitance

$(I\dot{f} = 1M\dot{H}z,$

Vin = 2.5v) . . . . . . . . 5pF

*ESD Protection* . . . . . 4KV min.

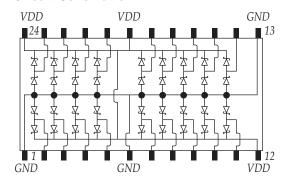

#### Circuit Schematic

#### **Available Pin Configurations**

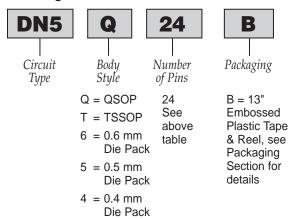

n = Number of Pins (24)See physical configurations on page G-3 for available pin/package configurations.

## **Physical Configurations**

| Body Style | Resistance<br>Pin Count |

|------------|-------------------------|

| QSOP       | . 24                    |

| TSSOP      | . 24                    |

| Die Pack * | . 24                    |

#### **Mechanical Characteristics**

| Item Material        |  |

|----------------------|--|

| Substrate Silicon    |  |

| Resistor materialTaN |  |

| Passivation Glass    |  |

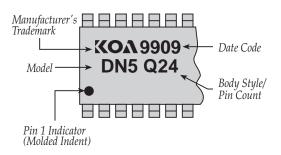

## **Part Marking**

## **Ordering Information**

<sup>\*</sup> See page J-6 for preliminary Die Pack specifications.