### Hardware Differences Between the DSP56002 and the DSP56303

by Barbara Johnson

The hardware differences between the DSP56002 and the DSP56303 must be considered when a system based on the DSP56002 is redesigned to use the DSP56303. This application note describes these hardware differences in detail. The DSP56300 is a rich product family, and, where applicable, this document also addresses changes that enable DSP56303 designs to migrate easily to other DSP56300 devices.

This application note does not describe an application per se. Rather it summarizes the hardware differences between two DSP products as a convenient reference for designers and programmers who are migrating to the DSP56303 from the DSP56002. It saves you the time that would be required to review the documentation and determine what these differences are.

For details on the software differences between the DSP56002 and DSP56303, refer to the application note AN1829/D, Software Differences Between the DSP56002 and the DSP56303, which covers the differences in the instruction pipeline, the instruction cache controller, and the instruction set. It also covers differences in various core modules—such as the arithmetic logic unit and address generation unit—and differences in the programming model.

### Contents

| 1     | Hardware Layout                     | 2   |

|-------|-------------------------------------|-----|

| 2     | Core                                | 7   |

| 2.1   | Power Supply                        |     |

| 2.2   | Electrical Characteristics          |     |

| 2.3   | Phase-Locked Loop (PLL)             | 8   |

| 2.4   | DMA Controller                      | .10 |

| 2.5   | Memory                              |     |

| 2.6   | Instruction Cache Controller        | .12 |

| 2.7   | Address Space Selection             |     |

| 3     | <b>Mode Control and Interrupts.</b> |     |

| 3.1   | Operating Modes                     |     |

| 3.2   | Interrupt Addresses and Sources     |     |

| 3.3   | Interrupt Priority Register         |     |

| 1     | Peripherals                         |     |

| 4.1   | Host Interface                      |     |

| 4.1.1 | Multiplexed Address/Data and        |     |

|       | Non-Multiplexed Bus Modes           | .21 |

| 4.1.2 | Single/Dual Data Strobe Bus Modes   | .22 |

| 4.1.3 | Single/Double Host Request Bus      |     |

|       | Modes                               | .22 |

| 1.1.4 | Big Endian/Little Endian Byte       |     |

|       | Order                               | .23 |

| 4.1.5 | Host Registers                      | .23 |

| 1.2   | Enhanced Synchronous Serial         |     |

|       | Interface                           | .24 |

| 1.2.1 | Network Enhancements                |     |

| 1.2.2 | Audio Enhancements                  | .25 |

| 1.2.3 | General Enhancements                | .25 |

| 1.3   | Triple Timer                        | .26 |

| 4.3.1 | Operating Modes                     | .26 |

| 5     | OnCE/JTAG PORT                      | 28  |

| 5.1   | Signals                             | .28 |

| 5.2   | Debug Mode                          | .29 |

| 5.3   | Chip Status                         | .29 |

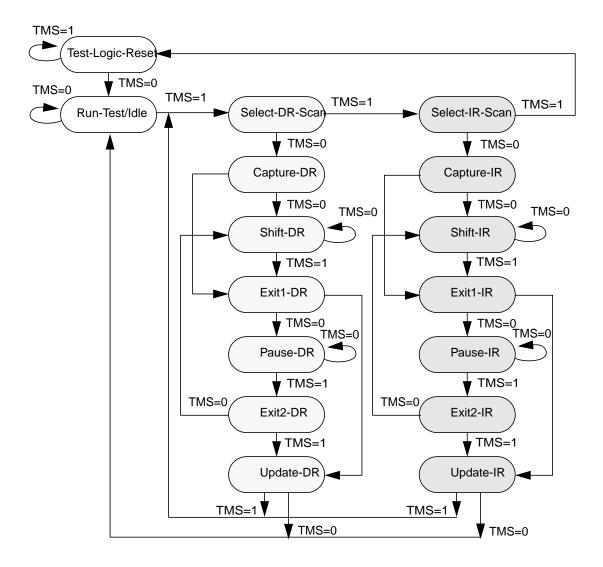

| 5.4   | TAP Controller State Machine        |     |

| 5.5   | OnCE Controller                     | .30 |

| 5.5.1 | OnCE Status and Control Register    | .30 |

| 5.5.2 | OnCE Memory Breakpoint Logic        |     |

| 5.5.3 | OnCE Pipeline                       |     |

## 1 Hardware Layout

The DSP56002 is available in the following package types:

- 144-pin plastic quad flat pack (PQFP)

- 144-pin thin quad flat pack (TQFP)

The DSP56303 is available in the following package types:

- 144-pin thin quad flat pack (TQFP)

- 196-pin plastic ball grid array (PBGA)

The 196-pin PBGA is strongly recommended for new DSP56303 designs. It is signal-pin compatible with future, higher-performance members of the DSP56300 family.

DSP56002-based designs require at least four  $0.1\mu F$  bypass capacitors positioned as closely as possible to the four sides of the package to connect the  $V_{CC}$  power source to GND. Refer to **Table 4**, *Differences Between the PLL of the DSP56002 and DSP56303*, on page 8 for the PLL capacitor value. DSP56303-based designs require at least six 0.01- $0.1\mu F$  bypass capacitors positioned as closely as possible to the four sides of the package to connect the  $V_{CC}$  power source to GND. Refer to **Table 4**, *Differences Between the PLL of the DSP56002 and DSP56303*, on page 8 for the PLL capacitor value.

The physical pinout of the DSP56002 differs from that of the DSP56303, so a direct replacement of the DSP is not possible. The board layout must be changed to reflect the differences in pinout. **Table 1** shows the signal names and pin numbers of the TQFP package, and **Table 2** shows the signal names and pin numbers of the PBGA package.

| Pin<br>No. | DSP56002<br>Signal Name      | DSP56303<br>Signal Name | Pin<br>No. | DSP56002<br>Signal<br>Name | DSP56303<br>Signal<br>Name | Pin<br>No. | DSP56002<br>Signal<br>Name | DSP56303<br>Signal<br>Name |

|------------|------------------------------|-------------------------|------------|----------------------------|----------------------------|------------|----------------------------|----------------------------|

| 1          | Not Connected (NC), reserved | SRD1/PD4                | 49         | SC0/PC3                    | NC, reserved               | 97         | A8                         | A15                        |

| 2          | D22                          | STD1/PD5                | 50         | V <sub>CCS</sub>           | AA3/RAS3                   | 98         | A9                         | A16                        |

| 3          | D23                          | SC02/PC2                | 51         | SCK/PC6                    | AA2/RAS2                   | 99         | GND <sub>A</sub>           | A17                        |

| 4          | MODC/NMI                     | SC01/PC1                | 52         | SC2/PC5                    | CAS                        | 100        | A10                        | D0                         |

| 5          | MODB/IRQB                    | DE                      | 53         | STD/PC8                    | XTAL                       | 101        | A11                        | D1                         |

| 6          | MODA/ĪRQA                    | PINIT/NMI               | 54         | GND <sub>S</sub>           | GND <sub>Q</sub>           | 102        | A12                        | D2                         |

| 7          | GND <sub>CK</sub>            | SRD0/PC4                | 55         | NC,<br>reserved            | EXTAL                      | 103        | V <sub>CCA</sub>           | V <sub>CCD</sub>           |

| 8          | CKOUT                        | V <sub>CCS</sub>        | 56         | SC1/PC4                    | V <sub>CCQ</sub>           | 104        | A13                        | GND <sub>D</sub>           |

| 9          | V <sub>CCCK</sub>            | GND <sub>S</sub>        | 57         | GND <sub>Q</sub>           | V <sub>CCC</sub>           | 105        | GND <sub>A</sub>           | D3                         |

| 10         | RESET                        | STD0/PC5                | 58         | V <sub>CCQ</sub>           | GND <sub>C</sub>           | 106        | A14                        | D4                         |

| 11         | CKP                          | SC10/PD0                | 59         | SRD/PC7                    | CLKOUT                     | 107        | A15                        | D5                         |

Table 1. DSP56002 and DSP56303 TQFP Pinout

Table 1. DSP56002 and DSP56303 TQFP Pinout (Continued)

| Pin<br>No. | DSP56002<br>Signal Name | DSP56303<br>Signal Name          | Pin<br>No. | DSP56002<br>Signal<br>Name | DSP56303<br>Signal<br>Name | Pin<br>No. | DSP56002<br>Signal<br>Name | DSP56303<br>Signal<br>Name |

|------------|-------------------------|----------------------------------|------------|----------------------------|----------------------------|------------|----------------------------|----------------------------|

| 12         | V <sub>CCP</sub>        | SC00/PC0                         | 60         | TIO                        | BCLK                       | 108        | NC,<br>reserved            | D6                         |

| 13         | PCAP                    | RXD/PE2                          | 61         | NC,<br>reserved            | BCLK                       | 109        | NC,<br>reserved            | D7                         |

| 14         | GND <sub>P</sub>        | TXD/PE1                          | 62         | BN                         | TA                         | 110        | D0                         | D8                         |

| 15         | PLOCK                   | SCLK/PE2                         | 63         | WT                         | BR                         | 111        | D1                         | V <sub>CCD</sub>           |

| 16         | PINIT                   | SCK1/PD3                         | 64         | BG                         | ВВ                         | 112        | GND <sub>D</sub>           | GND <sub>D</sub>           |

| 17         | XTAL                    | SCK0/PC3                         | 65         | BR                         | V <sub>CCC</sub>           | 113        | D2                         | D9                         |

| 18         | NC, reserved            | V <sub>CCQ</sub>                 | 66         | V <sub>CCC</sub>           | GND <sub>C</sub>           | 114        | D3                         | D10                        |

| 19         | EXTAL                   | GND <sub>Q</sub>                 | 67         | WR                         | WR                         | 115        | V <sub>CCD</sub>           | D11                        |

| 20         | V <sub>CCQ</sub>        | NC, reserved                     | 68         | RD                         | RD                         | 116        | D4                         | D12                        |

| 21         | GND <sub>Q</sub>        | HDS/HDS,<br>HWR/HWR,<br>PB12     | 69         | GND <sub>C</sub>           | AA1/RAS1                   | 117        | D5                         | D13                        |

| 22         | HA2/PB10                | HRW,<br>HRD/HRD,<br>PB11         | 70         | NC,<br>reserved            | AA0/RAS0                   | 118        | GND <sub>D</sub>           | D14                        |

| 23         | GND <sub>H</sub>        | HACK/HACK,<br>HRRQ/HRRQ,<br>PB15 | 71         | DSCK/OS1                   | BG                         | 119        | D6                         | V <sub>CCD</sub>           |

| 24         | HA1/PB9                 | HREQ/HREQ,<br>HTRQ/HTRQ,<br>PB14 | 72         | NC,<br>reserved            | A0                         | 120        | D7                         | GND <sub>D</sub>           |

| 25         | HA0/PB8                 | V <sub>CCS</sub>                 | 73         | NC,<br>reserved            | A1                         | 121        | D8                         | D15                        |

| 26         | HACK/PB14               | GND <sub>S</sub>                 | 74         | DR                         | V <sub>CCA</sub>           | 122        | D9                         | D16                        |

| 27         | V <sub>CCH</sub>        | TIO2                             | 75         | DSO                        | GND <sub>A</sub>           | 123        | V <sub>CCQ</sub>           | D17                        |

| 28         | HEN/PB12                | TIO1                             | 76         | DSI/OS0                    | A2                         | 124        | GND <sub>Q</sub>           | D18                        |

| 29         | GND <sub>H</sub>        | TIO0                             | 77         | BS                         | A3                         | 125        | GND <sub>D</sub>           | D19                        |

| 30         | HR/W/PB11               | HCS/HCS,<br>HA10,<br>PB13        | 78         | X/Y                        | A4                         | 126        | D10                        | V <sub>CCQ</sub>           |

| 31         | HREQ/PB13               | HA2,<br>HA9,<br>PB10             | 79         | GND <sub>A</sub>           | A5                         | 127        | NC,<br>reserved            | GND <sub>Q</sub>           |

| 32         | H7/PB7                  | HA1,<br>HA8,<br>PB9              | 80         | DS                         | V <sub>CCA</sub>           | 128        | D11                        | D20                        |

#### **Hardware Layout**

Table 1.

DSP56002 and DSP56303 TQFP Pinout (Continued)

| Pin<br>No. | DSP56002<br>Signal Name | DSP56303<br>Signal Name | Pin<br>No. | DSP56002<br>Signal<br>Name | DSP56303<br>Signal<br>Name | Pin<br>No. | DSP56002<br>Signal<br>Name | DSP56303<br>Signal<br>Name |

|------------|-------------------------|-------------------------|------------|----------------------------|----------------------------|------------|----------------------------|----------------------------|

| 33         | H6/PB6                  | HAO,<br>HAS/HAS,<br>PB8 | 81         | V <sub>CCA</sub>           | GND <sub>A</sub>           | 129        | V <sub>CCD</sub>           | V <sub>CCD</sub>           |

| 34         | GND <sub>H</sub>        | H7,<br>HAD7,<br>PB7     | 82         | PS                         | A6                         | 130        | D12                        | GND <sub>D</sub>           |

| 35         | H5/PB5                  | H6,<br>HAD6,<br>PB6     | 83         | A0                         | A7                         | 131        | D13                        | D21                        |

| 36         | NC                      | H5,<br>HAD5,<br>PB5     | 84         | A1                         | A8                         | 132        | GND <sub>D</sub>           | D22                        |

| 37         | NC, reserved            | H4,<br>HAD4,<br>PB4     | 85         | GND <sub>A</sub>           | A9                         | 133        | D14                        | D23                        |

| 38         | H4/PB4                  | V <sub>CCH</sub>        | 86         | A2                         | V <sub>CCA</sub>           | 134        | D15                        | MODD/<br>IRQD              |

| 39         | H3/PB3                  | GND <sub>H</sub>        | 87         | A3                         | GND <sub>A</sub>           | 135        | D16                        | MODC/<br>IRQC              |

| 40         | V <sub>CCH</sub>        | H3,<br>HAD3,<br>PB3     | 88         | A4                         | A10                        | 136        | D17                        | MODB/<br>IRQB              |

| 41         | H2/PB2                  | H2,<br>HAD2,<br>PB2     | 89         | GND <sub>S</sub>           | A11                        | 137        | GND <sub>D</sub>           | MODA/<br>ĪRQĀ              |

| 42         | GND <sub>H</sub>        | H1,<br>HAD1,<br>PB1     | 90         | GND <sub>Q</sub>           | $GND_Q$                    | 138        | D18                        | TRST                       |

| 43         | H1/PB1                  | H0,<br>HAD0,<br>PB0     | 91         | NC,<br>reserved            | V <sub>CCQ</sub>           | 139        | D19                        | TDO                        |

| 44         | H0/PB0                  | RESET                   | 92         | A5                         | A12                        | 140        | V <sub>CCD</sub>           | TDI                        |

| 45         | RXD/PC0                 | V <sub>CCP</sub>        | 93         | V <sub>CCA</sub>           | A13                        | 141        | D20                        | TCK                        |

| 46         | TXD/PC1                 | PCAP                    | 94         | GND <sub>A</sub>           | A14                        | 142        | D21                        | TMS                        |

| 47         | GND <sub>S</sub>        | GND <sub>P</sub>        | 95         | A6                         | V <sub>CCA</sub>           | 143        | GND <sub>D</sub>           | SC12/PD2                   |

| 48         | SCLK/PC2                | GND <sub>P1</sub>       | 96         | A7                         | GND <sub>A</sub>           | 144        | NC,<br>reserved            | SC11/PD1                   |

Table 2. DSP56303 PBGA Pinout

| Pin<br>No. | DSP56303<br>Signal Name | Pin<br>No. | DSP56303<br>Signal Name | Pin<br>No. | DSP56303 Signal<br>Name          | Pin<br>No. | DSP56303<br>Signal Name |

|------------|-------------------------|------------|-------------------------|------------|----------------------------------|------------|-------------------------|

| A1         | NC, reserved            | D8         | GND                     | H1         | NC, reserved                     | L8         | GND                     |

| A2         | SC11/PD1                | D9         | GND                     | H2         | V <sub>CCQ</sub>                 | L9         | GND                     |

| A3         | TMS                     | D10        | GND                     | НЗ         | SCK0/PC3                         | L10        | GND                     |

| A4         | TDO                     | D11        | GND                     | H4         | GND                              | L11        | GND                     |

| A5         | MODB/IRQB               | D12        | D1                      | H5         | GND                              | L12        | V <sub>CCA</sub>        |

| A6         | D23                     | D13        | D2                      | H6         | GND                              | L13        | A3                      |

| A7         | V <sub>CCD</sub>        | D14        | V <sub>CCD</sub>        | H7         | GND                              | L14        | A4                      |

| A8         | D19                     | E1         | STD0/PC5                | H8         | GND                              | M1         | HA1,<br>HA8,<br>PB9     |

| A9         | D16                     | E2         | V <sub>CCS</sub>        | H9         | GND                              | M2         | HA2,<br>HA9,<br>PB10    |

| A10        | D14                     | E3         | SRD0/PC4                | H10        | GND                              | М3         | HAO,<br>HAS/HAS,<br>PB8 |

| A11        | D11                     | E4         | GND                     | H11        | GND                              | M4         | V <sub>CCH</sub>        |

| A12        | D9                      | E5         | GND                     | H12        | V <sub>CCA</sub>                 | M5         | H0,<br>HAD0,<br>PB0     |

| A13        | D7                      | E6         | GND                     | H13        | A10                              | M6         | V <sub>CCP</sub>        |

| A14        | NC, reserved            | E7         | GND                     | H14        | A11                              | M7         | NC, reserved            |

| B1         | SRD1/PD4                | E8         | GND                     | J1         | HACK/HACK,<br>HRRQ/HRRQ,<br>PB15 | M8         | EXTAL                   |

| B2         | SC12/PD2                | E9         | GND                     | J2         | HRW,<br>HRD/HRD,<br>PB11         | M9         | CLKOUT                  |

| В3         | TDI                     | E10        | GND                     | J3         | HDS/HDS,<br>HWR/HWR,<br>PB12     | M10        | BCLK                    |

| B4         | TRST                    | E11        | GND                     | J4         | GND                              | M11        | WR                      |

| B5         | MODD/IRQD               | E12        | A17                     | J5         | GND                              | M12        | RD                      |

| В6         | D21                     | E13        | A16                     | J6         | GND                              | M13        | A1                      |

| B7         | D20                     | E14        | D0                      | J7         | GND                              | M14        | A2                      |

| B8         | D17                     | F1         | RXD/PE0                 | J8         | GND                              | N1         | H6,<br>HAD6,<br>PB6     |

| В9         | D15                     | F2         | SC10/PD0                | J9         | GND                              | N2         | H7,<br>HAD7,<br>PB7     |

Table 2.

DSP56303 PBGA Pinout (Continued)

| Pin<br>No. | DSP56303<br>Signal Name | Pin<br>No. | DSP56303<br>Signal Name | Pin<br>No. | DSP56303 Signal<br>Name          | Pin<br>No. | DSP56303<br>Signal Name |

|------------|-------------------------|------------|-------------------------|------------|----------------------------------|------------|-------------------------|

| B10        | D13                     | F3         | SC00/PC0                | J10        | GND                              | N3         | H4,<br>HAD4,<br>PB4     |

| B11        | D10                     | F4         | GND                     | J11        | GND                              | N4         | H2,<br>HAD2,<br>PB2     |

| B12        | D8                      | F5         | GND                     | J12        | A8                               | N5         | RESET                   |

| B13        | D5                      | F6         | GND                     | J13        | A7                               | N6         | GND <sub>P</sub>        |

| B14        | NC, reserved            | F7         | GND                     | J14        | A9                               | N7         | AA3/RAS3                |

| C1         | SC02/PC2                | F8         | GND                     | K1         | V <sub>CCS</sub>                 | N8         | CAS                     |

| C2         | STD1/PD5                | F9         | GND                     | K2         | HREQ/HREQ,<br>HTRQ/HTRQ,<br>PB14 | N9         | V <sub>CCQ</sub>        |

| C3         | TCK                     | F10        | GND                     | K3         | TIO2                             | N10        | BCLK                    |

| C4         | MODA/IRQA               | F11        | GND                     | K4         | GND                              | N11        | BR                      |

| C5         | MODB/IRQB               | F12        | V <sub>CCA</sub>        | K5         | GND                              | N12        | V <sub>CCC</sub>        |

| C6         | D22                     | F13        | A14                     | K6         | GND                              | N13        | AA0/RAS0                |

| C7         | V <sub>CCQ</sub>        | F14        | A15                     | K7         | GND                              | N14        | A0                      |

| C8         | D18                     | G1         | SCK1/PD3                | K8         | GND                              | P1         | NC, reserved            |

| C9         | V <sub>CCD</sub>        | G2         | SCLK/PE2                | K9         | GND                              | P2         | H5,<br>HAD5,<br>PB5     |

| C10        | D12                     | G3         | TXD/PE1                 | K10        | GND                              | P3         | H3,<br>HAD3,<br>PB3     |

| C11        | V <sub>CCD</sub>        | G4         | GND                     | K11        | GND                              | P4         | H1,<br>HAD1,<br>PB1     |

| C12        | D6                      | G5         | GND                     | K12        | V <sub>CCA</sub>                 | P5         | PCAP                    |

| C13        | D3                      | G6         | GND                     | K13        | A5                               | P6         | GND <sub>P1</sub>       |

| C14        | D4                      | G7         | GND                     | K14        | A6                               | P7         | AA2/RAS2                |

| D1         | PINIT/NMI               | G8         | GND                     | L1         | HCS/HCS,<br>HA10,<br>PB13        | P8         | XTAL                    |

| D2         | SC01/PC1                | G9         | GND                     | L2         | TIO1                             | P9         | V <sub>CCC</sub>        |

| D3         | DE                      | G10        | GND                     | L3         | TIO0                             | P10        | TA                      |

| D4         | GND                     | G11        | GND                     | L4         | GND                              | P11        | BB                      |

| D5         | GND                     | G12        | A13                     | L5         | GND                              | P12        | AA1/RAS1                |

| D6         | GND                     | G13        | V <sub>CCQ</sub>        | L6         | GND                              | P13        | BG                      |

| D7         | GND                     | G14        | A12                     | L7         | GND                              | P14        | NC, reserved            |

## 2 Core

The DSP56300 core can execute an instruction on every clock cycle, thus yielding a twofold performance increase (at the same clock rate) as compared to the DSP56000 core, while maintaining object code compatibility. For example, a DSP56002 running at 40 MHz can deliver 20 million instructions per second (MIPS), while a DSP56303 running at 40 MHz can deliver 40 MIPS. In addition to the performance increase inherent in the "1X" architecture of the DSP56300 core, devices in this family can operate at much greater clock rates than those of the DSP56000 family devices. This section compares the core characteristics of the DSP56002 and the DSP5603 in terms of power supply, electrical characteristics, phase locked-loop (PLL), DMA controller, memory, instruction cache, and other core features.

### 2.1 Power Supply

The DSP56002 requires a supply voltage ( $V_{CC}$ ) of 5V. The DSP56303 requires a  $V_{CC}$  of 3.3V. For easier migration to DSP56300 derivatives using Motorola's High-Performance (HiP4) process technology, a split power supply design for the core and I/Os is recommended. For example, the DSP56311 uses split power supplies to separate the I/O and peripheral sections, which operate at 3.3V, from the processor core, which runs at 1.8V.

#### 2.2 Electrical Characteristics

**Table 3** shows the differences in electrical characteristics between the DSP56002 and the DSP56303.

| Characteristics     | DSP56002                                                         |                                                       | DSP5                                                          | 66303                                                         |

|---------------------|------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|

|                     | MIN                                                              | MAX                                                   | MIN                                                           | MAX                                                           |

| Input High Voltage  | 4.0V (Note 1)<br>2.5V (Note 2)<br>3.5V (Note 3)<br>2.0V (Note 4) | V <sub>CC</sub><br>V <sub>CC</sub><br>V <sub>CC</sub> | 2.0V (Note 5)<br>2.0V (Note 6)<br>0.8V <sub>CC</sub> (Note 1) | V <sub>CC</sub><br>V <sub>CC</sub> +3.95V<br>V <sub>CC</sub>  |

| Input Low Voltage   | -0.5V<br>-0.5V<br>-0.5V                                          | 0.6V (Note 1)<br>2.0V (Note 3)<br>0.8V (Note 4)       | -0.3V<br>-0.3V<br>-0.3V                                       | 0.8V (Note 7)<br>0.8V (Note 8)<br>0.2V <sub>CC</sub> (Note 1) |

| Output High Voltage | 2.4V                                                             |                                                       | V <sub>CC</sub> -0.4V (TTL)<br>V <sub>CC</sub> -0.01V (CMOS)  |                                                               |

| Output Low Voltage  |                                                                  | 0.4V                                                  |                                                               | 0.4V (TTL)<br>0.01V (CMOS)                                    |

Table 3. DSP56002 and DSP56303 Electrical Characteristics

- NOTES: 1. EXTAL

- 2. RESET

- MODA/MODB/MODC

- 4. All other inputs

- 5. D[0–23], BG, BB, TA

- 6. MOD/IRQ, RESET, PINIT/NMI, JTAG, ESSI, SCI, Timer, HI08

- 7. D[0-23], BG, BB, TA, MOD/IRQ, RESET, PINIT/NMI

- 8. JTAG, ESSI, SCI, Timer, HI08

## 2.3 Phase-Locked Loop (PLL)

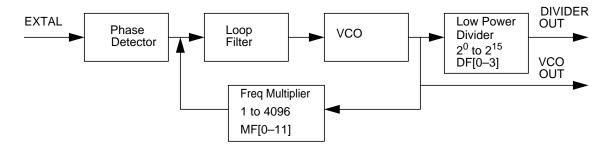

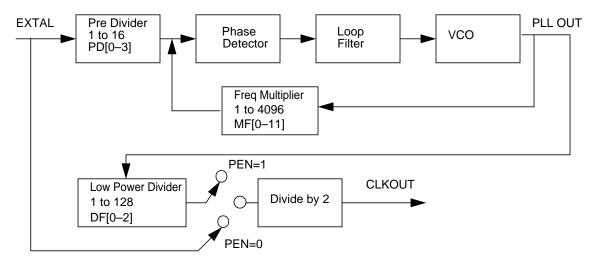

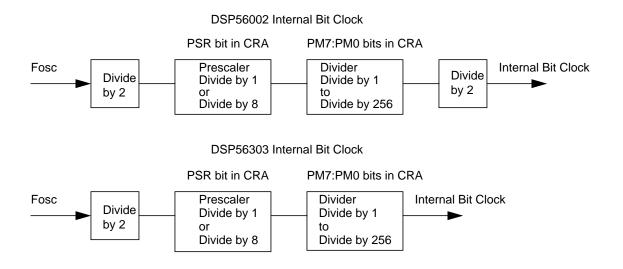

There are several key differences in the PLL of the DSP56002 and the DSP56303. To help you understand these differences, **Figure 1** shows the DSP56002 and DSP56300 PLL block diagrams. **Table 4** compares the different PLL elements shown in the block diagrams.

#### **DSP56002 PLL Block Diagram**

#### **DSP56303 PLL Block Diagram**

Figure 1. PLL Block Diagrams

Table 4. Differences Between the PLL of the DSP56002 and DSP56303

| DSP56002                            | DSP56303                                                                                                                                                                                                                                                       |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency Pre-divider Not Available | A <b>frequency pre-divider</b> is available on the DSP56303. This programmable division factor applies to the PLL input frequency and ranges from 1 to 16. The pre-divider factor bits PD[0–3] are written into bits 20–23 of the PLL Control Register (PCTL). |

| Fixed Divide by 2 Not Available     | In the DSP56300 core, the output of the voltage-controlled oscillator (VCO) is <b>divided by 2</b> . This results in a constant x2 multiplication of the PLL clock output that generates the special chip clock phases.                                        |

Table 4.

Differences Between the PLL of the DSP56002 and DSP56303

| DSP56002                                                                                                                                                                                                    | DSP56303                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The <b>low power divider</b> divides the output frequency of the VCO by any power of 2 from 2 <sup>0</sup> to 2 <sup>15</sup> . The division factor bits DF[0–3] are written into bits 12–15 of the PCTL.   | The clock generator performs the low power division. The <b>low power divider</b> divides the output frequency of the PLL by any power of 2 from 2 <sup>0</sup> to 2 <sup>7</sup> . The division factor bits DF[0–2] are written into PCTL bits 12–14.                                                                                                                                                          |

| The <b>operating frequency</b> is governed by the frequency control bits in the PCTL as follows:                                                                                                            | The <b>operating frequency</b> is governed by the frequency control bits in the PCTL, as follows:                                                                                                                                                                                                                                                                                                               |

| $F_{002} = F_{EXT} \times MF / DF = F_{VCO} / DF$                                                                                                                                                           | $F_{303} = F_{EXT} \times MF / (PDF \times DF) = F_{VCO} / DF$                                                                                                                                                                                                                                                                                                                                                  |

| When the PLL is disabled, the internal chip clock and CKOUT are driven from the EXTAL input.                                                                                                                | where: $F_{CHIP} \text{ is the chip operating frequency.}$ $F_{EXT} \text{ is the external input frequency to the chip at the EXTAL pin.}$ $MF \text{ is the multiplication factor defined by the MF[0-11] bits.}$ $DF \text{ is the division factor defined by the DF[0-3] bits.}$ $PDF \text{ is the pre-division factor defined by the PD[0-3] bits.}$ $F_{VCO} \text{ is the output frequency of the VCO.}$ |

|                                                                                                                                                                                                             | When the PLL is disabled, the frequency of the CLKOUT is half the EXTAL input.                                                                                                                                                                                                                                                                                                                                  |

| PLL Filter Capacitor The recommended PCAP value is 400 pF for a multiplication factor of MF <= 4 and 540 pF for a multiplication factor of MF > 4. For example, if a 40 MHz crystal is used and the desired | PLL Filter Capacitor The recommended PCAP value is (500*MF-150) pF for a multiplication factor of MF <= 4 and (690*MF) pF for a multiplication factor of MF > 4.                                                                                                                                                                                                                                                |

| operating frequency is 40 MHz, the MF factor is: $F_{002} = F_{\text{EXT}} \times \text{MF / DF} = 40 \text{ MHz} = 40 \text{ MHz} * \text{MF}$                                                             | For example, if a 16.9344 MHz crystal is used and the desired operating frequency is 68 MHz, the MF factor is:                                                                                                                                                                                                                                                                                                  |

| MF is 1. The PCAP value should be 400 pF, since MF <= 1.                                                                                                                                                    | F <sub>303</sub> = F <sub>EXT</sub> * MF / (PDF * DF) = 68 MHz = 16.9344 MHz * MF                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                             | MF is approximately 4. The PCAP value should be (500 * 4 - 150) pF = 1850 pF, since MF <= 4.                                                                                                                                                                                                                                                                                                                    |

| PLL Pins The Phase and Frequency Lock (PLOCK) pin is asserted when the PLL is enabled and has locked on the proper phase and frequency of EXTAL.                                                            | PLL Pins PLOCK and CKP pins Not available                                                                                                                                                                                                                                                                                                                                                                       |

| The Clock Output Polarity Control (CKP) pin is an input that defines the polarity of the CKOUT clock output.                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                 |

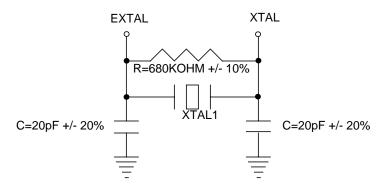

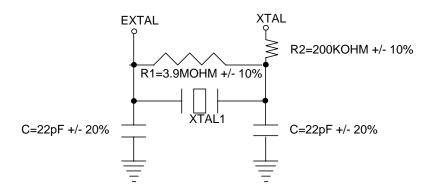

**Figure 2** and **Figure 3** show the recommended connection and component values for the DSP56002 and DSP56303, respectively, if the system clock derives from the on-chip crystal oscillator.

Figure 2. DSP56002 Fundamental Frequency Crystal Oscillator Circuit

Figure 3. DSP56303 Fundamental Frequency Crystal Oscillator Circuit

#### 2.4 DMA Controller

A key difference between the DSP56002 and the DSP56303 is that a DMA controller is available on the DSP56300 core. The DMA permits data transfers between internal/external memory and/or internal/external I/O independently of core operation. The DMA controller has six channels, each with its own register set. Data transfer for one channel requires a minimum of two clock cycles per single word. **Table 5** shows the various types of DMA data transfers available.

| Source          | Destination     | Clock Cycles per Single<br>Word Transfer |

|-----------------|-----------------|------------------------------------------|

| Internal Memory | Internal Memory | 2                                        |

| Internal Memory | External Memory | 2 + wait states                          |

| Internal Memory | Internal I/O    | 2                                        |

| External Memory | Internal Memory | 2 + wait states                          |

Table 5. DSP56300 DMA Controller Data Transfers

| Source          | Destination     | Clock Cycles per Single<br>Word Transfer |

|-----------------|-----------------|------------------------------------------|

| External Memory | External Memory | 2 + wait states                          |

| External Memory | Internal I/O    | 2 + wait states                          |

| Internal I/O    | Internal Memory | 2                                        |

| Internal I/O    | External Memory | 2 + wait states                          |

| Internal I/O    | Internal I/O    | 2                                        |

Table 5.

DSP56300 DMA Controller Data Transfers (Continued)

The DMA supports various types of address generation schemes, such as:

- Constant addressing:

- The address remains unchanged throughout the data transfer.

- Uni-dimensional addressing:

One block is transferred using consecutive addresses.

- Two-dimensional addressing:

Equally-spaced blocks are transferred using consecutive addresses within each block. The spacing between the blocks is programmed into an offset register.

- Three-dimensional addressing: Equally-spaced groups of equally-spaced blocks are transferred using consecutive addresses within each block. The two spacings are programmed into two offset registers.

### 2.5 Memory

**Table 6** compares the on-chip memory for the DSP56002 and the DSP56303. In DSP56300 derivatives using the HiP4 process technology, the internal memory block size is 1024 x 24-bit words compared to 256 x 24-bit words in Motorola's Communication Design Rules (CDR) process technology derivatives.

DSP56002 DSP56303 (words) (words) I-Cache Switch I-Cache Х **RAM** RAM RAM On/Off Mode **RAM** RAM **RAM** 512 Off Off 4 K 2 K 0 256 256 2 K Off 3 K 2 K 2 K 1 K On Off On 2 K 3 K 3 K 0 Off Off 1 K 3 K 3 K 1 K Р Χ Υ Р Χ **ROM ROM** ROM **ROM ROM ROM** 64 256 256 192

Table 6.On-Chip Memory

The DSP56002 PROM contains the bootstrap program, and the XROM and YROM contain sine, A-law, and mu-law tables. In contrast, the DSP56303 PROM contains the bootstrap program; XROM or YROM contain no data. You can program the DSP56303 PRAM, XRAM, YRAM, and instruction cache sizes by changing the values of the following bits:

- Cache Enable (CE) bit in the Status Register (SR): When the instruction cache is enabled, the lowest 1K of program words are allocated to the instruction cache.

- Memory Switch (MS) bit in the Operating Mode Register (OMR): When the memory switch mode is set, XRAM and YRAM can be reallocated as PRAM.

**Table 7** shows the off-chip memory expansion for each device.

| Memory Space | DSP56002 (words) | DSP56303 (words)                              |

|--------------|------------------|-----------------------------------------------|

| PRAM         | 64 K             | 16 M in 24-bit mode or<br>64 K in 16-bit mode |

| XRAM         | 64 K             | 16 M in 24-bit mode or<br>64 K in 16-bit mode |

| YRAM         | 64 K             | 16 M in 24-bit mode or<br>64 K in 16-bit mode |

Table 7. Off-Chip Memory Expansion

#### 2.6 Instruction Cache Controller

An instruction cache controller is present on the DSP56300 core but not on the DSP5600 core. This cache acts as buffer memory between the main memory and the CPU, storing instruction sequences that execute frequently. An increase in throughput results when instruction words that a program needs are available in the on-chip cache, eliminating the time required to access them on the external bus.

### 2.7 Address Space Selection

Address space is selected differently on the DSP56002 than on the DSP56303. In the DSP56002, the Program Memory Select ( $\overline{PS}$ ) signal is a program memory chip select signal that enables the program memory. The Data Memory Select ( $\overline{DS}$ ) signal enables two data memories, and the X/ $\overline{Y}$  Select (X/Y) signal selects X or Y data memory space. The three external memory spaces (program, X data, and Y data) do not have to reside in separate physical memories. A single memory suffices if the  $\overline{PS}$ ,  $\overline{DS}$ , and X/ $\overline{Y}$  signals are used as additional address lines to segment the memory into three spaces. **Table 8** shows how these signals are decoded.

| PS | DS | X/Y | External Memory References |

|----|----|-----|----------------------------|

| 1  | 1  | 1   | No Activity                |

| 1  | 0  | 1   | X Data Memory on Data Bus  |

| 1  | 0  | 0   | Y Data Memory on Data Bus  |

| 0  | 1  | 1   | Program Memory on Data Bus |

Table 8. DSP56002 Program and Data Memory Select Encoding

In the DSP56303, the Address Attribute AA[3–0] signals can function as chip selects or as additional address lines. By default, only one AA signal can be asserted at a time. However, when the OMR AA Priority Disable (APD) bit is set, the AA lines are used together as four external lines externally decoded into 16 chip select signals. The AA pin is asserted if the address in the appropriate Address Attribute Register AAR[3–0] matches the external address and if the external access is aimed to a space that is enabled in the appropriate AAR register. <sup>1</sup>

# 3 Mode Control and Interrupts

This section compares how the DSP56002 and DSP56303 operating modes are controlled. It also compares the ways that interrupts are addressed, sourced, and prioritized.

### 3.1 Operating Modes

When the DSP56002 leaves the reset state, it samples the mode MOD[C-A] signal lines and loads their values into the MC, MB, and MA bits in the OMR to set the initial operating mode. **Table 9** shows the DSP56002 operating modes.

| Operating Mode | МС | МВ | MA | Description          |

|----------------|----|----|----|----------------------|

| 0              | 0  | 0  | 0  | Single-Chip mode     |

| 1              | 0  | 0  | 1  | Bootstrap from EPROM |

| 2              | 0  | 1  | 0  | Normal Expanded mode |

| 3              | 0  | 1  | 1  | Development mode     |

| 5              | 1  | 0  | 1  | Bootstrap from host  |

| 6              | 1  | 1  | 0  | Bootstrap from SCI   |

Table 9. DSP56002 Operating Modes

When the DSP56303 leaves the reset state, it samples the mode MOD[D-A] signal lines and loads their values into the MD, MC, MB, and MA bits in the OMR to set the initial operating mode. **Table 10** shows the DSP56303 operating modes. For a complete description of the various modes, refer to the *DSP56303 User's Manual*.

| Label 101 201 occord operating measure |        |    |    |    |                                 |

|----------------------------------------|--------|----|----|----|---------------------------------|

| Operating Mode                         | MD     | МС | МВ | MA | Description                     |

| 0                                      | 0      | 0  | 0  | 0  | Expanded mode                   |

| 1                                      | 0 or 1 | 0  | 0  | 1  | Bootstrap from byte-wide memory |

| 2                                      | 0 or 1 | 0  | 1  | 0  | Bootstrap from SCI              |

| 4                                      | 0 or 1 | 1  | 0  | 0  | HI08 bootstrap in ISA/DSP5630x  |

Table 10. DSP56303 Operating Modes

<sup>1.</sup> Specified by the Address to Compare BAC[11–0] bits and the Number of Address Bits to Compare BNC[3–0].

Table 10. DSP56303 Operating Modes

| Operating Mode | MD     | МС | МВ | MA | Description                            |

|----------------|--------|----|----|----|----------------------------------------|

| 5              | 0 or 1 | 1  | 0  | 1  | HI08 bootstrap in HC11 non-multiplexed |

| 6              | 0 or 1 | 1  | 1  | 0  | HI08 bootstrap in 8051 multiplexed Bus |

| 7              | 0 or 1 | 1  | 1  | 1  | HI08 bootstrap in 68302 bus            |

| 8              | 1      | 0  | 0  | 0  | Expanded mode                          |

## 3.2 Interrupt Addresses and Sources

The Vector Base Address (VBA) register is available on the DSP56300 core and not on the DSP5600 core. The VBA is a 24-bit read/write register used as a base address of the interrupt vector and interrupt vector+1. Bits 7–0 are read-only and are always cleared. The VBA is referenced implicitly by interrupt processing or directly via the MOVEC instruction. **Table 11** shows the interrupt starting addresses and the interrupt priority level ranges for each interrupt source of both the DSP56002 (for which there is no VBA) and the DSP56303.

Table 11.

Interrupt Starting Addresses and Sources

|                                  | DSP                                     | 56002                                    |                               | DSP56303                          |                         |

|----------------------------------|-----------------------------------------|------------------------------------------|-------------------------------|-----------------------------------|-------------------------|

| Interrupt<br>Starting<br>Address | Interrupt<br>Priority<br>Level<br>Range | Interrupt Source                         | Interrupt<br>Starting Address | Interrupt Priority<br>Level Range | Interrupt Source        |

| \$00                             | 3                                       | Hardware RESET                           | VBA:\$00                      | 3                                 | Hardware RESET          |

| \$02                             | 3                                       | Stack Error                              | VBA:\$02                      | 3                                 | Stack Error             |

| \$04                             | 3                                       | Trace                                    | VBA:\$04                      | 3                                 | Illegal Instruction     |

| \$06                             | 3                                       | SWI                                      | VBA:\$06                      | 3                                 | Debug Request Interrupt |

| \$08                             | 0–2                                     | IRQA                                     | VBA:\$08                      | 3                                 | Trap                    |

| \$0A                             | 0–2                                     | IRQB                                     | VBA:\$0A                      | 3                                 | Non-Maskable Interrupt  |

| \$0C                             | 0–2                                     | SSI Receive Data                         | VBA:\$0C                      | 3                                 | Reserved                |

| \$0E                             | 0–2                                     | SSI Receive Data w/<br>Exception Status  | VBA:\$0E                      | 3                                 | Reserved                |

| \$10                             | 0–2                                     | SSI Transmit Data                        | VBA:\$10                      | 0–2                               | IRQA                    |

| \$12                             | 0–2                                     | SSI Transmit Data w/<br>Exception Status | VBA:\$12                      | 0–2                               | IRQB                    |

| \$14                             | 0–2                                     | SCI Receive Data                         | VBA:\$14                      | 0–2                               | IRQC                    |

| \$16                             | 0–2                                     | SCI Receive Data w/<br>Exception Status  | VBA:\$16                      | 0–2                               | IRQD                    |

| \$18                             | 0–2                                     | SCI Transmit Data                        | VBA:\$18                      | 0–2                               | DMA Channel 0           |

| \$1A                             | 0–2                                     | SCI Idle Line                            | VBA:\$1A                      | 0–2                               | DMA Channel 1           |

| \$1C                             | 0–2                                     | SCI Timer                                | VBA:\$1C                      | 0–2                               | DMA Channel 2           |

Table 11. Interrupt Starting Addresses and Sources (Continued)

|                                  | DSP                                     | 56002                         |                               | DSP56303                          |                                            |

|----------------------------------|-----------------------------------------|-------------------------------|-------------------------------|-----------------------------------|--------------------------------------------|

| Interrupt<br>Starting<br>Address | Interrupt<br>Priority<br>Level<br>Range | Interrupt Source              | Interrupt<br>Starting Address | Interrupt Priority<br>Level Range | Interrupt Source                           |

| \$1E                             | 3                                       | Non-Maskable Interrupt        | VBA:\$1E                      | 3                                 | DMA Channel 3                              |

| \$20                             | 0–2                                     | Host Receive Data             | VBA:\$20                      | 0–2                               | DMA Channel 4                              |

| \$22                             | 0–2                                     | Host Transmit Data            | VBA:\$22                      | 0–2                               | DMA Channel 5                              |

| \$24                             | 0–2                                     | Host Command                  | VBA:\$24                      | 0–2                               | TIMER 0 Compare                            |

| \$26                             | 0–2                                     | Available for Host<br>Command | VBA:\$26                      | 0–2                               | TIMER 0 Overflow                           |

| \$28                             | 0–2                                     | Available for Host<br>Command | VBA:\$28                      | 0–2                               | TIMER 1 Compare                            |

| \$2A                             | 0–2                                     | Available for Host<br>Command | VBA:\$2A                      | 0–2                               | TIMER 1 Overflow                           |

| \$2C                             | 0–2                                     | Available for Host<br>Command | VBA:\$2C                      | 0–2                               | TIMER 2 Compare                            |

| \$2E                             | 0–2                                     | Available for Host<br>Command | VBA:\$2E                      | 0–2                               | TIMER 2 Overflow                           |

| \$30                             | 0–2                                     | Available for Host<br>Command | VBA:\$30                      | 0–2                               | ESSI0 Receive Data                         |

| \$32                             | 0–2                                     | Available for Host<br>Command | VBA:\$32                      | 0–2                               | ESSI0 Receive Data w/<br>Exception Status  |

| \$34                             | 0–2                                     | Available for Host<br>Command | VBA:\$34                      | 0–2                               | ESSI0 Receive Last Slot                    |

| \$36                             | 0–2                                     | Available for Host<br>Command | VBA:\$36                      | 0–2                               | ESSI0 Transmit Data                        |

| \$38                             | 0–2                                     | Available for Host<br>Command | VBA:\$38                      | 0–2                               | ESSI0 Transmit Data w/<br>Exception Status |

| \$3A                             | 0–2                                     | Available for Host<br>Command | VBA:\$3A                      | 0–2                               | ESSI0 Transmit Last Slot                   |

| \$3C                             | 0–2                                     | Timer                         | VBA:\$3C                      | 0–2                               | Reserved                                   |

| \$3E                             | 3                                       | Illegal Instruction           | VBA:\$3E                      | 0–2                               | Reserved                                   |

| \$40                             | 0–2                                     | Available for Host<br>Command | VBA:\$40                      | 0–2                               | ESSI1 Receive Data                         |

| \$42                             | 0–2                                     | Available for Host<br>Command | VBA:\$42                      | 0–2                               | ESSI1 Receive Data w/<br>Exception Status  |

| \$44                             | 0–2                                     | Available for Host<br>Command | VBA:\$44                      | 0–2                               | ESSI1 Receive Last Slot                    |

| \$46                             | 0–2                                     | Available for Host<br>Command | VBA:\$46                      | 0–2                               | ESSI1 Transmit Data                        |

#### **Mode Control and Interrupts**

Table 11.

Interrupt Starting Addresses and Sources (Continued)

|                                  | DSP                                     | 56002                         |                               | DSP56303                          |                                            |

|----------------------------------|-----------------------------------------|-------------------------------|-------------------------------|-----------------------------------|--------------------------------------------|

| Interrupt<br>Starting<br>Address | Interrupt<br>Priority<br>Level<br>Range | Interrupt Source              | Interrupt<br>Starting Address | Interrupt Priority<br>Level Range | Interrupt Source                           |

| \$48                             | 0–2                                     | Available for Host<br>Command | VBA:\$48                      | 0–2                               | ESSI1 Transmit Data w/<br>Exception Status |

| \$4A                             | 0–2                                     | Available for Host<br>Command | VBA:\$4A                      | 0–2                               | ESSI1 Transmit Last Slot                   |

| \$4C                             | 0–2                                     | Available for Host<br>Command | VBA:\$4C                      | 0–2                               | Reserved                                   |

| 4E                               | 0–2                                     | Available for Host<br>Command | VBA:4E                        | 0–2                               | Reserved                                   |

| \$50                             | 0–2                                     | Available for Host<br>Command | VBA:\$50                      | 0–2                               | SCI Receive Data                           |

| \$52                             | 0–2                                     | Available for Host<br>Command | VBA:\$52                      | 0–2                               | SCI Receive Data w/<br>Exception Status    |

| \$54                             | 0–2                                     | Available for Host<br>Command | VBA:\$54                      | 0–2                               | SCI Transmit Data                          |

| \$56                             | 0–2                                     | Available for Host<br>Command | VBA:\$56                      | 0–2                               | SCI Idle Line                              |

| \$58                             | 0–2                                     | Available for Host<br>Command | VBA:\$58                      | 0–2                               | SCI Timer                                  |

| \$5A                             | 0–2                                     | Available for Host<br>Command | VBA:\$5A                      | 0–2                               | Reserved                                   |

| \$5C                             | 0–2                                     | Available for Host<br>Command | VBA:\$5C                      | 0–2                               | Reserved                                   |

| \$5E                             | 0–2                                     | Available for Host<br>Command | VBA:\$5E                      | 0–2                               | Reserved                                   |

| \$60                             | 0–2                                     | Available for Host<br>Command | VBA:\$60                      | 0–2                               | Host Receive Data Full                     |

| \$62                             | 0–2                                     | Available for Host<br>Command | VBA:\$62                      | 0–2                               | Host Transmit Data<br>Empty                |

| \$64                             | 0–2                                     | Available for Host<br>Command | VBA:\$64                      | 0–2                               | Host Command                               |

| \$66                             | 0–2                                     | Available for Host<br>Command | VBA:\$66                      | 0–2                               | Reserved                                   |

| :                                | :                                       | :                             | :                             | :                                 | :                                          |

| \$7E                             | 0–2                                     | Available for Host<br>Command | VBA:\$7E                      | :                                 | :                                          |

| :                                |                                         |                               | :                             | :                                 | :                                          |

| \$FE                             |                                         |                               | VBA:\$FE                      | 0–2                               | Reserved                                   |

### 3.3 Interrupt Priority Register

You can program interrupt priority levels for each on-chip peripheral device and for each external interrupt source under software control by writing to the interrupt priority register. Level 3 interrupts are non-maskable and have the highest priority; level 0 interrupts are maskable and have the lowest priority. **Table 12** shows the DSP56002 Interrupt Priority Register (IPR) configuration.

| Bit No. |          | Bit Description                |

|---------|----------|--------------------------------|

| 23–18   | Reserved | Read as zero                   |

| 17–16   | TIL[1-0] | Timer Interrupt Priority Level |

| 15–14   | SCL[1-0] | SCI Interrupt Priority Level   |

| 13–12   | SSL[1-0] | SSI Interrupt Priority Level   |

| 11–10   | HPL0     | Host Interrupt Priority Level  |

| 9–6     | Reserved | Read as zero                   |

| 5–3     | IBL[2-0] | IRQB Mode                      |

| 2–0     | IAL[2-0] | IRQA Mode                      |

Table 12. DSP56002 Interrupt Priority Register

The DSP56303 has two interrupt priority registers. The IPR-C is dedicated to the DSP56300 core interrupt sources, and the IPR-P is dedicated to the DSP56303 peripherals. **Table 13** and **Table 14** show the bits of each interrupt priority register.

Bit No. **Bit Name** 23-22 D5L[1-0] **DMA5 Interrupt Priority Level** 21-20 D4L[1-0] DMA4 Interrupt Priority Level 19-18 D3L[1-0] **DMA3 Interrupt Priority Level** 17-16 D2L[1-0] **DMA2 Interrupt Priority Level** D1L[1-0] **DMA1 Interrupt Priority Level** 15-14 D0L[1-0] 13-12 **DMA0 Interrupt Priority Level** 11-9 IDL[2-0] **IRQD** Mode 8-6 ICL[2-0] **IRQC** Mode IBL[2-0] **IRQB** Mode 5-3 2-0 IAL[2-0] **IRQA** Mode

Table 13. DSP56303 Interrupt Priority Register C

#### **Mode Control and Interrupts**

Table 14.

DSP56303 Interrupt Priority Register P

| Bit No. | Bit Name  |                                       |  |

|---------|-----------|---------------------------------------|--|

| 23–10   | Reserved  | Read as zero                          |  |

| 9–8     | T0L1-T0L0 | Triple Timer Interrupt Priority Level |  |

| 7–6     | SCL1-SCL0 | SCI Interrupt Priority Level          |  |

| 5–4     | S1L1-S1L0 | ESSI1 Interrupt Priority Level        |  |

| 3–2     | S0L1-S0L0 | ESSI0 Interrupt Priority Level        |  |

| 1–0     | HPL1-HPL0 | HI08 Interrupt Priority Level         |  |

## 4 Peripherals

The DSP56002 and DSP56303 peripherals compared in this section are the host interface, Enhanced Synchronous Serial Interface (SCI), triple timer, and the OnCE/JTAG port.

#### 4.1 Host Interface

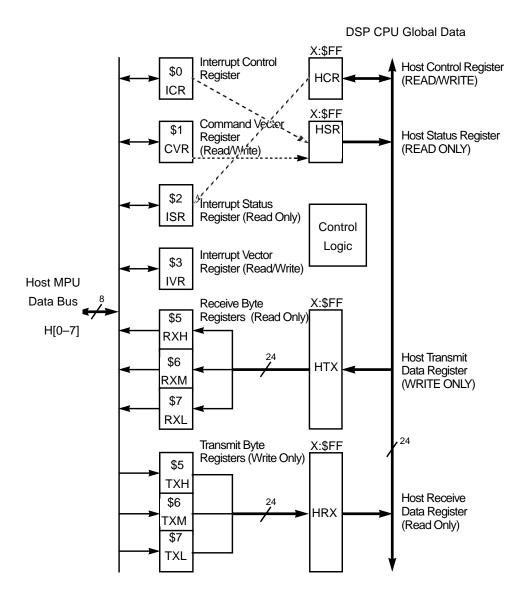

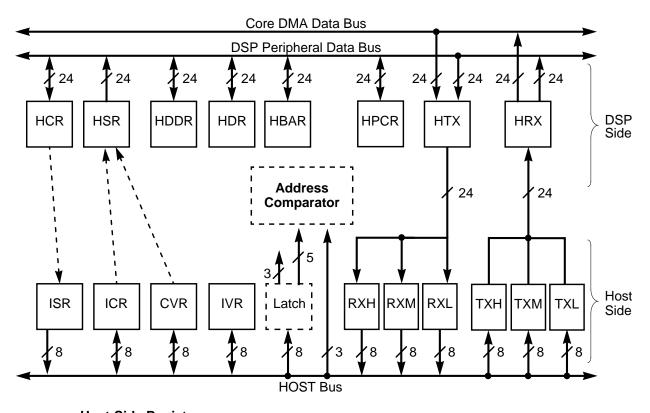

The DSP56002 host interface supports only non-multiplexed buses, single-strobe buses, and single host request bus modes. The DSP56303 HI08 host port supports non-multiplexed or multiplexed buses, single-or dual-strobe buses, and single- or double- host request bus modes. The discussion that follows refers to several DSP56002 and DSP56303 registers and to bits in those registers. To provide a context for this discussion, **Figure 4** and **Figure 5** show the DSP56002 and DSP56303 host block diagrams, respectively.

Figure 4. DSP56002 Host Block Diagram

#### **DSP-Side Registers**

#### **Control Registers**

HCR = Host Control Register

HSR = Host Status Register

HPCR = Host Port Control Register

HBAR = Host Base Address Register

#### **Data Registers**

HTX = Host Transmit Register HRX = Host Receive Register HDDR = Host Data Direction Register

HDR = Host Data Register

#### **Host-Side Registers**

#### **Control Registers**

ISR = Interface Status Register ICR = Interface Control Register CVR = Command Vector Register IVR = Interrupt Vector Register

#### **Data Registers**

RXH = Receive Register High RXM = Receive Register Middle RXL = Receive Register Low TXH = Transmit Register High TXM = Transmit Register Middle TXL = Transmit Register Low

Figure 5. HI08 Block Diagram

#### 4.1.1 Multiplexed Address/Data and Non-Multiplexed Bus Modes

In the DSP56002, the host data bus signals H[7–0] transfer data between the host processor and the DSP56002. The host address signals HA[2–0] provide the address selection for each host interface register. In the DSP56303, the HI08 connects to a multiplexed bus when the Host Multiplexed Bus (HMUX) bit in the Host Port Control Register (HPCR) is set. The HI08 employs the following signals (see **Table 15**):

- The Host Address/Data HAD[7–0] signals are lines 7–0 of the address/data bidirectional, multiplexed bus.

- The HAS/HAS signal is the Host Address Strobe input.

- The Host Address HA[10–8] signals are lines 10–8 of the Host Address input bus.

When the HPCR[HMUX] bit is cleared, the HI08 connects to a non-multiplexed bus (see **Table 15**):

- The values of the address lines are taken from the HI08 input pins.

- The Host Data H[7–0] signals are lines 7–0 of the data bidirectional bus.

- The Host Address Inputs HA[2–0] signals are lines 2–0 of the Host Address input bus.

- The HCS/HCS signal is the Host Chip Select input.

**Table 15.** HI08 Pin Definitions for Multiplexed/Non-Multiplexed Bus Modes

| HI08 Signal | MUltiplexed Address/Data Bus Mode<br>HMUX=1 in HPCR | Non-Multiplexed Bus Mode<br>HMUX=0 in HPCR |

|-------------|-----------------------------------------------------|--------------------------------------------|

| HAD[7-0]    | HAD[7-0]                                            | H[7–0]                                     |

| HAS/HA0     | HAS/HAS                                             | HA0                                        |

| HA8/HA1     | HA8                                                 | HA1                                        |

| HA9/HA2     | НА9                                                 | HA2                                        |

| HCS/HA10    | HA10                                                | HCS/HCS                                    |

In the multiplexed bus mode, the Host Base Address Register (HBAR) selects the base address in which the host-side registers are mapped into the bus address space. The address from the host bus is compared with the address as programmed in the HBAR. If the addresses match, an internal chip select is generated. As **Table 16** shows, the Base Address bits, BA[10–3], reflect the base address in which the host-side registers map into the bus address space.

**Table 16.** DSP56303 Host Base Address Register (HBAR)

| Bit No. | Bit Description |              |  |  |

|---------|-----------------|--------------|--|--|

| 15–8    | Reserved        | Read as zero |  |  |

| 7–0     | BA[10-3]        | Base Address |  |  |

### 4.1.2 Single/Dual Data Strobe Bus Modes

In the DSP56002, the host port operates in single-strobe bus mode. The Host Read/Write (HR/W) input signal selects the direction of data transfer for each host processor access:

- If HR/W is high and the Host Enable (HEN) pin is asserted, H[7–0] are outputs and DSP data transfers to the host processor.

- If  $HR/\overline{W}$  is low and the HEN pin is asserted, H[7-0] are inputs and host data transfers to the DSP.

In the DSP56303, the HI08 operates in the single-strobe bus mode when the Host Dual Data Strobe (HDDS) bit in the HPCR is cleared. The bus has a single data strobe signal for both read and write operations. The HDS/HDS signal qualifies the access, while the HRW signal specifies the direction of the access (see **Table 17**).

- When the HPCR[HDDS] bit is set, the HI08 operates in the dual data strobe bus mode. The bus has two separate data strobes, one for data reads (HRD/HRD) and the other for data writes (HWR/HWR).

- When the Host Data Strobe Polarity (HDSP) bit in the HPCR is cleared, the data strobe pin is configured as an active low input, and the data transfers when the data strobe is low.

- When HPCR[HDSP] is set, the data strobe pin is configured as an active high input, and the data transfers when the data strobe is high.

| HI08 Signal | Single-Strobe Bus<br>HDDS=0 in HPCR | Dual-Strobe Bus<br>HDDS=1 in HPCR |

|-------------|-------------------------------------|-----------------------------------|

| HRW/HRD     | HRW                                 | HRD/HRD                           |

| HDS/HWR     | HDS/HDS                             | HWR/HWR                           |

**Table 17.** HI08 Pin Definitions for Single- and Dual-Data Strobe Bus Modes

### 4.1.3 Single/Double Host Request Bus Modes

The DSP56002 supports the single-host request bus. The host interface uses the Host Request  $\overline{\text{HREQ}}$  signal to request service from the host processor. In the DSP56303, the single-host request bus is selected when the Double-Host Request (HDRQ) bit in the Interface Control Register (ICR) is cleared. The HREQ/HTRQ and HACK/HRRQ signal pins are configured as the Host Request ( $\overline{\text{HREQ}}$ ) and the Host Acknowledge ( $\overline{\text{HACK}}$ ), respectively (see **Table 18**).

The HREQ pin is asserted when:

- The Receive Request Enable (RREQ) bit in the ICR is set and the Receive Data Register Full (RXDF) status bit in the Interface Status Register (ISR) is set.

- The Transmit Request Enable (TREQ) bit in the ICR is set and the Transmit Data Register Empty (TXDE) status bit in the (ISR) is set.

When the HDRQ bit is set, the double host request bus is selected. The HREQ/HTRQ and HACK/HRRQ signal pins are configured as the Transmit Host Request HTRQ and Receive Host Request HRRQ, respectively. When the ICR[RREQ] bit is set and the ISR[RXDF] status bit is set, the HRRQ pin is asserted. When the ICR[TREQ] bit is set and the ISR[TXDE] status bit is set, the HTRQ pin is asserted.

HI08 Signal

Single-Host Request Bus

HDRQ=0 in ICR

HREQ/HTRQ

HACK/HRRQ

HACK/HRRQ

HACK/HRRQ

HACK/HRRQ

HI08 Signal

Double-Host Request Bus

HDRQ=1 in ICR

HTRQ

HTRQ

HTRQ

Table 18. HI08 Pin Definitions for Single and Double Host Request Bus Modes

#### 4.1.4 Big-Endian/Little-Endian Byte Order

The host can access the DSP56002 host port in little-endian byte order. The Receive/Transmit Register High (RXH/TXH) is located at address \$5, the Receive/Transmit Register Middle (RXM/TXM) is located at address \$6, and the Receive/Transmit Register Low (RXL/TXL) is located at address \$7.

The DSP56303 host port supports both big-endian and little-endian byte order. If the Host Little-Endian (HLEND) bit in the ICR is cleared, the HI08 can be accessed in little-endian byte order. If ICR[HLEND] is set, the HI08 can be accessed in big-endian byte order, where RXH/TXH is located at address \$7, RXM/TXM is located at address \$6, and RXL/TXL is located at address \$5 (see **Table 19**).

| Host Address | DSP56002 | DSP56303                 |                       | Registers         |

|--------------|----------|--------------------------|-----------------------|-------------------|

|              |          | Little Endian<br>HLEND=0 | Big Endian<br>HLEND=1 |                   |

| \$0          | ICR      | ICR                      | ICR                   | Interface Control |

| \$1          | CVR      | CVR                      | CVR                   | Command Vector    |

| \$2          | ISR      | ISR                      | ISR                   | Interface Status  |

| \$3          | IVR      | IVR                      | IVR                   | Interrupt Vector  |

| \$4          |          |                          |                       | Unused            |

| \$5          | RXH/TXH  | RXH/TXH                  | RXL/TXL               | Receive/Transmit  |

| \$6          | RXM/TXM  | RXM/TXM                  | RXM/TXM               | Bytes             |

| \$7          | RXL/TXL  | RXL/TXL                  | RXH/TXH               |                   |

Table 19. Host-Side Register Map

### 4.1.5 Host Registers

The DSP56002 and DSP56303 host control and host status registers are as follows:

- Host Control Register (HCR): In the DSP56002, the HCR is an 8-bit read/write control register by which the DSP controls the host interface interrupts and flags. In the DSP56303, the HCR is a 16-bit control register.

- Host Status Register (HSR): In the DSP56002, the HSR is an 8-bit read-only status register by which the DSP interrogates status and flags of the host interface. In the DSP56303, the HSR is a 16-bit read-only status register.

### 4.2 Enhanced Synchronous Serial Interface

The DSP56303 has two independent and identical Enhanced Synchronous Serial Interfaces: ESSI0 and ESSI1. The ESSI enhances the Synchronous Serial Interface (SSI) of the DSP56000 family with network, audio, and general improvements.

#### 4.2.1 Network Enhancements

ESSI network enhancements include time slot registers, the end-of-frame interrupt, and the drive enable signal.

#### 4.2.1.1 ESSI Time Slot Registers

The Transmit Slot Mask Registers (TSMA and TSMB) and the Receive Slot Mask Registers (RSMA and RSMB) reside on the DSP56303 but not on the DSP56002. TSMA and TSMB are accessible as a single 32-bit register with bits TS[31–0]. Bit n is an enable/disable control bit for transmission in slot number N. When TSn is cleared, all the transmit data registers of the enabled transmitters are tri-stated during transmit time slot number N. The data still transfers from the enabled Transmit Data Register(s) to the Transmit Shift Register, but the Transmit Data Empty (TDE) and the Transmit Underrun Error (TUE) flags in the SSI Status Register (SSISRx) are not set. During a disabled slot, no transmitter empty interrupt is generated. The DSP is interrupted only for the enabled slots. Data written to the Transmit Data Register when the transmitter empty interrupt request is serviced is transmitted in the next enabled transmit time slot. When TSn is set, data is transferred from the transmit register to the shift register during slot number N and the TDE flag is set.