DP84600R/DP84605R Thin-Film/MIG Head Read/Write Preamplifie

# DP84600R/DP84605R Thin-Film/MIG Head Read/Write Preamplifier

#### **General Description**

The DP84600R/DP84605R are 5V, high performance, four channel, low power, read preamplifiers/write current drivers designed for two-terminal recording head applications. An idle mode is available which conserves power to a level of 0.5 mW (typically) when activated. Power supply fault protection is included to disable the write current generator whenever the supply voltage is below 4V. Both parts incorporate  $300\Omega$  write damping.

The DP84600R has a read gain of 300 versus 200 for the DP84605R.

Upon request, other options such as other read gains, PECL inputs, no damping, and different packaging are available.

#### **Features**

- Low input capacitance: 12 pF typical

- Low input noise: 0.49 nV/√Hz typical

- Low power: 100 mW typical in read mode

- Very low idle power: 0.5 mW typical

- Programmable write current source (1 mA-40 mA)

- Low power supply protection in write mode

- Head short to ground protection

- Plug compatible to VTC VM7204/7104/7114

- Single 5V power supply

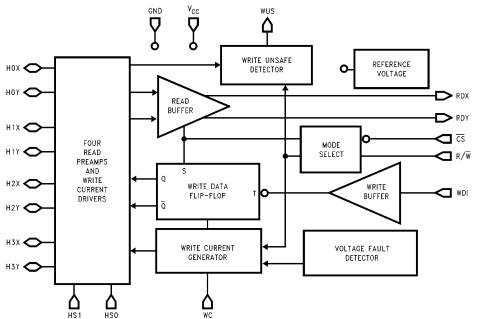

#### **Block Diagram**

FIGURE 1. Circuit Block Diagram

TL/F/11990-1

This Preliminary document contains information on a product under development. Specifications contained within are based on design targets or a limited amount of data and are subject to change without notice. National Semiconductor reserves the right to change or discontinue this product without notice.

| TABLE I. Pin Descriptions       |              |                                                                                                                                                                                                       |  |  |  |  |  |

|---------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name                        | Pin Type     | Pin Function Description                                                                                                                                                                              |  |  |  |  |  |

| V <sub>CC</sub>                 | Power Supply | Power supply Pin (5V $\pm$ 10%). These pins (10 and 13) are internally shorted.                                                                                                                       |  |  |  |  |  |

| WDI                             | Input (TTL)  | Each negative transition on WDI toggles the head current between the X and Y head connections.                                                                                                        |  |  |  |  |  |

| HS0, HS1                        | Input (TTL)  | Logic levels are applied to these pins to select 1 of 4 heads (see Table II).                                                                                                                         |  |  |  |  |  |

| R/W                             | Input (TTL)  | A logic high level selects the read mode while a low logic level selects the write mode. The $\overline{\text{CS}}$ pin must be at a low logic level for this operation to be active (see Table III). |  |  |  |  |  |

| CS                              | Input (TTL)  | A high logic level disables the operation of the device and puts the read data outputs (RDX, RDY) into a high impedance state.                                                                        |  |  |  |  |  |

| H0X, H0Y<br>through<br>H3X, H3Y | Outputs      | X and Y connections to the read/write heads.                                                                                                                                                          |  |  |  |  |  |

| WUS                             | Output       | A logic high level at this pin indicates that one of several conditions has been detected by internal circuitry which makes writing unsafe.                                                           |  |  |  |  |  |

| RDX, RDY                        | Output       | Differential read data outputs.                                                                                                                                                                       |  |  |  |  |  |

| WC                              | Output       | A resistor is connected from this pin to ground to control the magnitude of the write current (see formula in Write Mode description).                                                                |  |  |  |  |  |

| GND                             | Ground       | Device ground.                                                                                                                                                                                        |  |  |  |  |  |

#### **Connection Diagram**

TL/F/11990-

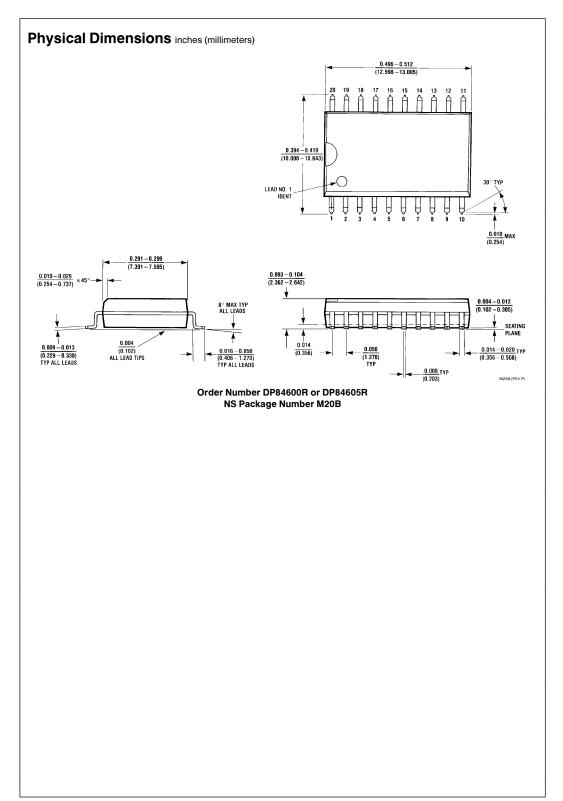

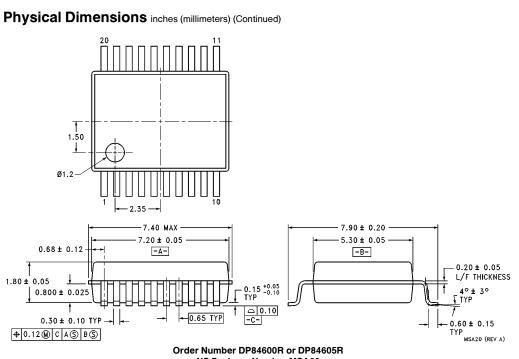

Order Number DP84600R or DP84605R See NS Package Number M20B or MSA20

FIGURE 2. Connection Diagram

#### **Basic Circuit Operation**

The DP84600R/DP84605R can address up to four two-terminal thin-film heads, providing the write current drive in the write mode or read data amplification in the read mode.

Head selection is controlled by the logic states on two pins, HEAD SELECT 0 (HS0) and HEAD SELECT 1 (HS1). Table II defines the results of each combination of these two pins. These pins have internal pull-down current so that head 0 is selected if an open condition exists on these pins.

**TABLE II. Head Selection**

| HS1 | HS0 | Head Selected |

|-----|-----|---------------|

| 0   | 0   | 0             |

| 0   | 1   | 1             |

| 1   | 0   | 2             |

| 1   | 1   | 3             |

The selection of device mode (write, read or idle) is also controlled by two pins,  $\overline{\text{CHIP SELECT}}$  ( $\overline{\text{CS}}$ ) and  $\overline{\text{READ/WRITE}}$  ( $\overline{\text{R/W}}$ ). Table III defines the results of each combination of these two pins. These pins have internal pull-up resistors so that the idle condition is selected if an open condition exists on these pins.

**TABLE III. Mode Selection**

| CS | R/W    | Mode Selected |  |  |

|----|--------|---------------|--|--|

| 0  | 0      | Write         |  |  |

| 0  | 1      | Read          |  |  |

| 1  | 0      | Idle          |  |  |

| 1  | 1 Idle |               |  |  |

#### **Write Mode**

The write mode is entered by setting both  $\overline{\text{CS}}$  and R/W to logical low values. In the write mode, the device acts as a current switch which toggles between the X and Y sides of the selected head on each high-to-low logic level transition of the WRITE DATA INPUT (WDI). When entering the write mode from the read mode, the write data flip-flop is initialized to pass current into the X side of the selected head. The magnitude of the write current is set by an external resistor, RWRITE connected between the WC pin and ground. The relationship between the write current and the write resistor is:

$$I_{WRITE} = A_{WC} \times \frac{V_{WC}}{R_{WRITE}}$$

where  $A_{WC}$  is the current gain (see Write Mode DC Electrical Characteristics Table).

#### Write Mode (Continued)

The portion of the write current that passes through the head  $(I_{\text{h}})$  is defined as:

$$I_h = \frac{I_{WRITE}}{1 + R_h/R_d}$$

where:  $R_h =$ the sum of the head and external wire resistance

and  $R_d =$  the damping resistance (if any).  $R_d = \infty$  for no damping.

When entering the write mode, the write unsafe detector circuitry is enabled. This circuit issues a high level output at the WRITE UNSAFE (WUS) output when any of the following conditions exist:

- 1) Write data input frequency is too low.

- 2) The device is in the read mode.

- 3) The chip is disabled.

- 4) No write current exists.

- 5) The head is an open circuit.

The WUS pin is an open-collector output and requires an external pull-up resistor. After the fault condition has been removed, two negative transitions of the WDI pin are required to clear the write unsafe circuitry.

A power supply fault detection circuit is provided on chip. This circuit will disable the write current generator during device power-up, power-down or when a power supply fault occurs. This will prevent the possibility of writing bad data onto the media.

#### **Read Mode**

The read mode is entered by setting  $\overline{CS}$  to a low logic level and  $R/\overline{W}$  to a high logic level. In this mode the write current generator is disabled and a low noise differential amplifier is enabled. The amplified head read-back signal is available at the RDX and RDY pins. These outputs are differential emitter-followers and should be AC coupled to the load.

During the write or idle modes, the read amplifier is disabled and the RDX, RDY outputs are forced to a high impedance state. This allows these outputs to be wire-ORed with outputs from other devices to support multiple read/write applications.

#### **Idle Mode**

The idle mode is entered by applying a logical high level to the  $\overline{\text{CS}}$  pin. In this mode the RDX and RDY outputs are in a high impedance state and the device is disabled. This will reduce the power consumption to a mimmum value when the device is not needed, which is particularly important for battery applications

#### **Absolute Maximum Ratings** Operation beyond these limits may permanently damage the device.

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage ( $V_{CC}$ ) 7V

Digital Input Voltage -0.3V to ( $V_{CC}+0.3$ )V

Maximum Head Port Voltage -0.3V to ( $V_{CC}+0.3$ )V

Maximum Output Current (RDX, RDY) -10 mA

### Recommended Operating Conditions

|                                     | Min | Тур | Max | Units |

|-------------------------------------|-----|-----|-----|-------|

| Supply Voltage (V <sub>CC</sub> )   | 4.5 | 5   | 5.5 | V     |

| Operating Free Air                  | 0   |     | 70  | °C    |

| Temperature Range (T <sub>△</sub> ) |     |     |     |       |

#### **General DC Electrical Characteristics**

Guaranteed over recommended operating free air temperature and supply voltage range unless otherwise specified.

| Symbol               | Parameter                         | Conditions                                                          | Min  | Typ<br>(Note 1)             | Max                        | Units | Test   |

|----------------------|-----------------------------------|---------------------------------------------------------------------|------|-----------------------------|----------------------------|-------|--------|

| I <sub>CCR</sub>     | Supply Current<br>(Read Mode)     | $\overline{\text{CS}} = \text{L, R/W} = \text{H}$                   |      | 20                          | 28                         | mA    | Note A |

| I <sub>CCW</sub>     | Supply Current<br>(Write Mode)    | $\overline{\text{CS}} = R/\overline{W} = L$                         |      | 20 + 1.1 (I <sub>W</sub> )  | 27 + 1.1 (1 <sub>W</sub> ) | mA    | Note A |

| I <sub>CCI</sub>     | Supply Current<br>(Idle Mode)     | CS = H                                                              |      | 0.1                         | 0.27                       | mA    | Note A |

| PDR                  | Power Dissipation<br>(Read Mode)  | $\overline{\text{CS}} = \text{L, R/}\overline{\text{W}} = \text{H}$ |      | 100                         | 154                        | mW    | Note A |

| PDW                  | Power Dissipation<br>(Write Mode) | $\overline{\text{CS}} = \text{L, R/}\overline{\text{W}} = \text{L}$ |      | 100 + 5.5 (I <sub>W</sub> ) | 150 + 6 (I <sub>W</sub> )  | mW    | Note A |

| PDI                  | Power Dissipation<br>(Idle Mode)  | CS = H                                                              |      | 0.5                         | 1.5                        | mW    | Note A |

| V <sub>IH(TTL)</sub> | TTL Input High Voltage            |                                                                     | 2    |                             | V <sub>CC</sub> + 0.3      | ٧     | Note A |

| V <sub>IL(TTL)</sub> | TTL Input Low Voltage             |                                                                     | -0.3 |                             | 0.8                        | ٧     | Note A |

| I <sub>IH(TTL)</sub> | TTL Input High Current            |                                                                     | -100 |                             | 100                        | μΑ    | Note A |

| I <sub>IL(TTL)</sub> | TTL Input Low Current             |                                                                     | -100 |                             | 100                        | μΑ    | Note A |

Note 1: Typical values are specified at 25°C and 5V supply.

Note A: This parameter is guaranteed by outgoing testing.

## DC and AC Electrical Characteristics—Read Mode Guaranteed over recommended operating conditions (see table) unless otherwise specified. Read characteristics: $C_{L(RDX,\,RDY)} <$ 20 pF, $R_{L(RDX,\,RDY)} =$ 1 k $\Omega$

| Symbol              | Parameter                                      | Conditions                                                    | Min  | Typ<br>(Note 1)       | Max  | Units            | Test   |

|---------------------|------------------------------------------------|---------------------------------------------------------------|------|-----------------------|------|------------------|--------|

| A <sub>V</sub>      | Differential Voltage Gain<br>(Note 2)          | V <sub>IN</sub> = 1 mV <sub>PP</sub> @ 1 MHz<br>DP84600R Only | 25   | 300                   | 350  | V/V              | Note A |

| A <sub>V</sub>      | Differential Voltage Gain                      | V <sub>IN</sub> = 1 mV <sub>PP</sub> @1 MHz<br>DP84605R Only  | 160  | 200                   | 240  | V/V              | Note A |

| V <sub>N</sub>      | Input Noise Voltage                            | $BW = 15 \text{ MHz}, L_h = R_h = 0$                          |      | 0.49                  | 0.65 | nV/√Hz           | Note B |

| I <sub>N</sub>      | Input Noise Current                            |                                                               |      | 3                     |      | pA/√Hz           | Note B |

| C <sub>I</sub>      | Differential Input<br>Capacitance              | $V_{IN} = 1 \text{ mV}_{PP}, f = 5 \text{ MHz}$               |      | 12                    | 17   | pF               | Note B |

| R <sub>I</sub>      | Differential Input Resistance                  | $f = 5 \text{ MHz}, V_{IN} = 1 \text{ mV}_{PP}$               | 720  | 1250                  |      | Ω                | Note A |

| V <sub>IRANGE</sub> | Input Voltage Dynamic<br>Range                 | f = 5 MHz, (Note 3)                                           | 4    | 6                     |      | mV <sub>PP</sub> | Note A |

| V <sub>O(OFF)</sub> | Output Offset Voltage                          |                                                               | -150 |                       | 150  | mV               | Note A |

| R <sub>O(SE)</sub>  | Single Ended Output<br>Resistance              | f = 5 MHz                                                     |      |                       | 40   | Ω                | Note B |

| lout                | Output Current                                 | AC Coupled Load, RDX to RDY                                   | 1.5  | 2                     |      | mA               | Note A |

| V <sub>O(CM)</sub>  | Common Mode Output<br>Voltage at RDX, RDY Pins |                                                               | 2    | V <sub>CC</sub> - 2.4 | 3.5  | V                | Note A |

| BW <sub>1dB</sub>   | Voltage Bandwidth −1 dB                        | $V_{IN} = 1 \text{ mV}_{PP}, Z_{SOURCE} < 5\Omega$            | 40   | 60                    |      | MHz              | Note B |

| BW <sub>3dB</sub>   | Voltage Bandwidth −3 dB                        | $V_{IN} = 1 \text{ mV}_{PP}, Z_{SOURCE} < 5\Omega$            | 80   | 100                   |      | MHz              | Note B |

| CMMR                | Common Mode Rejection<br>Ratio                 | $V_{CM} = 100 \text{ mV}_{PP}, @5 \text{ MHz}$                | 60   | 90                    |      | dB               | Note A |

| PSRR                | Power Supply Rejection<br>Ratio                | $\Delta V_{CC} = 100 \text{ mV}_{PP}, @5 \text{ MHz}$         | 60   | 90                    |      | dB               | Note A |

| CSRR                | Channel Separation                             | Unselected Channel 100 mV <sub>PP</sub>                       | 50   | 60                    |      | dB               | Note A |

Note 1: Typical values are specified at 25°C and 5V supply.

Note 2: Various gain options exist from 160 to 300. See order information.

Note 3: The dynamic input voltage range limit is defined as the point where the gain falls to 90% of its small signal gain value.

Note A: This parameter is guaranteed by outgoing testing.

Note B: The limit values have been determined by characterization data. No outgoing tests are performed.

### DC Electrical Characteristics—Write Mode Guaranteed over recommended operating conditions (see table) unless otherwise specified. Write characteristics: $I_W=20$ mA, $L_h=1$ $\mu$ H, $R_h=30\Omega$

| Symbol               | Parameter                                         | Conditions                                    | Min  | Typ<br>(Note 1) | Max  | Units           | Test   |

|----------------------|---------------------------------------------------|-----------------------------------------------|------|-----------------|------|-----------------|--------|

| K <sub>W</sub>       | Write Current Constant                            | $K_W = A_{WC} \times V_{WC}$                  | 46   | 50              | 54   | ٧               | Note A |

| $A_{WC}$             | I <sub>WC</sub> to I <sub>HEAD</sub> Current Gain | $R_{H} = 40\Omega$                            | 18.4 | 20              | 21.6 | mA              | Note A |

| Інм                  | Write Current Matching                            | $I_{H}=$ 20 mA, $R_{H}=$ 40 $\Omega$ (Note 2) | -10  |                 | +10  | %               | Note A |

| $V_{WC}$             | Write Current Pin Voltage                         | 1 mA < I <sub>W</sub> < 40 mA                 | 2.3  | 2.5             | 2.7  | V               | Note A |

| $V_{H}$              | Differential Head Voltage Swing                   | Open Head, I <sub>W</sub> = 20 mA             | 5    | 6.5             |      | V <sub>PP</sub> | Note A |

| I <sub>H(NS)</sub>   | Unselected Head Current                           | I <sub>H</sub> = 20 mA                        |      |                 | 100  | μΑ              | Note A |

| R <sub>DAMP</sub>    | Damping Resistance                                | Write Only                                    |      | 300             |      | Ω               | Note A |

| I <sub>H</sub>       | Head Write Current Range                          |                                               | 1    |                 | 40   | mA              | Note A |

| V <sub>CCF</sub>     | V <sub>CC</sub> Shut-Off Voltage                  | I <sub>W</sub> < 0.2 mA                       | 3.6  |                 | 4.2  | V               | Note A |

| V <sub>OL(WUS)</sub> | WUS Low Output Voltage                            | $I_{OL} = 4 \text{ mA}$                       |      |                 | 0.5  | V               | Note A |

| I <sub>LK(WUS)</sub> | WUS High Level Output Leakage<br>Current          | $V_{OH} = V_{CC}$                             |      |                 | 100  | μΑ              | Note A |

| C <sub>D</sub>       | Differential Head Load<br>Capacitance             |                                               |      |                 | 15   | pF              | Note B |

| f <sub>W</sub>       | WDI Transition Frequency                          | For WUS = low                                 | 1    |                 |      | MHz             | Note A |

| t <sub>PWH(WD)</sub> | WDI Pulse Width (High)                            |                                               | 5    |                 |      | ns              | Note B |

| t <sub>PWL(WD)</sub> | WDI Pulse Width (Low)                             |                                               | 5    |                 |      | ns              | Note B |

Note 1: Typical values are specified at 25°C and 5V supply.

Note 2: Write curent matching applies between any two heads.

$<sup>\</sup>textbf{Note A:} \ \textbf{This parameter is guaranteed by outgoing testing}.$

Note B: The limit values have been determined by characterization data. No outgoing tests are performed.

#### **AC Electrical Characteristics**

Guaranteed over recommended operating conditions (see table) unless otherwise specified.  $I_W=20$  mA,  $L_h=1$   $\mu$ H,  $R_h=40\Omega$  and f(data) = 5 MHz unless otherwise specified.

| Symbol                    | Parameter                                                                | Conditions                                                                                      | Min | Typ<br>(Note 1) | Max  | Units | Test   |

|---------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----------------|------|-------|--------|

| td <sub>RW</sub>          | Time Delay Switching from Read to Write Modes                            | $R/\overline{W}$ Transition to 90% of Write Current. $I_W > 5$ mA                               |     |                 | 0.35 | μs    | Note A |

| td <sub>RWL</sub>         | Time Delay Switching from Read to Write Modes                            | $R/\overline{W}$ Transition to 90% $I_{WRITE}$ .<br>1 mA $<$ $I_{W}$ $<$ 5 mA                   |     |                 | 2    | μs    | Note A |

| td <sub>WR</sub>          | Time Delay Switching from Write to Read Modes                            | R/W Transition to 90% of 100 mV Read Signal Envelope                                            |     |                 | 1    | μs    | Note A |

| td <sub>SELECT</sub>      | Time Delay Switching from Idle to Either Read or Write Modes             | CS Negative Transition to<br>90% I <sub>WRITE</sub> or 90% of 100 mV,<br>10 MHz Signal Envelope |     |                 | 0.6  | μs    | Note A |

| td <sub>IDLE</sub>        | Time Delay Switching from Either<br>Read or Write to Idle Mode           |                                                                                                 |     |                 | 0.6  | μs    | Note A |

| td <sub>HEAD</sub>        | Time Delay Switching from One<br>Head to Another                         | HS0/HS1 to 90% of 100 mV,<br>10 MHz Read Signal Envelope                                        |     |                 | 0.6  | μs    | Note A |

| td <sub>UNSAFE</sub>      | Time Delay from a Write Safe to a<br>Write Unsafe Condition              | WDI Negative Transition to WUS Positive Transition                                              | 1   |                 | 3.6  | μs    | Note A |

| td <sub>SAFE</sub>        | Time Delay from Write Unsafe to<br>Write Safe Condition                  | WDI Negative Transition to WUS Negative Transition                                              |     |                 | 1    | μs    | Note A |

| td <sub>HDI</sub>         | Time Delay from WDI to a<br>Current Direction Change in a<br>Head Output | Measurements Made from 50% Points. $L_h = 0$ , $R_h = 40$                                       |     | 10              | 20   | ns    | Note A |

| ASY <sub>HD</sub>         | Head Current Asymmetry                                                   | WDI has 1 ns $t_{r/f}$ Times. $L_h = 0$ , $R_h = 40$                                            |     |                 | 0.5  | ns    | Note B |

| t <sub>r/f(HD)</sub>      | Head Current Rise and Fall<br>Times                                      |                                                                                                 |     |                 | 6    | ns    | Note B |

| t <sub>r</sub> /f(loaded) | Head Current Rise and Fall<br>Times                                      | Measurements Made from 10% to 90% Points. $L_h=1~\mu H,$ $R_h=40\Omega,$ $I_W=20$ mA            |     | 10              | 16   | ns    | Note B |

Note 1: Typical values are specified at 25°C and 5V supply.

Note A: This parameter is guaranteed by outgoing testing.

Note B: The limit values have been determined by characterization data. No outgoing tests are performed.

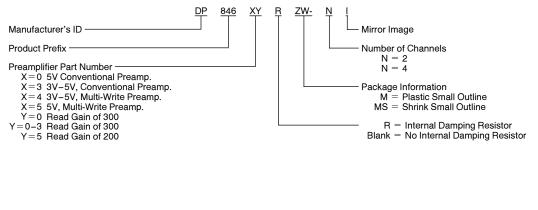

#### **Ordering Information**

### **NS Package Number MSA20**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 35 Italiano Tel: (+49) 0-180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon

Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408