DS90CP04 4x4 Low Power 2.5

**Gb/s LVDS Digital Cross-Point Switch**

# DS90CP04 4x4 Low Power 2.5 Gb/s LVDS Digital Cross-Point Switch

# **General Description**

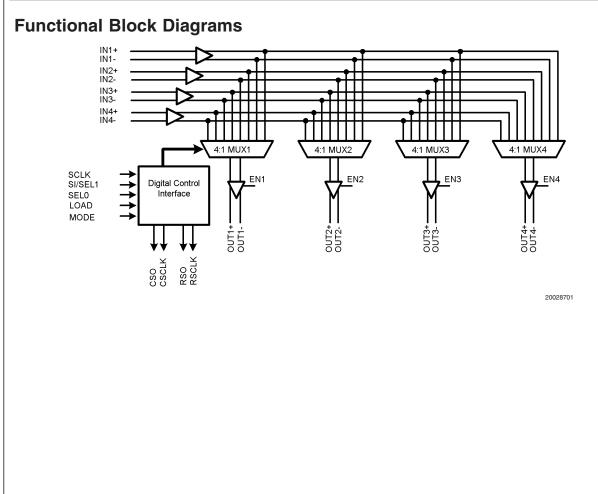

DS90CP04 is a 4x4 digital cross-point switch with broadside input and output pins for efficient board layout. It utilizes Low Voltage Differential Swing (LVDS) technology for low power, high-speed operation. Data paths are fully differential from input to output for low noise. The non-blocking architecture allows connections of any input to any output or outputs. The switch matrix consists of four differential 4:1 multiplexes. Each output channel connects to one of the four inputs common to all multiplexers. Each DS90CP04 output pair is capable of independent operation up to 2.5Gb/s.

A simple serial control interface or a configuration select port is activated by the state of the MODE pin. When utilizing the serial control interface a single load command will update the new switch configuration for all outputs simultaneously. When the direct configuration port is used, output configurations are updated immediately based on the decoded SEL0/1 logic state.

# Features

- 2.5 Gbps fully differential data paths

- Non-blocking architecture

- Broadcast from any input

- Broadside pin-out

- Possible expansion to larger switch array

- Accepts LVDS/BLVDS/LVPECL/2.5V-CML inputs

- TRI-STATE LVDS outputs

- Serial control interface with read-back capability

- Double register loading

- Single +2.5V supply

- Low power, 575 mW Typ at 2.5 Gb/s

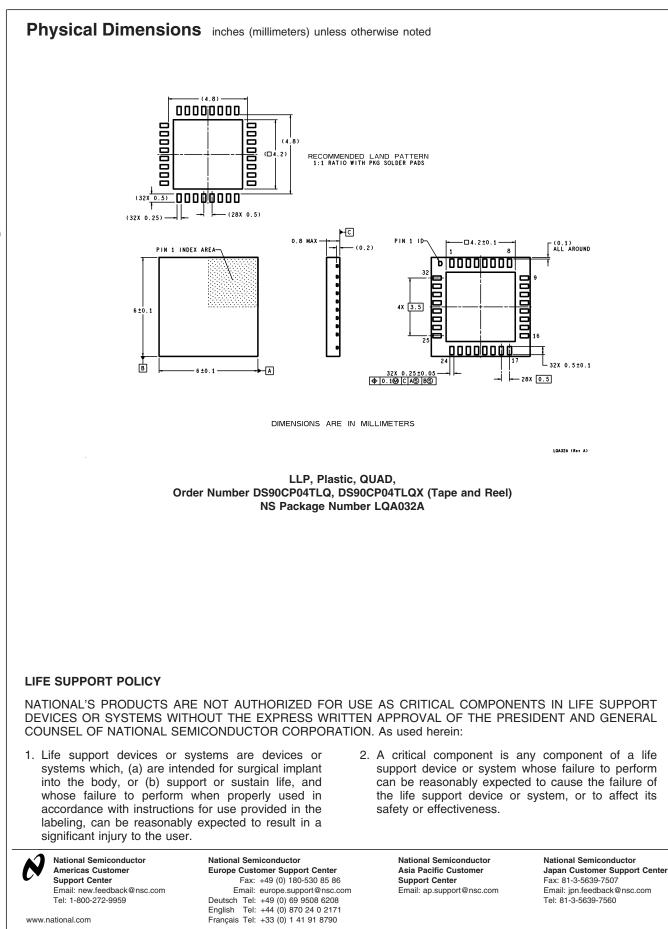

- Lead-less LLP-32 package 6x6 mm body size)

- Fabricated with advanced CMOS process technology

#### © 2003 National Semiconductor Corporation DS200287

#### inti D:

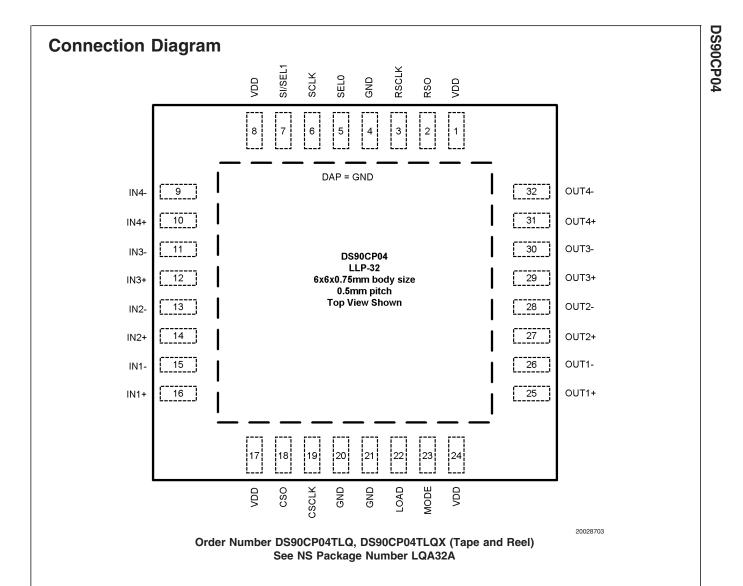

| Pin<br>Name     | Pin<br>Number     | I/O, Type     | Description                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | TIAL INPUTS       | COMMON TO ALL | MUXES                                                                                                                                                                                                                                                                                                                                                                 |

| IN1+            | 16                | I, LVDS       | Inverting and non-inverting differential inputs.                                                                                                                                                                                                                                                                                                                      |

| IN1–            | 15                |               |                                                                                                                                                                                                                                                                                                                                                                       |

| IN2+            | 14                | I, LVDS       | Inverting and non-inverting differential inputs.                                                                                                                                                                                                                                                                                                                      |

| IN2-            | 13                | .,            | ······································                                                                                                                                                                                                                                                                                                                                |

| IN3+            | 12                | I, LVDS       | Inverting and non-inverting differential inputs.                                                                                                                                                                                                                                                                                                                      |

| IN3–            | 11                | .,            | ······································                                                                                                                                                                                                                                                                                                                                |

| IN4+            | 10                | I, LVDS       | Inverting and non-inverting differential inputs.                                                                                                                                                                                                                                                                                                                      |

| IN4–            | 9                 | .,            |                                                                                                                                                                                                                                                                                                                                                                       |

|                 |                   | AL OUTPUTS    |                                                                                                                                                                                                                                                                                                                                                                       |

| OUT1+           | 25                | O, LVDS       | Inverting and non-inverting differential outputs. OUT1± can be connected to any                                                                                                                                                                                                                                                                                       |

| OUT1-           | 26                | 0, 2000       | one pair IN1±, IN2±, IN3±, or IN4±                                                                                                                                                                                                                                                                                                                                    |

| OUT2+           | 27                | O, LVDS       | Inverting and non-inverting differential outputs. OUT2± can be connected to any                                                                                                                                                                                                                                                                                       |

| OUT2+<br>OUT2-  | 27                | O, LVDS       |                                                                                                                                                                                                                                                                                                                                                                       |

|                 |                   | 0.11/00       | one pair IN1±, IN2±, IN3±, or IN4±                                                                                                                                                                                                                                                                                                                                    |

| OUT3+           | 29                | O, LVDS       | Inverting and non-inverting differential outputs. OUT3± can be connected to any                                                                                                                                                                                                                                                                                       |

| OUT3-           | 30                | 0.11/00       | one pair IN1±, IN2±, IN3±, or IN4                                                                                                                                                                                                                                                                                                                                     |

| OUT4+           | 31                | O, LVDS       | Inverting and non-inverting differential outputs. OUT4± can be connected to any                                                                                                                                                                                                                                                                                       |

| OUT4-           | 32                |               | one pair IN1±, IN2±, IN3±, or IN4±                                                                                                                                                                                                                                                                                                                                    |

|                 | ONTROL INT        |               |                                                                                                                                                                                                                                                                                                                                                                       |

| SCLK            | 6                 | I, LVCMOS     | Control clock to latch in programming data at SI. SCLK can be 0 MHz to<br>100 MHz. SCLK should be burst of clock pulses active only while accessing the<br>device. After completion of programming, SCLK should be kept at logic low to<br>minimize potential noise injection into the high-speed differential data paths.                                            |

| SI / SEL1       | 7                 | I, LVCMOS     | Programming data to select the switch configuration. Data is latched into the inpu buffer register at the rising edge of SCLK.                                                                                                                                                                                                                                        |

| SEL0            | 5                 | I, LVCMOS     | Programming data to select the switch configuration.                                                                                                                                                                                                                                                                                                                  |

| CSO             | 18                | O, LVCMOS     | With MODE low, control data is shifted out at CSO (RSO) for cascading to the                                                                                                                                                                                                                                                                                          |

| RSO             | 2                 |               | next device in the serial chain. The control data at CSO (RSO) is identical to that<br>shifted in at SI with the exception of the device column (row) address being<br>decremented by one internally before propagating to the next device in the chain.<br>CSO (RSO) is clocked out at the rising edge of SCLK.                                                      |

| CSCLK           | 19                | O, LVCMOS     | With MODE low, these pins function as a buffered control clock from SCLK.                                                                                                                                                                                                                                                                                             |

| RSCLK           | 3                 |               | CSCLK (RSCLK) is used for cascading the serial control bus to the next device ir the serial chain.                                                                                                                                                                                                                                                                    |

| LOAD            | 22                | I, LVCMOS     | When LOAD is high and SCLK makes a LH transition, the device transfers the programming data in the load register into the configuration registers. The new switch configuration for all outputs takes effect. LOAD needs to remain high for only one SCLK cycle to complete the process, holding LOAD high longer repeats the transfer to the configuration register. |

| MODE            | 23                | I, LVCMOS     | When MODE is low, the SCLK is active and a buffered SCLK signal is present at the CLKOUT output. When MODE is high, the SCLK signal is uncoupled from register and state machine internals. Internal registers will see an active low signa until MODE is brought Low again.                                                                                          |

| POWER           |                   |               |                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DD</sub> | 1, 8, 17,<br>24   | I, Power      | $V_{DD}$ = 2.5V ±5%. At least 4 low ESR 0.01 µF bypass capacitors should be connected from $V_{DD}$ to GND plane.                                                                                                                                                                                                                                                     |

| GND             | 4, 20, 21,<br>DAP | I, Power      | Ground reference to LVDS and CMOS circuitry.<br>DAP is the exposed metal contact at the bottom of the LPP-32 package. The DAI<br>is used as the primary GND connection to the device. It should be connected to<br>the ground plane with at least 4 vias for optimal AC and thermal performance.                                                                      |

| U |  |

|---|--|

| S |  |

| Q |  |

| 0 |  |

| 0 |  |

| τ |  |

| 0 |  |

| Ā |  |

# **Serial Interface Truth Table**

| LOAD | MODE | SCLK | Resulting Action                                                                      |  |  |  |

|------|------|------|---------------------------------------------------------------------------------------|--|--|--|

| 0    | 0    | LH   | The current state on SI is clocked into the input shift register.                     |  |  |  |

| 0    | 1    | LH   | Uncouples SCLK input from register and state machine internals. Internal registers    |  |  |  |

|      |      |      | will see and the RSCLK and CSCLK outputs will drive an active Low signal until        |  |  |  |

|      |      |      | MODE is brought Low again. See Configuration Select Truth Table below.                |  |  |  |

| LH   | 0    | X    | Loads OUT1-OUT4 configuration information from last valid frame. Places contents      |  |  |  |

|      |      |      | of load register into the configuration register. The switch configuration is updated |  |  |  |

|      |      |      | asynchronously from the SCLK input.                                                   |  |  |  |

| 1    | 1    | LH   | Uncouples SCLK input from register and state machine internals. Internal registers    |  |  |  |

|      |      |      | will see and the RSCLK and CSCLK outputs will drive an active Low signal until        |  |  |  |

|      |      |      | MODE is brought Low again. See Configuration Select Truth Table below.                |  |  |  |

# **Configuration Select Truth Table**

| MODE | SEL1 | SEL0 | Resulting Action                                                       |  |  |

|------|------|------|------------------------------------------------------------------------|--|--|

| 0    | Х    | Х    | The SEL0/1 pins only function in configuration select mode. See below. |  |  |

| 1    | 0    | 0    | Distribution: IN1 - OUT1 OUT2 OUT3 OUT4                                |  |  |

| 1    | 0    | 1    | Distribution: IN2 - OUT1 OUT2 OUT3 OUT4                                |  |  |

| 1    | 1    | 0    | Redundancy: IN1 - OUT1 OUT2 and IN3 - OUT3 OUT4                        |  |  |

| 1    | 1    | 1    | Broadside: IN1 - OUT1, IN2 - OUT2, IN3 - OUT3, IN4 - OUT4              |  |  |

LH: Low to High (positive edge) transition. X: Don't Care or Not Applicable.

#### Configuration Select Truth Table (Continued) SEL0 = 1 SEL0 = 0SEL1 = 1 SEL1 = 0 IN1+ OUT1+ IN1+ OUT1+ OUT1-IN1-OUT1-IN1-IN2+ OUT2+ OUT2+ IN2-OUT2-OUT2-IN3+ OUT3+ OUT3+ IN3-OUT3-OUT3-IN4+ OUT4+ OUT4+ IN4-OUT4-OUT4-SEL0 = 0SEL0 = 1 SEL1 = 1 SEL1 = 0 IN1+ OUT1+ OUT1+ IN1-OUT1-OUT1-IN2+ OUT2+ OUT2+ OUT2-IN2-OUT2-IN3+ OUT3+ OUT3+ IN3-OUT3-OUT3-OUT4+ OUT4+

FIGURE 1. DS90CP04 Configuration Select Decode

OUT4-20028704

OUT4-

DS90CP04

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>DD</sub> )   | -0.3V to +3V     |

|-------------------------------------|------------------|

| CMOS/TTL Input Voltage              | –0.3V to (V_{DD} |

|                                     | +0.3V)           |

| LVDS Receiver Input Voltage         | -0.3V to +3.3V   |

| LVDS Driver Output Voltage          | -0.3V to +3V     |

| LVDS Output Short Circuit Current   | 40mA             |

| Junction Temperature                | +150°C           |

| Storage Temperature                 | –65°C to +150°C  |

| Lead Temperature                    |                  |

| (Soldering, 4 sec.)                 | +260°C           |

| Maximum Package Power Dissipation a | t 25°C           |

| LLP-32                              | 3200 mW          |

| Derating above 25°C                 | 38 mW/°C         |

| Thermal Resistance, $\theta_{JA}$ | 26.4°C/W |

|-----------------------------------|----------|

| ESD Rating                        |          |

| HBM, 1.5 kΩ, 100 pF               |          |

| LVDS Outputs                      | >1.0 kV  |

| LVDS Inputs                       | >1.5 kV  |

| All Other Pins                    | >4.0 kV  |

| EIAJ, 0Ω, 200 pF                  | >100V    |

# Recommended Operating Conditions

|                                        | Min   | Тур | Max   | Unit |

|----------------------------------------|-------|-----|-------|------|

| Supply Voltage (V <sub>DD</sub> - GND) | 2.375 | 2.5 | 2.625 | V    |

| Receiver Input Voltage                 | 0.05  |     | 3.3   | V    |

| Operating Free Air                     |       |     |       |      |

| Temperature                            | -40   | 25  | 85    | °C   |

| Junction Temperature                   |       |     | 110   | °C   |

# **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless other specified.

| Symbol            | Parameter                         | Conditions                                               | Min       | Typ (Note<br>2) | Max      | Units |

|-------------------|-----------------------------------|----------------------------------------------------------|-----------|-----------------|----------|-------|

| LVCMOS/L          | VTTL DC SPECIFICATIONS (SCL       | K, SI/SEL1, SEL0, LOAD, MODE , CS                        | SCLK, RSC | LK, CSO, RS     | SO)      |       |

| V <sub>IH</sub>   | High Level Input Voltage          |                                                          | 1.7       |                 | $V_{DD}$ | V     |

| V <sub>IL</sub>   | Low Level Input Voltage           |                                                          | GND       |                 | 0.7      | V     |

| I <sub>IH</sub>   | High Level Input Current          | $V_{IN} = V_{DD} = V_{DDMAX}$                            | -10       |                 | +10      | μA    |

| I <sub>IL</sub>   | Low Level Input Current           | $V_{IN} = V_{SS}, V_{DD} = V_{DDMAX}$                    | -10       |                 | +10      | μA    |

| C <sub>IN1</sub>  | Input Capacitance                 | Any Digital Input Pin to $V_{\mbox{\scriptsize SS}}$     |           | 3.5             |          | pF    |

| C <sub>OUT1</sub> | Output Capacitance                | Any Digital Output Pin to $\rm V_{SS}$                   |           | 5.5             |          | pF    |

| V <sub>CL</sub>   | Input Clamp Voltage               | I <sub>CL</sub> = -18 mA                                 | -1.5      | -0.8            |          | V     |

| V <sub>он</sub>   | High Level Output Voltage         | $I_{OH}$ = -4.0 mA, $V_{DD}$ = $V_{DDMIN}$               | 1.9       |                 |          | V     |

|                   |                                   | $I_{OH} = -100 \ \mu A, \ V_{DD} = 2.5 V$                | 2.4       |                 |          | V     |

| V <sub>OL</sub>   | Low Level Output Voltage          | $I_{OL}$ = 4.0 mA, $V_{DD}$ = $V_{DDMIN}$                |           |                 | 0.4      | V     |

|                   |                                   | I <sub>OL</sub> = 100 μA, V <sub>DD</sub> = 2.5V         |           |                 | 0.1      | V     |

| LVDS INPU         | IT DC SPECIFICATIONS (IN1±, IN    | I2±, IN3±, IN4±)                                         |           |                 |          |       |

| V <sub>TH</sub>   | Differential Input High Threshold | V <sub>CM</sub> = 0.05V or 1.2V or 2.45V,                |           | 0               | 50       | m)/   |

|                   | (Note 3)                          | $V_{DD} = 2.5V$                                          |           | 0               |          | mV    |

| V <sub>TL</sub>   | Differential Input Low Threshold  | $V_{CM} = 0.05V \text{ or } 1.2V \text{ or } 2.45V,$     | -50       | 0               |          | mV    |

|                   |                                   | $V_{DD} = 2.5V$                                          | -30       | 0               |          | 111V  |

| V <sub>ID</sub>   | Differential Input Voltage        | $V_{\text{DD}}$ = 2.5V, $V_{\text{CM}}$ = 0.05V to 2.45V | 100       |                 | $V_{DD}$ | mV    |

| V <sub>CMR</sub>  | Common Mode Voltage Range         | $V_{ID} = 100 \text{ mV}, V_{DD} = 2.5 \text{V}$         | 0.05      |                 | 3.25     | V     |

| C <sub>IN2</sub>  | Input Capacitance                 | IN+ or IN– to V <sub>SS</sub>                            |           | 3.5             |          | pF    |

| I <sub>IN</sub>   | Input Current                     | $V_{IN}$ = 2.5V, $V_{DD}$ = $V_{DDMAX}$ or 0V            | -10       |                 | +10      | μA    |

|                   |                                   | $V_{IN} = 0V, V_{DD} = V_{DDMAX} \text{ or } 0V$         | -10       |                 | +10      | μA    |

| LVDS OUT          | PUT DC SPECIFICATIONS (OUT1       | ±, OUT2±, OUT3±, OUT4±)                                  |           |                 |          |       |

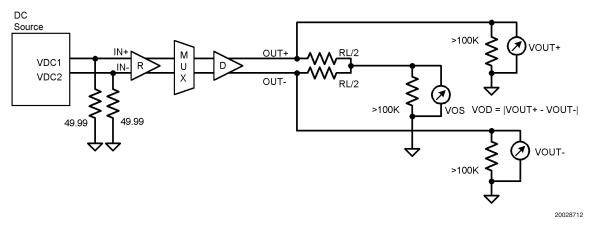

| V <sub>OD</sub>   | Differential Output Voltage (Note | $R_L = 100\Omega$ between OUT+ and                       | 250       | 400             | 475      | mV    |

|                   | 3)                                | OUT-Figure 2                                             | 250       | 400             | 475      | IIIV  |

| $\Delta V_{OD}$   | Change in V <sub>OD</sub> between |                                                          | -35       |                 | 35       | mV    |

|                   | Complementary States              |                                                          | -00       |                 | 00       |       |

| V <sub>os</sub>   | Offset Voltage (Note 4)           |                                                          | 1.125     | 1.25            | 1.375    | V     |

| $\Delta V_{OS}$   | Change in V <sub>OS</sub> between |                                                          | -35       |                 | 35       | mV    |

|                   | Complementary States              |                                                          | -00       |                 | 00       | 111V  |

DS90CP04

**Electrical Characteristics** (Continued) Over recommended operating supply and temperature ranges unless other specified.

| Symbol            | Parameter                                     | Conditions                                                                                                                                    | Min | Typ (Note<br>2) | Max  | Units |

|-------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|------|-------|

| oz                | Output TRI-STATE Current                      | TRI-STATE Output<br>$V_{OUT} = V_{DD}$ or $V_{SS}$                                                                                            | -10 |                 | +10  | μA    |

| OFF               | Power Off Leakage Current                     | $V_{DD} = 0V, V_{OUT} = 2.5V \text{ or GND}$                                                                                                  | -10 |                 | +10  | μA    |

| OFF<br>OS         | Output Short Circuit Current,                 | OUT+ or OUT– Short to GND                                                                                                                     | 10  | -15             | -40  | mA    |

| 05                | One Complementary Output                      | OUT+ or OUT- Short to $V_{DD}$                                                                                                                |     | 15              | 40   | mA    |

| OSB               | Output Short Circuit Current,                 | OUT+ and OUT– Short to GND                                                                                                                    |     | -15             | -30  | mA    |

| OSB               | both Complementary Outputs                    | OUT+ and OUT- Short to $V_{CM}$                                                                                                               |     | 15              | 30   | mA    |

| C <sub>OUT2</sub> | Output Capacitance                            | OUT+ or OUT– to GND when                                                                                                                      |     | 10              | 00   |       |

|                   |                                               | TRI-STATE                                                                                                                                     |     | 5.5             |      | pF    |

| SUPPLY C          |                                               |                                                                                                                                               |     |                 |      |       |

| I <sub>CCD</sub>  | Total Supply Current                          | All inputs and outputs enabled,<br>terminated with differential load of<br>$100\Omega$ between OUT+ and OUT                                   |     | 220             | 300  | mA    |

| I <sub>ccz</sub>  | TRI-STATE Supply Current                      | TRI-STATE All Outputs                                                                                                                         |     | 10              | 20   | mA    |

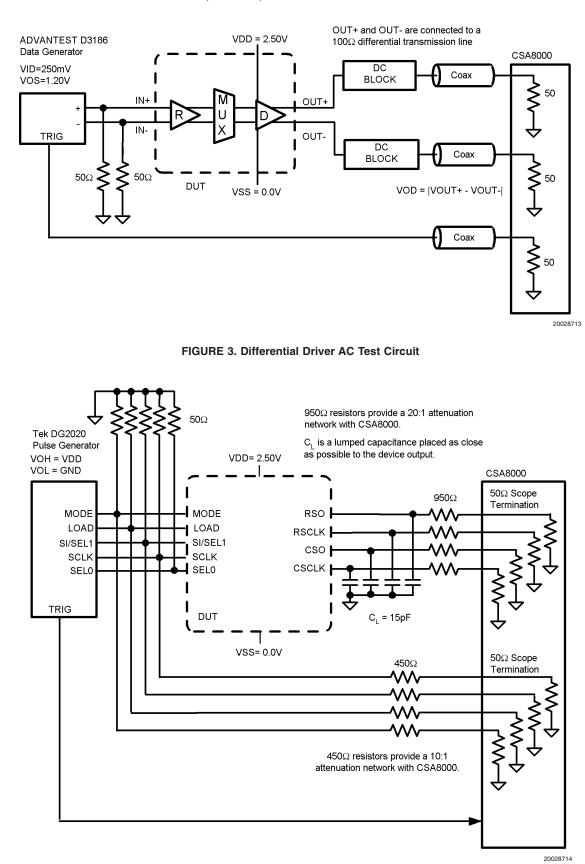

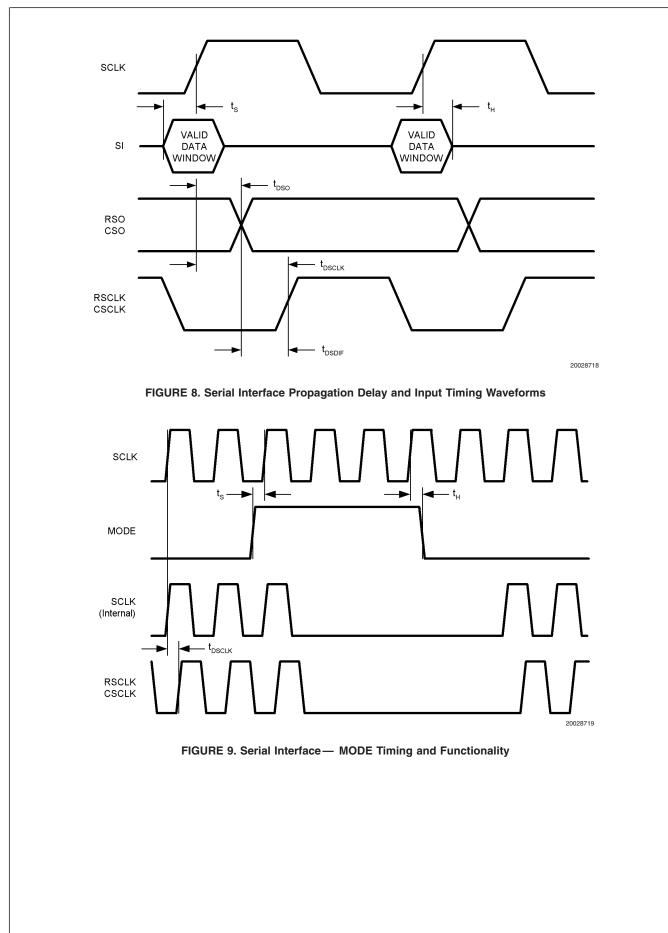

|                   | G CHARACTERISTICS-LVDS (                      | DUTPUTS (Figures 3, 5, 6)                                                                                                                     |     | ·               |      | -     |

| LHT               | Differential Low to High<br>Transition Time   | Use an alternating 1 and 0 pattern at 200 Mb/s, measure between                                                                               | 100 | 135             | 160  | ps    |

| t <sub>HLT</sub>  | Differential High to Low<br>Transition Time   | 20% and 80% of $V_{\rm OD}.$                                                                                                                  | 100 | 135             | 160  | ps    |

| t <sub>PLHD</sub> | Differential Low to High<br>Propagation Delay | Use an alternating 1 and 0 pattern at 200 Mb/s, measure at 50% $V_{\rm OD}$                                                                   | 500 | 750             | 1200 | ps    |

| t <sub>PHLD</sub> | Differential High to Low<br>Propagation Delay | between input to output.                                                                                                                      | 500 | 750             | 1200 | ps    |

| t <sub>skD1</sub> | Pulse Skew                                    | It <sub>PLHD</sub> -t <sub>PHLD</sub>                                                                                                         |     | 0               | 30   | ps    |

| t <sub>skcc</sub> | Output Channel to Channel<br>Skew             | Difference in propagation delay $(t_{PLHD} \text{ or } t_{PHLD})$ among all output channels in Broadcast mode (any one input to all outputs). | 0   | 50              | 100  | ps    |

| t <sub>JIT</sub>  | Jitter (Note 5)                               |                                                                                                                                               |     |                 |      |       |

|                   |                                               | Alternating 1 and 0 Pattern<br>750 MHz                                                                                                        |     | 1.6             | 2.5  | psrms |

|                   |                                               | 1.25 GHz                                                                                                                                      |     | 1.6             | 2.5  | psrms |

|                   |                                               | K28.5 Pattern                                                                                                                                 |     |                 |      |       |

|                   |                                               | 1.5 Gb/s                                                                                                                                      |     | 10              | 40   | psp-p |

|                   |                                               | 2.5 Gb/s                                                                                                                                      |     | 27              | 60   | psp-p |

|                   |                                               | PRBS 2 <sup>23</sup> -1 Pattern                                                                                                               |     |                 |      |       |

|                   |                                               | 1.5 Gb/s                                                                                                                                      |     | 25              | 40   | psp-p |

|                   |                                               | 2.5 Gb/s                                                                                                                                      |     | 40              | 70   | psp-p |

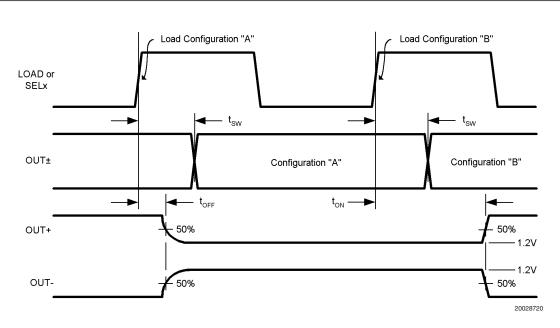

| t <sub>on</sub>   | LVDS Output Enable Time                       | Time from LOAD = LH or SELx to<br>OUT± change from TRI-STATE to<br>active.                                                                    | 50  | 150             | 300  | ns    |

| OFF               | LVDS Output Disable Time                      | Time from LOAD = LH or SELx to<br>OUT± change from active to<br>TRI-STATE.                                                                    |     | 3               | 5    | ns    |

| SW                | LVDS Switching Time                           | Time from LOAD = LH to new<br>switch configuration effective for<br>OUT±.                                                                     |     | 50              | 150  | ns    |

# Electrical Characteristics (Continued)

Over recommended operating supply and temperature ranges unless other specified.

| Symbol             | Parameter                                      | Conditions                                                                      |     | Typ (Note<br>2) | Мах | Units |

|--------------------|------------------------------------------------|---------------------------------------------------------------------------------|-----|-----------------|-----|-------|

| t <sub>SEL</sub>   | SELx to OUT±                                   | Configuration select to new data at OUT±.                                       |     | 50              | 150 | ns    |

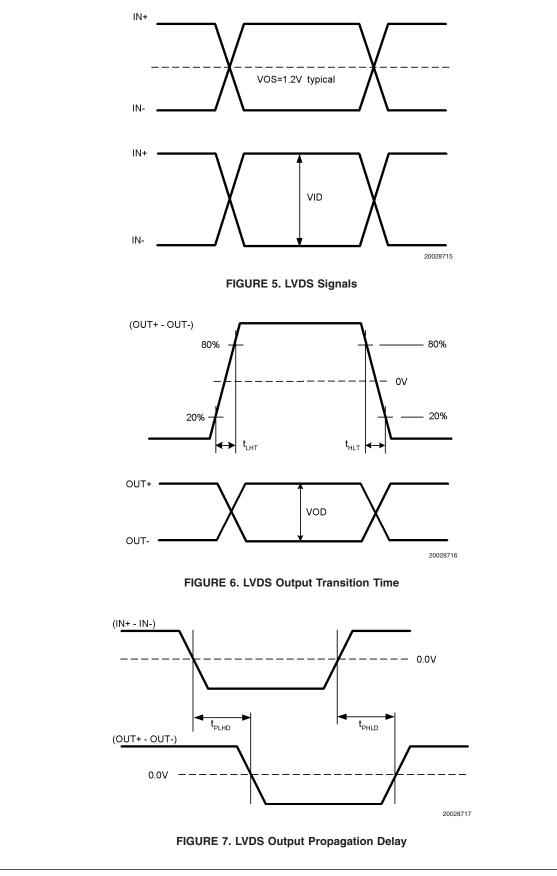

| SWITCHIN           | G CHARACTERISTICS — Serial                     | control Interface (Figures 4, 8, 9)                                             |     |                 |     |       |

| F <sub>SCLK</sub>  | SCLK Clock Frequency                           |                                                                                 | 0   |                 | 100 | MHz   |

| T <sub>DCCLK</sub> | CSCLK Duty Cycle<br>RSCLK Duty Cycle           | Input SCLK Duty Cycle set at 50%                                                | 45  |                 | 55  | %     |

| t <sub>s</sub>     | SI–SCLK or MODE–SCLK<br>Setup Time             | From SI or MODE Input Data to<br>SCLK Rising Edge                               | 1.5 |                 |     | ns    |

| t <sub>H</sub>     | SCLK-SI or SCLK-MODE Hold                      | From SCLK Rising Edge to SI or<br>MODE Input Data                               | 1   |                 |     | ns    |

| t <sub>DSO</sub>   | SCLK to RSO or CSO Delay                       | From SCLK to RSO or CSO                                                         | 1.5 |                 | 4   | ns    |

| t <sub>DSCLK</sub> | SCLK to RSCLK or CSCLK<br>Delay                | From SCLK to RSCLK or CSCLK                                                     | 4.0 |                 | 8.5 | ns    |

| t <sub>DSDIF</sub> | ISCLK to RSCLK or<br>CSCLK–SCLK to RSO or CSOI | Propagation Delay Difference<br>between t <sub>DSO</sub> and t <sub>DSCLK</sub> | 1.5 |                 | 4.5 | ns    |

| T <sub>RISE</sub>  | Logic Low to High Transition<br>Time           | 20% to 80% at RSO, CSO,<br>RSCLK, or CSCLK                                      |     | 1.5             |     | ns    |

| T <sub>fall</sub>  | Logic High to Low Transition<br>Time           | 80% to 20% at RSO, CSO,<br>RSCLK, or CSCLK                                      |     | 1.5             |     | ns    |

Note 1: "Absolute Maximum Ratings" are the ratings beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits.

Note 2: Typical parameters are measured at V<sub>DD</sub> = 2.5V, T<sub>A</sub> = 25°C. They are for reference purposes, and are not production-tested.

Note 3: Differential output voltage V<sub>OD</sub> is defined as IOUT+-OUT-I. Differential input voltage V<sub>ID</sub> is defined as IIN+-IN-I.

Note 4: Output offset voltage V<sub>OS</sub> is defined as the average of the LVDS single-ended output voltages at logic high and logic low states.

**Note 5:** Characterized from any input to any one differential LVDS output running at the specified data rate and data pattern, with all other 3 channels running K28.5 pattern at 1.25 Gb/s asynchronously to the channel under test. Jitter is not production-tested, but guaranteed through characterization on sample basis. Random Jitter is measured peak to peak with a histogram including 1000 histogram window hits. K28.5 pattern is repeating bit streams of (0011111010 1100000101). This deterministic jitter or DJ pattern is measured to a histogram mean with a sample size of 350 hits. Like RJ the Total Jitter or TJ is measured peak to peak with a histogram including 3500 window hits.

FIGURE 2. Differential Driver DC Test Circuit

# Electrical Characteristics (Continued)

#### FIGURE 4. LVCMOS Driver AC Test Circuit (Note 6)

# Electrical Characteristics (Continued)

Note 6: The LVCMOS input and output AC specifications may also be verified and tested using an input attenuation network instead of a power splitter as shown in Figure 4.

# **Functional Descriptions**

# PROGRAMMING WITH THE SERIAL INTERFACE

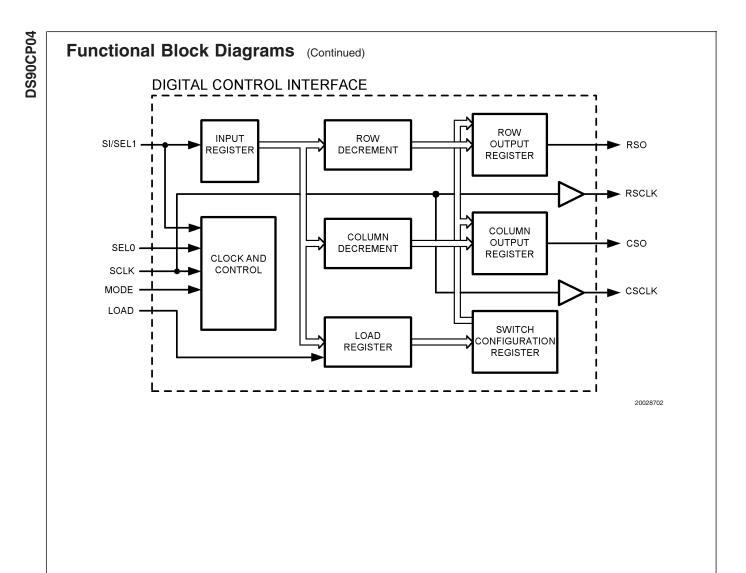

The configuration of the internal multiplexer is programmed through a simple serial interface consisting of serial clock SCLK and serial input data line SI. The serial interface is designed for easy expansion to larger switch array. A replicated output serial interface (RSCLK, RSO) is provided for propagating the control data to the downstream device in the row of an array of DS90CP04 devices in a matrix. A similar replicated serial interface (CSCLK, CSO) is provided for propagating the control data to the downstream devices in the first column of the device matrix. Through this scheme, user can program all the devices in the matrix through one serial control bus (SCLK and SI) with the use of the feedthrough replicated control bus at RSCLK and RSO, CSCLK and CSO.

To program the configuration of the switch, a 30-bit control word is sent to the device. The first 6 bits shift the start frame into SI. The only two valid start frames are 1F'h for a configuration load and 1E'h for a configuration read. The start frame is followed by the row and column addresses of the device to be accessed, as well as the switch configuration of the four channels of the device. *Table 1* and *Table 2* are the bit definitions of the control word. D29 is the first bit that shifts into SI.

| Bit     | Bit Length | Descriptions                                                                                                           |

|---------|------------|------------------------------------------------------------------------------------------------------------------------|

| D29–D24 | 6          | The start frame for control word synchronization (01 1111'b = LOAD).                                                   |

| D23–D18 | 6          | Specify the row address of the device to be access. The serial interface can access up to 64 devices in the row.       |

| D17–D12 | 6          | Specify the column address of the device to be access. The serial interface can access up to 64 devices in the column. |

| D11–D9  | 3          | Specify the switch configuration for Output 1. See Table 2.                                                            |

| D8-D6   | 3          | Specify the switch configuration for Output 2. See Table 2.                                                            |

| D5–D3   | 3          | Specify the switch configuration for Output 3. See Table 2.                                                            |

| D2-D0   | 3          | Specify the switch configuration for Output 4. See Table 2.                                                            |

#### TABLE 1. 30-Bit Control Word

|     | TABLE 2. Switch Configuration Data                          |   |                     |                     |                     |                     |  |  |  |

|-----|-------------------------------------------------------------|---|---------------------|---------------------|---------------------|---------------------|--|--|--|

| MSB | B LSB OUT1± Connects to OUT2± Connects to OUT3± Connects to |   |                     |                     |                     | OUT4± Connects to   |  |  |  |

| 0   | 0                                                           | 0 | Output 1 Tri-Stated | Output 2 Tri-Stated | Output 3 Tri-Stated | Output 4 Tri-Stated |  |  |  |

| 0   | 0                                                           | 1 | IN1±                | IN1±                | IN1±                | IN1±                |  |  |  |

| 0   | 1                                                           | 0 | IN2±                | IN2±                | IN2±                | IN2±                |  |  |  |

| 0   | 1                                                           | 1 | IN3±                | IN3±                | IN3±                | IN3±                |  |  |  |

| 1   | 0                                                           | 0 | IN4±                | IN4±                | IN4±                | IN4±                |  |  |  |

| 1   | 0                                                           | 1 | Invalid.            | ·                   |                     |                     |  |  |  |

|     | •                                                           |   | •                   |                     |                     |                     |  |  |  |

# Functional Descriptions (Continued) TABLE 2. Switch Configuration Data (Continued) MSB LSB OUT1± Connects to OUT2± Connects to OUT3± Connects to OUT4± Connects to 1 1 0 Use of these invalid combinations may cause loss of synchronization. Image: Content of the second sec

#### **ROW AND COLUMN ADDRESSING**

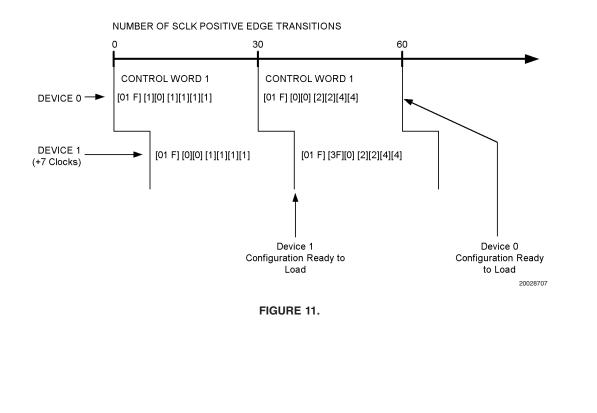

The upper left device in an array of NxN devices is assigned row address 0, and column address 0. The devices to its right have column addresses of 1 to N, whereas devices below it have row addresses of 1 to N. The Serial Control Interface (SCLK and SI) is connected to the first device with the row and column addresses of 0. The Serial Control Interface shifts in a control word containing the row and column address of the device it wants to access. When the control data propagates through each device, the control word's address is internally decremented by one before it is sent to the next row or column device. When the control data is sent out the column interface (CSO and CSCLK) the row address is decremented by one. Similarly, when the column address data is shifted out the row interface (RSO and RSCLK) the column address is decremented by one. By the time the control word reaches the device it has been intended to program, both the row and column addresses have been decremented to 0.

Each device constantly checks for the receipt of a frame start (D29-24=01 1111'b or 01 1110'b). When it detects the proper start frame string, and the row and column addresses it receives are both 0, the device responds by storing the switch configuration data of the 30-bit control word into its load register.

Each device in the array is sequentially programmed through the serial interface. When programming is completed for the entire array, LOAD is pulsed high and the load register's content is transferred to the configuration register of each device. The LOAD pulse must wait until the final bit of the control word has been placed into the "load" register. This timing is guaranteed to take place two clock cycles after programming has been completed.

Due to internal shift registers additional SCLK cycles will be necessary to complete array programming. It takes 7 clock (SCLK) positive edge transitions for the control data to appear at RSO and CSO for its near neighbor. Users must provide the correct number of clock transitions for the control data word to reach its destination in the array. *Table 3* shows an example of the control data words for a 4 device serial chain with connections (OUT1=IN1, OUT2=IN2, OUT16=IN16). To program the array, it requires four 30-bit control words to ripple through the serial chain and reach their destinations. In order to completely program the array in the 120 clock cycles associated with the 30-bit control words it is important to program the last device in the chain first. The following programming data pushes the initial data through the chain into the correct devices.

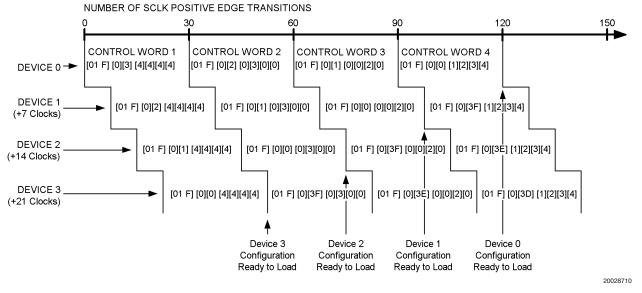

#### READ-BACK SWITCH CONFIGURATION

The DS90CP04 is put into read-back mode by sending a special "Read" start frame (01 1110'b). Upon receipt of the special read start frame the configuration register information is transferred into the shift register and output at both RSO and CSO in the OUT1 to OUT4 bit segments of the read control word. Each time the read-back data from a device passes through its downstream device, its default address (11 1111'b) is internally decremented by one. The "relative" column address emerges at RSO of the last device in the row and is used to determine (11 1111'b - N) the column of the sending device. Similarly, the row address emerges at CSO of the sending device. After inserting the channel configuration information in the "read" control word, the device will automatically revert to write mode, ready to accept a new control word at SI.

Table 4 shows an example of reading back the configuration registers of 4 devices in the first row of a 4x4 device array. Again, due to internal shift registers additional SCLK cycles will be necessary to complete the array read. It takes 4x30 SCLK clock cycles to shift out 4 30-bit configuration registers plus 7 SCLK cycles per device to account for device latency making for a total SCLK count of 148. The serialized read data is sampled at RSO and synchronized with RSCLK of the last device in the row. The user is recommended to backfill with all 0's at SI after the four reads have been shifted in.

| Frame<br>D29:D24 | Row<br>Address<br>D23:D18 | Column<br>Address<br>D17:D12 | OUT1<br>D11:D9                    | OUT2<br>D8:D6                 | OUT3<br>D5:D3    | OUT4<br>D2:D0 | Number of<br>SCLK<br>Cycles | Control Word<br>Destination<br>Device in<br>Array<br>Row, Column |

|------------------|---------------------------|------------------------------|-----------------------------------|-------------------------------|------------------|---------------|-----------------------------|------------------------------------------------------------------|

| 01 1111          | 00 0000                   | 00 0011                      | 001                               | 010                           | 011              | 100           | 30                          | 0, 3                                                             |

| 01 1111          | 00 0000                   | 00 0010                      | 001                               | 010                           | 011              | 100           | 30                          | 0, 2                                                             |

| 01 1111          | 00 0000                   | 00 0001                      | 001                               | 010                           | 011              | 100           | 30                          | 0, 1                                                             |

| 01 1111          | 00 0000                   | 00 0000                      | 001                               | 010                           | 011              | 100           | 30                          | 0, 0                                                             |

| Shift in confi   | guration inforn           |                              | vice furthest from                | om system SI<br>ming process. | input first to m | inimize array |                             |                                                                  |

| The 2 clock      | cycle delay e             |                              | nnel informatio<br>re ready to be | n has reached configured.     | the "load" reg   | ister and all | 2                           |                                                                  |

TABLE 3. Example to Program a 4 Device Array

# Functional Descriptions (Continued)

| Frame<br>D29:D24 | Row<br>Address<br>D23:D18 | Column<br>Address<br>D17:D12 | OUT1<br>D11:D9 | OUT2<br>D8:D6 | OUT3<br>D5:D3 | OUT4<br>D2:D0 | Number of<br>SCLK<br>Cycles | Descriptions            |

|------------------|---------------------------|------------------------------|----------------|---------------|---------------|---------------|-----------------------------|-------------------------|

| 01 1110          | 00 0000                   | 11 1111                      | 000            | 000           | 000           | 000           | 30                          | Read-Back<br>(R,C)=0, 3 |

| 01 1110          | 00 0000                   | 11 1110                      | 000            | 000           | 000           | 000           | 30                          | Read-Back<br>(R,C)=0, 2 |

| 01 1110          | 00 0000                   | 11 1101                      | 000            | 000           | 000           | 000           | 30                          | Read-Back<br>(R,C)=0, 1 |

| 01 1110          | 00 0000                   | 11 1100                      | 001            | 010           | 011           | 100           | 30                          | Read-Back<br>(R,C)=0, 0 |

Note 7: LOAD and READ programming example is based on the 16x16 array configuration shown in *Figure 11*. Alternative expansion array configurations will require a slightly different programming sequence.

# SWITCH EXPANSION FOR MINIMUM PROGRAMMING LATENCY

Programming data ripples through the array through RSO and RSCLK in the row and CSO and CSCLK in the first column. LOAD pins of all devices are electrically tied together and driven by the same "load" signal. To prevent excessive stub length in the array from affecting the signal quality of LOAD, it is recommended that the load signal is distributed to each row or column in large crosspoint array applications.

# **Programming Example**

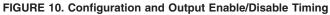

# CONFIGURATION WRITE

30 Bit Control Word: [WRITE FRAME] [ROW ADDRESS][COLUMN ADDRESS] [OUT1][OUT2][OUT3][OUT4]

# ARRAY WRITE:

[01 1111] [0][1] [1][1][1][1] //\*Array position 1, Broadcast IN1 \*// [01 1111] [0][0] [2][2][4][4] //\*Array position 0, Connect IN2 to OUT1 and 2, IN4 to OUT3 and OUT4 \*// LOAD = H and SCLK = LH

# **DEVICE 0 WRITE PROGRAMMING SEQUENCE**

| SCLK<br>Number | Event Description                                                                                                                                                         |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6              | Device 0 (R=0, C=0) detects "WRITE" frame of first Control Word.                                                                                                          |

| 18             | Device 0 (R=0, C=0) sees Row = 1, Column = 0 of first Control Word. The Row address of the first Control Word is decremented by 1 (Row Address = 0) and sent out RSO.     |

| 36             | Device 0 (R=0, C=0) detects "WRITE" frame of second Control Word.                                                                                                         |

| 48             | Device 0 (R=0, C=0) sees Row = 0, Column = 0 of second Control Word. This is a valid configuration write address, Device 1 prepares to receive configuration information. |

| 60             | Device 0 (R=0, C=0) has received configuration information and is waiting for a LOAD.                                                                                     |

# **DEVICE 1 WRITE PROGRAMMING SEQUENCE**

| SCLK<br>Number | Event Description                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------------|

| 13             | Device 1 (R=1, C=0) detects "WRITE" frame of first Control Word.                                       |

| 25             | Device 1 (R=1,C=0) sees Row = 0, Column = 0 of first Control Word. This is a valid configuration write |

|                | address, Device 1 prepares to receive configuration information.                                       |

| 37             | Device 1 (R=1,C=0) has received configuration information and is waiting for a LOAD.                   |

| 43             | Device 1 (R=1, C=0) detects "WRITE" frame of second Control Word.                                      |

| 55             | Device 1 (R=1,C=0) sees Row = 3F, Column = 0 of second Control Word. The Row address of the second     |

|                | Control Word is decremented by 1 (Row Address = 3E) and sent out RSO.                                  |

# CONFIGURATION READ

30 Bit Control Word: [READ FRAME] [ROW ADDRESS][COLUMN ADDRESS] [OUT1][OUT2][OUT3][OUT4]

#### ARRAY WRITE:

[01 1110] [1][0] [0][0][0][0] //\*Array position 1, Return Configuration Information \*//

[01 1110] [0][0] [0][0][0][0] //\*Array position 0, Return Configuration Information \*//

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.