SBAS150A - AUGUST 1987 - REVISED FEBRUARY 2003

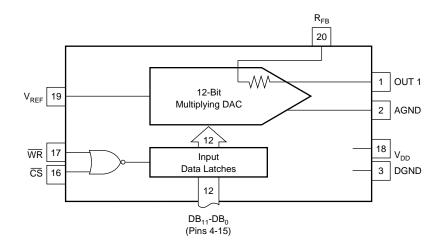

# CMOS 12-Bit Multiplying DIGITAL-TO-ANALOG CONVERTER Microprocessor Compatible

#### **FEATURES**

- FOUR-QUADRANT MULTIPLICATION

- LOW-GAIN TC: 2ppm/°C typ

- MONOTONICITY ENSURED OVER TEMPERATURE

- SINGLE 5V TO 15V SUPPLY

- TTL/CMOS LOGIC COMPATIBLE

- LOW OUTPUT LEAKAGE: 10nA max

- **LOW OUTPUT CAPACITANCE: 70pF max**

- DIRECT REPLACEMENT FOR THE AD7545, PM-7545

#### DESCRIPTION

The DAC7545 is a low-cost, CMOS, 12-bit, four-quadrant multiplying, digital-to-analog converter (DAC) with input data latches. The input data is loaded into the DAC as a 12-bit data word. The data flows through to the DAC when both the chip select  $(\overline{CS})$  and the write  $(\overline{WR})$  pins are at a logic low. Laser-trimmed thin-film resistors and excellent CMOS voltage switches provide true 12-bit integral and differential linearity. The device operates on a single +5V to +15V supply and is available in an SO-20 package; devices are specified over the commercial temperature range.

The DAC7545 is well suited for battery-powered or other low-power applications because the power dissipation is less than 0.5mW when used with CMOS logic inputs and  $V_{DD} = +5V$ .

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### ABSOLUTE MAXIMUM RATINGS(1)

$T_{\Delta}$  = +25°C, unless otherwise noted.

| V <sub>DD</sub> to DGND                       | 0.3V, +17             |

|-----------------------------------------------|-----------------------|

| Digital Input to DGND                         | 0.3V, V <sub>DD</sub> |

| V <sub>RFB</sub> , V <sub>REF</sub> , to DGND | ±25V                  |

| V <sub>PIN 1</sub> to DGND                    | 0.3V, V <sub>DD</sub> |

| AGND to DGND                                  | 0.3V, V <sub>DD</sub> |

| Power Dissipation: Any Package to +75°C       | 450mW                 |

| Derates above +75°C by                        | 6mW/°C                |

| Operating Temperature:                        |                       |

| Commercial J, K, L, and GL                    | 40°C to +85°C         |

| Storage Temperature                           | 65°C to +150°C        |

| Lead Temperature (soldering, 10s)             | +300°C                |

NOTE: (1) Stresses above those listed above may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT | RELATIVE<br>ACCURACY (LSB) | GAIN ERROR (LSB)<br>V <sub>DD</sub> = +5V | PACKAGE-LEAD |    | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|----------------------------|-------------------------------------------|--------------|----|-----------------------------------|--------------------|--------------------|------------------------------|

| DAC7545 | ±2                         | ±20                                       | SO-20        | DW | -40°C to +85°C                    | DAC7545JU          | DAC7545JU          | Rails, 38                    |

| "       | ±1                         | ±10                                       | "            | "  | "                                 | DAC7545KU          | DAC7545KU          | Rails, 38                    |

| DAC7545 | ±1/2                       | ±5                                        | SO-20        | DW | -40°C to +85°C                    | DAC7545LU          | DAC7545LU          | Rails, 38                    |

| "       | ±1/2                       | <u>+2</u>                                 | "            | "  | "                                 | DAC7545GLU         | DAC7545GLU         | Rails, 38                    |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com.

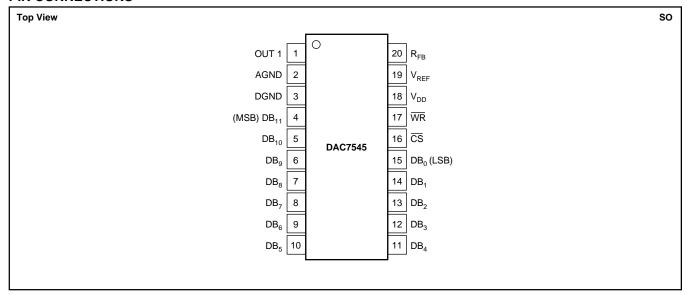

#### **PIN CONNECTIONS**

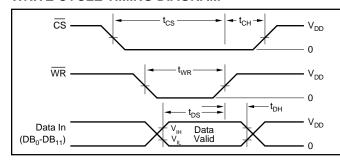

#### WRITE CYCLE TIMING DIAGRAM

| Mode Selection                                                                                                            |                                                                                                                                                                                                                        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Write Mode                                                                                                                | Hold Mode                                                                                                                                                                                                              |  |  |  |

| $\overline{\text{CS}}$ and $\overline{\text{WR}}$ low, DAC responds Data Bus (DB <sub>0</sub> -DB <sub>11</sub> ) inputs. | Either $\overline{\text{CS}}$ or $\overline{\text{WR}}$ high, data bus to $(DB_0\text{-}DB_{11})$ is locked out; DAC holds last data present when $\overline{\text{WR}}$ or $\overline{\text{CS}}$ assumed high state. |  |  |  |

NOTES:  $V_{DD}$  = +5V,  $t_R$  =  $t_F$  = 20ns.  $V_{DD}$  = +15V,  $t_R$  =  $t_F$  = 40ns. All inputs signal rise and fall times measured from 10% to 90% of  $V_{DD}$ . Timing measurement reference level is  $(V_{IH} + V_{IL})/2$ .

#### **ELECTRICAL CHARACTERISTICS**

$V_{REF}$  = +10V,  $V_{OUT\,1}$  = 0V, and ACOM = DCOM, unless otherwise specified.

|                                                                      |             | DAC7545                |                                                   |                        |                                                   |                        |                                                                      |

|----------------------------------------------------------------------|-------------|------------------------|---------------------------------------------------|------------------------|---------------------------------------------------|------------------------|----------------------------------------------------------------------|

|                                                                      |             | V <sub>DD</sub> :      | V <sub>DD</sub> = +5V                             |                        |                                                   |                        |                                                                      |

| PARAMETER                                                            | GRADE       | T <sub>A</sub> = +25°C | T <sub>MAX</sub> -T <sub>MIN</sub> <sup>(1)</sup> | T <sub>A</sub> = +25°C | T <sub>MAX</sub> -T <sub>MIN</sub> <sup>(1)</sup> | UNITS                  | TEST CONDITIONS/COMMENTS                                             |

| STATIC PERFORMANCE                                                   |             |                        |                                                   |                        |                                                   |                        |                                                                      |

| Resolution                                                           | All         | 12                     | 12                                                | 12                     | 12                                                | Bits                   |                                                                      |

| Accuracy                                                             | J           | ±2                     | ±2                                                | ±2                     | ±2                                                | LSB                    |                                                                      |

|                                                                      | K           | ±1                     | ±1                                                | ±1                     | ±1                                                | LSB                    |                                                                      |

|                                                                      | L           | ±1/2                   | ±1/2                                              | ±1/2                   | ±1/2                                              | LSB                    |                                                                      |

|                                                                      | GL          | ±1/2                   | ±1/2                                              | ±1/2                   | ±1/2                                              | LSB                    |                                                                      |

| Differential Nonlinearity                                            | J           | ±4                     | ±4                                                | ±4                     | ±4                                                | LSB                    | 10-Bit Monotonic, T <sub>MIN</sub> to T <sub>MAX</sub>               |

|                                                                      | K           | ±1                     | ±1                                                | ±1                     | ±1                                                | LSB                    | 10-Bit Monotonic, T <sub>MIN</sub> to T <sub>MAX</sub>               |

|                                                                      | L           | ±1                     | ±1                                                | ±1                     | ±1                                                | LSB                    | 12-Bit Monotonic, T <sub>MIN</sub> to T <sub>MAX</sub>               |

|                                                                      | GL          | ±1                     | ±1                                                | ±1                     | ±1                                                | LSB                    | 12-Bit Monotonic, T <sub>MIN</sub> to T <sub>MAX</sub>               |

| Gain Error (with internal R <sub>FB</sub> ) <sup>(2)</sup>           | J           | ±20                    | ±20                                               | ±25                    | ±25                                               | LSB                    | DAC register loaded with FFF <sub>H</sub> .                          |

|                                                                      | K           | ±10                    | ±10                                               | ±15                    | ±15                                               | LSB                    | Gain error is adjustable using                                       |

|                                                                      | L           | ±5                     | ±6                                                | ±10                    | ±10                                               | LSB                    | the circuits in Figures 2 and 3.                                     |

|                                                                      | GL          | ±2                     | ±3                                                | ±6                     | ±7                                                | LSB                    |                                                                      |

| Gain Temperature Coefficient <sup>(3)</sup>                          |             |                        | _                                                 |                        |                                                   |                        |                                                                      |

| (∆Gain/∆Temperature)                                                 | All         | ±5                     | ±5                                                | ±10                    | ±10                                               |                        | Typical Value is 2ppm/°C                                             |

| (0)                                                                  |             |                        |                                                   |                        | fc fc                                             | or V <sub>DD</sub> = + | -5                                                                   |

| DC Supply Rejection <sup>(3)</sup>                                   |             |                        |                                                   |                        |                                                   |                        |                                                                      |

| $(\Delta Gain/\Delta V_{DD})$                                        | All         | 0.015                  | 0.03                                              | 0.01                   | 0.02                                              | %/%                    | $\Delta V_{DD} \pm 5\%$                                              |

| Output Leakage Current at Out 1                                      | J, K, L, GL | 10                     | 50                                                | 10                     | 50                                                | nA                     | $DB_0$ - $DB_{11} = 0V$ ; $\overline{WR}$ , $\overline{CS} = 0V$     |

| DYNAMIC PERFORMANCE                                                  |             |                        |                                                   |                        |                                                   |                        |                                                                      |

| Current Settling Time(3)                                             | All         | 2                      | 2                                                 | 2                      | 2                                                 | μs                     | To 1/2 LSB. Out 1 Load = 100Ω                                        |

| -                                                                    |             |                        |                                                   |                        |                                                   |                        | DAC output measured from                                             |

|                                                                      |             |                        |                                                   |                        |                                                   |                        | falling edge of WR. CS = 0V.                                         |

| Propagation Delay <sup>(3)</sup> (from digital input                 | All         |                        |                                                   |                        |                                                   |                        |                                                                      |

| change to 90% of final analog output)                                | All         | 300                    |                                                   | 250                    |                                                   | ns                     | Out 1 Load = $100\Omega$ . $C_{EXT} = 13pF^{(4)}$                    |

| Glitch Energy                                                        | All         | 400                    |                                                   | 250                    |                                                   | nV-s <sup>(5)</sup>    | $V_{REF} = ACOM$                                                     |

| AC Feedback at I <sub>OUT</sub> 1                                    | All         | 5                      | 5                                                 | 5                      | 5                                                 | mVp-p <sup>(5)</sup>   | $V_{REF} = ACOW$<br>$V_{REF} = \pm 10V$ , 10kHz Sine Wave            |

|                                                                      | 7 (11       |                        |                                                   |                        |                                                   | mvp p.                 | VREF = ±10V, TOKI 12 OINC VVAVC                                      |

| REFERENCE INPUT                                                      |             | l _                    | _                                                 | _                      | _                                                 | 1.0(0)                 | 1 . 5                                                                |

| Input Resistance (pin 19 to AGND)                                    | All         | 7                      | 7                                                 | 7                      | 7                                                 | $k\Omega^{(6)}$        | Input Resistance TC = 300ppm/°C <sup>(5)</sup>                       |

|                                                                      |             | 25                     | 25                                                | 25                     | 25                                                | kΩ                     |                                                                      |

| AC OUTPUTS                                                           |             |                        |                                                   |                        |                                                   |                        |                                                                      |

| Output Capacitance(3): C <sub>OUT 1</sub>                            | All         | 70                     | 70                                                | 70                     | 70                                                | pF                     | $DB_0$ - $DB_{11} = 0V$ ; $\overline{WR}$ , $\overline{CS} = 0V$     |

| C <sub>OUT 2</sub>                                                   | All         | 200                    | 200                                               | 200                    | 200                                               | pF                     | $DB_0$ - $DB_{11} = V_{DD}$ ; $\overline{WR}$ , $\overline{CS} = 0V$ |

| DIGITAL INPUTS                                                       |             |                        |                                                   |                        |                                                   | -                      |                                                                      |

| V <sub>IH</sub> (Input HIGH Voltage)                                 | All         | 2.4                    | 2.4                                               | 13.5                   | 13.5                                              | V(6)                   |                                                                      |

| V <sub>II</sub> (Input LOW Voltage)                                  | All         | 0.8                    | 0.8                                               | 1.5                    | 1.5                                               | V                      |                                                                      |

| I <sub>IN</sub> (Input Current) <sup>(7)</sup>                       | All         | ±1                     | ±10                                               | ±1                     | ±10                                               | μA                     | $V_{IN} = 0V \text{ or } V_{DD}$                                     |

| Input Capacitance <sup>(3)</sup> : DB <sub>0</sub> -DB <sub>11</sub> | All         | 5                      | 5                                                 | 5                      | 5                                                 | pF                     | $V_{IN} = 0V$ or $V_{DD}$                                            |

| WR, CS                                                               | All         | 20                     | 20                                                | 20                     | 20                                                | рF                     | $V_{IN} = 0V$                                                        |

|                                                                      | 7 (11       | 20                     | 20                                                | 20                     | 20                                                | Pi                     | VIN = 0 V                                                            |

| SWITCHING CHARACTERISTICS(8)                                         |             |                        |                                                   |                        |                                                   |                        |                                                                      |

| Chip Select to Write Setup Time, $t_{CS}$                            | All         | 280                    | 380                                               | 180                    | 200                                               | ns <sup>(6)</sup>      | See Timing Diagram                                                   |

|                                                                      |             | 200                    | 270                                               | 120                    | 150                                               | ns <sup>(5)</sup>      |                                                                      |

| Chip Select to Write Hold Time, t <sub>CH</sub>                      | All         | 0                      | 0                                                 | 0                      | 0                                                 | ns <sup>(6)</sup>      | l                                                                    |

| Write Pulse Width, t <sub>WR</sub>                                   | All         | 250                    | 400                                               | 160                    | 240                                               | ns <sup>(6)</sup>      | $t_{CS} \ge t_{WR}, t_{CH} \ge 0$                                    |

| B . C . T                                                            |             | 175                    | 280                                               | 100                    | 170                                               | ns <sup>(5)</sup>      |                                                                      |

| Data Setup Time, t <sub>DS</sub>                                     | All         | 140                    | 210                                               | 90                     | 120                                               | ns <sup>(6)</sup>      |                                                                      |

| B                                                                    | <b></b>     | 100                    | 150                                               | 60                     | 80                                                | ns <sup>(5)</sup>      |                                                                      |

| Data Hold Time, t <sub>DH</sub>                                      | All         | 10                     | 10                                                | 10                     | 10                                                | ns <sup>(6)</sup>      |                                                                      |

| POWER SUPPLY, I <sub>DD</sub>                                        |             |                        |                                                   |                        |                                                   |                        |                                                                      |

|                                                                      | All         | 2                      | 2                                                 | 2                      | 2                                                 | mA                     | All Digital Inputs V <sub>IL</sub> or V <sub>IH</sub>                |

|                                                                      | All         | 100                    | 500                                               | 100                    | 500                                               | μΑ                     | All Digital Inputs 0V or V <sub>DD</sub>                             |

|                                                                      | All         | 10                     | 10                                                | 10                     | 10                                                | μA <sup>(5)</sup>      | All Digital Inputs 0V or V <sub>DD</sub>                             |

NOTES: (1) Temperature ranges—J, K, L, and GL:  $-40^{\circ}$ C to  $+85^{\circ}$ C. (2) This includes the effect of 5ppm max, gain TC. (3) Ensured but not tested. (4) DB<sub>0</sub>-DB<sub>11</sub> = 0V to V<sub>DD</sub> or V<sub>DD</sub> to 0V. (5) Typical. (6) Minimum. (7) Logic inputs are MOS gates. Typical input current (+25°C) is less than 1nA. (8) Sample tested at +25°C to ensure compliance.

### DISCUSSION OF SPECIFICATIONS

#### **RELATIVE ACCURACY**

This term (also known as end point linearity) describes the transfer function of analog output to digital input code. Relative accuracy describes the deviation from a straight line after zero and full-scale have been adjusted.

#### **DIFFERENTIAL NONLINEARITY**

Differential nonlinearity is the deviation from an ideal 1LSB change in the output, for adjacent input code changes. A differential nonlinearity specification of 1LSB ensures monotonicity.

#### **GAIN ERROR**

Gain error is the difference in measure of full-scale output versus the ideal DAC output; the ideal output for the DAC7545 is  $-(4095/4096)(V_{REF})$ . Gain error can be adjusted to zero using external trims, see the Applications section.

#### **OUTPUT LEAKAGE CURRENT**

The current that appears at OUT 1 with the DAC loaded with all zeros.

#### MULTIPLYING FEEDTHROUGH ERROR

The AC output error due to capacitive feedthrough from  $V_{REF}$  to OUT 1 with the DAC loaded with all zeros; this test is performed using a 10kHz sine wave.

#### **OUTPUT CURRENT SETTLING TIME**

The time required for the output to settle within  $\pm 0.5$  LSB of final value from a change in code of all zeros to all ones, or all ones to all zeros.

#### **PROPAGATION DELAY**

The delay of the internal circuitry is measured as the time from a digital code change to the point at which the output reaches 90% of final value.

#### **DIGITAL-TO-ANALOG GLITCH IMPULSE**

The area of the glitch energy measured in nanovolt-seconds. Key contributions to glitch energy are internal circuitry timing differences and charge injected from digital logic. The measurement is performed with  $V_{REF} = GND$ , an OPA600 as the output op amp, and  $G_1$  (phase compensation) = 0pF.

#### **MONOTONICITY**

Monotonicity assures that the analog output will increase or stay the same for increasing digital input codes. The DAC7545 is ensured monotonic to 12 bits, except the J grade is specified to be 10-bit monotonic.

#### POWER-SUPPLY REJECTION

Power-supply rejection is the measure of the sensitivity of the output (full-scale) to a change in the power-supply voltage.

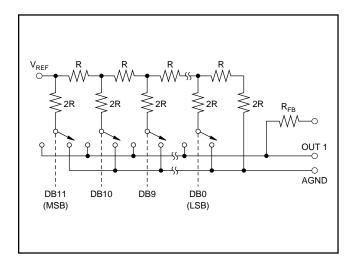

#### CIRCUIT DESCRIPTION

Figure 1 shows a simplified schematic of the DAC portion of the DAC7545. The current from the  $V_{REF}$  pin is switched from OUT 1 to AGND by the FET switch. This circuit architecture keeps the resistance at the reference pin constant and equal to  $R_{LDR}$ , so the reference can be provided by either a voltage or current, AC or DC, positive or negative polarity, and have a voltage range up to  $\pm 20V$  even with  $V_{DD} = 5V$ . The  $R_{LDR}$  is equal to R and is typically 11kW.

The output capacitance of the DAC7545 is code dependent and varies from a minimum value (70pF) at code 000h to a maximum (200pF) at code FFFh.

The input buffers are CMOS inverters, designed so that when the DAC7545 is operated from a 5V supply ( $V_{DD}$ ), the logic threshold is TTL-compatible. Being simple CMOS inverters, there is a range of operation where the inverters operate in the linear region and thus draw more supply current than normal. Minimizing this transition time through the linear region and insuring that the digital inputs are operated as close to the rails as possible will minimize the supply drain current.

FIGURE 1. Simplified DAC Circuit of the DAC7545.

#### **APPLICATIONS**

#### UNIPOLAR OPERATION

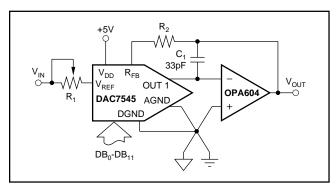

Figure 2 shows the DAC7545 connected for unipolar operation. The high-grade DAC7545 is specified for a 1LSB gain error, so gain adjust is typically not needed; however, the resistors shown are for adjusting full-scale errors. The value of  $R_1$  should be minimized to reduce the effects of mismatching temperature coefficients between the internal and external resistors. A range of adjustment of 1.5 times the desired range will be adequate. For example, for a DAC7545JP, the gain error is specified to be  $\pm 25$ LSB, therefore, a range of adjustment of  $\pm 37$ LSB will be adequate. Equation 1 results in a value of 458W for the potentiometer (use 500 $\Omega$ ).

$$R_1 = \frac{R_{LADDER}}{4096} \left( 3 \bullet Gain Error \right) \tag{1}$$

FIGURE 2. Unipolar Binary Operation.

The addition of  $R_1$  will cause a negative gain error. To compensate for this error,  $R_2$  must be added. The value of  $R_2$  should be one-third the value of  $R_1$ .

The capacitor across the feedback resistor is used to compensate for the phase shift due to stray capacitances of the circuit board, the DAC output capacitance, and op amp input capaci-

tance. Eliminating this capacitor will result in excessive ringing and an increase in glitch energy, therefore, this capacitor must be as small as possible to minimize settling time.

The circuit of Figure 2 can be used with input voltages up to  $\pm 20$ V as long as the output amplifier is biased to handle the excursions. Table I represents the analog output for four codes into the DAC for Figure 2.

#### **BIPOLAR OPERATION**

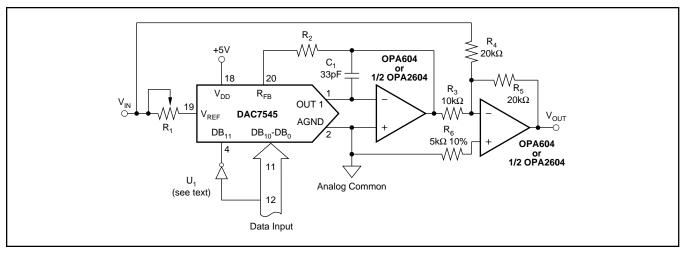

Figure 3 and Table II illustrate the recommended circuit and code relationship for bipolar operation. The DAC function uses offset binary code. The inverter,  $U_1$ , on the MSB line converts binary two's complement input code to offset binary code. If the inversion is done in software,  $U_1$  can be omitted.

| BINARY CODE    | ANALOG OUTPUT                        |

|----------------|--------------------------------------|

| MSB LSB        |                                      |

| 1111 1111 1111 | -V <sub>IN</sub> (4095/4096)         |

| 1000 0000 0000 | $-V_{IN}$ (2048/4096) = $-1/2V_{IN}$ |

| 0000 0000 0001 | -V <sub>IN</sub> (1/4096)            |

| 0000 0000 0000 | 0V                                   |

TABLE I. Unipolar Codes.

| DATA INPUT     | ANALOG OUTPUT                |

|----------------|------------------------------|

| MSB LSB        |                              |

| 0111 1111 1111 | +V <sub>IN</sub> (2047/2048) |

| 0000 0000 0001 | +V <sub>IN</sub> (1/2048)    |

| 0000 0000 0000 | 0V                           |

| 1111 1111 1111 | -V <sub>IN</sub> (1/2048)    |

| 1000 0000 0000 | -V <sub>IN</sub> (2048/2048) |

TABLE II. Binary Two's Complement Code Table for Circuit of Figure 3.

$R_3,\ R_4,$  and  $R_5$  must match within 0.01% and must be the same type of resistors (preferably wire-wound or metal foil), so that the temperature coefficients match; mismatch of  $R_3$  value to  $R_4$  causes both offset and full-scale error. Mismatch of  $R_5$  to  $R_4$  and  $R_3$  causes full-scale error.

FIGURE 3. Bipolar Operation (binary two's complement code).

#### DIGITALLY-CONTROLLED GAIN BLOCK

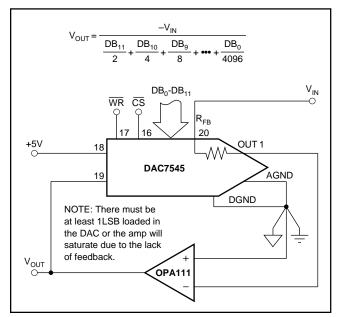

Figure 4 shows a circuit for a digitally-controlled gain block. The feedback for the op amp is made up of the FET switch and the R-2R ladder. The input resistor to the gain block is the  $R_{FB}$  of the DAC7545. As the FET switch is in the feedback loop, a zero code into the DAC will result in the op amp having no feedback, and a saturated op amp output.

FIGURE 4. Digitally Controlled Gain Block.

#### **APPLICATION HINTS**

CMOS DACs, such as the DAC7545, exhibit a code-dependent out resistance. The effect of this is a code-dependent differential nonlinearity at the amplifier output that depends on the offset voltage,  $\rm V_{OS}$ , of the amplifier. Thus linearity depends upon the potential of OUT 1 and AGND being exactly equal to each other. Usually the DAC is connected to an external op amp with the noninverting input connected to AGND. The op amp selected should have a low input bias current and low  $\rm V_{OS}$  and  $\rm V_{OS}$  drift over temperature. The op amp offset voltage should be less than (25  $\bullet$  10 $^{-6}$ )(V<sub>REF</sub>) over operating conditions. Suitable op amps are the OPA37 and the OPA627 for fixed

reference applications and low-bandwidth requirement; the OPA37 has low  $V_{OS}$  and does not require an offset trim. For wide bandwidth, high slew rate, or fast-settling applications, the OPA604 or 1/2 OPA2604 are recommended.

Unused digital inputs must be connected to  $V_{DD}$  or to DGND, this prevents noise from triggering the high impedance digital input. It is suggested that the unused digital inputs also be given a path to ground or  $V_{DD}$  through a 1mW resistor to prevent the accumulation of static charge if the PC card is unplugged from the system. In addition, in systems where the AGND to DGND connection is on a backplane, it is recommended that two diodes be connected in inverse parallel between AGND and DGND.

## INTERFACING TO MICROPROCESSORS

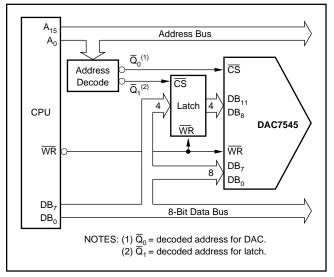

The DAC7545 can be directly interfaced to either an 8- or 16-bit microprocessor through its 12-bit wide data latch using the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  controls.

An 8-bit processor interface is shown in Figure 5. It uses two memory addresses: one for the lower 8 bits and one for the upper 4 bits of data into the DAC via the latch.

FIGURE 5. 8-Bit Processor Interface.

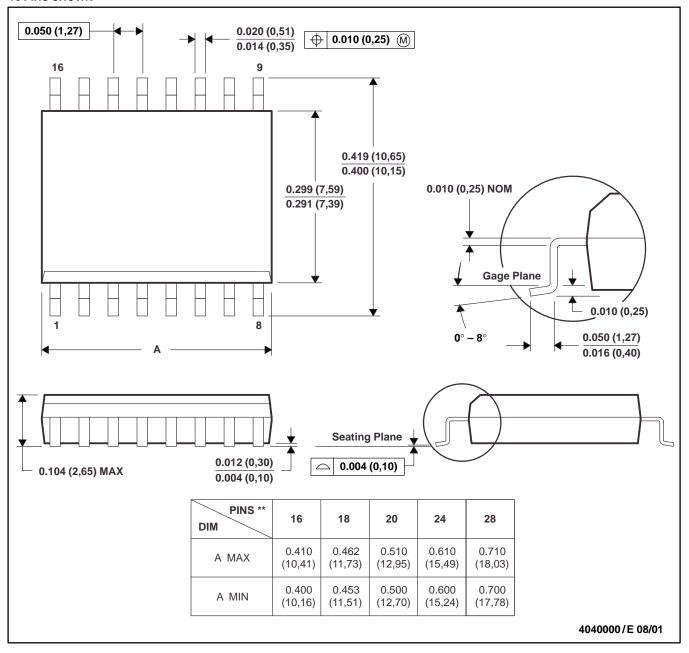

#### DW (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### **16 PINS SHOWN**

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated