# DP83924A Quad 10 Mb/s Ethernet Transceiver

### **General Description**

The Quad 10 Mb/s Ethernet Transceiver is a 4-Port ■ 100 pin package Encoder/Decoder (ENDEC) that includes all the circuitry required to interface four Ethernet Media Access Controllers (MACs) to 10BASE-T. This device is ideally suited for switch hub applications where 8, 16, 24, or 32 ports are commonly used.

The DP83924A has three dedicated 10BASE-T ports. There is an additional port that is selectable for either 10BASE-T or for an Attachment Unit Interface (AUI). In 10BASE-T mode, any port can be configured to be Half or Full Duplex. (Continued)

### **Features**

- 10BASE-T and AUI interfaces

- 4 ports TP interface with TRI-STATE control

- Single Full AUI and TP Interface on port 1 supports 50 meter drops

- Automatic or manual selection of twisted pair or Attachment Unit Interfaces on port 1

- Direct Interface to NRZ Compatible controllers

- MII-Like Management Interface (Continued)

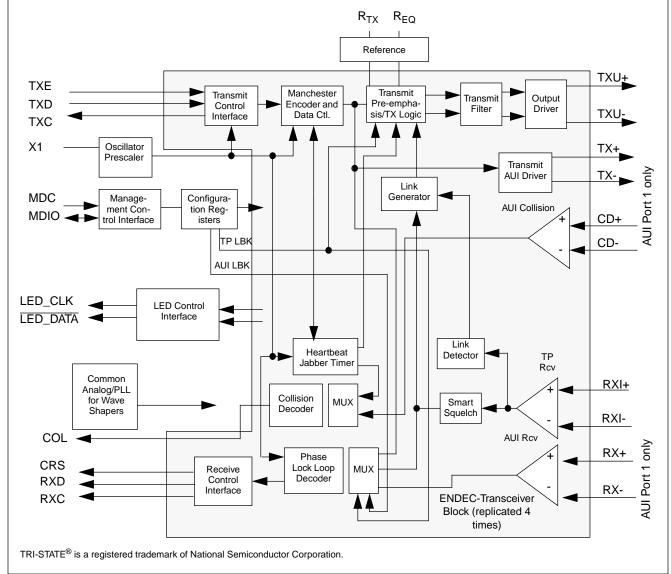

### System Diagram

### **General Description** (Continued)

The various modes on the transceivers can be configured and controlled via the MII management interface. This management interface makes inter-operability with other manufacturers MAC units relatively easy. If no management interface is desired, some of the critical operating modes of the transceiver can be set via strapping options (latching configuration information during reset). The ENDEC section of the transceiver also supplies a simple Non-Return-to-Zero (NRZ) interface to transmit and receive data to/from standard 10 Mb/s MACs.

The transceivers include on-chip filtered transmit outputs, which reduce emissions and eliminate the need for external filter modules.

### Features (Continued)

- Serial management interface for configuration and monitoring of ENDEC/Transceiver operation

- Twisted Pair Transceiver Module

- On-chip filters for transmit outputs

- Adjustable Equalization and Amplitude

- Low Power Driver

- Heartbeat and Jabber Timers

- Link Disable and Smart Receive Squelch

- Polarity detection and correction

- Jabber Enable/Disable

- ENDEC Module (one per port)

- Low Power Class AB Attachment Unit Interface (AUI)

Driver for one port

- Enhanced Supply Rejection

- Enhanced Jitter Performance

- Diagnostic ENDEC Loopback

- Squelch on Collision and Receive Pair

- Serial LED interface for LINK, POLARITY, ACTIVITY, and ERROR

- JTAG Boundary Scan per IEEE 1149.1

2

#### **Table of Contents** 1.0 Pin Connection Diagram .....4 Register Map and Descriptions ............................... 15 5.0 Interface Descriptions 8 2.1 Management Interface 8 2.0 AC and DC Electrical Specifications .................. 18 2.2 6.0 2.3 Detailed Functional Description ......12 3.0 3.1 Twisted Pair Functional Description ......12 3.2 3.3 Additional Features ......13

www.national.com

3

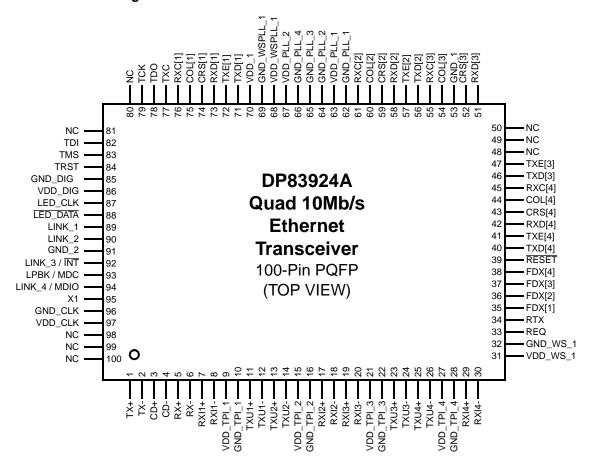

# 1.0 Pin Information

### 1.1 Pin Connection Diagram

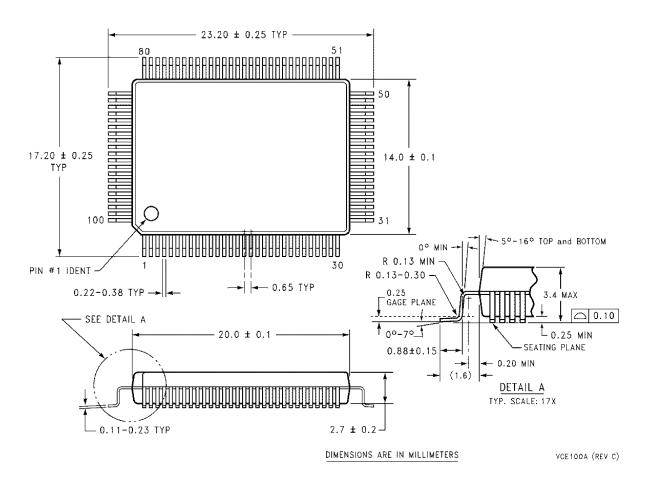

Order Number DP83924AVCE NS Package Number VCE100A

# 1.0 Pin Information (Continued)

# 1.2 Pin Description

**Table 1. NRZ CONTROLLER INTERFACE and MANAGEMENT INTERFACE:** These pins provide the interface signalling between the Media Access Controller and the transceiver. (30 Pins)

| Symbol                               | Pin #                | Type                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------|----------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXC                                  | 77                   | 0                                      | <b>Transmit Clock:</b> This pin outputs a 10 MHz output clock signal synchronized to the transmit data (one pin for all ports).                                                                                                                                                                                                                                                                                          |

| TXD[4]<br>TXD[3]<br>TXD[2]<br>TXD[1] | 40<br>46<br>56<br>71 | I                                      | Transmit Data: The serial TXD contains the transmit serial data output stream.                                                                                                                                                                                                                                                                                                                                           |

| TXE[4] TXE[3] TXE[2] TXE[1]          | 41<br>47<br>57<br>72 | I                                      | <b>Transmit Enable:</b> This active high input indicates the presence of valid data on the TXD pins.                                                                                                                                                                                                                                                                                                                     |

| CRS[4]<br>CRS[3]<br>CRS[2]           | 43<br>52<br>59       | O, pull-up<br>O, pull-up<br>O, pull-up | Carrier Sense: Active high output indicates that valid data has been detected on the receive inputs.  CRS[3:1] are dual purpose pins. When RESET is active, the value on these pins are                                                                                                                                                                                                                                  |

| CRS[1]                               | 74                   | O, pull-up                             | sampled to determine the transceiver address for the mgmt interface. These pins have internal pull-ups, a 2.7 k $\Omega$ pull down resistor is required to program a logic '0'.                                                                                                                                                                                                                                          |

| COL[4]                               | 44<br>54             |                                        | <b>Collision:</b> This active high output is asserted when a collision condition has been detected. It is also asserted for 1µs at the end of a packet to indicate the SQE test function.                                                                                                                                                                                                                                |

|                                      | 60<br>75             | O, pull-up<br>O, pull-up               | COL[4:1] are dual purpose pins. When $\overline{\text{RESET}}$ is active, these pins are sampled and selects the operating mode for the device. To select the non-default mode(s), a 2.7 k $\Omega$ pull down resistor(s) is required. The strappable functions are:                                                                                                                                                     |

|                                      |                      |                                        | COL[4]; selects the number of receive clocks after carrier sense deassertion (5 RXCs or continuous RXCs). Default is 5 RXCs. COL[3]; enables or disables the receive filter. Default is to disable the receive filter. COL[2]; selects the full duplex operating mode (normal or enhanced). Default is normal full duplex mode. COL[1]; selects the LED operating mode (normal or enhanced). Default is normal LED mode. |

| RXC[4]<br>RXC[3]<br>RXC[2]<br>RXC[1] | 45<br>55<br>61<br>76 | 0                                      | <b>Receive Clock:</b> This 10 MHz signal is generated by the transceiver, and is the recovered clock from the decoded network data stream. The number of RXCs after the deassertion of CRS is programmable via the Global Configuration Register, GATERXC bit, D0. The options are for 5 RXCs or continuous RXCs.                                                                                                        |

| RXD[4]<br>RXD[3]<br>RXD[2]<br>RXD[1] | 42<br>51<br>58<br>73 | 0                                      | Receive Data: Provides the decoded receive serial data. Data is valid on the rising edge of RXC.                                                                                                                                                                                                                                                                                                                         |

| MDC<br>LPBK                          | 93                   | I                                      | <b>Management Data Clock:</b> When "normal" full duplex mode is selected (strap option, COL[2]=1), this clock signal (0-2.5 MHz) is the clock for transferring data across the management interface.                                                                                                                                                                                                                     |

|                                      |                      |                                        | <b>LoopBack</b> : When "enhanced" full duplex mode is selected (strap option, COL[2]=0), then this pin is an active high input to configure all ports into diagnostic loopback mode.                                                                                                                                                                                                                                     |

| MDIO<br>LINK_4                       | 94                   | I/O                                    | <b>Management Data I/O:</b> When "normal" full duplex mode is selected (strap option, COL[2]=1), this Bidirectional signal transfers data on the management interface between the controller and the transceiver.                                                                                                                                                                                                        |

|                                      |                      |                                        | <b>Link Lost Status Port 4</b> : When "enhanced" full duplex mode is selected, (strap option, COL[2]=0), this pin outputs the link lost status for port 4. If link is lost, this output is high.                                                                                                                                                                                                                         |

| INT<br>LINK_3                        | 92                   | OD                                     | <b>Interrupt:</b> When "normal" full duplex mode is selected (strap option, COL[2]=1), this output pin is driven low when an interrupt condition is detected within the Quad Transceiver. An interrupt can occur when, link status changes or, LED status changes. This is an open-drain output. And requires an external pull-up resistor.                                                                              |

|                                      |                      |                                        | Link Lost Status Port 3: When "enhanced" full duplex mode is selected, (strap option, COL[2]=0), this pin outputs the link lost status for port 3. If link is lost, this output is high.                                                                                                                                                                                                                                 |

| LINK_2<br>LINK_1                     | 90<br>89             | 0                                      | <b>Link Lost Status Ports 1,2</b> : These pins indicate the link lost status for ports 1 and 2, when "enhanced" full duplex mode is selected.                                                                                                                                                                                                                                                                            |

# 1.0 Pin Information (Continued)

Table 2. NETWORK INTERFACES: Attachment Unit, Twisted Pair Interface (24 Pins)

| Symbol          | Pins       | Type   | Description                                                                                                                                                                                         |

|-----------------|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXI4+<br>RXI4-  | 29<br>30   | I      | <b>Twisted Pair Receive Input:</b> This differential input pair receives the incoming data from the twisted pair medium via an isolation transformer.                                               |

| RXI3+<br>RXI3-  | 19<br>20   |        |                                                                                                                                                                                                     |

| RXI2+<br>RXI2-  | 17<br>18   |        |                                                                                                                                                                                                     |

| RXI1+<br>RXI1-  | 7<br>8     |        |                                                                                                                                                                                                     |

| TXU4+<br>TXU4-  | 25<br>26   | 0      | UTP Transmit Outputs: This pair of drivers provide pre-emphasized and filtered differential output for UTP (100 $\Omega$ cable). These drivers maintain the same common mode                        |

| TXU3+<br>TXU3-  | 23<br>24   |        | voltage during data transmission and idle mode.                                                                                                                                                     |

| TXU2+<br>TXU2-  | 13<br>14   |        |                                                                                                                                                                                                     |

| TXU1+<br>TXU1-  | 11<br>12   |        |                                                                                                                                                                                                     |

| REQ             | 33         | I      | <b>Equalization Resistor:</b> An external resistor connects to ground to adjust the equalization on the twisted pair transmit outputs.                                                              |

| R <sub>TX</sub> | 34         | I      | <b>Transmit Amplitude Resistor:</b> An external resistor connects to ground to adjust the amplitude of the differential transmit outputs to the unshielded twisted pair cable.                      |

| Attachmen       | t Unit Int | erface |                                                                                                                                                                                                     |

| RX+<br>RX-      | 5<br>6     | I      | <b>Port 1 Full AUI Receive Input:</b> In AUI mode this differential input pair receives the incoming data from the AUI medium via an isolation transformer.                                         |

| TX+<br>TX-      | 1<br>2     | 0      | <b>Port 1 Full AUI Transmit Output:</b> In AUI mode this differential pair sends encoded data from the AUI transceiver. These outputs are source followers and require 270 Ohm pull down resistors. |

| CD+ CD-         | 34         | I      | <b>Port 1 Full AUI Collision Detect</b> : In AUI mode, this differential input pair receives the collision detect signals from the AUI medium via an isolation transformer.                         |

### Table 3. LED & GENERAL CONFIGURATION Pins (8 Pins)

| Symbol   | Pins      | Туре | Description                                                                                                                                                                                                       |

|----------|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED_DATA | 88        | 0    | <b>LED serial data output:</b> This output should be connected to the input of the 1st serial shift register.                                                                                                     |

| LED_CLK  | 87        | 0    | LED Clock: This is the clock for the serial shift registers.                                                                                                                                                      |

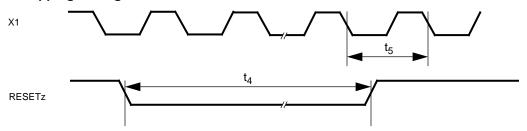

| X1       | 95        | I    | <b>External Oscillator Input:</b> This signal is used to provide clocking signals for the internal ENDEC. A 20 MHz oscillator module should be used to drive this pin.                                            |

| RESET    | 39        | I    | <b>Reset:</b> Active low input resets the transceiver, and starts the initialization of the device. This pin has a noise filter on it's input, which requires that the reset pulse must be greater than 30 TXC's. |

| FDX[4:1] | 38<br>-35 | I    | <b>Full Duplex:</b> This pin is sampled during reset. They control the full duplex (or half duplex) configuration of each port.                                                                                   |

# 1.0 Pin Information (Continued)

Table 4. SCAN TEST Pins (5 Pins)

| Symbol | Pins | Туре | Description                                                                                                                                                                                                           |

|--------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK    | 79   | I    | <b>Test Clock:</b> This signal is used during boundary scan to clock data in and out of the device.                                                                                                                   |

| TDI    | 82   | I    | <b>Test Input:</b> The signal contains serial data that is shifted into the device by the TAP controller. An internal pullup is provided if not used.                                                                 |

| TDO    | 78   | O,Z  | <b>Test Output:</b> The signal can be set to TRI-STATE and contains serial data that is shifted out of the device by the TAP controller.                                                                              |

| TMS    | 83   | I    | <b>Test Mode Select:</b> This selects the operation mode of the TAP controller. An internal pullup is provided if not used.                                                                                           |

| TRST   | 84   | I    | <b>Test Reset:</b> When this signal is asserted low, it forces the TAP (Test Access Port) controller into a logic reset state. An internal pullup is provided. This pin should be pulled low during normal operation. |

7

Table 5. POWER AND GROUND Pins (33 Pins)

Table 6. Pin Type Description

| Symbol                                           | Pins                                          | Туре | Description                              |

|--------------------------------------------------|-----------------------------------------------|------|------------------------------------------|

| NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC           | 48<br>49<br>50<br>80<br>81<br>98<br>99<br>100 | NA   | No Connect                               |

| VDD_TPI_4<br>VDD_TPI_3<br>VDD_TPI_2<br>VDD_TPI_1 | 27<br>21<br>15<br>9                           | Р    | Power for TPI Ports 1-4                  |

| GND_TPI_4<br>GND_TPI_3<br>GND_TPI_2<br>GND_TPI_1 | 28<br>22<br>16<br>10                          | G    | Ground for TPI Ports 1-4                 |

| VDD_PLL_2<br>VDD_PLL_1                           | 67<br>63                                      | Р    | Power for PLL Circuitry                  |

| GND_PLL_4<br>GND_PLL_3<br>GND_PLL_2<br>GND_PLL_1 | 66<br>65<br>64<br>62                          | G    | Ground for PLL Circuitry                 |

| VDD_WSPLL_1                                      | 68                                            | Р    | Power for Wave Shaper and PLL Circuitry  |

| GND_WSPLL_1                                      | 69                                            | G    | Ground for Wave Shaper and PLL Circuitry |

| VDD_WS_1                                         | 31                                            | Р    | Power for Wave Shaper Circuitry          |

| GND_WS_1                                         | 32                                            | G    | Ground for Wave Shaper<br>Circuitry      |

| VDD_DIG                                          | 86                                            | Р    | Power for Core Logic                     |

| GND_DIG                                          | 85                                            | G    | Ground for Core Logic                    |

| GND_CLK                                          | 96                                            | G    | Ground for Clock Circuitry               |

| VDD_CLK                                          | 97                                            | Р    | Power for Clock Circuitry                |

| GND_2<br>GND_1                                   | 91<br>53                                      | G    | Ground for NRZ Circuitry                 |

| VDD_1                                            | 70                                            | Р    | Power for NRZ Circuitry                  |

| Pin Type | Description                                                            |

|----------|------------------------------------------------------------------------|

| I        | Input Buffer                                                           |

| 0        | Output Buffer (driven at all times)                                    |

| I/O      | Bi-directional Buffer                                                  |

| O, Z     | Output Buffer with High Impedance Capability                           |

| OD       | Open Drain-Like Output. Either driven Low or to a High Impedance State |

www.national.com

### 2.0 Interface Descriptions

#### Interface Overview

The Quad Transceiver's interfaces can be categorized into the following groups of signals:

- Management Interface Allows host to read status and set operating modes.

- Media Access Control Interface Straight forward NRZ interface to Ethernet MACs.

- LED Interface Serial LED interface to off chip shift registers.

- 4. Network Interfaces Integrated 10BASE-T and AUI.

- 5. Clock Allows connection of an external clock module.

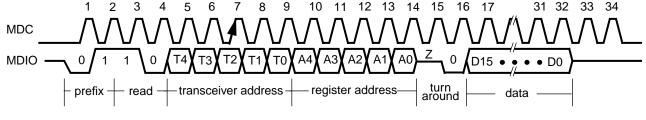

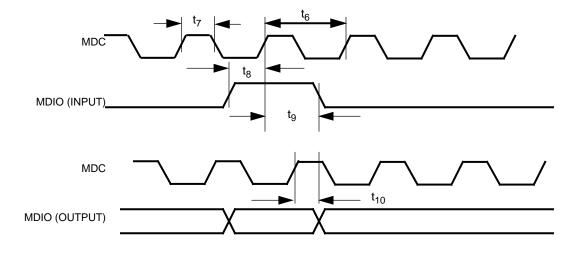

#### 2.1 Management Interface

This interface is a simple serial interface that is modeled after the MII standard serial interface, though it does not adhere to the MII standard completely (the protocol is followed, but the register space is not). The interface signals consist of a clock and data line for transfer of data to and from the registers.

In a multiple Quad Transceiver system, it is necessary to distinguish between the devices in order to access the correct registers for configuration and status information. This is accomplished by assigning each Quad Transceiver a unique transceiver address. The lower 3 bits of the transceiver address, T[2:0], is latched in during reset based on the logic state of CRS[3:1]. The upper 2 bits of the transceiver address, T[4:3], must be zero. Therefore, 32 ports can be supported with a single MII bus.

The register address field indicates which register within the DP83924A that is to be accessed (read or write).

During a write operation, all 32 bits are driven onto MDIO by the host, indicating which transceiver and register the data is to be written.

During a read operation, the first 14 bits are driven onto MDIO by the host, then the bus is released, allowing the DP83924A to drive the requested data onto MDIO.

The serial lines do not require any preamble on these pins, however if it is provided it is ignored so long as the 0110 or 0101 pattern is not present. If a continuous MDC is not supplied, then at the end of each command (read or write), 2 additional MDCs are required in order to allow the internal state machine to transition back to it's idle state. Refer to Figure 1.

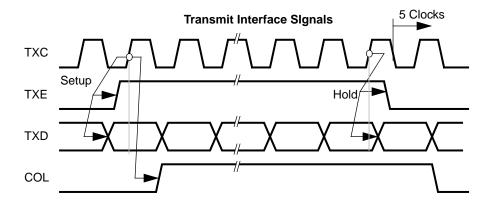

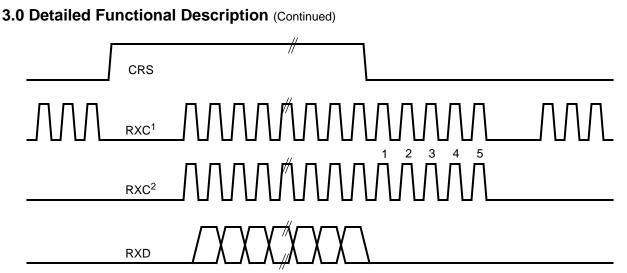

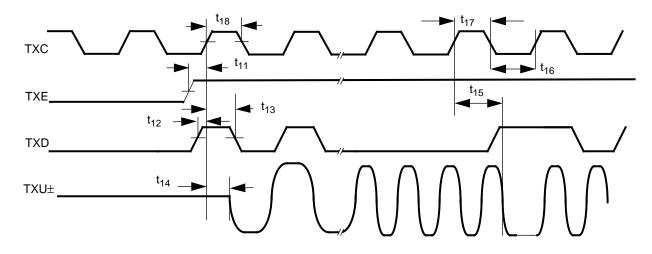

#### 2.2 MAC Interface

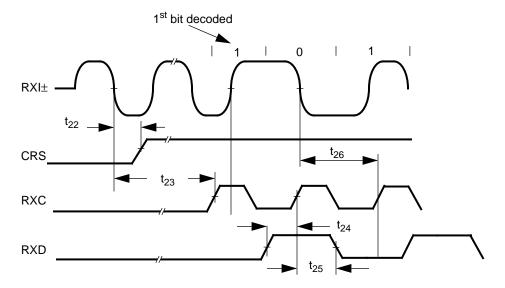

This interface connects the ENDEC/Transceiver to an Ethernet MAC controller. This interface consists of a serial data transmit interface and a serial receive interface. The interface clocks data out (on receive) or in (on transmit) on the rising edge of the clock. Refer to Figure 2. All signals are active high with rising edge sampling. The recovered clock (RXC) is selectable for 5 RXCs after the deassertion of carrier sense (CRS) or for continuous RXCs after the deassertion of CRS. This is programmable through the serial MII or through the COL[4] strapping option.

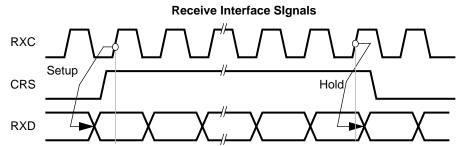

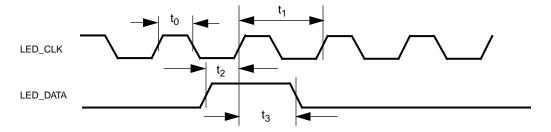

#### 2.3 LED Interface

The LED interface consists of two modes. The first option, normal LED mode, requires an external 8-bit shift register. During every LED update cycle, 8-bits are shifted out to the external shift registers. This allows two status LEDs per port. One LED indicates activity (Tx or Rx) and the second indicates port status (per Table 6). The LEDs attached to the shift register will be on, if the associated port has tx or rx activity. The status LEDs will blink at different rates depending on the associated ports status.

#### **Register Read**

Note 1: The management interface addressing includes a 5 bit field for the Transceiver Address, T[4:0], and a 5 bit field for the register address, A[4:0]. The MII assumes the transceiver address applies to a single port, but in this implementation a single address refers to a single IC. The transceiver address is set by 3 external pins, CRS[3:1]. T[4:3] must be zero to address the transceiver. Thus up to 32 10BASE-T ports can be addressed from a single interface (8 addr x 4 ports/addr).

Note 2: Two MDCs (clocks 33, 34) are required after each read or write in order to allow the internal state machine to transition back to it's IDLE state.

Figure 1. Serial Management Interface Timing Diagram (read/write)

8

### 2.0 Interface Descriptions (Continued)

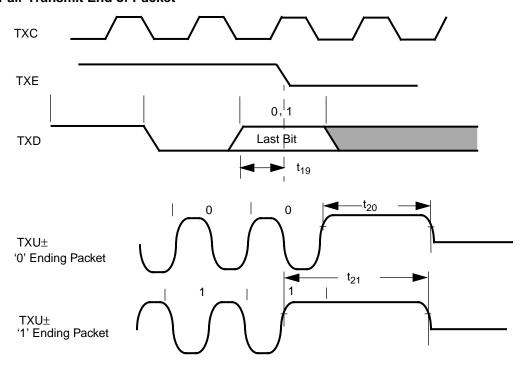

Figure 2. NRZ Interface Timing Diagram

Figure 3. Normal LED Mode Timing Diagram

If a port experiences both Bad Polarity and Link Lost, then the LEDs will go to the fast blink state (i.e. Link Lost). Port activity and status are shifted out serially, with port 1 shifted out first. The LED update rate is every 50 ms. The LED clock rate is 1 MHz. All port activity is extended to 50 ms to make it visible. Data is valid on the rising edge of LED\_CLK and is active low (LED on). Refer to Figure 3.

**Table 7. Normal LED Mode**

| LED Condition        | Status Indication |

|----------------------|-------------------|

| Off                  | Good Status       |

| On - Solid           | Error'd Status    |

| Fast Blink (400 ms)  | Link Lost         |

| Slow Blink (1600 ms) | Bad Polarity      |

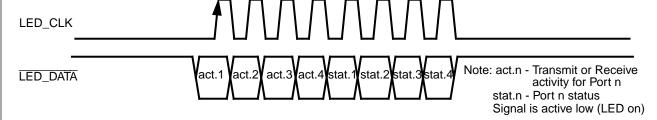

The second option, enhanced LED mode, serially shifts a 16-bit stream out of the Quad Transceiver. This option outputs per port data for Rx, Tx, Full Duplex (FDX), and Link-Coded status. These four bits per port are intended to be

used to support two LEDs. One is a bi-color LED (decode of the FDX and LinkCoded bits) to indicate LINK status. The second LED indicates activity (Tx or Rx). The Tx and Rx bits are not intended to be used as separate LEDs for transmit and receive activity. Refer to the User Information document regarding this mode. As with the first LED option, port 1 status is shifted out first. Refer to Figure 4.

Table 8. Enhanced LED Mode - Bit Decode

| FDX | LinkCoded | LED Status | Comments                  |

|-----|-----------|------------|---------------------------|

| 0   | 0         | OFF        | Link Fail, Full<br>Duplex |

| 0   | 1         | ON         | Good Link, Full<br>Duplex |

| 1   | 0         | ON         | Good Link, Half<br>Duplex |

| 1   | 1         | OFF        | Link Fail, Half<br>Duplex |

### 2.0 Interface Descriptions (Continued)

Figure 4. Enhanced Mode LED Timing Diagram

To select the desired LED mode, the COL [1] pin has a strapping feature. If COL[1] is a logic '0' during reset, then "enhanced" LED mode is enabled. If COL[1] is a logic '1' during reset, then "normal" LED mode is enabled.

#### 2.4 Network Interface

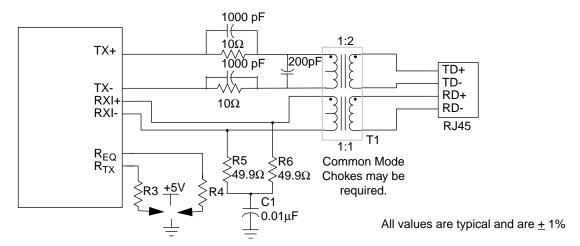

#### 2.4.1 Twisted Pair Interface

The Quad 10 Mb/s Transceiver provides two buffered and filtered 10BASE-T transmit outputs (for each port) that are connected to the output isolation transformer via two impedance matching resistor/capacitor networks. See Figure 5. The twisted pair receiver implements an intelligent receive squelch on the RXI+ differential inputs to ensure that impulse noise on the receive inputs will not be

mistaken for a valid signal. This smart squelch circuitry (which is described in detail under the Functional Description) employs a combination of amplitude and timing measurements to determine the validity of data on the twisted pair inputs. Only after these conditions have been satisfied will Carrier Sense (CRS) be generated to indicate that valid data is present.

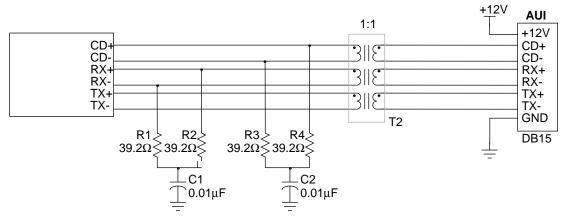

#### 2.4.2 Attachment Unit Interface

A single port (port 1) on the transceiver has a separate (non- multiplexed) AUI interface. This interface is a full 802.3 standard AUI interface capable of driving the full 50m cable. The schematic for connecting this interface to the AUI connector is shown in Figure 6.

Figure 5. Twisted Pair Interface Schematic Diagram

### 2.0 Interface Descriptions (Continued)

Figure 6. Full AUI Interface Schematic

If the standard  $78\Omega$  transceiver cable is used, the receive differential input must be externally terminated with two  $39\Omega$  resistors connected in series. In thin Ethernet applications, these resistors are optional. To prevent noise from falsely triggering the decoder, a squelch circuit at the input rejects signals with levels less than -175 mV. Signals more negative than -300 mV are decoded.

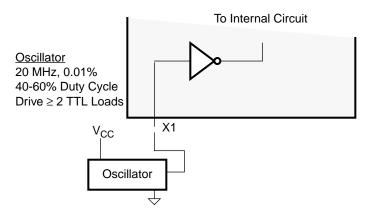

#### 2.4.3 Oscillator Clock

When using an oscillator, additional output drive may be necessary if the oscillator must also drive other components. The X1 pin is a simple TTL compatible input. See Figure 7.

Figure 7. External Oscillator Connection Diagram

### 3.0 Detailed Functional Description

This product utilizes the standard 10BASE-T and AUI interface core building blocks which are replicated on this device, one per port. The basic function of these blocks are described in the following sections. Also described are the common digital blocks. Refer to the "System Diagram" on page 1.

#### 3.1 Twisted Pair Functional Description

#### 3.1.1 Smart Squelch

The Smart Squelch is responsible for determining when valid data is present on the differential receive inputs (RXI±). The Twisted Pair Transceiver (TPT) implements an intelligent receive squelch on the RXI± differential inputs to ensure that impulse noise on the receive inputs will not be mistaken for a valid signal.

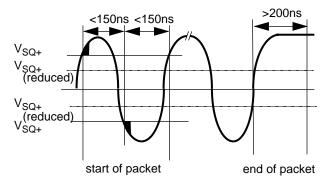

The squelch circuitry employs a combination of amplitude and timing measurements to determine the validity of data on the twisted pair inputs. The operation of the smart squelch is shown in Figure 8.

Figure 8. Twisted Pair Squelch Operation Diagram

The signal at the start of packet is checked by the smart squelch and any pulses not exceeding the squelch level (either positive or negative, depending upon polarity) will be rejected. Once this first squelch level is overcome correctly the opposite squelch level must then be exceeded within 150ns. Finally, the signal must exceed the original squelch level within an additional 150ns to ensure that the input waveform will not be rejected. The checking procedure results in the loss of typically three bits at the beginning of each packet.

Only after all these conditions have been satisfied will a control signal be generated to indicate to the remainder of the circuitry that valid data is present. At this time, the smart squelch circuitry is reset.

Valid data is considered to be present until squelch level has not been generated for a time longer than 150ns, indicating End of Packet. Once good data has been detected the squelch levels are reduced to minimize the effect of noise causing premature End of Packet detection.

#### 3.1.2 Collision Detect

A collision is detected on the twisted pair cable when the receive and transmit channels are active simultaneously. If the ENDEC is receiving when a collision is detected (AUI only) it is reported to the MAC block immediately (through the COL signal). If, however, the ENDEC is transmitting when a collision is detected the collision is not reported until seven bits have been received while in the collision state. This prevents a collision being reported incorrectly

due to noise on the network. The COL signal remains for the duration of the collision.

Approximately 1µsec after the tansmission of each packet a signal called the Signal Quality Error (SQE) consisting of typically 10 cycles of a 10 MHz signal is generated by the transceiver. This 10 MHz signal, also called the Heartbeat, assures the continued functioning of the collision circuitry. The SQE signal is passed on to the MAC via the COL signal and is represented as a pulse.

#### 3.1.3 Link Detector/Generator

The link generator is a timer circuit that generates a link pulse as defined by the 10BASE-T specification that will be sent by the transmitter section. The pulse which is 100ns wide is transmitted on the transmit output, every 16ms, in the absence of transmit data. The pulse is used to check the integrity of the connection to the remote MAU.

The link detection circuit checks for valid pulses from the remote MAU and if valid link pulses are not received the link detector will disable the twisted pair transmitter, receiver and collision detection functions.

#### 3.1.4 Jabber

The Jabber function disables the transmitter if it attempts to transmit a much longer than legal sized packet. The jabber timer monitors the transmitter and disables the transmission if the transmitter is active for greater than 20-30ms. The transmitter is then disabled for the entire time that the ENDEC module's internal transmit is asserted. The transmitter signal has to be deasserted for approximately 400-600 ms (the unjab time) before the Jabber re-enables the transmit outputs.

There is also a jabber disable bit in each of the port control/status registers which when activated, disables the jabber function.

#### 3.1.5 Transmit Driver

The transmit driver function utilizes the internal filters to provide a properly matched and wave shaped output which directly drives the isolation transformer/choke.

#### 3.1.6 Transmit Filter

There is no need for external filters on the twisted pair transmit interface because the filters are integrated. Only an isolation transformer and impedance matching resistors are needed for the transmit twisted pair interface (see Figure 5). The transmit filter ensures that all the harmonics in the transmit signal are attenuated by at least 27dB. The transmit signal requires a 1:2 (1 on the chip side and 2 on the cable side) isolation transformer.

#### 3.2 ENDEC Module

The ENDEC consists of two major blocks:

- The Manchester encoder accepts NRZ data from the controller, encodes the data to Manchester, and transmits it differentially to the transceiver, through the differential transmit driver.

- The Manchester decoder receives Manchester data from the transceiver, converts it to NRZ data and recovers clock pulses and sends them to the controller.

#### 3.2.1 Manchester Encoder and Differential Driver

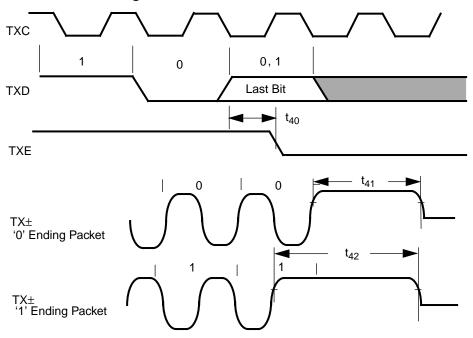

The encoder begins operation when the Transmit Enable input (TXE) goes high and converts the clock and NRZ data to Manchester data for the transceiver. For the dura-

### 3.0 Detailed Functional Description (Continued)

tion of TXE remaining high, the Transmit Data (TXD) is encoded for the transmit-driver pair (TX±). TXD must be valid on the rising edge of Transmit Clock (TXC). Transmission ends when TXE goes low. The last transition is always positive; it occurs at the center of the bit cell if the last bit is a one, or at the end of the bit cell if the last bit is a zero.

#### 3.2.2 Manchester Decoder

The decoder consists of a differential receiver and a PLL to separate the Manchester encoded data stream into internal clock signals and data. Once the input exceeds the squelch requirements, Carrier Sense (CRS) is asserted off the first edge presented to the decoder. Once the decoder has locked onto the incoming data stream, it provides data (RXD) and clock (RXC) to the MAC.

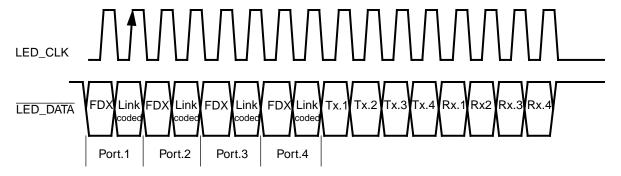

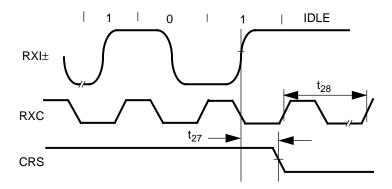

The decoder detects the end of a frame when no more mid-bit transitions are detected. Within one and a half bit times after the last bit, carrier sense is de-asserted. Receive clock stays active for at least five more bit times after CRS goes low, to guarantee the receive timings of the controller.

The GATERXC bit, D0, in the Global Control and Status Register, controls the receive clock (RXC) gated function. This allows the selection between 5 RXCs after the deassertion of carrier sense (CRS) or continuous RXCs after the deassertion of CRS. The GATERXC function which is programmable through the serial management interface is also available via a strap option. The default mode is to enable 5 RXCs after the deassertion of CRS. If a 2.7 k resistor is connected to the COL[4] pin (and the device reset), then the continuous RXCs mode is enabled. If the GATERXC mode is configured through the strap option, a register write via the serial management interface to the GATERXC control bit in the Global Control Register will be ignored (this bit only). A read of this register will always show the default value for this bit (5 RXCs) even though continuous RXCs may have been programmed through the strap option. All other bits are read/write as normal.

#### 3.2.3 Collision Translator

When in AUI Mode and the external Ethernet transceiver detects a collision, it generates a 10 MHz signal to the differential collision inputs (CD  $\pm$ ) of the Quad Transceiver. When these inputs are detected active, the transceiver asserts COL which signals the MAC controller to back off its current transmission and reschedule another one.

The differential collision inputs are terminated the same way as the differential receive inputs. The squelch circuitry is the same, rejecting pulses with levels less than -175 mV.

#### 3.3 Additional Features

#### 3.3.1 Transceiver Loopback

When diagnostic loopback is programmed (in twisted pair mode), the transceiver redirects its transmitted data back into its receive path. The transmit driver and receive input circuitry are disabled in diagnostic loopback mode, hence, the transceiver is isolated from the network cable. This allows for diagnostic testing of the data path all the way up to the transceiver without transmitting or being interrupted by the media. This test can be performed regardless of the link status (i.e. a twisted pair cable does not have to be connected to perform transceiver loopback).

#### 3.3.2 AUI/TP AutoSwitching - Port 1

The AUI/TP autoswitching lets the transceiver auto-switch between the AUI and TP outputs. At power up, the autoswitch function is enabled (AUTOSW bit = 1). When the auto-switch function is enabled, it allows the transceiver to automatically switch between TP and AUI outputs. If there is an absence of link pulses, the transceiver will switch to AUI mode. Similarly, when the transceiver starts detecting link pulses it will switch to TP mode. The switching from one mode to the next is only done after the current packet has been transmitted or received. If the twisted pair output is jabbering and it gets into the link fail state, then the switch to AUI mode is made only after the jabbering has stopped (this includes the time it takes to unjab). Also, if TP mode is selected, transmit packet data will only be driven by the twisted pair outputs and the AUI transmit outputs will remain idle. Similar behavior applies when AUI mode is selected. In TPI mode, the twisted pair drivers will continue to send link pulses, however, no packet data will be transmitted. It must also be noted that when switching from TP to AUI mode, it might take a few msec to completely power-up the AUI before it becomes fully operational. Switching in the opposite direction (AUI to TP) does not have this power-up time, since the TP section is already powered (the twisted pair transmit section still sends link pulses in AUI mode).

### 3.3.3 Full Duplex Mode

The full duplex mode is supported by the transceiver being able to simultaneously transmit and receive without asserting collision. The ENDEC has been implemented such that it can encode and decode simultaneously and also be robust enough to reject crosstalk noise with both transmit and receive channels enabled.

The full duplex feature has two modes of operation. The first option (normal FDX mode), allows full duplex configuration of the ports only after a reset (through the FDX[4:1] pins). The FDX[4:1] pins are sampled during reset to determine which ports to configure into full duplex mode. Changing the logic state on the FDX[4:1] pins will not take affect until a reset is performed. A logic '0' enables full duplex and a logic '1' enables simplex mode. In addition, the full duplex capability of a port can also be changed dynamically by writing the FDX bit (D12) of the Port Control Register via the Mgmt Interface.

The second option (enhanced FDX mode), allows changing the full duplex configuration of each port dynamically through the FDX[4:1] pins. As soon as the logic state on the FDX[4:1] pins are changed, the corresponding ports full duplex mode will be enabled or disabled.

In order to select the desired full duplex mode, the COL[2] pin has a strapping feature. The default is normal full duplex mode. If enhanced full duplex mode is desired, then a 2.7k pull-down resistor is required on the COL[2] pin. During reset, the COL[2] pin is sampled to determine the correct full duplex mode configuration.

Regardless of the full duplex mode, the logic state of the FDX[4:1] pins are sampled during reset to determine a port's initial configuration for full duplex capability.

Note 1: Continuous receive clock mode. In this mode, when CRS is deasserted, at least 5 RXCs are generated. RXC will go to idle until the RXC can be switched to an internal free running 10 MHz signal. Conversely, when CRS is asserted, RXC will go to idle. It remains idle until the decoder is able to lock onto the incoming data stream and generate the recovered clock.

Note 2: 5 Receive clock mode. In this mode, when CRS deasserts, at least 5 RXCs are generated before RXC goes to idle. RXC will remain in idle until the next received packet.

Figure 9. Receive Clock Timing - 5 RXC Mode vs Continuous RXC Mode

### 3.3.4 JTAG Boundary Scan

The DP83924A supports JTAG Boundary Scan per IEEE 1149.1 via test clock (TCK), test data input (TDI), test data output (TDI), test mode select (TMS), and test reset (TRST).

#### 3.3.5 Strapping Options

Table 9 shows the various strapping options and the associated pins used to configure the device at power-up. These pins are sampled during reset. These pins have internal pull-ups, if the default modes are desired, no external resistors are required. A 2.7 k $\Omega$  pull down resistor(s) are required to select non-default modes. If some type of control logic is used to select the non-default modes, instead of pull down resistors, then the level on the strapping pins must be maintained for approximately 10 clocks after the  $\overline{\text{RESET}}$  signal deasserts.

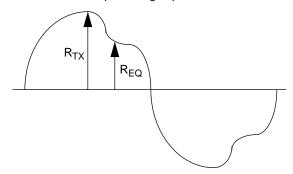

#### 3.3.6 R<sub>EQ</sub> and R<sub>TX</sub>

These pins can change the twisted pair differential output voltage amplitude. By adding pull-up resistors, the differential output voltage will increase. And adding pull down resistors, the differential output voltage will decrease.  $R_{TX}$  controls the amplitude of the output waveform and  $R_{EQ}$  controls the waveform equalization (pre-emphasis, location

of the knee in a 5M waveform). If resistors are used to change the differential output voltage, then it is recommended that the same value resistor be used for both pins and both pins are either pulled-up or pulled-down. All IEEE transmitter electrical characteristics should be verified after adding resistors to  $R_{EQ}$  and  $R_{TX}.$  Based on device characterization, it is recommended that 47  $k\Omega$  pull down resistors be used for both  $R_{EQ}$  and  $R_{TX}$  in order to meet the IEEE 802.3 differential output voltage specification.

Figure 10. 5M Waveform Differential Output Voltage

**Table 9. Strapping Option Description**

| Pin Name | Function                    | Default '1' | <b>'0'</b>  | Comments                                                                  |

|----------|-----------------------------|-------------|-------------|---------------------------------------------------------------------------|

| COL[4]   | Gate RXC                    | 5 RXCs      | Continuous  | Selects the # of RXCs after CRS deassertion                               |

| COL[3]   | Rx Filter Select            | Disabled    | Enabled     | Enables/disables the Rx filter. Suggest enable                            |

| COL[2]   | Full Duplex Mode Select     | Normal      | Enhanced    | Selects normal or enhanced full duplex mode                               |

| COL[1]   | LED Mode Select             | Normal      | Enhanced    | Selects normal or enhanced LED mode                                       |

| CRS[3:1] | Transceiver Address Select  | Address     | Address     | Sets the tcvr's address for MII access                                    |

| FDX[4:1] | Per Port Full Duplex Select | None        | Full Duplex | Selects full or half duplex configuration per port (no internal pull-ups) |

# 4.0 Register Descriptions

### 4.1 Register Map and Descriptions

The following is an overall register map for the transceiver/ENDEC. There are two groups of registers. The first group provides individual port control which configures and reports status for functions applicable on a port basis. The second group provides global control which enables configuration of operations that are common to all the ports.

Table 10. DP83924A Register Map Accessible via the Management Interface

| Register Address | Name                      | Description                                                                                       | Access |

|------------------|---------------------------|---------------------------------------------------------------------------------------------------|--------|

| 00H              | Port 1 Control/Status     | Configuration setting and Operational Status for Port 1.                                          | R/W    |

| 01H              | Port 2 Control/Status     | Configuration setting and Operational Status for Port 2.                                          | R/W    |

| 02H              | Port 3 Control/Status     | Configuration setting and Operational Status for Port 3.                                          | R/W    |

| 03H              | Port 4 Control/Status     | Configuration setting and Operational Status for Port 4.                                          | R/W    |

| 04H - 07H        | Reserved                  | reserved                                                                                          | R      |

| 08H              | Global Control and status | Provides global reset and interrupt configuration capabilities.                                   | R/W    |

| 09H - 1EH        | Reserved                  | reserved                                                                                          | R      |

| 1FH              | Test Control              | Controls test functions for manufacturing test of the device. User MUST NOT access this register. | R/W    |

### Table 11. Port N Control/Status Register, addr = 00h - 03h (port 1 to port 4)

| D15 | D14  | D13  | D12 | D11  | D10  | D9   | D8     | D7  | D6   | D5   | D4   | D3   | D2    | D1     | D0     |

|-----|------|------|-----|------|------|------|--------|-----|------|------|------|------|-------|--------|--------|

| RST | LPBK | resv | FDX | JABE | resv | resv | LNKDIS | ERR | resv | resv | resv | resv | POLST | LNK ST | JAB ST |

This register controls the various operating modes available for the transceiver and ENDEC functions. There is one register per ENDEC/Transceiver on this device.

| Name   | Bit   | Reset<br>(Default)<br>Value | Description                                                                                                                                                                                                                                       | Туре |

|--------|-------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| RST    | D15   | 0                           | <b>Software Reset/Enable:</b> If this bit is set, then this port's transceivers and ENDEC modules are reset back to their idle state. If this bit is reset, then normal operation is expected.                                                    | R/W  |

| LPBK   | D14   | 0                           | <b>Loopback Transceiver:</b> If this bit is set, then this port's 10base-T transceiver will loop data from near the network interface pins back to the MAC, to test the operation of the transceiver. If this bit is reset, loopback is disabled. | R/W  |

| resv   | D13   | 0                           | Reserved: Must be written with '0'.                                                                                                                                                                                                               | R/W  |

| FDX    | D12   | strap                       | Full Duplex Operation: If this bit is set, then the ports full duplex capability is enabled. If this bit is reset, then half-duplex is enabled.                                                                                                   | R/W  |

| JABE   | D11   | 1                           | <b>Jabber Enable:</b> If this bit is set, then the ports jabber function is enabled. If this bit is reset, then the jabber feature is disabled.                                                                                                   | R/W  |

| resv   | D10-9 | 0                           | Reserved: Must be written with '0'.                                                                                                                                                                                                               | R    |

| LNKDIS | D8    | 0                           | <b>Link Disable:</b> If this bit is set, this port's link detection circuitry will be disabled. If this bit is reset, then normal link operation is enabled.                                                                                      | R/W  |

| ERR    | D7    | 0                           | <b>LED Error</b> : If this bit is set, this port's status LED will go solid. If this bit is reset, normal LED operation is resumed.                                                                                                               | R/W  |

| resv   | D6-3  | 0                           | Reserved: Must be written with '0'.                                                                                                                                                                                                               | R    |

| POL ST | D2    | 1                           | <b>Polarity Status</b> : This bit is set when bad polarity has been detected. Status bit, read-only.                                                                                                                                              | R    |

| LNK ST | D1    | 1                           | Link Status: This bit is set when the port is in the link-fail state. Status bit, read-only.                                                                                                                                                      | R    |

| JAB ST | D0    | 0                           | <b>Jabber Status</b> : This bit is set when the port is in the jabber condition. Status bit, read-only.                                                                                                                                           | R    |

# 4.0 Register Descriptions (Continued)

### Table 12. Global Control/Mask Register, addr = 08h

| D15  | D14  | D13       | D12    | D11    | D10  | D9      | D8   | D7   | D6   | D5   | D4   | D3   | D2   | D1        | D0      |

|------|------|-----------|--------|--------|------|---------|------|------|------|------|------|------|------|-----------|---------|

| resv | resv | LNKJABINT | AUTOSW | TPIAUI | HBEN | ENPOLSW | resv | resv | resv | resv | resv | resv | KLED | LJINTMASK | GATERXC |

This register controls the various operating modes available for the transceiver and ENDEC functions. This register will affect the operation of ALL ports of the DP83924A.

| Name      | Bit    | Reset<br>(Default)<br>Value | Description                                                                                                                                                                                                           | Туре |

|-----------|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| resv      | D15-14 | 0                           | Reserved: Must be written with '0'.                                                                                                                                                                                   | R    |

| LNKJABINT | D13    | 0                           | <b>Link Jabber Interrupt Status</b> : This bit is set when an interrupt occurs due to a link status change or a jabber condition on any port. This bit is cleared on a register read (the interrupt is also cleared). | R    |

| AUTOSW    | D12    | 1                           | <b>Auto Switching</b> : If this bit is set, automatic selection of TPI or AUI on port 1 is nabled. If this bit is reset, port 1 configuration is determined by the TPIAUI bit.                                        |      |

| TPIAUI    | D11    | 1                           | <b>TPI Select</b> : If this bit is set, then port 1 is placed into TP mode. If this bit is reset, then port 1 is configured for AUI mode.                                                                             | R/W  |

|           |        |                             | This bit is ignored if the AUTOSW bit is set.                                                                                                                                                                         |      |

| HBEN      | D10    | 1                           | <b>Hearbeat Enable</b> : If this bit is set, then heartbeat is enabled. If this bit is reset, it is disabled for all ports.                                                                                           | R/W  |

| ENPOLSW   | D9     | 1                           | <b>Enable Polarity Switching</b> : If this bit is set, then auto polarity detection and correction is enabled for all ports. If this bit is reset, it is disabled.                                                    | R/W  |

| resv      | D[8:3] | 0                           | Reserved: Must be written with '0'.                                                                                                                                                                                   | R    |

| KLED      | D2     | 0                           | <b>Enhanced LED Mode</b> : If this bit is set, "enhanced" LED mode is selected. If this bit is reset, "normal" LED mode is selected.                                                                                  | R/W  |

| LJINTMASK | D1     | 0                           | <b>Link Jabber Interrupt Mask</b> : If this bit is set, an interrupt will NOT be generated on a link-fail or jabber condition experienced on any port. If this bit is reset, interrupt generation is enabled.         | R/W  |

| GATERXC   | D0     | 1                           | RXC Gated: If this bit is set, five RXC clocks are forced after CRS is deasserted. If this bit is reset, then RXC clocks are continuous after CRS deasserts.                                                          | R/W  |

### 5.0 Application Information

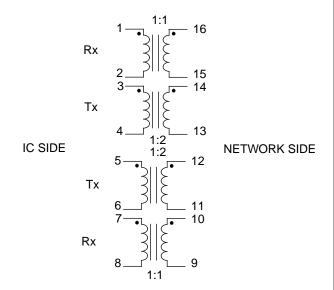

### 5.1 Magnetics Specifications

This section describes the required magnetics to be used with the Quad Transceiver. The external filter/transformer used in conventional twisted pair ports is now replaced by a transformer. By integrating the transmit filter, the transformer is the only magnetics required. In this configuration, a transformer with 1:2 turn ratio on the transmit path and a 1:1 turn ratio on the receive path is required. The system designer must determine if a choke is required. Careful layout may eliminate the need.

The following is a list of suppliers that may provide magnetic components with the electrical specifications listed in Table 13. This is not an exclusive list, and National Semiconductor makes no warranty as to the suitability of any of the magnetics. It is the responsibility of the user to verify the performance of any magnetics prior to production use.

BEL FUSE HALO Electronics PCA PULSE Engineering VALOR Electronics

**Table 13. Transformer Electrical Specifications**

| Parameter                                    | Pins                                                                        | Value                |

|----------------------------------------------|-----------------------------------------------------------------------------|----------------------|

| Open Circuit In-                             | 3-4, 5-6                                                                    | 50 μH (min)          |

| ductance (OCL)                               | 1-2, 7-8, 9-10, 11-<br>12, 13-14, 15-16.                                    | 200 μH (min)         |

| Inter-winding Capacitance (C <sub>ww</sub> ) | 1-2 to 15-16,<br>3-4 to 13-14<br>5-6 to 11-12<br>7-8 to 9-10                | 12 pF (max)          |

| Leakage Inductance (LL)                      | 1-2, short 15-16<br>3-4, short 13-14<br>5-6, short 11-12<br>7-8, short 9-10 | 0.3 μH (max)         |

| DC Resistance                                | 3-4, 5-6                                                                    | 0.35Ω (max)          |

| (DCR)                                        | 1-2, 7-8, 9-10, 15-<br>16.                                                  | 0.5Ω (max)           |

|                                              | 11-12, 13-14                                                                | 1.0Ω (max)           |

| High Potential                               | 1-2 to 15-16<br>3-4 to 13-14<br>5-6 to 11-12<br>7-8 to 9-10                 | 2000 Vrms for 1 min. |

#### 5.2 Layout Considerations

#### **Power Plane**

- Minimize signal traces which traverse across multiple islands to reduce reflections and impedance mismatches.

Therefore, the ground should extend from the DP83924A to under the magnetics (transformer).

- Use a single power plane.

### **Ground Plane**

— Use a single ground plane, similar to the Power Plane.

#### **DP83924A Placement and Routing**

The DP83924A should be placed as close as possible to the external transformer module/RJ45 connector.

**Figure 11. Typical Dual Transformer Pinout**

Each trace of a differential pair (i.e. TX+, TX-) between the DP83924A and the transformer module should be as follows:

$Rx \pm pair$  trace lengths should be matched. The width should be 8 mils min, with a trace-to-trace spacing of 8 mils min.

Tx  $\pm$  pair trace lengths should be matched. The width should be 15 mils min, with a trace-to-trace spacing of 15 mils min (if the total trace length between the DP83924A and the RJ45 connector is less than 1.5", then 8 mil spacing and width can be used).

The Tx and Rx spacing should be 15 mils min.

- The source termination (R,C) must be placed as close to the device as possible.

- 100 $\Omega$  traces between the transformer module and the RJ45 connector.

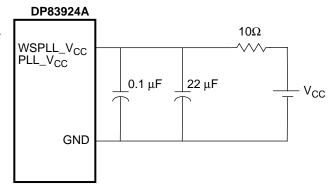

#### **Analog Power and Ground Circuit**

Recommended Low Pass Filter for the Internal PLL and WSPLL Circuitry to eliminate any power supply injected noise. This applies to both the PLL and WS supply pins. This should improve jitter performance. Refer to Figure 10 and Figure 11.

Bypass for all other supplies should use a 0.01  $\mu F$  capacitor. Additional bypass for the VDD\_TPI supplies should use a 1.0  $\mu F$  capacitor.

Figure 12. WSPLL and PLL  $V_{CC}$  Circuit Diagram

# 6.0 AC and DC Electrical Specifications

### **Absolute Maximum Ratings**

# **Recommended Operating Conditions**

Supply Voltage (V<sub>CC</sub>) -0.5V to +7.0VSupply voltage (V<sub>CC</sub>) 5 Volts ± 5% DC Input Voltage (V<sub>IN</sub>) -0.5V to  $V_{CC} + 0.5V$

DC Output Voltage (V<sub>OUT</sub>) -0.5V to  $V_{CC} + 0.5V$

Storage Temperature Range (T<sub>STG</sub>) -65°C to + 150°C

Power Dissipation (PD) 1.6W

Lead Temperature (TL) 260°C

(Soldering, 10 sec.)

**ESD** Rating 1.5 kV

$(R_{ZAP} = 1.5k, C_{ZAP} = 120 pF)$

**Ambient Temperature** 0°C to 70°C

Note: Absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits.

# **DC Specifications** $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = 5V \pm 5\%$ .

| Symbol             | Parameter                                       | Conditions                                     | Min          | Max        | Units |

|--------------------|-------------------------------------------------|------------------------------------------------|--------------|------------|-------|

| DIGITAL            | PINS (LED_CLK, LED_DATA, MDIO, MDC, CRS,        | RXC,RXD,COL,TXE,TXD,TXC,X1,RESET,LINK, IN      | T,TCK,TDI,TI | DO,TMS,TRS | т)    |

| V <sub>OH1</sub>   | Minimum High Level Output Voltage               | I <sub>OH</sub> = -2 mA (Except MDIO and INTz) | 3.0          |            | V     |

| V <sub>OH2</sub>   | Minimum High Level Output Voltage               | I <sub>OH</sub> = -8 mA (MDIO Only)            | 3.0          |            | V     |

| V <sub>OL1</sub>   | Maximum Low Level Output Voltage                | I <sub>OL</sub> = 2 mA (except MDIO and INTz)  |              | 0.4        | V     |

| V <sub>OL2</sub>   | Maximum Low Level Output Voltage                | I <sub>OL</sub> = 8 mA (MDIO and INTZ Only)    |              | 0.4        | V     |

| V <sub>IH</sub>    | Minimum High Level Input Voltage                |                                                | 2.0          |            | V     |

| V <sub>IL</sub>    | Maximum Low Level Input Voltage                 |                                                |              | 0.8        | V     |

| I <sub>IN</sub>    | Pull-up Resistor Current (Note 1, 3)            | V <sub>IN</sub> = GND, V <sub>CC</sub> =5V     | -250         | -100       | μΑ    |

| I <sub>IL</sub>    | Input Leakage (Note 2)                          | V <sub>IN</sub> = V <sub>CC</sub> or GND       | -10          | 10         | μΑ    |

| I <sub>OZ</sub>    | TRI-STATE Output Leakage Current                | V <sub>OUT</sub> = V <sub>CC</sub> or GND      | -10          | 10         | μΑ    |

| I <sub>CC</sub>    | Average Operating Supply Current                | TXU ± Transmitting into 50Ω (Note 4)           |              | 320        | mA    |

| AUI INTE           | ERFACE PINS (TX±, RX±, and CD±)                 |                                                |              |            |       |

| V <sub>OD</sub>    | Diff. Output Voltage (TX±)                      | 78Ω Termination                                | ± 550        | ± 1200     | mV    |

| V <sub>DS</sub>    | Diff. Squelch Threshold (RX± and CD±)           |                                                | -160         | -300       | mV    |

| TWISTE             | D PAIR INTERFACE PINS                           |                                                |              |            |       |

| V <sub>ODT</sub>   | TXU <u>+</u> Differential Output Voltage        | 100Ω Load @RJ45 Connector                      | 4.4          | 5.6        | Vp-p  |

| V <sub>SRON1</sub> | Receive Threshold Turn-On Voltage 10BASE-T Mode |                                                | ± 300        | ± 585      | mV    |

| V <sub>SROFF</sub> | Receive Threshold Turn-Off Voltage              |                                                | ± 175        | ± 300      | mV    |

Note 1: CRS[4:1], COL[4:1], TDI, TMS, TRST

Note 2: MDIO, MDC, TXE[4:1]. TXD[4:1], X1, RESET, TCK

Note 3: Internal pull-up resistor typically 20 k $\Omega$  - 50 k $\Omega$

Note 4: This includes the current consumed off chip by the load. Typically, the power dissipated off-chip is about 76 mW/port so the on-chip power being dissipated will be: [Total power dissipation (5.0v x 320ma)] - [the off-chip power dissipation (4 ports x 76 mW/port)] = 1.3W

# AC Switching Specifications $T_A$ = 0°C to 70°C, $V_{CC}$ = 5V $\pm$ 5%

# **LED Interface Timing**

| Symbol         | Parameter                   | Min | Max  | Units |

|----------------|-----------------------------|-----|------|-------|

| t <sub>O</sub> | LED Clock Duty Cycle        | 40  | 60   | %     |

| t <sub>1</sub> | LED Clock Cycle Time        | 900 | 1100 | ns    |

| t <sub>2</sub> | LED_Data Valid to LED_Clk   | 25  |      | ns    |

| t <sub>3</sub> | LED_Data Valid from LED_Clk | 25  |      | ns    |

# **Reset and Strapping Timing**

| Symbol         | Parameter                                           | Min | Max | Units   |

|----------------|-----------------------------------------------------|-----|-----|---------|

| -              | Reset Pulse Width (X1 Must be Active During RESETz) | 30  | -   | X1 Clks |

| t <sub>5</sub> | X1 Duty Cycle                                       | 40  | 60  | %       |

# **Management Interface Timing**

| Symbol          | Parameter                              | Min | Max | Units |

|-----------------|----------------------------------------|-----|-----|-------|

| t <sub>6</sub>  | MDC Frequency                          |     | 2.5 | MHz   |

| t <sub>7</sub>  | MDC Duty Cycle                         | 40  | 60  | %     |

| t <sub>8</sub>  | MDIO (Input) Set Up to MDC Rising Edge | 10  |     | ns    |

| t <sub>9</sub>  | MDIO (Input) Hold MDC from Rising Edge | 10  |     | ns    |

| t <sub>10</sub> | MDC to MDIO (Output) Delay Time        |     | 300 | ns    |

# **Twisted Pair Start of Transmit Packet**

| Symbol          | Parameter                               | Min | Max | Units |

|-----------------|-----------------------------------------|-----|-----|-------|

| t <sub>11</sub> | TXE Setup Time to TXC Rising Edge       | 20  |     | ns    |

| t <sub>12</sub> | TXD Setup Time to TXC Rising Edge       | 20  |     | ns    |

| t <sub>13</sub> | TXD Hold Time from TXC Rising Edge      | 5   |     | ns    |

| t <sub>14</sub> | TXU Start-up Delay from TXC Rising Edge |     | 400 | ns    |

| t <sub>15</sub> | TX Prop Delay (TXC Rising Edge to TXU±) |     | 350 | ns    |

| t <sub>16</sub> | TXC Low Time (Note 1)                   | 40  |     | ns    |

| t <sub>17</sub> | TXC High Time (Note 1)                  | 40  |     | ns    |

| t <sub>18</sub> | TXC Duty Cycle (Note 1)                 | 40  | 60  | %     |

Note 1: This specification is provided for information only and is not tested

# **Twisted Pair Transmit End of Packet**

| Symbol          | Parameter                                        | Min | Max | Units |

|-----------------|--------------------------------------------------|-----|-----|-------|

| t <sub>19</sub> | TXE Hold Time from TXC Rising Edge               | 5   |     | ns    |

|                 | TXU± End of Packet Hold Time with "0" Ending Bit | 225 |     | ns    |

| t <sub>21</sub> | TXU± End of Packet Hold Time with "1" Ending Bit | 225 |     | ns    |

### **Twisted Pair Start of Receive Packet**

| Symbol          | Parameter                                 | Min | Max  | Units |

|-----------------|-------------------------------------------|-----|------|-------|

| t <sub>22</sub> | Carrier Sense Turn On Delay (RXI± to CRS) |     | 550  | ns    |

| t <sub>23</sub> | Decoder Acquisition Time (Note 1)         |     | 2200 | ns    |

| t <sub>24</sub> | Receive Data Valid to RXC Rising Edge     | 25  |      | ns    |

| t <sub>25</sub> | Receive Data Invalid From RXC Rising Edge | 25  |      | ns    |

| t <sub>26</sub> | Receive Data Bit Delay                    |     | 375  | ns    |

Note 1: This parameter includes TPI smart squelch turn on time plus ENDEC data acquisition time.

### **Twisted Pair End of Receive Packet**

| Symbol          | Parameter                             | Min | Max | Units     |

|-----------------|---------------------------------------|-----|-----|-----------|

| t <sub>27</sub> | Carrier Sense Turn Off Delay          |     | 400 | ns        |

| t <sub>28</sub> | Number of RXCs after CRS Low (Note 1) | 5   |     | Bit Times |

Note 1: This only applies when the GATERXC bit, D0, in the Global Configuration Register is set.

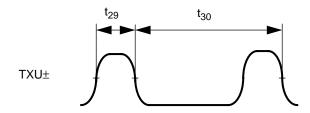

### **Link Pulse Timing**

| Symbol          | Parameter                         | Min | Max | Units |

|-----------------|-----------------------------------|-----|-----|-------|

| t <sub>29</sub> | Link Integrity Output Pulse Width | 80  | 130 | ns    |

| t <sub>30</sub> | Time between Link Output Pulses   | 8   | 24  | ms    |

# **Heartbeat Specifications**

| Symbol          | Parameter             | Min | Max  | Units |

|-----------------|-----------------------|-----|------|-------|

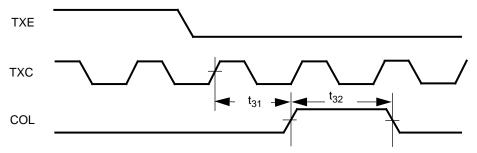

| t <sub>31</sub> | CD Heartbeat Delay    | 600 | 1600 | ns    |

| t <sub>32</sub> | CD Heartbeat Duration | 500 | 1500 | ns    |

# **Jabber Specifications**

| Symbol          | Parameter                | Min | Max | Units |

|-----------------|--------------------------|-----|-----|-------|

| t <sub>33</sub> | Jabber Activation Time   | 20  | 60  | ms    |

| t <sub>34</sub> | Jabber Deactivation Time | 250 | 750 | ms    |

### **AUI Start of Packet Transmit Timing**

| Symbol          | Parameter                               | Min | Max | Units |

|-----------------|-----------------------------------------|-----|-----|-------|

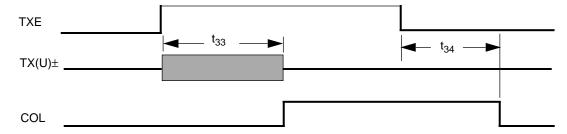

| t <sub>35</sub> | TXE Setup Time to TXC Rising Edge       | 20  |     | ns    |

| t <sub>36</sub> | TXD Setup Time to TXC Rising Edge       | 20  |     | ns    |

| t <sub>37</sub> | TXD Hold Time from TXC Rising Edge      | 5   |     | ns    |

| t <sub>38</sub> | TX± Start-up Delay from TXC Rising Edge |     | 300 | ns    |

| t <sub>39</sub> | TX Prop Delay (TXC Rising Edge to Tx±)  |     | 300 | ns    |

# **AUI End of Packet Transmit Timing**

| Symbol          | Parameter                                       | Min | Max | Units |

|-----------------|-------------------------------------------------|-----|-----|-------|

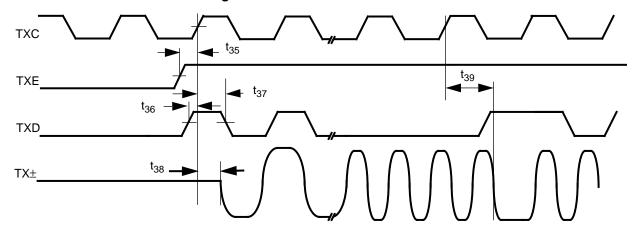

| t <sub>40</sub> | TXE Hold Time from TXC Rising Edge              | 5   |     | ns    |

| t <sub>41</sub> | TX± End of Packet Hold Time with "0" Ending Bit | 200 |     | ns    |

| t <sub>42</sub> | TX± End of Packet Hold Time with "1" Ending Bit | 200 |     | ns    |

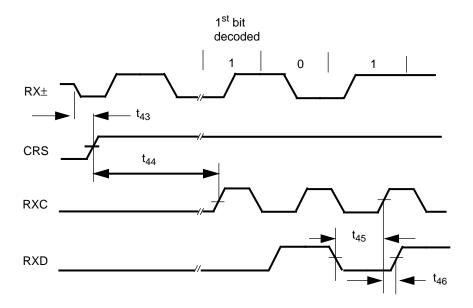

# **AUI Start of Packet Receive Timing**

| Symbol          | Parameter                                 | Min | Max  | Units |

|-----------------|-------------------------------------------|-----|------|-------|

| t <sub>43</sub> | Carrier Sense Turn On Delay (RX± to CRS)  |     | 200  | ns    |

| t <sub>44</sub> | Decoder Acquisition Time                  |     | 2200 | ns    |

| t <sub>45</sub> | Receive Data Valid to RXC Rising Edge     | 25  |      | ns    |

| t <sub>46</sub> | Receive Data Invalid from RXC Rising Edge | 25  |      | ns    |

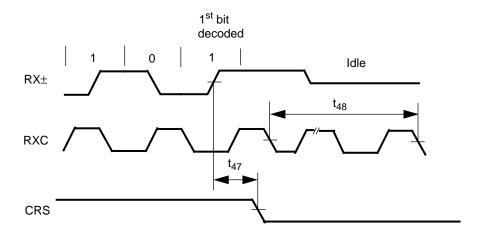

# **AUI End of Packet Receive Timing**

| Symbol          | Parameter                             | Min | Max | Units     |

|-----------------|---------------------------------------|-----|-----|-----------|

| t <sub>47</sub> | Carrier Sense Turn Off Delay          |     | 400 | ns        |

| t <sub>48</sub> | Number of RXCs after CRS Low (Note 1) | 5   |     | Bit Times |

Note 1: This only applies when GATERXC, bit D0, in the Global Configuration Register is set.

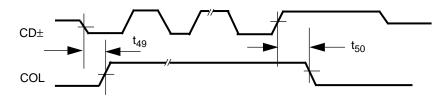

# **Collision Specifications**

| Symbol          | Parameter                             | Min | Max | Units |

|-----------------|---------------------------------------|-----|-----|-------|

| t <sub>49</sub> | Collision Turn On Delay (CD± to COL)  |     | 600 | ns    |

| t <sub>50</sub> | Collision Turn Off Delay (CD± to COL) |     | 900 | ns    |

28

www.national.com

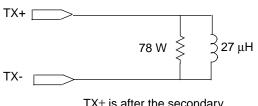

### **Network Test Loads**

### **Twisted Pair Interface Load**

### **Attachment Unit Interface Load**

TX± Output Test Load

TX± is after the secondary side of the transformer.

TXU± is after the secondary side of the transformer.

# **AC Timing Test Condition**

All measurement taken with the external transformer in place.

| Reference                                                          | Limits              |

|--------------------------------------------------------------------|---------------------|

| Input Levels (Digital Pins, t <sub>R</sub> = t <sub>F</sub> = 3ns) | 0V - 3.0V           |

| Input/Output Reference Levels (Digital Pins)                       | 1.5V                |

| Differential Input Reference Levels                                | 2.0 Vp-p            |

| Differential Input/Output Reference Levels                         | 50% of Differential |

### 7.0 Physical Dimensions inches (millimeters) unless otherwise noted

Molded Plastic Quad Flat Package, JEDEC Order Number DP83924AVCE NS Package Number VCE100A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com National Semiconductor Europe

Fax: (+49) 0-180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: (+49) 0-180-530 85 85

English Tel: (+49) 0-180-532 78 32