### **FEATURES**

- Programmable Time Delay of Analog Signals

- Capture and Loop Playback after Trigger

- Up To 3 Analog Channels

- Playback Data At Reduced Rates

- 175 ms Maximum Delay With External Memory

- Single 5 Volt Supply

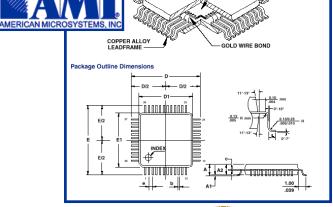

- 100 Lead Thin Quad Flat Pack

- Available In Die Form

#### **APPLICATIONS**

- Munitions Testing

- Industrial Instrumentation

- Store And Forward Data Acquisition

- System Health Monitoring

## **GENERAL DESCRIPTION**

The 3 Channel Delay/Repeater (D/R) IC provides three channels of delayed or delayed and repeated analog signals with a bandwidth range of 0 to 60 KHz. The D/R provides up to 20 ms of time delay in 5 ms increments on-chip. A maximum delay of 175 ms can be supported using an external commercial-off-the-shelf (COTS) SRAM.

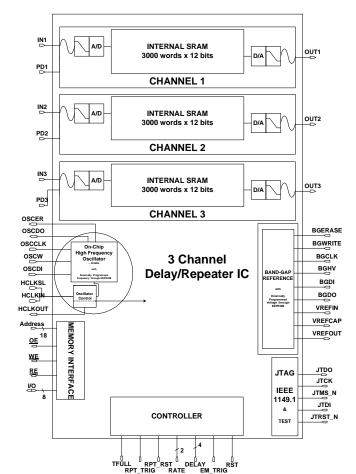

A block diagram of the 3 Channel D/R IC is shown in Figure 1. It uses a mixed signal implementation where three independent analog-to-digital (A/D) converters with 12-bit accuracy are used to sample the input signal waveform. The 60 KHz signal bandwidth is approximately 40 percent of the sample rate. This meets the Nyquist criteria and allows for anti-alias filter rolloff.

The digitized outputs of the A/D converters (12 bits at 150 KSPS) are bussed and written to the internal memory (3 channels x 12 bits x 150 KSPS x 0.02 sec = 108 Kbits) or external memory interface (256K x 8 bits SRAM).

After the data is read from memory, it is fed into three independent digital-to-analog (D/A) converters for signal reconstruction. Output filters remove spurs generated by the D/A converters.

3 Channel D/R Integrated Circuit

**Figure 1: Functional Block Diagram**

#### **PROGRAMMING**

The 3 Channel Delay/Repeater IC uses discrete signals that may be set using dip switches and/or jumpers to program the input control signals. The following Tables illustrate the D/R's programming functions.

| Truth Tables |     |                         |  |      |                  |

|--------------|-----|-------------------------|--|------|------------------|

| TRIG         | RST | Function                |  | Rate | Playback<br>Rate |

| 0            | 0   | Power-up FIFO function  |  | 00   | x1.0             |

| 1            | 0   | Repeat function         |  | 01   | x1.0             |

| 0            | 1   | Return to FIFO function |  | 10   | x0.5             |

| 1            | 1   | No Action               |  | 11   | x0.1             |

| Internal Memory |                    |  |

|-----------------|--------------------|--|

| Delay           | Time<br>Delay (ms) |  |

| 0001            | 5                  |  |

| 0010            | 10                 |  |

| 0011            | 15                 |  |

| 0100            | 20                 |  |

| External Memory |                    |  |  |

|-----------------|--------------------|--|--|

| Delay           | Time<br>Delay (ms) |  |  |

| 1001            | 25                 |  |  |

| 1010            | 50                 |  |  |

| 1011            | 75                 |  |  |

| 1100            | 100                |  |  |

| 1101            | 125                |  |  |

| 1110            | 150                |  |  |

| 1111            | 175                |  |  |

©2000 Systems & Processes Engineering Corporation – SoC Products 101 West Sixth Street, Suite 200, Austin, Texas 78701-2932 Tel: 512/479-7732 Fax: 512/494-0756

e-mail: socproducts.info@spec.com URL: http://www.spec.com REV A1-8

# **SPECIFICATIONS**

| Parameter                  |               | Symbol            | Min                  | Тур                  | Max                  | Units  |

|----------------------------|---------------|-------------------|----------------------|----------------------|----------------------|--------|

| Power Requirem             | ents          |                   |                      |                      |                      |        |

| Digital                    |               | $V_{DDD}$         | 4.5                  | 5.0                  | 5.5                  | V      |

| Supply Voltage             | Analog        | $V_{DDA}$         | 4.5                  | 5.0                  | 5.5                  | V      |

| 0                          | Operating     | I <sub>DD</sub>   |                      | 50                   |                      | mA     |

| Supply Current             | Low-Power     | I <sub>PD</sub>   |                      | TBD                  |                      | μΑ     |

| Power                      | Operating     |                   |                      | 250                  |                      | mW     |

| Consumption                | Low-Power     |                   |                      | TBD                  |                      | μW     |

| Dynamic Specific           | cations       |                   |                      |                      |                      |        |

| Operating Ambien           | t Temperature | T <sub>A</sub>    | -40                  | 25                   | 85                   | °C     |

| External Voltage F         | Reference     | V <sub>EXT</sub>  | 1.5                  | 2.25                 | 2.5                  | V      |

| Internal Voltage R         | eference      | V <sub>REF</sub>  | 2.13                 | 2.25                 | 2.37                 | V      |

| Resolution                 |               |                   |                      |                      | 12                   | Bits   |

| Clock Frequency            |               | Fc                |                      | 19.2                 | 20                   | MHz    |

| Conversion Rate            |               | Fs                |                      | 150                  | 156                  | KSPS   |

| Input Frequency F          | Response      |                   | DC                   |                      | 60K                  | Hz     |

| Signal to Noise            |               | S/N               | 68                   |                      |                      | dB     |

| Total Harmonic Distortion  |               | THD               |                      | 0.4                  | 1                    | %      |

| Interchannel Crosstalk     |               |                   |                      |                      | 1.25                 | mVrms  |

| Interchannel Gain Mismatch |               |                   |                      |                      | ±0.5                 | dB     |

| Absolute Gain Error        |               |                   |                      | ± 1                  | ± 2                  | %      |

| Gain Drift                 |               |                   |                      | 100                  | 200                  | ppm/°C |

| Analog Inputs              |               |                   |                      |                      |                      |        |

| Full Scale Input Voltage   |               | IN1-IN3           |                      | 1.8*V <sub>REF</sub> | 4.2                  | V      |

| Input Capacitance          |               | C <sub>INA</sub>  |                      |                      | 15                   | pF     |

| Input Resistance           |               | R <sub>INA</sub>  | 1M                   |                      |                      | Ω      |

| Analog Outputs             |               |                   |                      |                      |                      |        |

| Full Scale Output Voltage  |               | OUT1-OUT3         |                      | 1.8*V <sub>REF</sub> | 4.2                  | ٧      |

| Output Resistance          |               | R <sub>OA</sub>   |                      | 600                  | 1K                   | Ω      |

| External Load Capacitance  |               | C <sub>LA</sub>   |                      |                      | 100                  | pF     |

| External Load Res          | sistance      | R <sub>LA</sub>   | 10K                  |                      |                      | Ω      |

| Clock                      |               |                   |                      |                      |                      |        |

| Duty Ratio                 |               | CLK               | 45                   | 50                   | 55                   | %      |

| Clock High Voltage         |               | V <sub>CLKH</sub> | 0.7*V <sub>DDD</sub> |                      | V <sub>DDD</sub>     | ٧      |

| Clock Low Voltage          |               | V <sub>CLKL</sub> | 0                    |                      | 0.3*V <sub>DDD</sub> | ٧      |

| Digital Inputs             |               |                   |                      |                      |                      |        |

| Input High Voltage         |               | V <sub>INHD</sub> | 2.4                  |                      | $V_{DDD}$            | V      |

| Input Low Voltage          |               | V <sub>INLD</sub> | 0                    |                      | 0.8                  | V      |

| Input Current              |               | I <sub>IND</sub>  |                      |                      | ± 1                  | μΑ     |

| Input Capacitance          |               | C <sub>IND</sub>  |                      |                      | 10                   | pF     |

| Digital Outputs            |               |                   |                      |                      |                      |        |

| Output High Voltage        |               | V <sub>OHD</sub>  | 4.0                  |                      | $V_{DDD}$            | V      |

| Output Low Voltage         |               | V <sub>OLD</sub>  | 0                    |                      | 0.4                  | V      |

|        | 100       |      |  |

|--------|-----------|------|--|

|        | 14x14     |      |  |

| Symbol | MIN.      | MAX. |  |

| Α      | -         | 1.60 |  |

| A1     | 0.05      | 0.15 |  |

| A2*    | 1.35      | 1.45 |  |

| D      | 16.00 BSC |      |  |

| D/2    | 8.00 BSC  |      |  |

| D1     | 14.00 BSC |      |  |

| E      | 16.00 BSC |      |  |

| E/2    | 8.00 BSC  |      |  |

| E1     | 14.00 BSC |      |  |

| L      | 0.45      | 0.75 |  |

| е      | 0.50 BSC  |      |  |

| b      | 0.17      | 0.27 |  |

| С      | 0.00      | 0.20 |  |

# **PACKAGING**

The Thin Quad Flatpack (TQFP) plastic package family is a reduced thickness plastic surface mount package. The 100 lead TQFP packages are constructed using the latest wire bonding and molding technology to provide surface mount packages with a body thickness of 1.0 or 1.4mm. This package finds many applications where size and weight are a critical factor.

The 3 Channel D/R IC will be available in die form.

©2000 Systems & Processes Engineering Corporation – SoC Products 101 West Sixth Street, Suite 200, Austin, Texas 78701-2932 Tel: 512/479-7732 Fax: 512/494-0756

e-mail: socproducts.info@spec.com URL: http://www.spec.com REV A1-8 -2-

Package Description

LOW STRESS —

MOLDING COMPOUND