# **DSP101 DSP102**

# DSP-Compatible Sampling Single/Dual ANALOG-TO-DIGITAL CONVERTERS

## **FEATURES**

- ZERO-CHIP INTERFACE TO STANDARD DSP ICs: AD, AT&T, MOTOROLA, TI

- SINGLE CHANNEL: DSP101

- DUAL CHANNEL: DSP102

Two Serial Outputs or Cascade to Single 32-Bit Word

- SAMPLING RATE TO 200kHz

- DYNAMIC SPECIFICATIONS:

Signal/(Noise + Distortion) = 88dB;

Spurious-Free Dynamic Range = 94dB;

THD = -91dB

- SERIAL OUTPUT DATA COMPATIBLE WITH 16-, 24-, AND 32-BIT DSP IC FORMATS

## **DESCRIPTION**

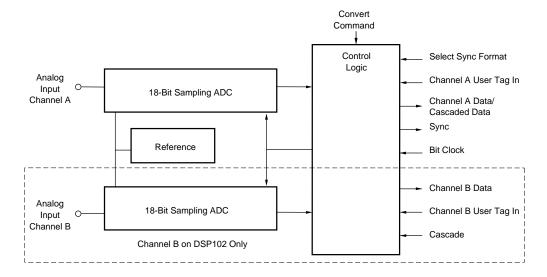

The DSP101 and DSP102 are high performance sampling analog-to-digital converters designed for simplicity of use with modern digital signal processing ICs. Both are complete with all interface logic for use directly with DSP ICs, and provide full sampling and conversion at rates up to 200kHz.

The DSP101 offers a single conversion channel, with 18 bits of serial data output, allowing the user to drive 16-bit, 24-bit, or 32-bit DSP ports. The DSP102 offers two complete conversion channels, with either two full 18-bit output ports, or a mode to cascade two 16-bit conversions into a 32-bit port as one word.

Both the DSP101 and DSP102 are packaged in standard, low-cost 28-pin plastic DIP packages. Each is offered in two performance grades to match application requirements.

International Airport Industrial Park

• Mailing Address: PO Box 11400

• Tucson, AZ 85734

• Street Address: 6730 S. Tucson Blvd.

• Tucson, AZ 85706

Tel: (520) 746-1111

• Twx: 910-952-1111

• Cable: BBRCORP

• Telex: 066-6491

• FAX: (520) 889-1510

• Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

### **ELECTRICAL**

At  $T_A = 0^{\circ}$ C to  $70^{\circ}$ C,  $\pm 2.75$ V input signal, sampling frequency (f<sub>S</sub>) = 200kHz,  $V_A + V_D = +5V$ ,  $V_A - = -5V$ , 16MHz external clock on OSC1, CLKOUT tied to CLKIN, 8MHzdata transfer clock on XCLK, data analysis band-limited to 20kHz, unless otherwise specified.

|                                                                                                                                                    |                                                                                                                                                                                                                                                    |                   | DSP101JP<br>DSP102JP              |                       |                    | DSP101KP<br>DSP102KP            |             |                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------|-----------------------|--------------------|---------------------------------|-------------|-------------------------------------------------|

| PARAMETER                                                                                                                                          | CONDITIONS                                                                                                                                                                                                                                         | MIN               | TYP                               | MAX                   | MIN                | TYP                             | MAX         | UNITS                                           |

| RESOLUTION                                                                                                                                         |                                                                                                                                                                                                                                                    |                   |                                   | 18                    |                    |                                 | *           | Bits                                            |

| ANALOG INPUT Voltage Range Impedance Capacitance                                                                                                   |                                                                                                                                                                                                                                                    |                   | ±2.75V<br>1<br>20                 |                       |                    | * *                             |             | V<br>kΩ<br>pF                                   |

| THROUGHPUT SPEED Complete Cycle Throughput Rate                                                                                                    | Acquisition + Conversion                                                                                                                                                                                                                           | 200               |                                   | 5                     | *                  |                                 | *           | μs<br>kHz                                       |

| AC ACCURACY <sup>(1)</sup> Signal-to-(Noise + Distortion) Ratio  Total Harmonic Distortion Spurious-Free Dynamic Range Signal-to-Noise Ratio (SNR) | $\begin{split} f_{\text{IN}} &= 1 \text{kHz} \\ f_{\text{IN}} &= 1 \text{kHz} \; (-60 \text{dB}) \\ f_{\text{IN}} &= 25 \text{kHz} \\ f_{\text{IN}} &= 1 \text{kHz} \\ f_{\text{IN}} &= 1 \text{kHz} \\ f_{\text{IN}} &= 1 \text{kHz} \end{split}$ | 83<br>89<br>84    | 86<br>32<br>82<br>-90<br>92<br>88 | -86                   | 86<br>92<br>87     | 88<br>*<br>*<br>-91<br>94<br>89 | -89         | dB <sup>(2)</sup><br>dB<br>dB<br>dB<br>dB<br>dB |

| DC ACCURACY Gain Error Gain Error Mismatch Integral Linearity Differential Linearity Error Differential Linearity Error                            | DSP102 Channels<br>±2.75V Input Range<br>±2.75V Input Range<br>±0.7V Input Range<br>±0.7V Input Range                                                                                                                                              |                   |                                   |                       | AC Accuracy        |                                 |             | %<br>%<br>%                                     |

| No Missing Codes Bipolar Zero Error <sup>(3)</sup> Bipolar Zero Mismatch <sup>(3)</sup> Power Supply Sensitivity                                   | $\pm 0.7$ V Input Range DSP102 Channels $-5.25$ V < $V_A$ < $-4.75$ V < $V_A$ +, $V_D$ + < $+5.25$ V                                                                                                                                               |                   | 14<br>±2<br>±2<br>-60<br>-60      |                       |                    | *                               |             | Bits<br>mV<br>mV<br>dB<br>dB                    |

| SAMPLING DYNAMICS Aperture Delay Aperture Jitter Transient Response Overvoltage Recovery                                                           |                                                                                                                                                                                                                                                    |                   | 30<br>100<br>1<br>5               |                       |                    | * * *                           |             | ns<br>ps, rms<br>μs<br>μs                       |

| DIGITAL INPUTS Logic Levels (Except OSC1)  V <sub>IL</sub> V <sub>IH</sub> OSC1 Clock                                                              | $I_L = \pm 10 \mu A$ $I_H = \pm 10 \mu A$                                                                                                                                                                                                          | 0<br>+2.4         |                                   | +0.8<br>+5<br>74HC Co | * * ompatible      |                                 | *           | V<br>V                                          |

| Frequency Data Transfer Clock (XCLK) Frequency                                                                                                     |                                                                                                                                                                                                                                                    | 0.1               |                                   | 16                    | *                  |                                 | *           | MHz<br>MHz                                      |

| Duty Cycle<br>Conversion Clock (CLKIN)<br>Frequency                                                                                                |                                                                                                                                                                                                                                                    | 40<br>0.5         | 50                                | 60<br>5.33            | *                  |                                 | *           | %<br>MHz                                        |

| Duty Cycle  DIGITAL OUTPUTS  Format Coding                                                                                                         |                                                                                                                                                                                                                                                    |                   | 33<br>Serial; MSB fi              | Binary Tw             | o's Complem        | ent                             | e           | %                                               |

| Logic Levels (Except OSC2) VoL VoH OSC2 Conversion Clock (CLKOUT) Drive Capability                                                                 | $I_{SINK} = 4mA$ $I_{SOURCE} = 4mA$                                                                                                                                                                                                                | 0<br>+2.4<br>±2mA | Can o                             | +0.4<br>+5            | * * to drive cryst |                                 | *           | V<br>V<br>mA                                    |

| POWER SUPPLIES Rated Voltage V <sub>A</sub> +                                                                                                      |                                                                                                                                                                                                                                                    | +4.75             | +5                                | +5.25                 | *                  | *                               | *           | V                                               |

| $V_A^ V_D$ Power Consumption Supply Current                                                                                                        | XCLK = OSC1 = 12MHz<br>XCLK = OSC1 = 12MHz                                                                                                                                                                                                         | -5.25<br>+4.75    | -5<br>+5<br>250                   | -4.75<br>+5.25<br>425 | *                  | * *                             | *<br>*<br>* | V<br>V<br>mW                                    |

| I <sub>A</sub> +<br>I <sub>A</sub> -<br>I <sub>D</sub>                                                                                             |                                                                                                                                                                                                                                                    |                   | 30<br>–18<br>5                    | 45<br>–25<br>15       |                    | * *                             | *<br>*<br>* | mA<br>mA<br>mA                                  |

| TEMPERATURE RANGE Specification Storage                                                                                                            |                                                                                                                                                                                                                                                    | 0<br>–65          |                                   | +70<br>+125           | *                  |                                 | *           | °C<br>°C                                        |

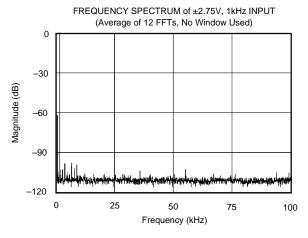

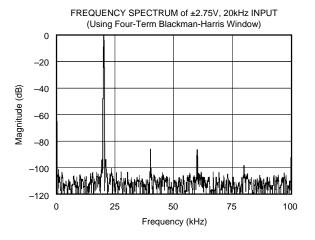

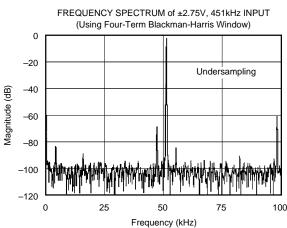

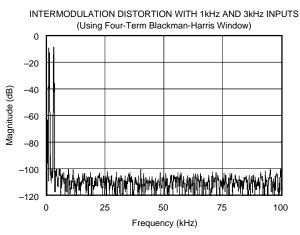

NOTES: (1) All dynamic specifications are based on 2048-point FFTs, using four-term Blackman-Harris window. (2) All specifications in dB are referred to a full-scale input, ±2.75Vp-p. (3) Adjustable to zero with external potentiometer.

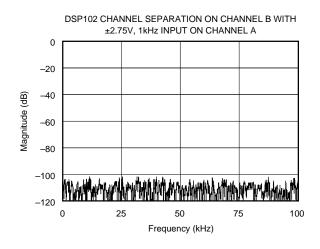

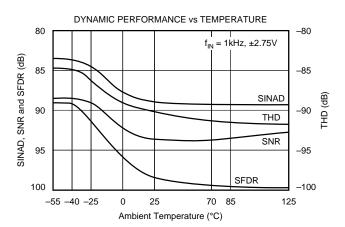

# TYPICAL PERFORMANCE CURVES

At  $T_A = +25^{\circ}C$ ,  $V_A + = V_D + = +5V$ ,  $V_A - = V_D - = -5V$ , Sampling Frequency  $f_S = 200kHz$ ; External Clock Input at OSC1 =  $80f_S = 16MHz$ , XCLK =  $40f_S = 8MHz$ ; Using 2048 Point FFT; Data analysis limited to 0 to 20kHz band; Unless otherwise specified.

SINAD means Signal-to-(Noise + Distortion) Ratio. SNR means Signal-to-Noise Ratio excluding harmonics thru the 8th.

THD means Total Harmonic Distortion thru 8th harmonic. SFDR means Spurious Free Dynamic Range, including harmonics.

# **TYPICAL PERFORMANCE CURVES (CONT)**

At  $T_A = +25^{\circ}C$ ,  $V_A + = V_D + = +5V$ ,  $V_A - = V_D - = -5V$ , Sampling Frequency  $f_S = 200kHz$ ; External Clock Input at OSC1 =  $80f_S = 16MHz$ , XCLK =  $40f_S = 8MHz$ ; Using 2048 Point FFT; Data analysis limited to 0 to 20kHz band; Unless otherwise specified.

0.1

100

10

Input Frequency (kHz)

-100

1000

Input Frequency (kHz)

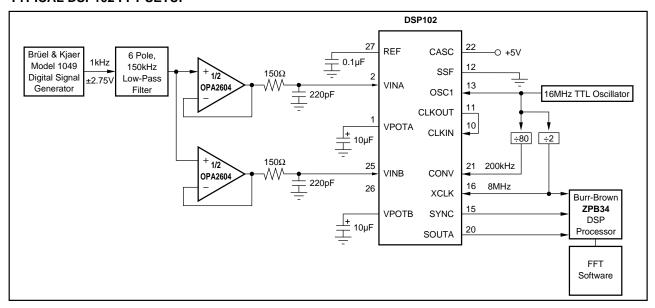

#### **TYPICAL DSP102 FFT SETUP**

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>A</sub> + to Analog Common+7V                  |

|-------------------------------------------------------|

| V <sub>A</sub> - to Analog Common                     |

| V <sub>D</sub> to Digital Common+7V                   |

| Analog Common to Digital Common±1V                    |

| Control Inputs to Digital Common                      |

| Analog Input Voltage ±5V                              |

| Maximum Junction Temperature                          |

| Internal Power Dissipation825mW                       |

| Lead Temperature (soldering, 10s)+300°C               |

| Thermal Resistance, $\theta_{JA}$ , Plastic DIP50°C/W |

|                                                       |

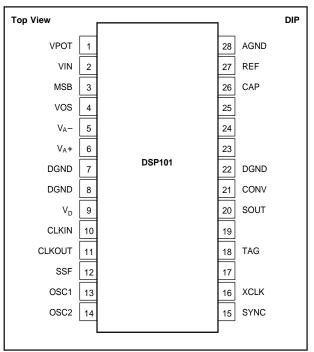

#### **DSP101 PIN CONFIGURATION**

#### **DSP101 PIN ASSIGNMENTS**

| PIN#   | NAME                    | DESCRIPTION                                                                                                                                                             |  |

|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | VPOT                    | Trim Reference Out. 10μF Tantalum to AGND. Voltage on this pin is approximately 2.75V.                                                                                  |  |

| 2      | VIN                     | Analog In.                                                                                                                                                              |  |

| 3      | MSB                     | MSB Adjust In.                                                                                                                                                          |  |

| 4      | vos                     | VOS Adjust In.                                                                                                                                                          |  |

| 5      | V <sub>A</sub> -        | –5V Analog Power.                                                                                                                                                       |  |

| 6      | V <sub>A</sub> +        | +5V Analog Power.                                                                                                                                                       |  |

| 7      | DGND                    | Digital Ground.                                                                                                                                                         |  |

| 8<br>9 | DGND                    | Digital Ground.<br>+5V Digital Power.                                                                                                                                   |  |

| 10     | V <sub>D</sub><br>CLKIN | Conversion Clock In.                                                                                                                                                    |  |

| 11     | CLKOUT                  | Conversion Clock Out. Can drive multiple DSP101/DSP102s to synchronize conversion.                                                                                      |  |

| 12     | SSF                     | Select Synch Format In. If HIGH, SYNC will be active High. If LOW, SYNC will be active Low. See timing diagram (Figure 1).                                              |  |

| 13     | OSC1                    | Oscillator Point 1 Input/External Clock In. If using external clock, drive with 74HC logic levels. Connect to DGND if not used.                                         |  |

| 14     | OSC2                    | Oscillator Point 2 Output. Provides drive for<br>crystal oscillator. Make no electrical connection if<br>using external clock.                                          |  |

| 15     | SYNC                    | Data Synchronization Out. Active High when SSF is HIGH; active Low when SSF is LOW.                                                                                     |  |

| 16     | XCLK                    | Data Transfer Clock In.                                                                                                                                                 |  |

| 17     |                         | No Internal Connection.                                                                                                                                                 |  |

| 18     | TAG                     | User Tag In. Data clocked into this pin is appended to the conversion results on SOUT. See timing diagram (Figure 1).                                                   |  |

| 19     |                         | No Internal Connection.                                                                                                                                                 |  |

| 20     | SOUT                    | Serial Data Out. MSB first, Binary Two's Complement format.                                                                                                             |  |

| 21     | CONV                    | Convert Command In. Falling edge puts converter into hold state, initiates conversion, and transmits previous conversion results to DSP IC with appropriate SYNC pulse. |  |

| 22     | DGND                    | Digital Ground.                                                                                                                                                         |  |

| 23     |                         | No Internal Connection.                                                                                                                                                 |  |

| 24     |                         | No Internal Connection.                                                                                                                                                 |  |

| 25     |                         | No Internal Connection.                                                                                                                                                 |  |

| 26     | CAP                     | Bypass Capacitor. 10μF Tantalum to AGND.  Voltage on this pin is approximately 2.7V.                                                                                    |  |

| 27     | REF                     | Reference Bypass. 0.1µF Ceramic to AGND.  Voltage on this pin is approximately 3.8V.                                                                                    |  |

| 28     | AGND                    | Analog Ground.                                                                                                                                                          |  |

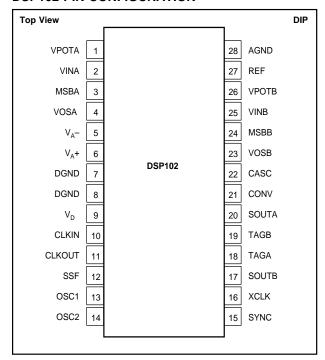

#### **DSP102 PIN CONFIGURATION**

#### **PACKAGE INFORMATION**

| MODEL    | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|--------------------|------------------------------------------|

| DSP101JP | 28-Pin Plastic DIP | 215                                      |

| DSP101KP | 28-Pin Plastic DIP | 215                                      |

| DSP102JP | 28-Pin Plastic DIP | 215                                      |

| DSP102KP | 28-Pin Plastic DIP | 215                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

## **ORDERING INFORMATION**

| MODEL    | NUMBER<br>OF<br>CHANNELS | SIGNAL-TO-<br>(NOISE + DIST.) RATIO<br>dB min |

|----------|--------------------------|-----------------------------------------------|

| DSP101JP | 1                        | 83                                            |

| DSP101KP | 1                        | 86                                            |

| DSP102JP | 2                        | 83                                            |

| DSP102KP | 2                        | 86                                            |

#### **DSP102 PIN ASSIGNMENTS**

| PIN# | NAME             | DESCRIPTION                                                                                                                                                                               |  |

|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | VPOTA            | Channel A Trim Reference Out. 10μF Tantalum to AGND. Voltage on this pin is approximately 2.75V.                                                                                          |  |

| 2    | VINA             | Channel A Analog In.                                                                                                                                                                      |  |

| 3    | MSBA             | Channel A MSB Adjust In.                                                                                                                                                                  |  |

| 4    | VOSA             | Channel A VOS Adjust In.                                                                                                                                                                  |  |

| 5    | V <sub>A</sub> - | –5V Analog Power.                                                                                                                                                                         |  |

| 6    | V <sub>A</sub> + | +5V Analog Power.                                                                                                                                                                         |  |

| 7    | DGND             | Digital Ground.                                                                                                                                                                           |  |

| 8    | DGND             | Digital Ground.                                                                                                                                                                           |  |

| 9    | V <sub>D</sub>   | +5V Digital Power.                                                                                                                                                                        |  |

| 10   | CLKIN            | Conversion Clock In.                                                                                                                                                                      |  |

| 11   | CLKOUT           | Conversion Clock Out. Can drive multiple DSP101/<br>DSP102s to synchronize conversion.                                                                                                    |  |

| 12   | SSF              | Select Synch Format In. If HIGH, SYNC will be active High. If LOW, SYNC will be active Low. See timing diagram (Figure 1).                                                                |  |

| 13   | OSC1             | Oscillator Point 1 Input / External Clock In. If using external clock, drive with 74HC logic levels. Connect to DGND if not used.                                                         |  |

| 14   | OSC2             | Oscillator Point 2 Output. Provides drive for crystal oscillator. Make no electrical connection if using external clock.                                                                  |  |

| 15   | SYNC             | Data Synchronization Out. Active High when SSF is HIGH; active Low when SSF is LOW.                                                                                                       |  |

| 16   | XCLK             | Data Transfer Clock In.                                                                                                                                                                   |  |

| 17   | SOUTB            | Channel B Serial Data Out. MSB first, Binary                                                                                                                                              |  |

| '    |                  | Two's Complement format.                                                                                                                                                                  |  |

| 18   | TAGA             | Channel A User Tag In. Data clocked into this pin is appended to the conversion results of SOUTA. See timing diagram (Figure 1).                                                          |  |

| 19   | TAGB             | Channel B User Tag In. Data clocked into this pin is appended to the conversion results of SOUTB. See timing diagram (Figure 1).                                                          |  |

| 20   | SOUTA            | Channel A Serial Data Out. MSB first, Binary<br>Two's Complement format. If CASC is HIGH, 32<br>bits of data output, with first 16 bits being Channel<br>A data.                          |  |

| 21   | CONV             | Convert Command In. Falling edge puts converter into hold state, initiates conversion, and transmits previous conversion results to DSP IC with appropriate SYNC pulse.                   |  |

| 22   | CASC             | Select Cascade Mode In. If HIGH, DSP102 transmits a 32-bit word on SOUTA, with the first 16 bits being data on Channel A. If LOW, DSP102 transmits data for both channels simultaneously. |  |

| 23   | VOSB             | Channel B VOS Adjust In.                                                                                                                                                                  |  |

| 24   | MSBB             | Channel B MSB Adjust In.                                                                                                                                                                  |  |

| 25   | VINB             | Channel B Analog In.                                                                                                                                                                      |  |

| 26   | VPOTB            | Channel B Trim Reference Out. 10μF Tantalum to                                                                                                                                            |  |

| 27   | REF              | AGND. Voltage on this pin is approximately 2.75V. Reference Bypass. 0.1μF Ceramic to AGND.                                                                                                |  |

| 28   | AGND             | Voltage on this pin is approximately 3.8V.<br>Analog Ground.                                                                                                                              |  |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

7

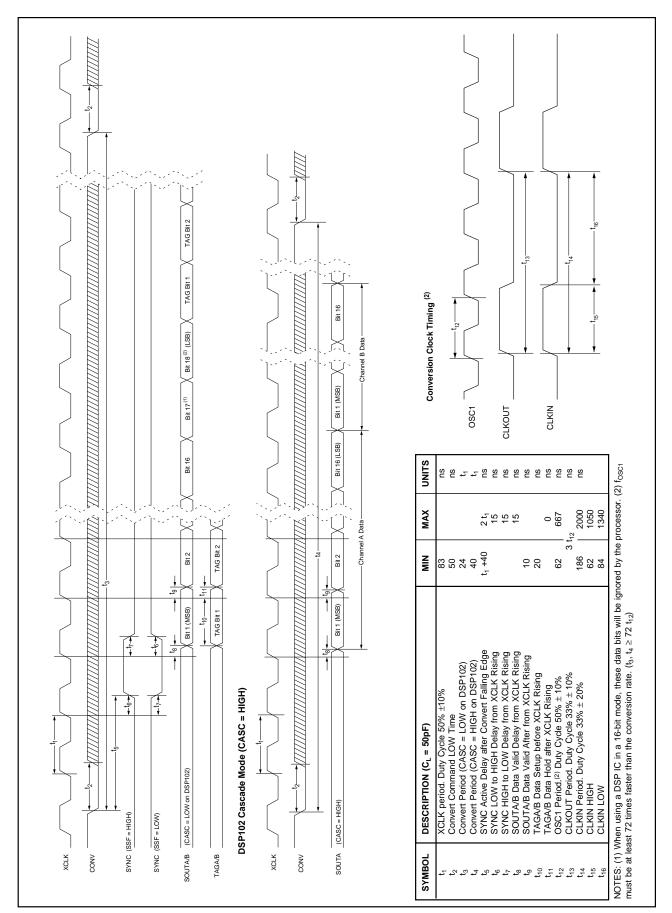

FIGURE 1. DSP101 and DSP102 Timing.

### THEORY OF OPERATION

The DSP101 and DSP102 are sampling analog-to-digital converters optimized for handling dynamic signals. They have complete logic interface circuitry for ease of use with standard digital signal processing ICs, and transmit data words in a serial stream. The successive approximation conversion architecture is combined with an inherently sampling switched capacitor array to provide maximum user flexibility over sampling and conversion timing.

The DSP101 and DSP102 are pipelined internally. When the user gives a convert command at time (t), two actions are initiated. First, the internal sample/holds are switched to the hold state, and a conversion cycle is initiated. At the same time, the DSP101 or DSP102 transmits a synchronization pulse and starts shifting out the conversion results from the previous convert command at (t-1) using the system bit clock. The data from the conversion at time (t) is shifted out of the converter after the next convert command is received.

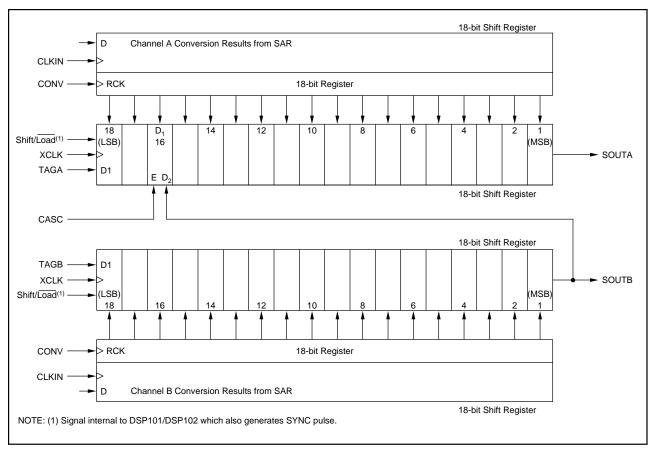

Both the DSP101 and the DSP102 are 18-bit A/Ds internally. When the DSP IC is programmed to accept 16-bit word lengths, the processor will ignore the last two data bits transmitted from the DSP101 or DSP102. A Cascade Mode on the DSP102 can be invoked to transmit data for both conversion channels over a single serial line as a 32-bit word. In this mode, the first 16 bits of data transmitted after the Sync pulse contain data from channel A, followed by 16 bits of information from channel B, allowing a single 32-bit word to contain data for both channels.

A unique Tag feature allows additional digital data to be appended to the conversion results, so that a single data word contains conversion results plus other signal information, such as gain settings or multiplexer channel settings in front of the converter.

The DSP101 and DSP102 are high-resolution A/D converters complete with sampling capability and on-board references. They can acquire and convert analog signals at up to a 200kHz sampling rate. Both operate from ±5V supplies, and have full-scale analog input ranges of ±2.75V.

# **BASIC OPERATION**

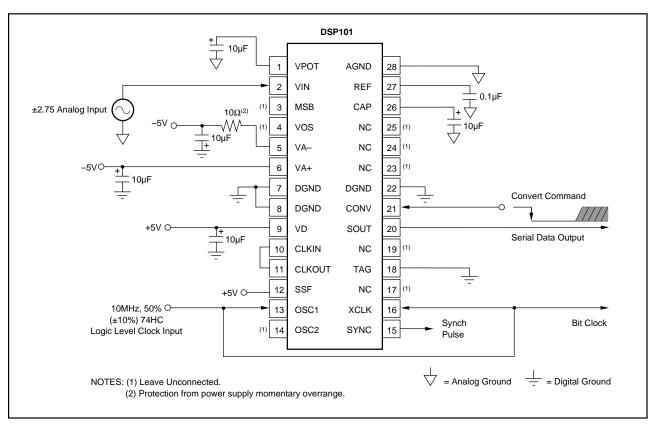

Figure 2 shows the minimum connections required to operate the DSP101. The falling edge of a convert command on pin 21 puts the internal sampling capacitor array into the hold state. The falling edge on pin 21 also starts the process to initiate a conversion and transmit data from the previous conversion, synchronizing both appropriately to the 10MHz clock input on pin 13. Figure 1 shows the timing relationship between the convert command, the output data, and the synchronization pulse.

In this basic system, the 10MHz clock is used both to generate a 3.33MHz conversion clock and as the data transfer bit clock for outputting data. Per Figure 1, there must be at least 72 clock pulses on pin 13 between convert commands, so that this circuit can sample and convert at up to 138kHz.

FIGURE 2. DSP101 Basic Operation.

The convert command at pin 21 causes a Sync pulse to be output on pin 15, followed by the data from the previous conversion output on pin 20. The Sync pulse will be HIGH for one bit clock cycle, since pin 12 is tied HIGH. (A LOW Sync pulse will be output on pin 15 if pin 12 is tied LOW.) Data is serially transmitted in an MSB-first data stream, in Binary Two's Complement format. Both the Sync pulse (pin 15) and the data stream (pin 20) are synchronized to the bit clock (at pins 13 and 16), with the timing relationships shown in Figure 1.

After the 18 bits of data from the previous conversion have been transmitted, pin 20 will continue to clock out LOWs until a new convert command restarts the process, since pin 18 (the Tag input) is grounded. If pin 18 is tied HIGH, pin 20 will clock out HIGHs between conversion cycles.

#### **CONVERSION**

A falling edge on pin 21 (CONV) puts the internal sampling capacitors in the hold state with minimum aperture jitter, initiates a conversion synchronized to the conversion clock, and outputs the data from the previous conversion with an appropriate Sync pulse. On the DSP102, a single convert command simultaneously samples both channels. The timing relationship between the convert command, Sync and the output data is shown in Figure 1. Both Sync and the output data are synchronized to XCLK, the system bit clock. Following a convert command falling edge, pin 21 must be held LOW at least 50ns.

Convert commands can be sent to the DSP101 and DSP102 completely asynchronous to other clocks in the system. This allows external events to be used to trigger conversions.

From Figure 1, it can be seen that two different clocking conditions must be considered in determining the minimum acceptable time between convert commands. First, there need to be a minimum of 24 XCLK periods between convert commands, to allow internal synchronization and transmission of Sync and the data. (In the Cascade Mode on the DSP102, there need to be at least 40 XCLK periods between convert commands, to allow transmission of the 32-bit data words.) When used with DSP processors programmed for data words longer than 16 bits, the transmission time to the processor may determine the minimum time between convert commands.

The second limitation on convert commands is the requirement that the internal analog-to-digital converter be given enough time to complete a conversion, shift the data to the output register, and acquire a new sample. This condition is met by having a minimum of 24 CLKIN periods between convert commands, or a minimum of 72 clock cycles on OSC1, if it is used to generate the conversion clock (CLKOUT driving CLKIN).

#### SIGNAL ACQUISITION

After a conversion is completed, the DSP101 or DSP102 will switch back to the sampling mode. With at least 24

CLKIN periods between convert commands, the A/D will have had sufficient time to acquire a new input sample to full rated accuracy.

#### DATA FORMAT AND INPUT LEVELS

The DSP101 and DSP102 output serial data, MSB first, in Binary Two's Complement format. In the Cascade Mode on the DSP102, the serial data will first contain 16 bits of data for channel A, MSB-first, followed by channel B data, again MSB-first. The analog input levels that generate specific output codes are shown in Table I.

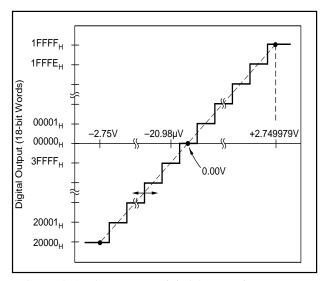

As with all standard A/Ds, the first output transition will occur at an analog input voltage 1/2 LSB above negative full scale (-2.75V + 1/2 LSB) and the last transition will occur 3/2 LSB below positive full scale (+2.75V - 3/2 LSB.) See Figure 3.

FIGURE 3. Analog Input to Digital Output Diagram.

|                                                  |                          | DIGITAL OUTPUT<br>(BINARY TWO'S COMPLEMENT) |                          |                          |

|--------------------------------------------------|--------------------------|---------------------------------------------|--------------------------|--------------------------|

| DESCRIPTION                                      | ANALOG<br>INPUT          | BINARY CODE                                 | 16-BIT<br>WORDS<br>(HEX) | 18-BIT<br>WORDS<br>(HEX) |

| Least Significant Bit $(LSB = \frac{5.5V}{2^n})$ |                          |                                             |                          |                          |

| 16-bit Words<br>18-bit Words                     | 84μV<br>21μV             |                                             |                          |                          |

| Input Range                                      | ±2.75V                   |                                             |                          |                          |

| + Full Scale<br>(2.75V-1LSB)                     | +2.749916V<br>+2.749979V | 011111                                      | 7FFF                     | 1FFFF                    |

| Bipolar Zero<br>(Midscale)                       | 0V                       | 000000                                      | 0000                     | 00000                    |

| One LSB below<br>Bipolar Zero                    | –84μV<br>–21μV           | 111111                                      | FFFF                     | 3FFFF                    |

| - Full Scale                                     | -2.75V                   | 100000                                      | 8000                     | 20000                    |

TABLE I. Ideal Input Voltage vs Output Code.

FIGURE 4. Output Structure of DSP102.

#### **DATA TRANSFER**

The internal A/Ds generate 18 bits of data, transmitting the data MSB first. When read by a DSP IC programmed to accept 16 bits of data, the first 16 MSB bits of data from the DSP101, or each channel of the DSP102, will be shifted into the processor's input shift register, and the last two least significant bits of data from the A/D will be ignored, although they will still be present on the serial data line. When the DSP processor is programmed to accept words of more than 16-bit length (typically 24-bit or 32-bit), the DSP101 and DSP102 will transmit the full 18-bit conversion results, after which the information input on the TAG input (or TAGA and TAGB on the DSP102) will be appended to the output word. (See Tag Feature below.)

In the Cascade Mode, the DSP102 will first transmit the 16 MSBs from channel A, followed by the full 18 bits from channel B, although DSP processors programmed to accept 32 bits of data will ignore the final two bits of information on Channel B. See the DSP102 Cascade Mode section below for details of the Cascade mode.

#### **DATA SYNCHRONIZATION**

A convert command both initiates a conversion and starts the process for transmitting data from the previous conversion. Convert commands can come at any time, completely asynchronous to the conversion clock or the bit clock, and the conversion clock may also be independent of the bit clock. The DSP101 and DSP102 internally synchronize the output data, Sync pulse, and Tag inputs to the bit clock.

While the convert command, conversion clock and bit clock can be asynchronous, system performance is usually enhanced by synchronizing all of them to a system master clock, whenever the application permits. This minimizes changes in digital loads and currents when the critical S/H transition and A/D bit decisions are occurring. Within the DSP101 and DSP102 themselves, running asynchronous convert commands, conversion clocks and bit clocks typically degrades performance only several dB, as shown in the various typical performance curves, but the system board design can easily have more effect.

When a convert command is received, the internal logic generates an appropriate Sync pulse, synchronized to XCLK, as shown in Figure 1. The output Sync pulse will be active High or active Low depending on whether a HIGH or a LOW, respectively, is input at SSF (pin 12).

The convert command also causes the conversion results from the previous conversion to be loaded into the output shift register, synchronous to XCLK. Figure 4 shows the operation of the internal data shift registers on the DSP102. The DSP101 is basically similar, but includes only the top of the figure, showing the SOUTA path.

During the internal successive approximation conversion process, the conversion results are shifted into the input shift registers of the output stage on the DSP102. A new convert command latches that data into the 18-bit parallel latches shown. The internal signal that also generates the Sync pulse, labeled "Shift/Load" in Figure 4, synchronously loads the conversion data into the output shift register on the rising edge of XCLK. The conversion results are then clocked out of the shift register on subsequent rising edges of XCLK.

#### **DATA TRANSFER CLOCK**

XCLK is the data transfer clock, or bit clock, for the system, and is an input for the DSP101 or DSP102. This input is TTL- and 74HC-level compatible. The serial data and SYNC outputs are synchronized internally to this clock, with data valid on the rising edge of XCLK, per the timing shown in Figure 1. Data input on pin 18 (TAG) on the DSP101, or on pins 18 and 19 on the DSP102 (TAGA and TAGB), will be clocked into the output shift register on the rising edge of XCLK, as discussed in the Tag Feature section.

#### **CONVERSION CLOCK**

The analog-to-digital converter sections in the DSP101 and DSP102 were designed to provide accurate conversions under worst case conditions of supplies, temperatures, etc. In order to achieve a full 200kHz sampling capability, they were designed to use a 33% duty cycle conversion clock (CLKIN on pin 10) as shown in Figure 1. The clock is LOW

long enough for internal analog circuitry to settle sufficiently between bit decisions to insure rated accuracy. Bit decisions in the A/D are then made on the rising edge of CLKIN.

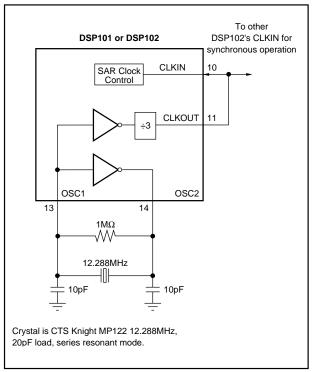

FIGURE 5. DSP101 or DSP102 Conversion Clock Circuit.

11

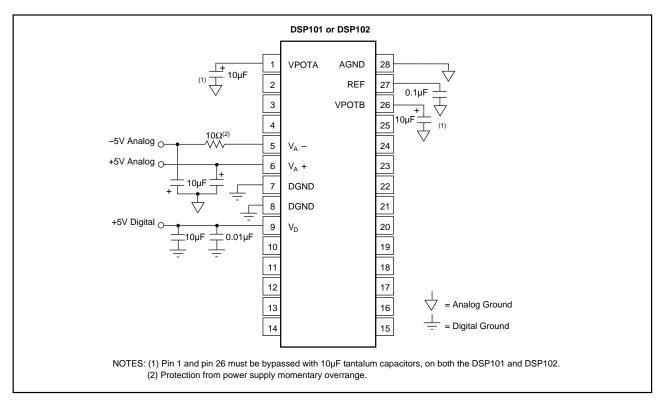

FIGURE 6. DSP101 or DSP102 Power Supply Connections.

When a convert command is received, the DSP101 or DSP102 immediately switches the sampling capacitors to the hold state, and then internally gates the conversion clock to the A/D appropriately. Allowing a minimum of 24 CLKIN pulses between conversions insures that there is sufficient time for complete, accurate conversions, and allows the input sampling capacitor to fully acquire the next sample, regardless of the timing between the convert command and CLKIN.

In most applications, CLKIN (pin 10) can be driven from a 50% duty cycle clock without performance degradation. During characterization of the DSP101 and DSP102, the performance of a number of parts was measured under various conditions with a 4.8MHz, 50% duty cycle input to CLKIN at a full 200kHz conversion rate without noticeable degradation.

#### **OSCILLATOR INPUTS AND CLKOUT**

The DSP101 or DSP102 can generate a 33% duty cycle conversion clock output on CLKOUT (pin 11). This is accomplished by dividing by three a clock from either an external 74HC-level clock or from a crystal oscillator. CLKOUT can deliver ±2mA, and can be used to drive multiple DSP101 or DSP102 CLKINs. See Figure 1 for the timing relationship between OSC1 and CLKOUT.

To use an external 74HC-level clock, drive the clock into OSC1 (pin 13), and leave OSC2 (pin 14) unconnected.

To use a crystal oscillator to generate the conversion clock, refer to Figure 5. Connect the oscillator between OSC1 and OSC2. OSC2 provides the drive for the crystal oscillator. This pin cannot be used elsewhere in the system.

If CLKOUT is not used, both it and OSC2 should be left unconnected, and OSC1 should be grounded.

#### **TAG FEATURE**

Figure 4 shows the implementation of the TAG feature on the DSP101 and DSP102. When a convert command is received, the internal Shift/Load signal loads conversion result data into the output shift register synchronous to XCLK. Between convert commands, the information input on TAG (on the DSP101) or on TAGA and TAGB (on the DSP102) will be clocked into the output shift register on the rising edges of XCLK. Since this is an 18-bit shift register, the data input on the Tag lines will be output on SOUT (DSP101) or SOUTA and SOUTB (DSP102) delayed by 18 bit clocks.

The Tag Feature can be used in various ways. The Tag inputs can be tied HIGH or LOW to differentiate between two converters in a system. As discussed in the Applications section below, the Tag feature can be used to append to the serial output data word information on multiplexer channel address, or other digital data related to the input signal (such as the setting on a programmable gain amplifier.) Another option would be to daisy-chain multiple DSP101 or DSP102 converters, linking the serial output of one to the Tag input of the next. This can simplify the transmission of data from multiple A/Ds over a single optical isolation channel.

#### **DSP102 CASCADE MODE**

If pin 22 (CASC) is tied HIGH, the DSP102 will be in the Cascade Mode. In this mode, when a convert command is received, the DSP102 will transmit a 32-bit data word on pin

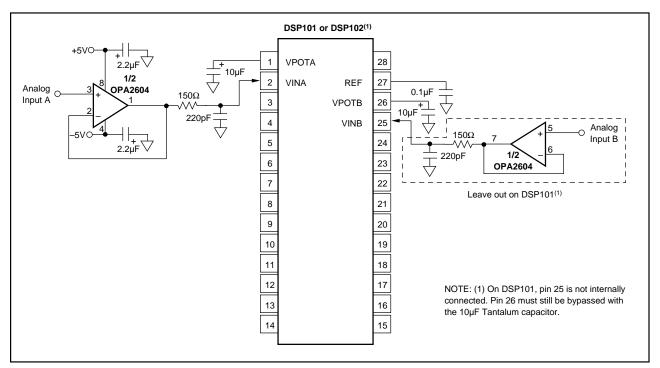

FIGURE 7. DSP101 or DSP102 Input Buffering.

20 (SOUTA) containing data for both input channels in two 16-bit words. Referring to Figure 1, the first 16 bits of data will be the results for channel A, followed by 16 bits of information for channel B. The data will be transferred MSB first. A convert command at time (t) will initiate the transmission of the results of the conversion initiated at time (t-1).

From the descriptions above of the internal shift registers shown in Figure 4, it can be seen that the DSP102 in the Cascade Mode actually continues to shift out data after the 32nd bit of the data word. The next two bits clocked out will be the last two data bits from the full 18-bit conversion on channel B, after which the information output on SOUTA will be the information clocked into TAGB 35 bit clock cycles earlier.

In the Cascade mode on the DSP102, SOUTB will still output channel B conversion data and tag data as usual.

## ANALOG PERFORMANCE

#### **LINEARITY**

The DSP101 and DSP102 are optimized for signal processing applications with wide dynamic range requirements. Linearity is trimmed for best performance in the range around 0V, which is critical for handling low amplitude signals. The DSP101 and DSP102 typically have integral and differential non-linearity below  $\pm 0.003\%$  in the input range of  $\pm 0.7V$ , with there being no missing codes at the 14-bit level in this range. Over the full  $\pm 2.75V$  input range, the largest non-linearities are centered around the bit #2 transition points at +1.375V and -1.375V levels.

#### NOISE AND BIPOLAR ZERO ERROR

The equivalent input noise and bipolar zero error of the DSP101 and DSP102 is shown in the typical performance section for both channels on a DSP102. The inputs to both channels were grounded, and the results of 5,000 conversions was recorded. The data shown is binned at the 16-bit level. The noise results from all sources in the circuit, including clocks, reference noise, etc.

In a theoretically ideal converter with no offset and no noise, the results of all 5,000 conversion for each channel would lie in the bin corresponding to bipolar zero, code 0000. The typical DSP101 or DSP102 will have offset errors in the range of 1 to 2mV, and the two channels on the DSP102 will be matched closer than 2mV. The DSP102 shown in the typical performance section has the worst offset, -0.8mV, on channel A, with channel B being less than 1mV different, and the three sigma noise on either channel being less than  $250\mu$ V.

#### **INPUT BANDWIDTH**

From the typical performance curves, it can be seen that there is very little degradation in Signal-to-(Noise + Distortion) for input signals up to 100kHz. The wideband sampling input typically maintains a 60dB Signal-to-(Noise + Distortion) Ratio undersampling 500kHz input signals.

#### LAYOUT CONSIDERATIONS

Because of the high resolution, linearity and speed of the DSP101 and DSP102, system design problems such as ground path resistance, contact resistance and power supply quality become very important.

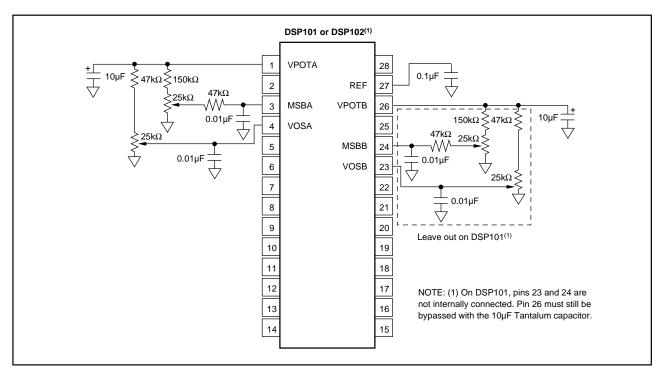

FIGURE 8. DSP101 or DSP102 Optional MSB and Offset Adjust.

Optimal dynamic performance is achieved by soldering the parts directly into boards, to keep the A/Ds as close as possible to ground. The use of sockets will often degrade AC performance. Zero-Insertion-Force sockets are particularly poor because longer lead lengths create inductance.

Short traces on the board, and bypass capacitors as close as possible to the A/D, will further improve dynamic performance.

#### **GROUNDS**

To achieve the maximum performance from the DSP101 or DSP102, care should be taken to minimize the effect of changes in current flowing in the system grounds, particularly while bit decisions are being made in the successive approximation converter's comparator. Pin 28 (AGND) on both the DSP101 and the DSP102 is the most critical, and care should be taken to make this pin as close as possible to the same potential as the system analog ground.

Whenever possible, it is strongly recommended that separate analog and digital ground planes be used. With an LSB level of  $84\mu V$  at the 16-bit level, and one-quarter of that at the 18-bit level, the currents switched in a typical DSP system can easily corrupt the accuracy of the A/Ds unless great care is taken to analyze and design for current flows.

#### POWER SUPPLY DECOUPLING

All of the supplies should be decoupled to the appropriate grounds using tantalum capacitors in parallel with ceramic capacitors, as shown in Figure 6. For optimum performance of any high resolution A/D, all of the supplies should be as clean as possible. If separate digital and analog supplies are available in a system, care should be taken to insure that the difference between the analog and the digital supplies is not more than 0.5V for more than a few hundred milliseconds, as may occur at power-on.

#### INPUT SIGNAL CONDITIONING

To avoid introducing distortion, the DSP101 and DSP102 analog inputs must be driven by a source with low impedance over the input bandwidth needed in the application. Op amps such as the NE5532 or Burr-Brown's OPA2604 work well over audio bandwidths. Figure 7 shows an appropriate input driver circuit. The  $150\Omega$  and 220pF shown on the input help reduce the dynamic load on the input signal conditioning amp in front of the A/D, since all switched capacitor array architectures exhibit fast changes in input current load as the input sampling switch is opened and closed. These dynamic changes in the load can affect any signal conditioning circuit at the input. Other R and C combinations can be

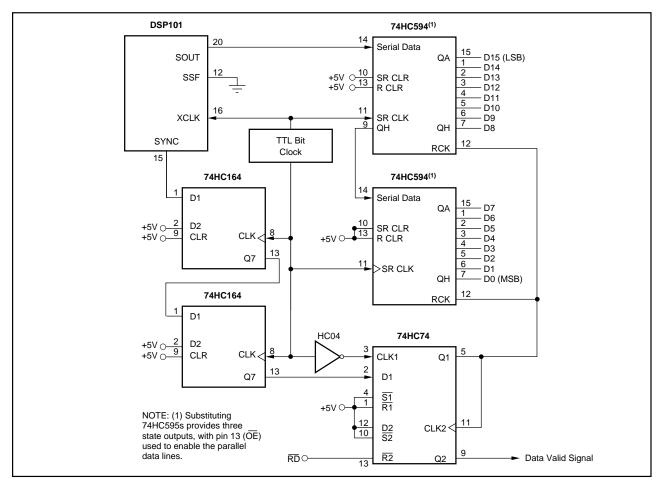

FIGURE 9. Driving a 16-bit Parallel Port from the DSP101.

used, but the resistor should not exceed  $200\Omega$ , or the output settling time of the signal conditioning amplifier may be too long.

#### **EXTERNAL ADJUSTMENTS**

All of the specifications for the DSP101 and DSP102, plus the typical performance curves, are based on the performance of these A/Ds without external trims. In most applications, external trims are not required.

#### **OFFSET ADJUST**

Where required by specific applications, offsets can be adjusted using the circuit of Figure 8. When not adjusted, VOS (pin 4) on the DSP101, and VOSA (pin 4) and VOSB (pin 23) on the DSP102, should be left open. If these pins are connected to traces on the board, they should be bypassed to ground with  $0.01\mu F$  capacitors, as close as possible to the A/D.

To trim offset, one alternative is to ground the analog input while converting continually. Then adjust the trimpot (on VOS for the DSP101, on VOSA and VOSB for the DSP102) until the output code is toggling between the codes FFFF and 0000 (Hex) at the 16-bit level (3FFFF and 00000 at the

18-bit level.) This will center the offset at 1/2 LSB below 0V, which is respectively  $-42\mu V$  or  $-10\mu V$  at the 16- and 18-bit levels.

The offset can also be adjusted by providing a sine wave to the A/D input. Using FFT, or even simple averaging of several thousand conversion results at a time, the trimpots can be adjusted until there is no DC offset of the signal.

Grounding the input, or providing the sine wave, as far in front of the A/D as possible allows offset from intervening signal conditioning components to be also corrected by this procedure.

#### **MSB ADJUST**

In most applications, adjustment of the Most Significant Bit weight will not be required. When not adjusted, MSB (pin 3) on the DSP101, and MSBA (pin 3) and MSBB (pin 24) on the DSP102, should be left open. If these pins are connected to traces on the board, they should be bypassed to ground with 0.01µF capacitors, as close as possible to the A/D.

MSB (pin 3) on the DSP101, and MSBA (pin 3) and MSBB (pin 24) on the DSP102, are internally connected to a resistor divider network that is used to laser-trim the weight

FIGURE 10. A Complete Eight-Channel Analog Input System Using the DSP202 and the HI-508A.

of the MSB capacitor in the CDAC. These pins are nominally at +100mV after laser-trimming during manufacturing. They can handle external inputs up to about one diode drop below ground (-0.6V) before internal clamping circuitry is triggered.

Figure 8 shows an appropriate circuit for adjusting the weight of the most significant bit to minimize differential non-linearity at the critical major-carry transition. To adjust, provide a small amplitude sine wave to the selected A/D input pin while converting continually, and adjust for maximum Signal-to-(Noise + Distortion) ratio, using appropriate signal analysis software.

#### **GAIN ADJUST**

If circuit gain needs to be adjusted in hardware, rather than in system software, appropriate trimpots should be included in the analog signal conditioning section in front of the DSP101 or DSP102. No specific gain adjust circuitry is included in the parts.

# **APPLICATIONS**

#### **INTERFACING DSP101 TO PARALLEL PORTS**

Figure 9 shows a circuit for converting the serial output data from the DSP101 into 16 bits of parallel data, within the timing constraints of the serial bit-stream from the DSP101. In many applications, this circuit can be easily incorporated into gate arrays or other programmed logic circuits already used in the system, since the extra gate count is not high.

This circuit adds an additional pipeline delay to the conversion data, so that the parallel data from a conversion at time

(t) is valid one conversion cycle plus 17 XCLK clocks later (at t+1 plus 17 times XCLK). A convert command at time (t+1) generates a Sync and begins transmitting serial data from SOUT. The serial data is shifted into the 74HC594 shift registers, and Sync is shifted through the 74HC164 shift registers. The Q1 output of the 74HC74 dual D-type flip-flops clocks the conversion data into the output register of the 74HC594s, and triggers a data valid signal on its Q2 output. The user can then read the data at any time before the next conversion is started, and the Read signal will reset the data valid output from Q2.

In many systems, galvanic isolation of signals is required. Using opto-couplers on the serial data lines in Figure 9 allows a fully isolated system to be built using a DSP101 and only three couplers across the barrier (for serial data, XCLK and SYNC.)

#### **MULTIPLEXING INPUTS TO THE DSP101**

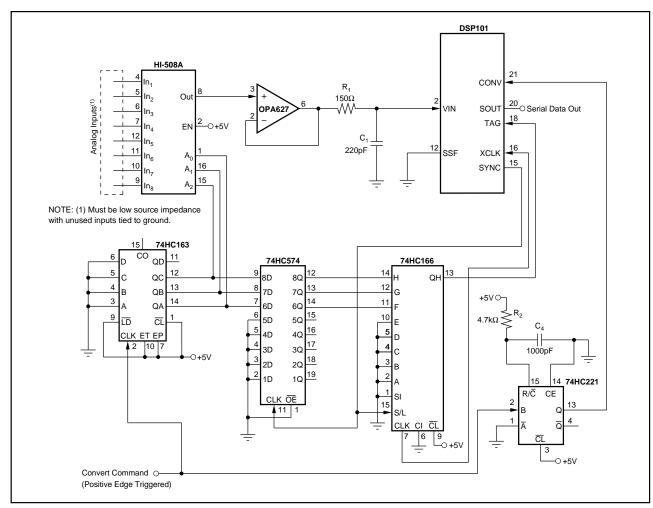

Figure 10 shows a complete circuit for sequentially scanning eight analog input channels with a single DSP101, and using the Tag feature on the DSP101 to append the multiplexer channel address to the serial output conversion results.

The circuit in Figure 10 includes the required digital logic and timing logic. The 74HC163 counter provides the scan sequence to the Burr-Brown HI-508A analog multiplexer. In order to allow the HI-508A enough time to switch to the next channel and settle before the DSP101 begins a conversion, a 74HC221 one-shot introduces a 3µs delay for the DSP101 convert command input.

The Burr-Brown OPA627 provides a low impedance source for the DSP101, buffering it from the output impedance of

FIGURE 11. Analog Input and Analog Output System.

the multiplexer. This unity-gain buffer minimizes distortion, taking full advantage of the resolution and bandwidth of the DSP101.

The 74HC574D register delays the multiplexer address data by one conversion before appending the channel data to the serial conversion results from the DSP101. This attaches the channel address to the correct conversion results. Since the channel scanning shown in Figure 10 is sequential, this delay latch could be left out and software could recognize that the time (t) conversion results have the MUX address from the time (t-1) conversion appended. However, for systems using non-sequential scan lists, this delay latch is essential to maintain the conversion data and channel address integrity.

The 74HC166 synchronous loading shift register loads the channel address tag data into the shift register on the rising edge of the bit clock, in conjunction with the Sync output of the DSP101. The channel address tag data is then clocked into the DSP101 Tag input (pin 18) by the bit clock, while the conversion data is clocked out the other end of the

DSP101 shift register (discussed in another section of this data sheet.)

Figure 10 was developed and tested using a Burr-Brown ZPB34 DSP board, which contains an AT&T DSP32C, so that the SYNC output is programmed to be active LOW. The circuit needs to be modified for DSP processors from ADI, TI, and Motorola, which use active HIGH Sync pulses. For these processors, tie SSF (pin 12) on the DSP101 HIGH, and use a 74HC04 hex inverter to invert the Sync signal to the 74HC574 and 74HC166.

The same basic circuit can be duplicated to drive two channels in a DSP102, or can be easily modified for more or less than eight channels of analog input.

# USING DSP101 AND DSP102 WITH TEXAS INSTRUMENTS DSP ICS

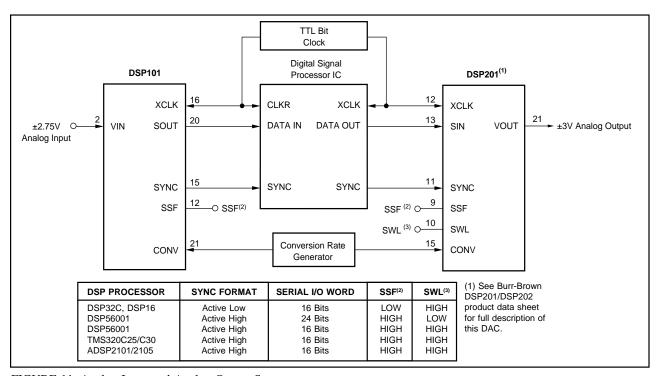

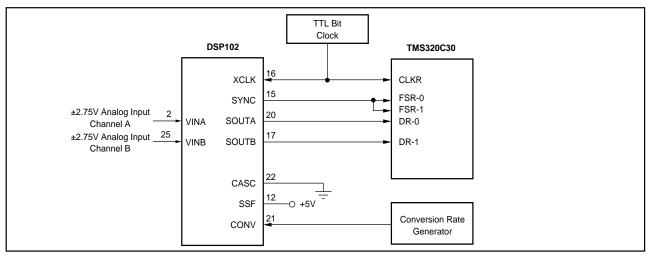

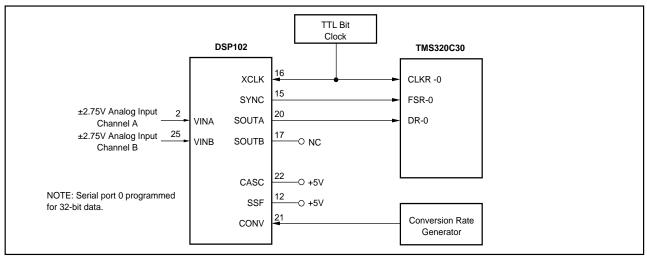

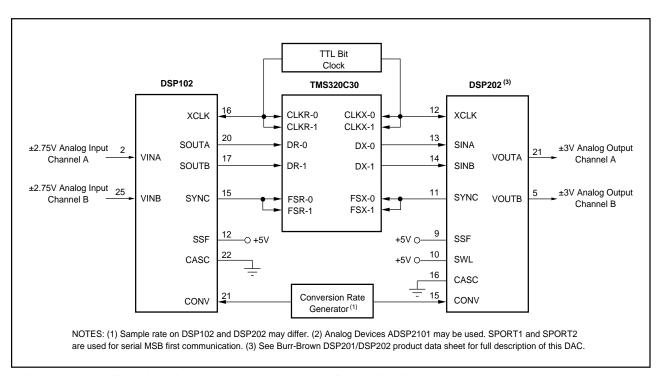

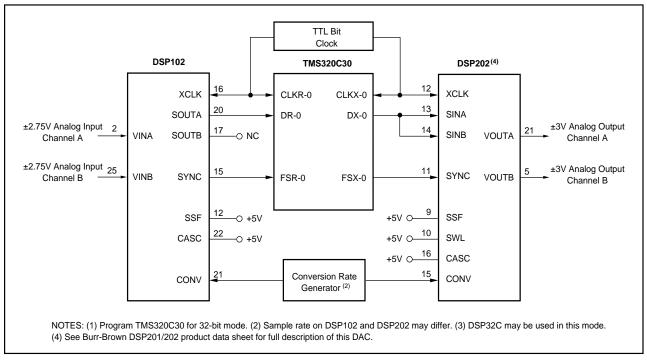

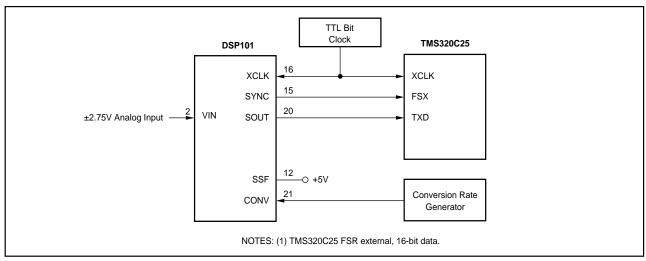

Figures 11 thru 17 show various ways to use the DSP101 and DSP102 with DSP ICs from the Texas Instruments TMS320Cxx series. For simplicity, all of these circuits are

FIGURE 12. Using DSP102 with TMS320C30.

FIGURE 13. Using DSP102 with TMS320C30 in Cascade Mode.

based on using the TME320Cxx in the mode where SSF (Select Synch Format, pin 12) is tied HIGH, so that there is an active High synchronization pulse generated by the DSP101 or DSP102 after receiving a convert command. The synchronization pulse can be changed to active Low simply by making SSF LOW, where appropriate, without changing the basic operation of the A/Ds.

In all cases, the DSP101 and DSP102 will transmit data MSB-first, and the TMS320Cxx needs to be programmed for this.

Figure 11 shows a circuit for using the TMS320C25 or TMS320C30 in a complete analog input and analog output system using the DSP101 along with the Burr-Brown DSP201 D/A.

FIGURE 14. Two-Channel Analog Input and Output System with TMS320C30.

FIGURE 15. Two-Channel Analog Input and Output System with TMS320C30 in Cascade Mode.

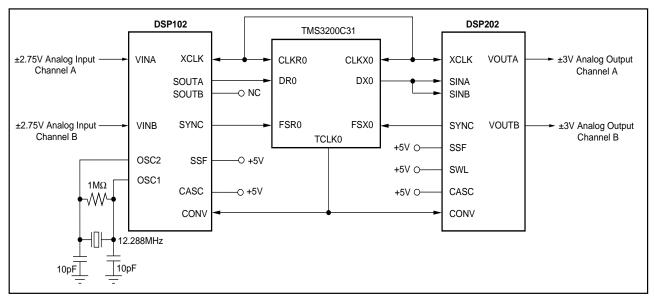

# USING TMS320C31 TO GENERATE ALL CONTROL SIGNALS

Figure 17 shows a circuit for using the TMS320C31 with a DSP102 and a Burr-Brown DSP202 D/A to provide a two channel analog I/O system. The flexibility of the TMS320C31 allows it to generate the data transfer clock (XCLK) and the Convert Command, minimizing additional circuitry and synchronizing the timing signals to the processor's master

clock. In this circuit, the DSP102 and DSP202 are used in their Cascade modes, transmitting and receiving two channels of data in a single 32-bit word. (See the Cascade Mode section above.)

Table II shows how to set up the circuit in Figure 17 for a 44.1kHz conversion rate for both channels of the DSP102 A/D and both channels of the DSP202 D/A. Both inputs and outputs will be simultaneously converted.

FIGURE 16. Using DSP101 with TMS320C25.

19

FIGURE 17. Two Channel Analog I/O Using TMS320C31.

| SERIAL PORT                                     | 0.0550040  |  |  |

|-------------------------------------------------|------------|--|--|

| Port Global Control Register                    | 0x0EBC040  |  |  |

| FSX/DX/CLKX Port Control Register               | 0x00000111 |  |  |

| FSR/DR/CLKR Port Control Register               | 0x00000111 |  |  |

| Receive/Transmit Timer Control Register         | 0x000000F  |  |  |

| TIMER                                           |            |  |  |

| Timer Global Control Register                   | 0x000002C1 |  |  |

| Timer Period Register                           | 0x000000B5 |  |  |

| NOTE: Assumes TMS320C31 has 32MHz Master Clock. |            |  |  |

TABLE II. TMS320C31 Register Settings for 44.1kHz Conversion Rate in Figure 17.

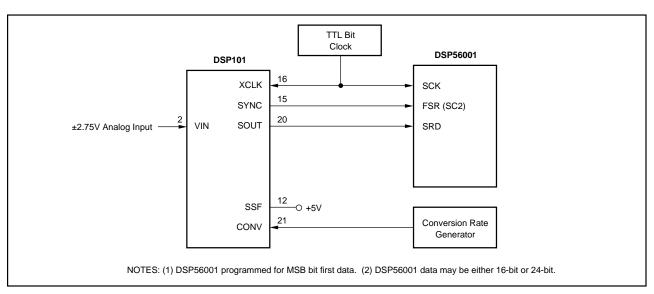

# USING DSP101 AND DSP102 WITH MOTOROLA DSP ICS

Figure 18 shows how to use the DSP101 with a Motorola DSP56001. Using the DSP102 requires using two DSP56001s. The DSP56001 needs to be programmed to receive data MSB-first with SYNC in the Bit Mode.

SSF (pin 12) needs to be tied HIGH for using either the DSP101 or the DSP102 with DSP56001s. This will cause the DSP101 or DSP102 to transmit an appropriate active High synchronization pulse on SYNC (pin 15) after a convert command is received by the A/D. Timing is shown in Figure 1.

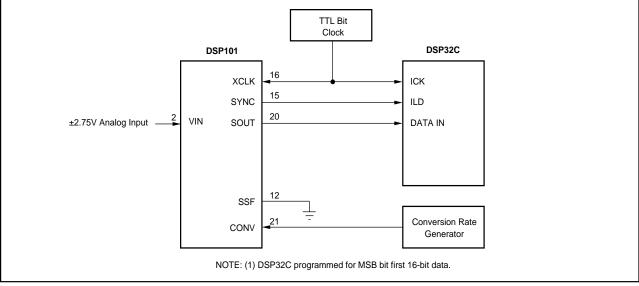

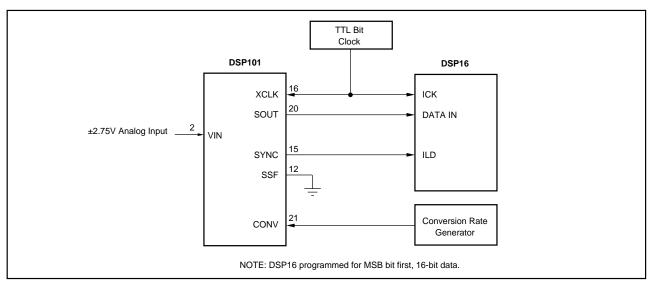

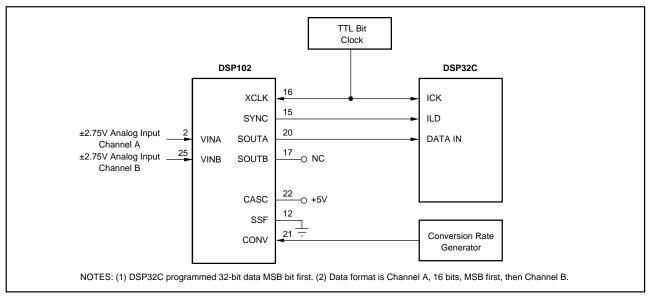

#### USING DSP101 AND DSP102 WITH AT&T DSP ICS

Figures 11, 19, 20, and 21 show how to use the DSP101 and

DSP102 with the DSP16 and DSP32C in different modes. The AT&T processors need to be programmed to accept data MSB-first, and the DSP101 or DSP102 needs to have SSF (pin 12) tied LOW, so that an appropriate active Low synchronization pulse will be transmitted by the A/D after a convert command is received.

Figures 19 and 20 show the DSP32C and DSP16 respectively used with the DSP101 to handle a single analog input channel.

Figure 21 shows how to transmit to a single DSP32C conversion results from both DSP102 channels in a single 32-bit word, using the Cascade mode on the A/D.

Figure 11 indicates how to build a complete analog input and analog output system using a DSP32C or DSP16 with a DSP101 and a Burr-Brown DSP201 D/A.

FIGURE 18. Using DSP101 with DSP56001.

FIGURE 19. Using DSP101 with DSP32C.

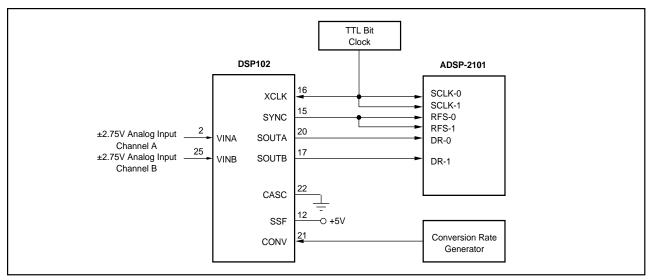

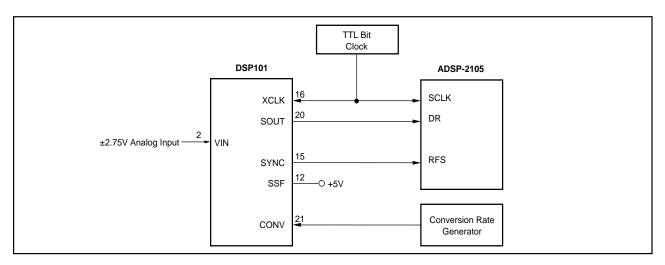

#### **USING DSP101 AND DSP102 WITH ADI DSP ICS**

When using the DSP101 or DSP102 with the fixed-point ADSP21xx series, the processors need to be programmed to receive data MSB-first.

Figure 22 shows how to use the DSP102 with an ADSP2101 to provide a two-channel simultaneous sampling system.

Figure 23 shows the connections required to generate an analog input channel using an ADSP2105 with the DSP101.

The same basic circuit can be used to connect a DSP101 to the ADSP2101.

Figure 11 indicates how to build a complete analog I/O system using either the ADSP2101 or the ADSP2105 with a DSP101 and a Burr-Brown DSP201 D/A.

The two serial ports on the ADSP2101 can also be used with the DSP102 and the Burr-Brown DSP202 D/A to make two complete analog I/O channels, as indicated in footnote 2 of Figure 14.

FIGURE 20. Using DSP101 with DSP16.

21

FIGURE 21. Using DSP102 with DSP32C in Cascade Mode.

FIGURE 22. Using DSP102 with ADSP-2101.

FIGURE 23. Using DSP101 with ADSP-2105.

#### **DEM-DSP102/202 EVALUATION BOARD**

An evaluation fixture, the DEM-DSP102/202, is available to simplify evaluation of the DSP101 and DSP102, and the companion digital-to-analog converters, the single DSP201 and dual DSP202. The DEM-DSP102/202 comes complete with a socketed DSP102 and DSP202, a breadboard area, TTL I/O headers and differential line drivers for data trans-

fer options, a complete clocking circuit for the conversion clock and bit clock, and analog filter modules. The board makes it easy to go from design concept to working prototype of a DSP-based system, offering two complete analog I/O channels.

Contact your local Burr-Brown representative for a full data sheet on the DEM-DSP102/202.