# DM2203/2213 Multibank EDO EDRAM 512Kb x 8 Enhanced Dynamic RAM

Product Specification

# **Features**

- 8Kbit SRAM Cache Memory for 12ns Random Reads Within Four Active Pages (Multibank Cache)

- Fast 4Mbit DRAM Array for 30ns Access to Any New Page

- Write Posting Register for 12ns Random Writes and Burst Writes Within a Page (Hit or Miss)

- 5ns Output Enable Access Time Allows Fast Interleaving

- 256-byte Wide DRAM to SRAM Bus for 14.2 Gigabytes/Sec Cache Fill

- On-chip Cache Hit/Miss Comparators Maintain Cache Coherency Without the Need for External Cache Control

- A Hit Pin Outputs Status of On-chip Page Hit/Miss Comparators to Simplify Control

- Output Latch Enable Allows Extended Data Output (EDO) For Faster System Operation

- **■** Hidden Precharge Cycles

- **■** Hidden Refresh Cycles

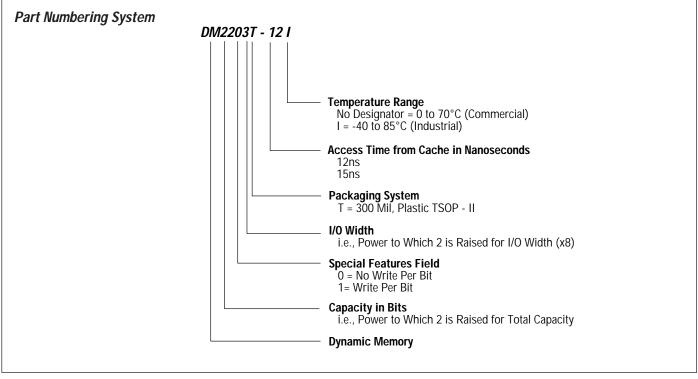

- Write-per-bit Option (DM2213) for Parity and Video Applications

- **■** Extended 64ms Refresh Period for Low Standby Power

- Standard CMOS/TTL Compatible I/O Levels and +5 Volt Supply

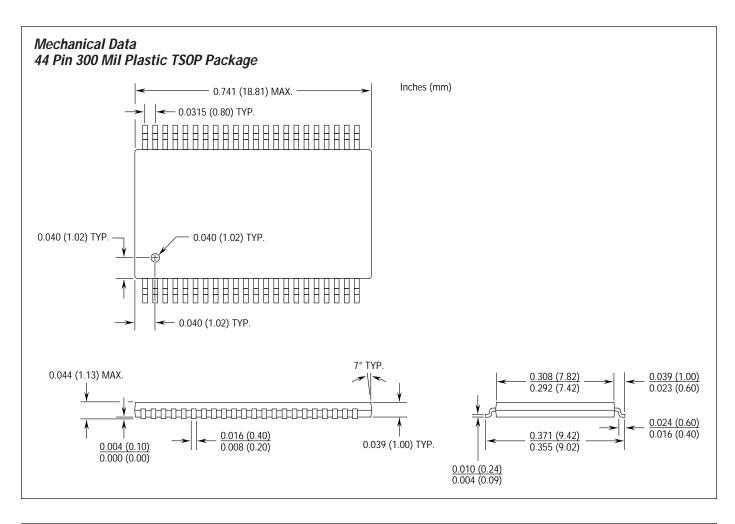

- Low Profile 300-Mil 44-Pin TSOP-II Package

- **■** Industrial Temperature Range Option

# **Description**

The Enhanced Memory Systems 4Mb EDRAM combines raw speed with innovative architecture to offer the optimum cost-performance solution for high performance local or main memory in computer and embedded control systems. In most high speed applications, zero-wait-state operation can be achieved without secondary SRAM cache for system clock speeds of up to 83MHz without interleaving or 132MHz with two-way interleaving. The EDRAM outperforms conventional SRAM cache plus DRAM or synchronous DRAM memory systems by minimizing wait states on initial reads (hit or miss) and by eliminating writeback delays. Architectural similarity with JEDEC DRAMs allows a single memory controller design to support either slow JEDEC DRAMs or high speed EDRAMs. A system designed in this manner can provide a simple upgrade path to higher system performance.

The 512K x 8 EDRAM has the same control and address interface as Enhanced's 4M x 1 and 1M x 4 EDRAM products so that EDRAMs

of different organizations can be supported with the same controller design. The 512K x 8 EDRAM implements the following additional features which can be supported on new designs:

- A controllable output latch provides an extended data out (EDO) mode.

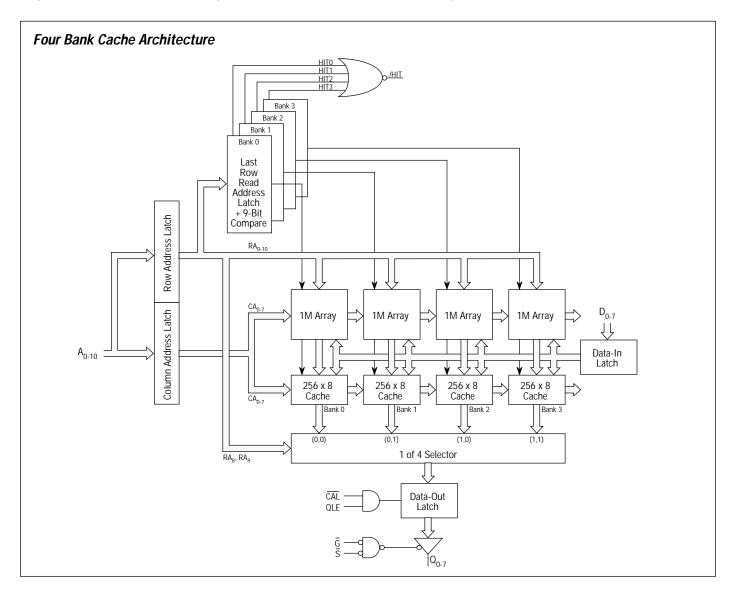

- Cache size is increased from 2Kbits to 8Kbits. The 8Kbit cache is organized as four 256 x 8 direct mapped row registers.

- A hit pin is provided to tell the memory controller when a hit occurs to one of the on-chip cache row registers.

# **Architecture**

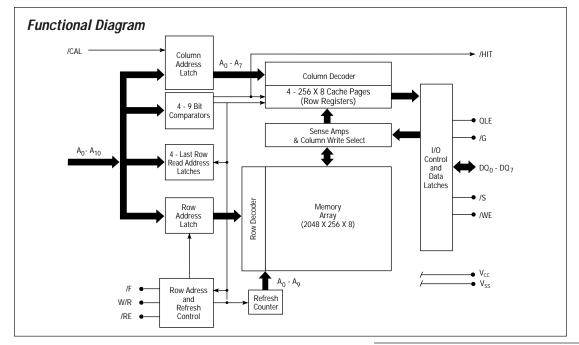

The EDRAM architecture has a simple integrated SRAM cache which allows it to operate much like a page mode or static column DRAM.

| Pin Configu                                                                                                                                                                       | uration                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Vcc   1  /F   2  Vss   3  DQ0   4  Vcc   5  DQ1   6  DQ2   7  Vss   8  DQ3   9  QLE   10  Vcc   11  /G   12  DQ4   13  Vss   14  DQ5   15  DQ6   16  Vcc   17  DQ7   18  Vss   19 | 44                                     |

| NC ☐ 20<br>NC ☐ 21<br>V <sub>CC</sub> ☐ 22                                                                                                                                        | 25 NC<br>24 7HIT<br>23 V <sub>SS</sub> |

The EDRAM's SRAM cache is integrated into the DRAM array as tightly coupled row registers. The 512K x 8 EDRAM has a total of four independent DRAM memory banks each with its own 256 x 8 SRAM row register. Memory reads always occur from the cache row register of one of these banks as specified by row address bits  $A_8$  and  $A_9$  (bank select). When the internal comparator detects that the row address matches the last row read from any of the four DRAM banks (page hit), the SRAM is accessed and data is available on the output pins in 12ns from column address input. The /HIT pin is driven low during a page hit to signify to the DRAM control logic that data is available early. Subsequent reads within the page (burst reads or random reads) can continue at 12ns cycle time. When the row address does not match the last row read from any of the four DRAM banks (page miss), the new DRAM row is accessed and loaded into the appropriate SRAM row register and data is available on the output pins all within 30ns from row enable. In this case, the /HÎT pin is driven high to signify to the control logic that data is available later. Subsequent reads within the page (burst reads or random reads) can continue at 12ns cycle time. During either read hit or read miss operations, a user controllable on-chip output data latch can be used to extend data output time to allow use of the full 83Mbyte/second bandwidth.

Since reads occur from the SRAM cache, the DRAM precharge can occur during burst reads. This eliminates the precharge time delay suffered by other DRAMs and SDRAMs when accessing a new page. The EDRAM has an independent on-chip refresh counter and dedicated refresh control pin to allow the DRAM array to be refreshed concurrently with cache read operations (hidden refresh).

During EDRAM read accesses, data can be accessed in either static column or page mode depending upon the operation of the /CAL input. If /CAL is held high, new data is accessed with each new column address (static column mode). If /CAL is brought low during a read access, the column address is latched and new data will not be accessed until both the column address is changed and /CAL is brought high (page mode). A dedicated output enable (/G) with 5ns access time allows high speed two-way interleave without an external multiplexer.

Memory writes are posted to the input data latch and directed to the DRAM array. During a write hit, the on-chip address comparator activates a parallel write path to the SRAM cache to maintain coherency. Random or page mode writes can be posted 5ns after column address and data are available. The EDRAM allows 12ns page mode cycle time for both write hits and write misses. Memory writes do not affect the contents of the cache row

register except during a cache hit. Since the DRAM array can be written to at SRAM speeds, there is no need for complex writeback schemes.

By integrating the SRAM cache as row registers in the DRAM array and keeping the on-chip control simple, the EDRAM is able to provide superior performance over standard slow 4Mb DRAMs. By eliminating the need for SRAMs and cache controllers, system cost, board space, and power can all be reduced.

# Functional Description

The EDRAM is designed to provide optimum memory performance with high speed microprocessors. As a result, it is possible to perform simultaneous operations to the DRAM and SRAM cache sections of the EDRAM. This feature allows the EDRAM to hide precharge and refresh operation during reads and maximize hit rate by maintaining page cache contents during write operations even if data is written to another memory page. These capabilities, in conjunction with the faster basic DRAM and cache speeds of the EDRAM, minimize processor wait states.

# EDRAM Basic Operating Modes

The EDRAM operating modes are specified in the table below.

# Hit and Miss Terminology

In this datasheet, "hit" and "miss" always refer to a hit or miss to any of the four pages of data contained in the SRAM cache row registers. There are four cache row registers, one for each of the four banks of DRAM. These registers are specified by the bank select row address bits  $A_8$  and  $A_9$ . The contents of these cache row registers is always equal to the last row that was read from each of the four internal DRAM banks (as modified by any write hit data).

#### DRAM Read Hit

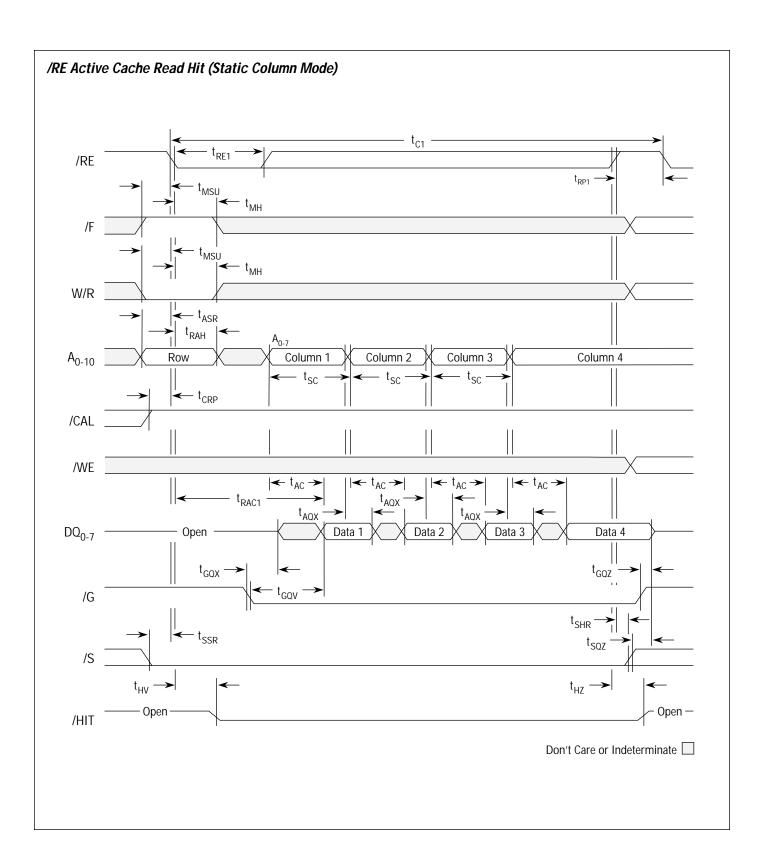

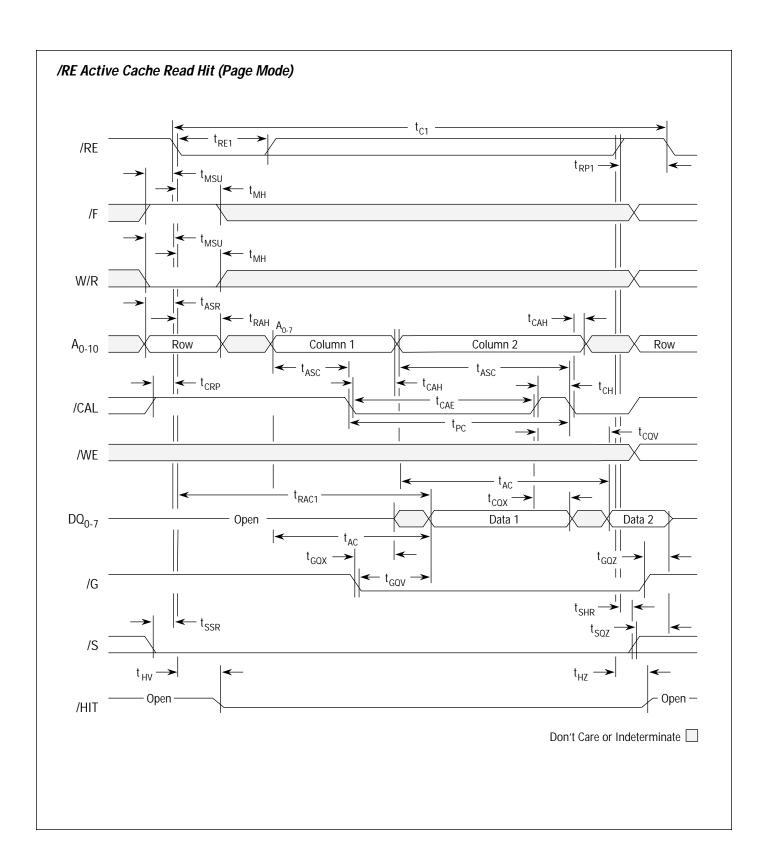

A DRAM read request is initiated by clocking /RE with W/R low and /F high. The EDRAM will compare the new row address to the last row read address latch for the bank specified by row address bits  $A_{8-9}$  (LRR: a 9-bit row address latch for each internal DRAM bank which is reloaded on each /RE active read miss cycle). If the row address matches the LRR, the requested data is already in the SRAM cache and no DRAM memory reference is initiated. The data specified by the row and column address is available at the output pins at the greater of times  $t_{AC}$  or  $t_{GQV}$ . The /HIT output is driven low at time  $t_{HV}$  after /RE to indicate the shorter access time to the external control logic. Since no DRAM activity is initiated, /RE can

be brought high after time  $t_{RE1}$ , and a shorter precharge time,  $t_{RP1}$ , is required. Additional locations within the currently active page may be accessed concurrently with precharge by providing new column addresses to the multiplex address inputs. New data is available at the output at time  $t_{AC}$  after each column address change in static column mode. During any read cycle, it is possible to operate in either static column mode with /CAL=high or page mode with /CAL clocked to latch the column address. In page mode, data valid time is determined by either  $t_{AC}$  and  $t_{COV}$ .

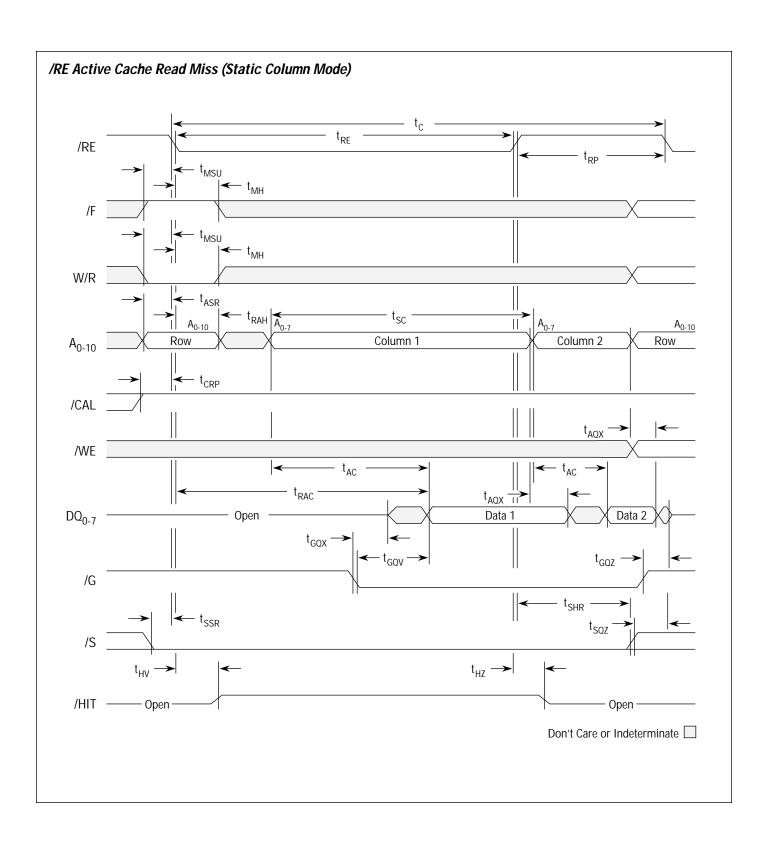

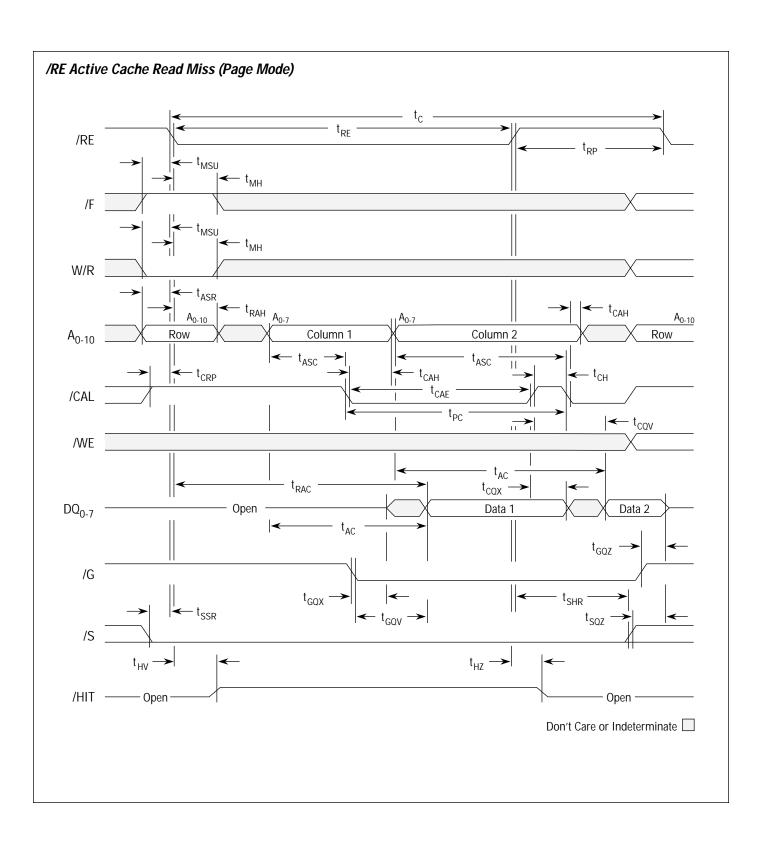

#### **DRAM Read Miss**

A DRAM read request is initiated by clocking /RE with W/R low and /F high. The EDRAM will compare the new row address to the LRR address latch for the bank specified by row address bits  $A_{8-9}$ (LRR: a 9-bit row address latch for each internal DRAM bank which is reloaded on each /RE active read miss cycle). If the row address does not match the LRR, the requested data is not in SRAM cache and a new row is fetched from the DRAM. The EDRAM will load the new row data into the SRAM cache and update the LRR latch. The data at the specified column address is available at the output pins at the greater of times  $t_{RAC}$ ,  $t_{AC}$ , and  $t_{GQV}$ . The /HIT output is driven high at time  $t_{HV}$  after /RE to indicate the longer access time to the external control logic. /RE may be brought high after time t<sub>RE</sub> since the new row data is safely latched into SRAM cache. This allows the EDRAM to precharge the DRAM array while data is accessed from SRAM cache. Additional locations within the currently active page may be accessed by providing new column addresses to the multiplex address inputs. New data is available at the output at time t<sub>AC</sub> after each column address change in static column mode. During any read cycle, it is possible to operate in either static column mode with /CAL=high or page mode with /CAL clocked to latch the column address. In page mode, data valid time is determined by either t<sub>AC</sub> and t<sub>COV</sub>.

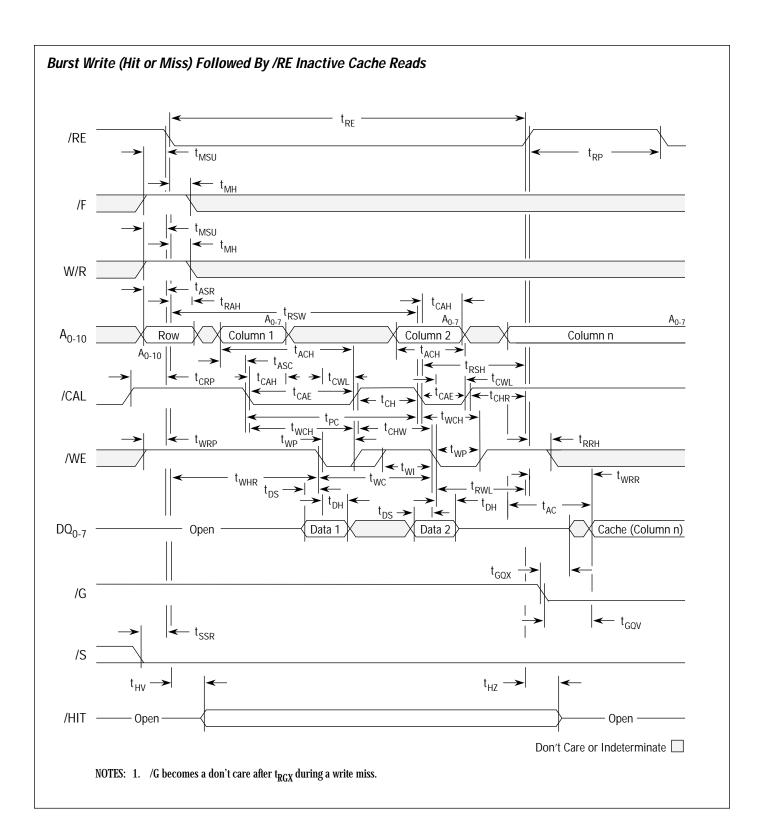

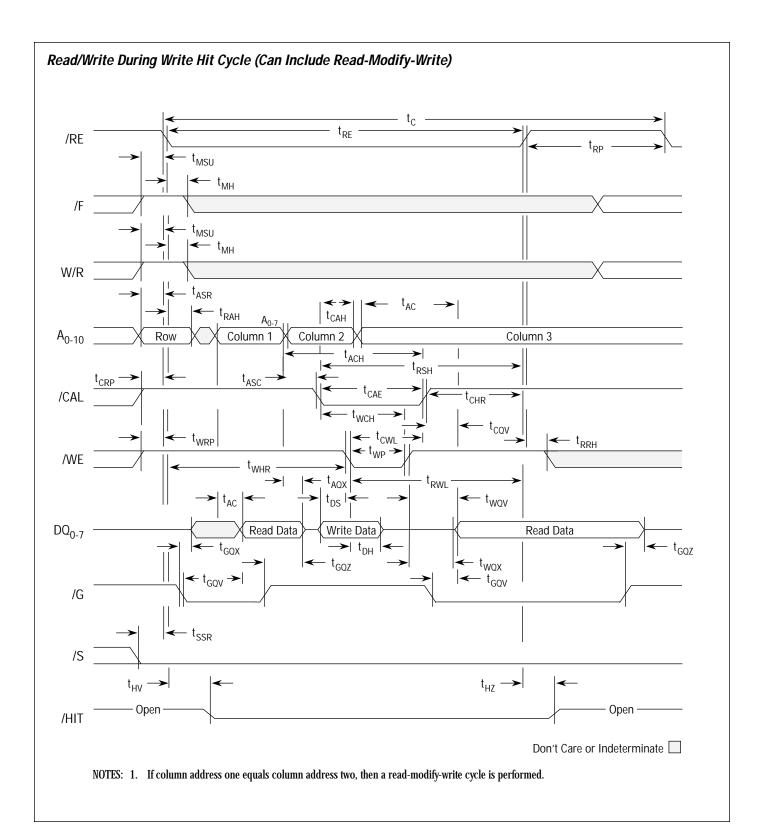

## DRAM Write Hit

A DRAM write request is initiated by clocking /RE while W/R, /CAL, /WE, and /F are high. The EDRAM will compare the new row address to the LRR address latch for the bank specified by row address bits  $A_{8-9}$  (LRR: a 9-bit row address latch for each internal DRAM bank which is reloaded on each /RE active read miss cycle). If the row address matches the LRR, the EDRAM will write data to both the DRAM page in the appropriate bank and its corresponding SRAM cache simultaneously to maintain coherency. The write address and data are posted to the DRAM as soon as the column address is latched by bringing /CAL low and the write data is latched by bringing /WE low (both /CAL and /WE must be high when

## EDRAM Basic Operating Modes

| Function          | /S | /RE      | W/R | /F | A <sub>0-10</sub>                                 | Comment                          |  |

|-------------------|----|----------|-----|----|---------------------------------------------------|----------------------------------|--|

| Read Hit          | L  | <b>\</b> | L   | Н  | Row = LRR                                         | No DRAM Reference, Data in Cache |  |

| Read Miss         | L  | <b>\</b> | L   | Н  | Row ≠ LRR DRAM Row to Cache                       |                                  |  |

| Write Hit         | L  | <b>\</b> | Н   | Н  | Row = LRR Write to DRAM and Cache, Reads Enabled  |                                  |  |

| Write Miss        | L  | <b>\</b> | Н   | Н  | Row ≠ LRR Write to DRAM, Cache Not Updated, Reads |                                  |  |

| Internal Refresh  | Х  | <b>\</b> | Х   | L  | Х                                                 |                                  |  |

| Low Power Standby | Н  | Н        | Х   | Х  | Х                                                 | 1mA Standby Current              |  |

| Unallowed Mode    | Н  | L        | Х   | Н  | Х                                                 |                                  |  |

H = High; L = Low; X = Don't Care; Ø = High-to-Low Transition; LRR = Last Row Read

initiating the write cycle with the falling edge of /RE). The write address and data can be latched very quickly after the fall of /RE  $(t_{RAH} + t_{ASC})$  for the column address and  $t_{DS}$  for the data). During a write burst sequence, the second write data can be posted at time t<sub>RSW</sub> after /RE. Subsequent writes within a page can occur with write cycle time t<sub>PC</sub>. With /G enabled and /WE disabled, read operations may be performed while /RE is activated in write hit mode. This allows read-modify-write, write-verify, or random read-write sequences within the page with 12ns cycle times. During a write hit sequence, the /HIT output is driven low. At the end of any write sequence (after /CAL and /WE are brought high and  $t_{RE}$  is satisfied), /RE can be brought high to precharge the memory. Cache reads can be performed concurrently with precharge (see "/RE Inactive Operation"). When /RE is inactive, the cache reads will occur from the page accessed during the last /RE active read cycle. During write sequences, a write operation is not performed unless both /CAL and /WE are low. As a result, the /CAL input can be used as a byte write select in multi-chip systems.

#### **DRAM Write Miss**

A DRAM write request is initiated by clocking /RE while W/R, /CAL, /WE, and /F are high. The EDRAM will compare the new row address to the LRR address latch for the bank specified for row address bits A<sub>8-9</sub> (LRR: a 9-bit row address latch for each internal DRAM bank which is reloaded on each /RE active read miss cycle). If the row address does not match any of the LRRs, the EDRAM will write data to the DRAM page in the appropriate bank and the contents of the current cache is not modified. The write address and data are posted to the DRAM as soon as the column address is latched by bringing /CAL low and the write data is latched by bringing /WE low (both /CAL and /WE must be high when initiating the write cycle with the falling edge of /RE). The write address and data can be latched very quickly after the fall of /RE ( $t_{RAH} + t_{ASC}$  for the column address and  $t_{DS}$  for the data). During a write burst  $% \left\{ t_{DS}\right\} =\left\{ t_{DS}\right\}$ sequence, the second write data can be posted at time t<sub>RSW</sub> after /RE. Subsequent writes within a page can occur with write cycle time  $t_{PC}$ . During a write miss sequence, the /HIT output is driven high, cache reads are inhibited, and the output buffers are disabled (independently of /G) until time t<sub>WRR</sub> after /RE goes high. At the end of a write sequence (after /CAL and /WE are brought high and t<sub>RF</sub> is satisfied), /RE can be brought high to precharge the memory. Cache reads can be performed concurrently with the precharge (see "/RE Inactive Operation"). When /RE is inactive, the cache reads will occur from the page accessed during the last /RE active read cycle. During write sequences, a write operation is not performed unless both /CAL and /WE are low. As a result, /CAL can be used as a byte write select in multi-chip systems.

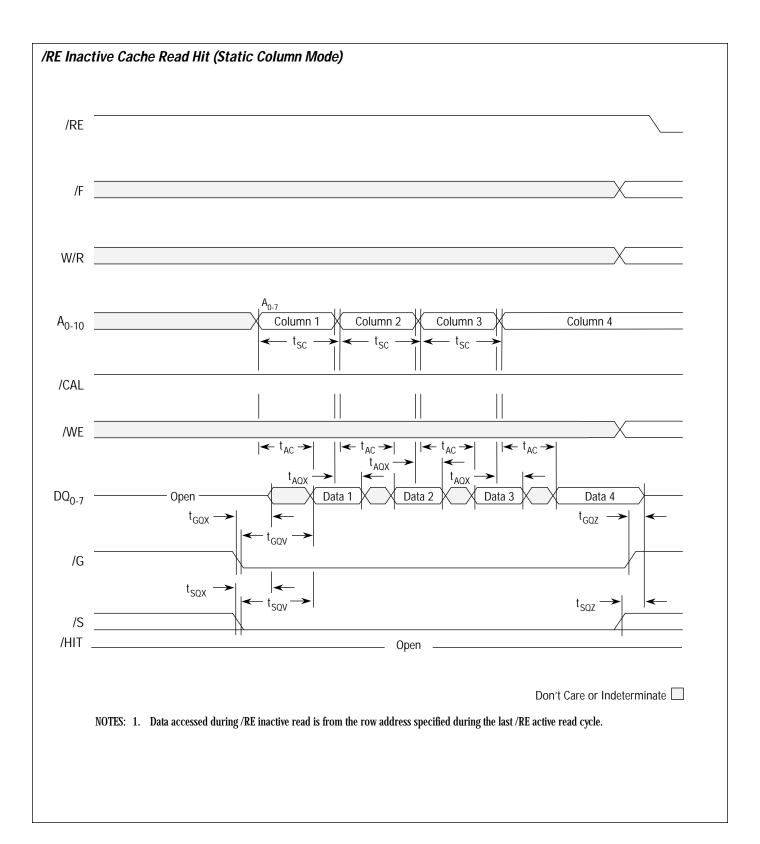

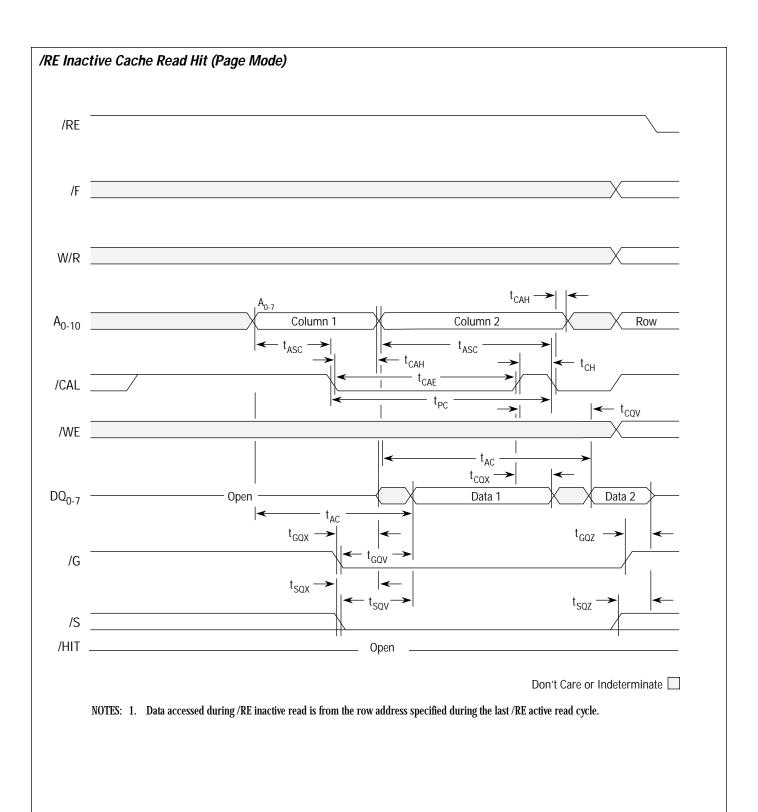

# /RE Inactive Operation

Data may be read from the SRAM cache without clocking /RE. This capability allows the EDRAM to perform cache read operations during precharge and refresh cycles to minimize wait states. It is only necessary to select /S and /G and provide the appropriate column address to read data as shown in the table below. In this mode of operation, the cache reads will occur from the page accessed during the last /RE active read cycle. To perform a cache read in static column mode, /CAL is held high, and the cache contents at the specified column address will be valid at time  $t_{\rm AC}$  after address is stable. To perform a cache read in page mode, /CAL is clocked to latch the column address. When /RE is inactive, the hit pin is not driven and is in a high impedance state.

This option is desirable when the external control logic is

capable of fast hit/miss comparison. In this case, the controller can avoid the time required to perform row/column multiplexing on hit cycles.

| Function                   | /S | /G | /CAL     | A <sub>0-7</sub> |

|----------------------------|----|----|----------|------------------|

| Cache Read (Static Column) | L  | L  | Н        | Col Adr          |

| Cache Read (Page Mode)     | L  | L  | <b>‡</b> | Col Adr          |

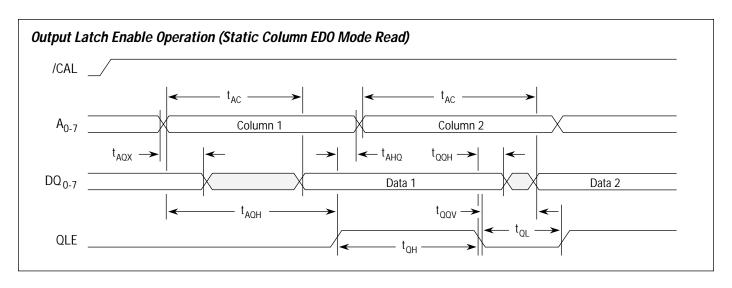

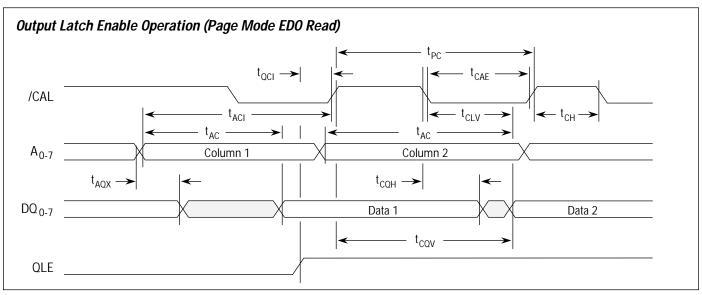

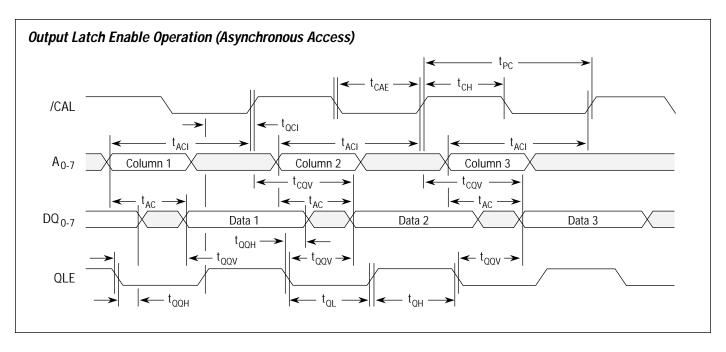

EDO Mode and Output Latch Enable Operation

The QLE and /CÅL inputs can be used to create extended data output (EDO) mode timings in either static column or page modes. The 512K x 8 EDRAM has an output latch enable (QLE) that can be used to extend the data output valid time. The output latch enable operates as shown in the following table.

When QLE is low, the latch is transparent and the EDRAM operates identically to the standard 4M x 1 and 1M x 4 EDRAMs. When /CAL is high during a static column mode read, the QLE input can be used to latch the output to extend the data output valid time. QLE can be held high during page mode reads. In this case, the data outputs are latched while /CAL is high and open when /CAL is not high.

| QLE      | /CAL     | Comments                                      |

|----------|----------|-----------------------------------------------|

| L        | Х        | Output Transparent                            |

| <b>‡</b> | Н        | Output Latched When QLE=H (Static Column EDO) |

| Н        | <b>‡</b> | Output Latched When /CAL=H (Page Mode EDO)    |

When output data is latched and /S goes high, data does not go Hi-Z until /G is disabled or either QLE or /CAL goes low to unlatch data.

#### Write-Per-Bit Operation

The DM221 $\dot{3}$  version of the 512Kb x 8 EDRAM offers a write-per-bit capability which allows single bits of the memory to be selectively written without altering other bits in the same word. This capability may be useful for implementing parity or masking data in video graphics applications. The bits to be written are determined by a bit mask data word which is placed on the I/O data pins DQ<sub>0-7</sub> prior to clocking /RE. The logic one bits in the mask data select the bits to be written. As soon as the mask is latched by /RE, the mask data is removed and write data can be placed on the databus. The mask is only specified on the /RE transition. During page mode burst write operations, the same mask is used for all write operations.

#### Internal Refresh

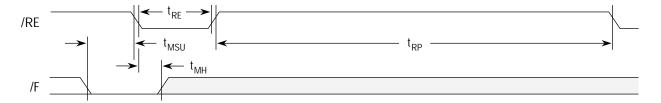

If /F is active (low) on the assertion of /RE, an internal refresh cycle is executed. This cycle refreshes the row address supplied by an internal refresh counter. This counter is incremented at the end of the cycle in preparation for the next /F refresh cycle. At least 1,024 /F cycles must be executed every 64ms. /F refresh cycles can be hidden because cache memory can be read under column address control throughout the entire /F cycle. /F cycles are the only active cycles where /S can be disabled.

## /CAL Before /RE Refresh ("/CAS Before /RAS")

/CAL before /RE refresh, a special case of internal refresh, is discussed in the "Reduced Pin Count Operation" section.

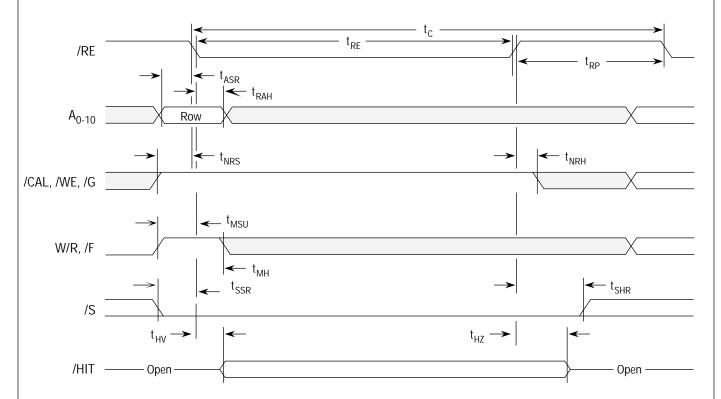

#### /RE Only Refresh Operation

Although /F refresh using the internal refresh counter is the recommended method of EDRAM refresh, an /RE only refresh may be performed using an externally supplied row address. /RE refresh is performed by executing a *write cycle* (W/R, /G, and /F are high) where /CAL is not clocked. This is necessary so that the current cache contents and LRR are not modified by the refresh operation. All combinations of addresses  $A_{0-9}$  must be sequenced every 64ms refresh period.  $A_{10}$  does not need to be cycled. Read refresh cycles are not allowed because a DRAM refresh cycle does not occur when a read refresh address matches the LRR address latch.

#### Low Power Mode

The EDRAM enters its low power mode when  $\slash\!$ S is high. In this mode, the internal DRAM circuitry is powered down to reduce standby current to 1mA.

## Initialization Cycles

A minimum of eight /RE active initialization cycles (read, write, or refresh) are required before normal operation is guaranteed. Following these start-up cycles, two read cycles to different row addresses must be performed for each of the four internal banks of DRAM to initialize the internal cache logic. Row address bits  $A_8$  and  $A_9$  define the four internal DRAM banks.

#### **Unallowed Mode**

Read, write, or /RE only refresh operations must not be performed to unselected memory banks by clocking /RE when /S is high.

#### Reduced Pin Count Operation

Although it is desirable to use all EDRAM control pins to optimize system performance, the interface to the EDRAM may be simplified to reduce the number of control lines by either tying pins to ground or by tying one or more control inputs together. The /S input can be tied to ground if the low power standby mode is not required. The QLE input can be tied low if output latching is not required, or it can be tied high if "extended data out" (hyper page mode) is required. The /HIT output pin is not necessary for device operation. The /CAL and /F pins can be tied together if hidden refresh operation is not required. In this case, a CBR refresh (/CAL before (RE) can be performed by holding the combined input low prior to /RE. A CBR refresh does not require that a row address be supplied when /RE is asserted. The timing is identical to /F refresh cycle timing. The /WE input can be tied to /CAL if independent posting of column addresses and data are not required during write operations. In this case, both column address and write data will be latched by the combined input during writes. The W/R and /G inputs can be tied together if reads are not required during a write hit cycle. If these techniques are used, the EDRAM will require only three control lines for operation (/RE, /CAS [combined /CAL, /F, and /WE], and W/R [combined W/R and /G]). The simplified control interface still allows the fast page read/write cycle times, fast random read/write times, and hidden precharge functions available with the EDRAM.

# Pin Descriptions

## /RE — Row Enable

This input is used to initiate DRAM read and write operations and latch a row address. It is not necessary to clock /RE to read data from the most currently read SRAM row register. On read

operations, /RE can be brought high as soon as data is loaded into cache to allow early precharge.

#### /CAL — Column Address Latch

This input is used to latch the column address and in combination with /WE to trigger write operations. When /CAL is high, the column address latch is transparent. When /CAL transitions low, it latches the address present while /CAL was high. /CAL can be toggled when /RE is low or high. However, /CAL must be high during the high-to-low transition of /RE except for /F refresh cycles. If QLE is high during a read, /CAL will hold data output until it transitions low.

#### W/R — Write/Read

This input along with /F specifies the type of DRAM operation initiated on the low going edge of /RE. When /F is high, W/R specifies either a write (logic high) or read operation (logic low).

# /F — Refresh

This input will initiate a DRAM refresh operation using the internal refresh counter as an address source when /F is low on the low going edge of /RE.

#### /WE — Write Enable

This input controls the latching of write data on the input data pins. A write operation is initiated when both /CAL and /WE are low

## /G — Output Enable

This input controls the gating of read data to the output data pins during read operations.

## /S — Chip Select

This input is used to power up the I/O and clock circuitry. When /S is high, the EDRAM remains in its low power mode. /S must remain active throughout any read or write operation. With the exception of /F refresh cycles, /RE should never be clocked when /S is inactive.

# *DQ<sub>0-7</sub>* — *Data Input/Output*

These bidirectional data pins are used to read and write data to the EDRAM. On the DM2213 write-per-bit memory, these pins are also used to specify the bit mask used during write operations.

## *A*<sub>0-10</sub> — *Multiplex Address*

These inputs are used to specify the row and column addresses of the EDRAM data. The 11-bit row address is latched on the falling edge of /RE. The 8-bit column address can be specified at any other time to select read data from the SRAM cache or to specify the write column address during write cycles.

# **QLE** — Output Latch Enable

This input enables the output latch. When QLE is low, the output latch is transparent. Data is latched when both /CAL and QLE are high. This allows output data to be extended during either static column or page mode read cycles.

#### /HIT — Hit Pin

This output pin will be driven during /RE active read or write cycles to indicate the hit/miss status of the cycle.

## **V<sub>CC</sub>** Power Supply

These inputs are connected to the +5 volt power supply.

#### $V_{SS}$ Ground

These inputs are connected to the power supply ground connection.

# Pin Names

| Pin Names         | Function             |

|-------------------|----------------------|

| A <sub>0-10</sub> | Address Inputs       |

| /RE               | Row Enable           |

| DQ <sub>0-7</sub> | Data In/Data Out     |

| /CAL              | Column Address Latch |

| W/R               | Write/Read Control   |

| V <sub>CC</sub>   | Power (+5V)          |

| V <sub>SS</sub>   | Ground               |

| Pin Names | Function            |

|-----------|---------------------|

| /WE       | Write Enable        |

| /G        | Output Enable       |

| /F        | Refresh Control     |

| /S        | Chip Select         |

| /HIT      | Hit Output          |

| QLE       | Output Latch Enable |

| NC        | Not Connected       |

# **Absolute Maximum Ratings** (Beyond Which Permanent Damage Could Result)

| Description                                               | Ratings                  |

|-----------------------------------------------------------|--------------------------|

| Input Voltage (V <sub>IN</sub> )                          | - 1 ~ V <sub>CC</sub> +1 |

| Output Voltage (V <sub>OUT</sub> )                        | - 1 ~ V <sub>CC</sub> +1 |

| Power Supply Voltage (V <sub>CC</sub> )                   | - 1 ~ 7v                 |

| Ambient Operating Temperature (T <sub>A</sub> )           | -40 ~ +85°C              |

| Storage Temperature (T <sub>S</sub> )                     | -55 ~ 150°C              |

| Static Discharge Voltage<br>(Per MIL-STD-883 Method 3015) | Class 1                  |

| Short Circuit O/P Current (I <sub>OUT</sub> )             | 50mA*                    |

# Capacitance

| Description        | Max | Pins                             |

|--------------------|-----|----------------------------------|

| Input Capacitance  | 5pf | A <sub>0-10</sub>                |

| Input Capacitance  | 6pf | /RE, /CAL, W/R, /WE, /F, /S, QLE |

| Input Capacitance  | 2pf | /G                               |

| Output Capacitance | 4pf | /HIT                             |

| I/O Capacitance    | 6pf | DQ <sub>0-7</sub>                |

\*One output at a time; short duration.

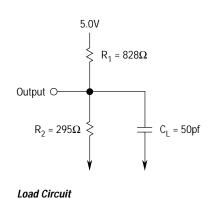

# AC Test Load and Waveforms

$V_{\mbox{\footnotesize{IN}}}$  Timing Reference Point at  $V_{\mbox{\footnotesize{IL}}}$  and  $V_{\mbox{\footnotesize{IH}}}$   $V_{\mbox{\footnotesize{OUT}}}$  Timing Referenced to 1.5 Volts

Input Waveforms

# **Electrical Characteristics**

$T_A=0$  to  $70^{\circ}\text{C}$  (Commercial), -40 to  $85^{\circ}\text{C}$  (Industrial)

| Symbol            | Parameters             | Min   | Мах                | Test Conditions                                                 |

|-------------------|------------------------|-------|--------------------|-----------------------------------------------------------------|

| V <sub>CC</sub>   | Supply Voltage         | 4.75V | 5.25V              | All Voltages Referenced to V <sub>SS</sub>                      |

| V <sub>IH</sub>   | Input High Voltage     | 2.4V  | V <sub>CC</sub> +1 |                                                                 |

| V <sub>IL</sub>   | Input Low Voltage      | -1.0V | V8.0               |                                                                 |

| V <sub>OH</sub>   | Output High Level      | 2.4V  | _                  | I <sub>OUT</sub> = - 5mA                                        |

| V <sub>OL</sub>   | Output Low Level       | _     | 0.4V               | $I_{OUT} = 4.2 \text{mA}$                                       |

| V <sub>i(L)</sub> | Input Leakage Current  | -10µA | 10μΑ               | 0V ≤ V <sub>IN</sub> ≤ 6.5V, All Other Pins Not Under Test = 0V |

| V <sub>0(L)</sub> | Output Leakage Current | -10µA | 10μΑ               | $0V \le V_{IN}$ , $0V \le V_{OUT} \le 5.5V$                     |

| Symbol           | Operating Current                         | 33MHz Typ <sup>(1)</sup> | -12 Max                                                             | -15 Max                                                                               | Test Condition                                                            | Notes |

|------------------|-------------------------------------------|--------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------|

| I <sub>CC1</sub> | Random Read                               | 110mA                    | 225mA                                                               | 180mA                                                                                 | /RE, /CAL, /G and Addresses Cycling: $t_C = t_C$ Minimum                  | 2, 3  |

| I <sub>CC2</sub> | Fast Page Mode Read                       | 65mA                     | 145mA                                                               | 115mA                                                                                 | /CAL, /G and Addresses Cycling: t <sub>PC</sub> = t <sub>PC</sub> Minimum | 2, 4  |

| I <sub>CC3</sub> | Static Column Read 55mA 110mA 90mA /G and |                          | /G and Addresses Cycling: t <sub>AC</sub> = t <sub>AC</sub> Minimum |                                                                                       |                                                                           |       |

| I <sub>CC4</sub> | Random Write                              | 135mA                    | 190mA                                                               | 150mA /RE, /CAL, /WE and Addresses Cycling: $t_C = t_C$ Minimum                       |                                                                           | 2, 3  |

| I <sub>CC5</sub> | Fast Page Mode Write                      | 50mA                     | 135mA                                                               | B5mA 105mA /CAL, /WE and Addresses Cycling: t <sub>PC</sub> = t <sub>PC</sub> Minimum |                                                                           | 2, 4  |

| I <sub>CC6</sub> | Standby                                   | 1mA                      | 1mA                                                                 | 1mA                                                                                   | mA All Control Inputs Stable ≥ V <sub>CC</sub> - 0.2V, Outputs Driven     |       |

| I <sub>CCT</sub> | Average Typical<br>Operating Current      | 30mA                     | _                                                                   | _                                                                                     | See "Estimating EDRAM Operating Power" Application Note                   | 1     |

<sup>(1) &</sup>quot;33MHz Typ" refers to worst case  $I_{CC}$  expected in a system operating with a 33MHz memory bus. See power applications note for further details. This parameter is not 100% tested

<sup>(2)</sup>  $I_{CC}$  is dependent on cycle rates and is measured with CMOS levels and the outputs open. (3)  $I_{CC}$  is measured with a maximum of one address change while /RE =  $V_{IL}$  (4)  $I_{CC}$  is measured with a maximum of one address change while /CAL =  $V_{IH}$

# Switching Characteristics

| Sumbal                            | Description                                                     | -   | 12  | -   | llmit a |       |

|-----------------------------------|-----------------------------------------------------------------|-----|-----|-----|---------|-------|

| Symbol                            | Description                                                     | Min | Max | Min | Max     | Units |

| t <sub>AC</sub> <sup>(1)</sup>    | Column Address Access Time                                      |     | 12  |     | 15      | ns    |

| t <sub>ACH</sub>                  | Column Address Valid to /CAL Inactive (Write Cycle)             | 12  |     | 15  |         | ns    |

| t <sub>ACI</sub>                  | Address Valid to /CAL Inactive (QLE High)                       | 12  |     | 15  |         | ns    |

| t <sub>AHQ</sub>                  | Column Address Hold From QLE High (/CAL=H)                      | 0   |     | 0   |         | ns    |

| t <sub>AQH</sub>                  | Address Valid to QLE High                                       | 12  |     | 15  |         | ns    |

| t <sub>AQX</sub>                  | Column Address Change to Output Data Invalid                    | 5   |     | 5   |         | ns    |

| t <sub>ASC</sub>                  | Column Address Setup Time                                       | 5   |     | 5   |         | ns    |

| t <sub>ASR</sub>                  | Row Address Setup Time                                          | 5   |     | 5   |         | ns    |

| $t_{C}$                           | Row Enable Cycle Time                                           | 55  |     | 65  |         | ns    |

| t <sub>C1</sub>                   | Row Enable Cycle Time, Cache Hit (Row=LRR), Read Cycle Only     | 20  |     | 25  |         | ns    |

| t <sub>CAE</sub>                  | Column Address Latch Active Time                                | 5   |     | 6   |         | ns    |

| t <sub>CAH</sub>                  | Column Address Hold Time                                        | 0   |     | 0   |         | ns    |

| t <sub>CH</sub>                   | Column Address Latch High Time (Latch Transparent)              | 5   |     | 5   |         | ns    |

| t <sub>CHR</sub>                  | /CAL Inactive Lead Time to /RE Inactive (Write Cycles Only)     | -2  |     | -2  |         | ns    |

| t <sub>CHW</sub>                  | Column Address Latch High to Write Enable Low (Multiple Writes) | 0   |     | 0   |         | ns    |

| t <sub>CLV</sub>                  | Column Address Latch Low to Data Valid (QLE High)               |     | 7   |     | 7       | ns    |

| t <sub>CQH</sub>                  | Column Address Latch Low to Data Invalid (QLE High)             | 5   |     | 5   |         | ns    |

| t <sub>CQV</sub>                  | Column Address Latch High to Data Valid                         |     | 15  |     | 15      | ns    |

| t <sub>CQX</sub>                  | Column Address Latch Inactive to Data Invalid                   | 5   |     | 5   |         | ns    |

| t <sub>CRP</sub>                  | Column Address Latch Setup Time to Row Enable                   | 5   |     | 5   |         | ns    |

| t <sub>CWL</sub>                  | /WE Low to /CAL Inactive                                        | 5   |     | 5   |         | ns    |

| t <sub>DH</sub>                   | Data Input Hold Time                                            | 0   |     | 0   |         | ns    |

| t <sub>DMH</sub>                  | Mask Hold Time From Row Enable (Write-Per-Bit)                  | 1   |     | 1.5 |         | ns    |

| t <sub>DMS</sub>                  | Mask Setup Time to Row Enable (Write-Per-Bit)                   | 5   |     | 5   |         | ns    |

| t <sub>DS</sub>                   | Data Input Setup Time                                           | 5   |     | 5   |         | ns    |

| t <sub>GQV</sub> <sup>(1)</sup>   | Output Enable Access Time                                       |     | 5   |     | 5       | ns    |

| t <sub>GQX</sub> <sup>(2,3)</sup> | Output Enable to Output Drive Time                              | 0   | 5   | 0   | 5       | ns    |

| t <sub>GQZ</sub> <sup>(4,5)</sup> | Output Turn-Off Delay From Output Disabled (/G↑)                | 0   | 5   | 0   | 5       | ns    |

| t <sub>HV</sub>                   | Hit Valid From Row Enable                                       |     | 5   |     | 5       | ns    |

| t <sub>HZ</sub>                   | Hit Turn-Off From Row Enable Going High                         | 0   |     | 0   |         | ns    |

| t <sub>MH</sub>                   | /F and W/R Mode Select Hold Time                                | 0   |     | 0   |         | ns    |

| t <sub>MSU</sub>                  | /F and W/R Mode Select Setup Time                               | 5   |     | 5   |         | ns    |

| t <sub>NRH</sub>                  | /CAL, /G, and /WE Hold Time For /RE-Only Refresh                | 0   |     | 0   |         | ns    |

| t <sub>NRS</sub>                  | /CAL, /G, and /WE Setup Time For /RE-Only Refresh               | 5   |     | 5   |         | ns    |

| t <sub>PC</sub>                   | Column Address Latch Cycle Time                                 | 12  |     | 15  |         | ns    |

| t <sub>QCI</sub>                  | QLE High to /CAL Inactive                                       | 0   |     | 0   |         | ns    |

| t <sub>QH</sub>                   | QLE High Time                                                   | 5   |     | 5   |         | ns    |

| Cumbal                            | Description                                                             |     | -12    | -15 |        | Units  |

|-----------------------------------|-------------------------------------------------------------------------|-----|--------|-----|--------|--------|

| Symbol                            | Description                                                             | Min | Max    | Min | Max    | UIIIIS |

| t <sub>QL</sub>                   | QLE Low Time                                                            | 5   |        | 5   |        | ns     |

| t <sub>QQH</sub>                  | Data Hold From QLE Inactive                                             | 2   |        | 2   |        | ns     |

| t <sub>QQV</sub>                  | Data Valid From QLE Low                                                 |     | 7.5    |     | 7.5    | ns     |

| t <sub>RAC</sub> <sup>(1)</sup>   | Row Enable Access Time, On a Cache Miss                                 |     | 30     |     | 35     | ns     |

| t <sub>RAC1</sub> <sup>(1)</sup>  | Row Enable Access Time, On a Cache Hit (Limit Becomes t <sub>AC</sub> ) |     | 15     |     | 17     | ns     |

| t <sub>RAH</sub>                  | Row Address Hold Time                                                   | 1   |        | 1.5 |        | ns     |

| t <sub>RE</sub>                   | Row Enable Active Time                                                  | 30  | 100000 | 35  | 100000 | ns     |

| t <sub>RE1</sub>                  | Row Enable Active Time, Cache Hit (Row=LRR) Read Cycle                  | 8   |        | 10  |        | ns     |

| t <sub>REF</sub>                  | Refresh Period                                                          |     | 64     |     | 64     | ms     |

| t <sub>RGX</sub>                  | Output Enable Don't Care From Row Enable (Write, Cache Miss), DQ = Hi-Z | 9   |        | 10  |        | ns     |

| t <sub>RQX1</sub> (2,5)           | Row Enable High to Output Turn-On After Write Miss                      | 0   | 12     |     | 15     | ns     |

| t <sub>RP</sub>                   | Row Precharge Time                                                      | 20  |        | 25  |        | ns     |

| t <sub>RP1</sub>                  | Row Precharge Time, Cache Hit (Row=LRR) Read Cycle                      | 8   |        | 10  |        | ns     |

| t <sub>RRH</sub>                  | Write Enable Don't Care From Row Enable (Write Only)                    | 0   |        | 0   |        | ns     |

| t <sub>RSH</sub>                  | Last Write Address Latch to End of Write                                | 12  |        | 15  |        | ns     |

| t <sub>RSW</sub>                  | Row Enable to Column Address Latch Low For Second Write                 | 35  |        | 40  |        | ns     |

| t <sub>RWL</sub>                  | Last Write Enable to End of Write                                       | 12  |        | 15  |        | ns     |

| t <sub>SC</sub>                   | Column Address Cycle Time                                               | 12  |        | 15  |        | ns     |

| t <sub>SHR</sub>                  | Select Hold From Row Enable                                             | 0   |        | 0   |        | ns     |

| t <sub>SQV</sub> <sup>(1)</sup>   | Chip Select Access Time                                                 |     | 12     |     | 15     | ns     |

| t <sub>SQX</sub> <sup>(2,3)</sup> | Output Turn-On From Select Low                                          | 0   | 12     | 0   | 15     | ns     |

| t <sub>SQZ</sub> <sup>(4,5)</sup> | Output Turn-Off From Chip Select                                        | 0   | 8      | 0   | 10     | ns     |

| t <sub>SSR</sub>                  | Select Setup Time to Row Enable                                         | 5   |        | 5   |        | ns     |

| t <sub>T</sub>                    | Transition Time (Rise and Fall)                                         | 1   | 10     | 1   | 10     | ns     |

| t <sub>WC</sub>                   | Write Enable Cycle Time                                                 | 12  |        | 15  |        | ns     |

| t <sub>WCH</sub>                  | Column Address Latch Low to Write Enable Inactive Time                  | 5   |        | 5   |        | ns     |

| t <sub>WHR</sub> <sup>(6)</sup>   | Write Enable Hold After /RE                                             | 0   |        | 0   |        | ns     |

| t <sub>WI</sub>                   | Write Enable Inactive Time                                              | 5   |        | 5   |        | ns     |

| t <sub>WP</sub>                   | Write Enable Active Time                                                | 5   |        | 5   |        | ns     |

| t <sub>WQV</sub> <sup>(1)</sup>   | Data Valid From Write Enable High                                       |     | 12     |     | 15     | ns     |

| t <sub>WQX</sub> <sup>(2,5)</sup> | Data Output Turn-On From Write Enable High                              | 0   | 12     | 0   | 15     | ns     |

| t <sub>WQZ</sub> (3,4)            | Data Turn-Off From Write Enable Low                                     | 0   | 12     | 0   | 15     | ns     |

| t <sub>WRP</sub>                  | Write Enable Setup Time to Row Enable                                   | 5   |        | 5   |        | ns     |

| t <sub>WRR</sub>                  | Write to Read Recovery (Following Write Miss)                           |     | 12     |     | 15     | ns     |

<sup>(1)</sup> V<sub>QUT</sub> Timing Reference Point at 1.5V; (2) Parameter Defines Time When Output is Enabled (Sourcing or Sinking Current) and is Not Referenced to V<sub>OH</sub> or V<sub>QL</sub>; (3) Minimum Specification is Referenced from V<sub>IH</sub> and Maximum Specification is Referenced from V<sub>IL</sub> on Input Control Signal; (4) Parameter Defines Time When Output Achieves Open-Circuit Condition and is Not Referenced to V<sub>OH</sub> or V<sub>OL</sub>; (5) Minimum Specification is Referenced from V<sub>IL</sub> and Maximum Specification is Referenced from V<sub>IH</sub> on Input Control Signal; (6) On DM2213, t<sub>WHR</sub> Minimum is t<sub>DS</sub>

2-52

# Write-Per-Bit Cycle (/G=High) $t_{RE}$ /RE $t_{\mathsf{RSH}}$ $t_{CHR}$ $\mathrm{t}_{\mathrm{CAE}}$ /CAL - t<sub>RAH</sub> t<sub>ASC</sub> - t<sub>CAH</sub> $t_{ASR}$ $A_{0-10}$ Row Column $\leftarrow$ t<sub>MH</sub> $t_{CWL}$ $t_{MSU}$ W/R - t<sub>DMH</sub> $t_{\rm RWL}$ $t_{\text{WCH}}$ t<sub>DMS</sub> DQ<sub>0-7</sub> Mask Data $t_{DS}$ $\longrightarrow$ $\leftarrow$ t<sub>RRH</sub> **←** t<sub>DH</sub> → $t_{WRP}$ $\mathrm{t}_{\mathrm{WP}}$ $t_{\mathsf{MSU}}$ $\stackrel{-}{\longleftarrow}$ t<sub>MH</sub> - t<sub>SSR</sub> - t<sub>SHR</sub>

Don't Care or Indeterminate

Open

$t_{HZ} \longrightarrow$

NOTES: 1. Data mask bit high (1) enables bit write; data mask bit low (0) inhibits bit write.

2. Write-per-bit cycle valid only for DM2213.

$t_{HV} \longrightarrow$

- Open

/HIT -

# /F Refresh Cycle

Don't Care or Indeterminate

NOTES: 1. During /F refresh cycles, the status of W/R, /WE,  ${\rm A_{0-10}}$ , /CAL, /S, and /G is a don't care.

2. /RE inactive cache reads may be performed in parallel with /F refresh cycles.

# /RE-Only Refresh

Don't Care or Indeterminate

NOTES: 1. All binary combinations of  $A_{0-9}$  must be refreshed every 64ms interval.  $A_{10}$  does not have to be cycled, but must remain valid during row address setup and hold times.

2. /RE refresh is write cycle with no /CAL active cycle.

The information contained herein is subject to change without notice. Enhanced Memory Systems Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in an Enhanced product, nor does it convey or imply any license under patent or other rights.