# C713 53mm Inverter Thyristor 2000V / 1000A

The C713 reverse blocking thyristor is a pressure mounted, high current reverse blocking thyristor designed for power switching. It utilizes an involute interdigitated pilot gate and is manufactured by the proven multi-diffusion process.

# Features:

- · Off-State and Reverse Blocking Capabilities to 2000 Volts

- · Very Low Switching Losses at High Frequencies

- · 50 usec Maximum Turn-Off Time at Severe Operating Conditions with Feedback Diode

- · Involute, Interdigitated Gate for High di/dt Capability

- · Narrow Pulse Capability for PWM Inverter Commutating SCR Socket

- · 1" Creepage-Path, Glazed Ceramic Package

# MAXIMUM ALLOWABLE RATINGS

| TYPE   | V <sub>DRM</sub> /V <sub>RRM</sub> <sup>3</sup><br>REPETITIVE<br>T <sub>J</sub> = -40°C to +125°C | V <sub>DRM</sub> /V <sub>RRM</sub> 1<br>REPETITIVE<br>T <sub>J</sub> = 0°C to +125°C | TRANSIENT PEAK REVERSE  VOLTAGE, V <sub>RSM</sub> <sup>1</sup> T <sub>J</sub> = -40°C to +125°C |  |

|--------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|

| C713L  | 2000 Volts                                                                                        | 2100 Volts                                                                           | 2100 Volts                                                                                      |  |

| C713PT | 1900                                                                                              | 2000                                                                                 | 2000                                                                                            |  |

| C713PN | 1800                                                                                              | 1900                                                                                 | 1900                                                                                            |  |

| C713PS | 1700                                                                                              | 1800                                                                                 | 1800                                                                                            |  |

| C713PM | 1600                                                                                              | 1700                                                                                 | 1700                                                                                            |  |

| C713PE | 1500                                                                                              | 1600                                                                                 | 1600                                                                                            |  |

Consult factory for lower rated voltage devices.

| Peak One-Cycle Surge On-State Current, I <sub>TSM</sub> (8.3 msec)                 | 5,000 Amperes              |

|------------------------------------------------------------------------------------|----------------------------|

| (10 msec)                                                                          | 3,500 Amperes              |

| Maximum Rate-of-Rise of Anode Current Turn-On Interval (Switching From 1200 Volts) | 800 A/μsec                 |

| Repetitive di/dt Rating <sup>2</sup>                                               | 200 A/μsec                 |

| I <sup>2</sup> t (for fusing) (at 8.3 milliseconds)                                | npere <sup>2</sup> Seconds |

| Peak Gate Power Dissipation, P <sub>GM</sub>                                       | 100 Watts                  |

| Average Gate Power Dissipation, P <sub>G(AV)</sub>                                 | 5 Watts                    |

| Peak Reverse Gate Voltage, VGRM                                                    | 20 Volts                   |

| Storage and Operating Temperature, T <sub>STG</sub> and T <sub>I</sub>             | 40°C to +125°C             |

| Mounting Force Required                                                            | + 1000 - 0 Lb.             |

| 22.2 K                                                                             | N + 4.4 - 0 KN             |

#### NOTES:

<sup>110</sup> msec voltage sinewaye

<sup>2</sup> di/dt rating established in accordance with EIA-NEMA Standard RS-397, Section 5.2.2. This di/dt is in addition to the discharge of a 0.25  $\mu$ f. 20 ohm snubber circuit in parallel with the DUT.

# **CHARACTERISTICS**

| TEST                                                                                                           | SYMBOL                                      | MIN.     | TYP.     | MAX. | UNITS   | TEST CONDITIONS                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------|----------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Peak Reverse and On-<br>State Blocking Current                                                                 | l <sub>DRM</sub><br>and<br>l <sub>RRM</sub> | -        | 20       | 60   | mA      | $T_J = +125$ °C, $V = V_{DRM} = V_{RRM}$                                                                                                                                                                                                                                  |

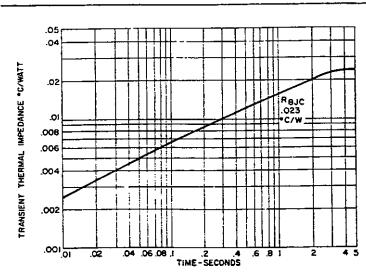

| Effective Thermal Resistance, Junction-to-Case                                                                 | R <sub>∂JC</sub>                            | -        |          | .023 | °C/Watt | Double-Side Cooled (DC)                                                                                                                                                                                                                                                   |

| Critical Linear Rate-of-Rise<br>of Forward Blocking Volt-<br>age (Higher values may<br>cause device switching) | dv/dt                                       | 500      | <u>-</u> | _    | V/μsec  | T <sub>J</sub> = +125°C, V <sub>DRM</sub> = .80 Rated V <sub>RRM</sub><br>Gate Open.                                                                                                                                                                                      |

| Delay Time                                                                                                     | ta                                          | -        | 1.5      |      | μsec    | Switching from 1000 Volts, 20 Volt, 10 Ohm Gate 0.5 µsec Rise Time, T <sub>J</sub> = 25°C                                                                                                                                                                                 |

| Gate Pulse Width<br>Necessary To Trigger                                                                       |                                             | 10       | -        | _    | μsec    | T <sub>3</sub> = 25°C                                                                                                                                                                                                                                                     |

| Gate Trigger Current                                                                                           | I <sub>GT</sub>                             | -        | 120      | 200  | mAdc    | $T_C = 25^{\circ}C, V_D = 10 \text{ Vdc}, R_L = 3 \text{ Ohms}$                                                                                                                                                                                                           |

|                                                                                                                |                                             | 5.0      | 30       | _    |         | $T_C = +125^{\circ}C$ , $V_D = .5 \times Rated$ , $R_L = 1000 \text{ Ohms}$                                                                                                                                                                                               |

| Gate Trigger Voltage                                                                                           | V <sub>GT</sub>                             |          | 3.0      | 5.0  | Vdc     | $T_C = 0^{\circ}\text{C to } + 125^{\circ}\text{C}, V_D = 10 \text{ Vdc}, R_L = 3 \text{ Ohms}$                                                                                                                                                                           |

| Peak On-State Voltage                                                                                          | V <sub>TM</sub>                             | -        | -        | 1.7  | Voits   | $T_C$ = +125°C, $I_T$ = 1000 Amps. Peak<br>Duty Cycle $\leq 0.01\%$                                                                                                                                                                                                       |

| Conventional Circuit Commutated Turn-Off Time(1) (With Reverse Voltage)                                        | t <sub>q</sub>                              | _        | 45       | 50   | µѕес    | (1) Tc = + 125 °C (2) It = 1000 amps (3) Vr ≥ 50 volts (4) Rate of Rise of Forward Blocking Voltage = 200V/usec to 80% Vdrm or 400V/usec to 70% of Vdrm (5) Gate Bias = Open During Turn-Off Interval 0 Volts, 100 ohms. (6) Duty Cycle ≤ 0.01%                           |

| Conventional Circuit Commutated Turn-Off Time(1) (With Feedback Diode)                                         | tq                                          | <u>-</u> | 50       | 55   | µsec    | <ul> <li>(1) Tc = +125 °C</li> <li>(2) It = 1000 amps</li> <li>(3) Vr = 2 Volts Min.</li> <li>(4) Rate of Rise of Forward Blocking<br/>Voltage = 400 V/usec to 80% Vdrm</li> <li>(5) Gate Bias = Open During Turn-Off Interval</li> <li>(6) Duty Cycle ≤ 0.01%</li> </ul> |

<sup>(1)</sup> Turn-off times are measured on a go/no-go basis using LEM test equipment. Experimental determination of critical turn-off times may lead to device degradation.

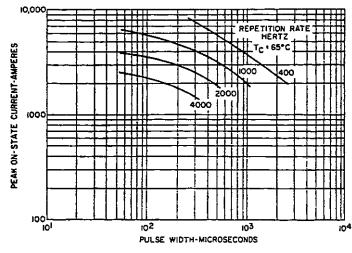

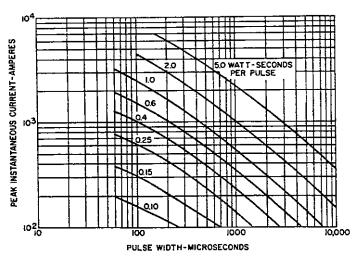

1. MAXIMUM ALLOWABLE PEAK ON-STATE CURRENT VS. PULSE WIDTH AT  $T_C = 65^{\circ}C$  FOR SINUSOIDAL CURRENT WAVEFORMS

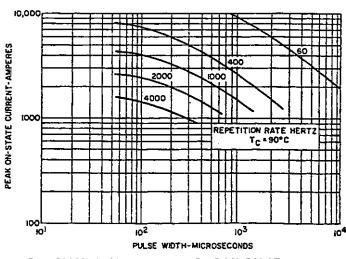

2. MAXIMUM ALLOWABLE PEAK ON-STATE CURRENT VS. PULSE WIDTH AT  $T_C = 90^{\circ}$ C FOR SINUSOIDAL CURRENT WAVEFORMS

#### NOTES:

- Switching capability and losses with bypass diode.

- 2. Switching voltage from 15 Volts to 0.8 VDRM.

- 3. Snubber discharge < 50 Amps. RC time constant < 10  $\mu \rm sec$ .

- 4. High gate drive, 20 V/10 Ohms,  $0.5\,\mu\mathrm{sec}$  rise time.

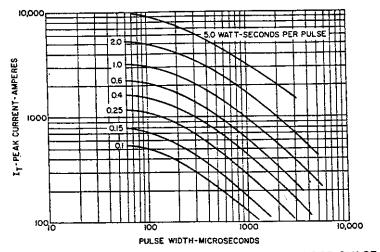

3. ENERGY PER PULSE FOR SINUSOIDAL PULSES

ACC - STATE CURRENT - AMPERES ON - STATE COOL IO - STATE COUNTY - AMPERICA ON - STATE COOL IO - STATE COUNTY - AMPERICA ON - STATE C

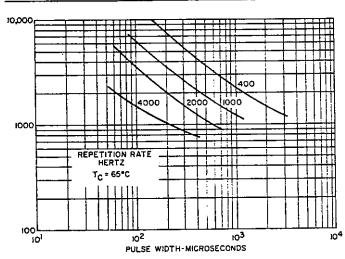

4. MAXIMUM ALLOWABLE PEAK ON-STATE CURRENT FOR TRAPEZOIDAL CURRENT WAVEFORMS FOR  $T_C = 65^{\circ}C$

5. MAXIMUM ALLOWABLE PEAK ON-STATE CURRENT FOR TRAPEZOIDAL CURRENT WAVEFORMS FOR  $T_C = 90^{\circ}C$

## NOTES:

- 1. Switching voltage from 15 Volts to 0.8 VDRM-

- 2. DI/DT during turn-on: 100A/µsec.

- 3 Reverse voltage < 50 Volts. If no bypass diode is used, recovery switching losses must be added.

- RC snubber time constant < 10 μsec.</li>

- 5. High gate drive: 20V/10 Ohms, 0.5 µsec rise time.

6. ENERGY PER PULSE FOR TRAPEZOIDAL CURRENT WAVEFORMS

IRM (REC)-PEAK RECOVERY CURRENT-AMPERES dî<sub>R</sub>/di 60 70 80 90 100 50

MAX. I RM (REC.)

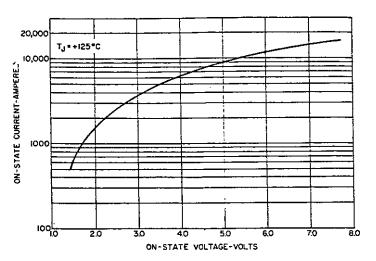

7. FORWARD CONDUCTION CHARACTERISTIC **ON-STATE**

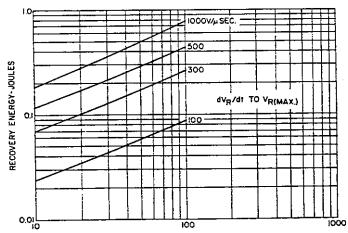

8. RECOVERED CHARGE (125°C)

di<sub>R</sub>/d1 - (A/µs)

DIR OT-AMPERES PER MICROSECOND

#### NOTES:

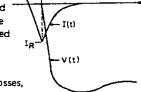

If no bypass diode is used with this thyristor, the switching losses during recovery can be significant. The actual magnitude of these losses will vary widely depending on circuit conditions and snubber design. The switching losses in a given circuit may be calculated with SLR =  $\int_{0}^{\infty} \tilde{I}(t) . V/t$  dt the following equation:

Where SLR is the recovery switching losses; I (t) is the recovery current decay; V(t) is the recovery voltage; and t = o occurs at the peak of the recovery current. I (t) may be expressed as an exponential decay:

$$I(t) = I_{Re} - (t/T)$$

Where IR is the peak recovery current and  $T = 2.5 \mu sec.$  The junction temperature rise due to the recovery losses may be computed as follows:

000

-REVERSE RECOVERY

$$\Delta T_j = F \cdot \sigma_A \cdot R_{\theta JA} + \alpha_A \cdot 3.5$$

Where O a is the recovery losses,

$R\theta_{

m JA}$  is the DC junction to ambient thermal impedance, and F is the operating frequency.

This curve represents the maximum recovery loss as a function of circuit di/dt, and different assumed linear dv/dts.

# 9. RECOVERY CURRENT SWITCHING LOSSES

# NOTES:

- 1. Add .006°C/W to account for both case to dissipator interfaces when properly mounted; e.g., Rajs = .029° C/W. See Mounting Instructions.

- 2. DC Thermal Impedance is based on average full cycle junction temperature.

10. TRANSIENT THERMAL RESISTANCE -JUNCTION-TO-CASE

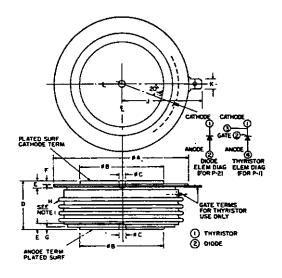

#### **OUTLINE DRAWING**

| SYMBOL | INCHES |       | MILLIN | NOT50 |       |

|--------|--------|-------|--------|-------|-------|

|        | MIN.   | MAX.  | MIN.   | MAX.  | NOTES |

| φΑ     |        | 2.960 |        | 75.18 |       |

| φВ     | 1.800  | 1.900 | 45.72  | 48.26 |       |

| φC     | 0.136  | 0.146 | 3.45   | 3.71  |       |

| D      | 1.000  | 1.070 | 25.40  | 27.18 |       |

| E      | .070   | 1.00  | 1.78   | 2.54  |       |

| F      | .030   | _     | 0.76   |       |       |

| G      | .005   | .067  | 0.13   | 1.70  |       |

| н      |        | _     |        | _     | 1     |

| j      | 1.680  | 1.710 | 42.67  | 43.43 |       |

| К      | .186   | .189  | 4.72   | 4.80  |       |

|        |        |       |        |       |       |

#### NOTES:

- Glazed ceramic insulator with 1.00-inch (25.40mm) surface creepage, min.

- Lead lengths are 12" (30.5cm.) with eyelet terminals to accompdate no.6 or M3 screws.

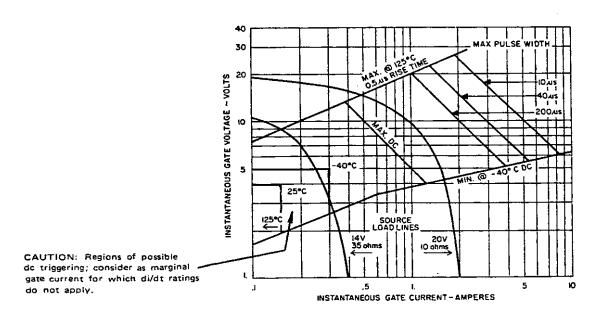

11. GATE TRIGGER CHARACTERISTICS

AND POWER RATINGS

### SUGGESTED MOUNTING METHODS FOR PRESS-PAKS TO HEAT DISSIPATORS

When the Press-Pak is assembled to a heat sink in accordance with the following general instructions, a reliable and low thermal resistance interface will result.

- 1. Check each mating surface for nicks, scratches, flatness and surface finish. The heat dissipator mating surfaces should be flat within .0005 inches and have a surface finish of 63 micro-inches.

- 2. It is recommended that the heat dissipator be plated with nickel or tin. Bare aluminum or copper surfaces will oxidize in time resulting in excessively high thermal resistance.

- 3. Sand each surface lightly with 600 grit paper just prior to assembly. Clean off and apply silicone oil (GE SF1154 200 centistoke viscosity) or silicone grease (GE G623 or Dow Corning DC3, 4, 340 or 640). Clean off and apply again as a thin film. (A thick film will adversely affect the electrical and thermal resistances.)

- 4. Assemble with the specified mounting force applied through a self-leveling, swivel connection. The force has to be evenly distributed over the full area. Center holes on both top and bottom of the Press-Pak are for locating purposes only.