### **Product Features**

- High Speed Clock support provides a 267 to 400MHz differential clock source for Direct Rambus® memory systems for an 1.6 GbPS data transfer rate

- Synchronization Flexibility provides signals to synchronize the clock domains of the Rambus® Channel with an external system or processor clock, provided by C9801, C9812, C9830, C9840, C9850, C9851, and C9853.

- Power Management Support permits channel clocks to be enabled and disabled as required

- Supports Independent Channel Clocking

- 24 pin 150 mil SSOP Package

- Supports Intel Architecture platforms

### **Product Description**

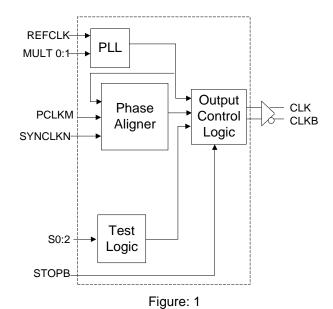

The C9822 is a Rambus® compliant DRCG clock synchronizer. It contains a Phase Locked Loop that provides complimentary Rambus® memory clocks. Included in its functionality is the control logic to phase and frequency synchronizing the device's output clocks with the system reference clock. Power management logic is also provided for Mobile application and green PC functionality. Also included are separate power pins for each internal functional block so as to minimize interaction of these sections with each other and thus maximize the device performance.

### **Block Diagram**

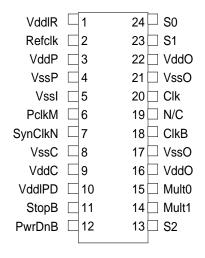

### **Pin Configuration**

Figure: 2

### **Pin Description**

| Pin No.      | Pin Name                | I/O      | Description                                                                                                   |

|--------------|-------------------------|----------|---------------------------------------------------------------------------------------------------------------|

| 2            | REFCLK                  | l        | Reference clock input. Normally supplied by a system clock source generator.                                  |

| 6            | PCLKM                   | ı        | Phase detector input: The phase difference between this signal and SYNCLKN is                                 |

|              |                         |          | used to synchronize the Rambus®channel Clock with the system clock. Both the                                  |

|              |                         |          | PCLKM and SYNCLKN are provided by the memory controller. If the gear ratio is                                 |

|              | 0)(1)(1)                |          | not used, connect this pin to ground.                                                                         |

| 7            | SYNCLKN                 | l        | Phase detector input: The phase difference between this signal and PCLKM is                                   |

|              |                         |          | used to synchronize the Rambus® Channel Clock with the system clock. PCLKM                                    |

|              |                         |          | and SYNCLKN are provided by the memory controller. If the gear ratio is not used, connect this pin to ground. |

| 11           | STOPB                   | ı        | Clock Stop. When this input is driven to low state, the differential Rambus®                                  |

|              |                         | '        | channel clocks are disabled.                                                                                  |

| 12           | PWRDNB                  | I        | Power Down. When this input is driven to a logic low level, the differential                                  |

|              |                         |          | Rambus® channel clocks are disabled and the system clock generator is placed                                  |

|              |                         |          | in a power-down mode.                                                                                         |

| 15, 14       | MULT (0:1)              | l        | PLL Multiplier Select: These inputs select the PLL prescaler and feedback                                     |

| 10.00        | CL KB CL K              | 0        | dividers to determine the multiply ratio for the PLL from the input REFLCK.                                   |

| 18, 20       | CLKB, CLK<br>S0, S1, S2 | <u> </u> | Differential Rambus ® channel clock outputs.                                                                  |

| 24, 23<br>13 | 50, 51, 52              | ı        | These input pins control the operating mode of the device.                                                    |

| 19           | NC                      | -        | No Connect. DO NOT CONNECT ANY VOLTAGE LEVELS TO THIS PIN.                                                    |

| 1            | VDDIR                   | RefV     | Base voltage reference level for the device's input reference clock.                                          |

| 10           | VDDIPD                  | RefV     | Base voltage reference for the PCLKM, SYNCLKN, and STOPB.                                                     |

| 9            | VDDC                    | Р        | Power supply connection for the devices phase aligner circuitry. Connected to 3.3V supply.                    |

| 3            | VDDP                    | Р        | Power supply for Analog PLL circuitry. Connected to 3.3V supply.                                              |

| 16, 22       | VDDO                    | Р        | Power supply clock output buffers. Connected to 3.3V supply. Care should be                                   |

|              |                         |          | taken when routing these power supply connections so as to not have their power                               |

|              |                         |          | supply current is adequately bypassed (as close to the device as possible) and                                |

|              |                         |          | their switching noise (surges) does not couple into the other device power supplies.                          |

| 8            | VSSC                    | Р        | Power supply ground return connection for the devices phase aligner circuitry.                                |

|              |                         | _        | Connected to system ground.                                                                                   |

| 5            | VSSI                    | Р        | Reference supply ground for control input signals.                                                            |

| 4            | VSSP                    | Р        | Power supply ground return connection for Analog PLL circuitry. Should be                                     |

| 47.04        | V000                    |          | connected to system ground potential through a well bypassed path.                                            |

| 17, 21       | VSSO                    | Р        | System Ground for clock output buffers. Care should be taken when routing these                               |

|              |                         |          | power return connections so as to not have their power return current shared with                             |

|              |                         |          | other power return paths of the device.                                                                       |

A bypass capacitor (0.1μF) should be placed as close as possible to each Vdd pin. If these bypass capacitors are not close to the pins their high frequency filtering characteristic will be canceled by the lead inductance's of the traces.

### **System Clock Configuration**

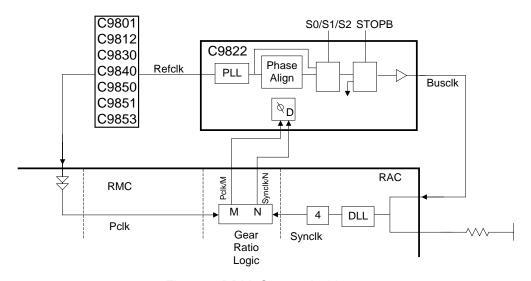

Figure 3 shows the clocking configuration for an example Direct Rambus subsystem. The configuration shows the interconnection of the system clock source, the C9822, and the clock signals of a memory controller ASIC. The ASIC contains the RAC, the Rambus Memory Controller protocol engine (RMC), and logic to support synchronizing the Channel clock with the controller clock (This diagram represents the differential clocks as a single Busclk wire).

Figure: 3 DDLL System Architecture

This configuration achieves frequency-lock between the controller and Rambus Channel clocks (Pclk and Synclk). these clock signals are matched and phase-aligned at the RMC/RAC boundary in order to allow data transfers to occur across this boundary without additional latency.

The main clock source drives the system clock (Pclk) to the ASIC, and also drives the reference clock (Refclk) to the C9822. Refclk is not the same frequency as Pclk. A PLL inside the C9822 multiplies Refclk to generate the desired frequency for Busclk. Busclk is driven on the Rambus Channel through a terminated transmission line. At the mid-point of the Channel, the RAC senses Busclk using its own DLL for clock alignment, followed by a fixed divide-by-4 circuit that generates SynClk.

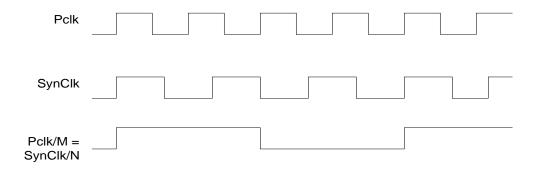

Pclk is the clock used in the Rambus memory controller (RMC) in the ASIC. SynClk is the clock used at the ASIC interface of the RAC. the C9822 together with the Gear Ratio Logic enables the controller to exchange data directly from the Pclk domain to the SynClk domain without incurring additional latency for synchronization. In general, Pclk and SynClk can run at different frequencies, so the Gear Ratio Logic must select the appropriate M and N dividers such that the frequencies of Pclk/M and SynClkN are equal. In one example, Pclk = 133 MHz and SynClk = 100 MHz, and M = 4 while N = 3, giving Pclk/M = SynClk/N = 33 MHz.

The ASIC drives the output clocks, Pclk and SynClk/N from the Gear Ratio Logic to the C9822 Phase Detector inputs. The routing of the Pclk/M and SynClk/N signal traces must be matched in impedance and propagation delay on the ASIC as well as on the board. These signals are not part of the Rambus Channel and their routing must be matched by board designers.

### **System Clock Configuration (Cont.)**

After comparing the phases of Pclk/M and SynClk/N, the C9822 Phase Detector drives a phase aligner that adjusts the phase of the C9822 output clock, busclk. Since the other elements in the distributed loop have a fixed delay, adjusting Busclk adjusts the phase of SynClk and thus the phase of SynClk/N.

In this manner, the distributed loop adjusts the phase of SynClk/N to match that of Pclk/M, eliminating the phase error at the input of the C9822. When the clocks are aligned, data can be exchanged directly from the Pclk domain to the SynClk domain.

The Gear Ratio Logic supports four clock ratios (1.0, 1.33, 1.5, 2.0), where the ratio is defined as the ratio of Pclk/SynClk. Since Busclk - 4\*synClk, this ratio also is equal to 4\*Pclk/busclk.

In addition, the device is able to receive input signals that are generated from different voltage power supplies. The controller output voltage supply is connected to the pin VDDIPD of the C9822, and is used as the reference for the two-phase detector input signal, PclkM and SynClkN. The output voltage supply is also used as the reference for the output enable/disable signal, StopB.

The reference clock comes from the main clock source chip. The main clock source output voltage supply is connected to the pin VDDIR of C9822, and is used as the reference for the Refclk input signal.

### **Table of Frequencies and Gear Ratios**

#### **Gear Ratio Timing Diagram**

Figure: 4

## Table of Frequencies and Gear Ratios (Cont.)

| Pclk | Refclk | Busclk | Synclk | Α  | В | М | N | Ratio | F@PD |

|------|--------|--------|--------|----|---|---|---|-------|------|

| 67   | 33     | 267    | 67     | 8  | 1 | 2 | 2 | 1.0   | 33   |

| 100  | 50     | 300    | 75     | 6  | 1 | 8 | 6 | 1.33  | 12.5 |

| 100  | 50     | 267    | 67     | 16 | 3 | 6 | 4 | 1.5   | 16.7 |

| 133  | 67     | 356    | 89     | 16 | 3 | 6 | 4 | 1.5   | 22   |

| 133  | 67     | 400    | 100    | 6  | 1 | 8 | 6 | 1.33  | 16.7 |

| 200  | 100    | 400    | 100    | 4  | 1 | 4 | 2 | 2     | 50   |

Table 1A. Frequencies, Dividers, and Gear Ratios

A: Feedback divider in the DRCG PLL.

B: Refclk divider in the DRCG PLL

M: Pclk divider in the gear ratio logic.

N: synclk divider in the gear ratio logic.

Table 1A above shows several supported Pclk and Busclk frequencies, the corresponding A and B dividers required in the DRCG PLL, and the corresponding M and N dividers in the gear ratio logic. The column Ratio gives the Gear Ratio as defined by Pclk/Synclk (same as M/N). The column F@PD gives the divided down frequency (in MHz) at the Phase Detector, where F@PD = Pclk/M = Synclk/N.

Table 1B below show examples of CLK/CLKB frequencies for different DRCG input frequencies.

| Mult0 | Mult1 | DRCG input Frequency | CLK and CLKB output frequency |

|-------|-------|----------------------|-------------------------------|

| 0     | 0     | 75 MHz               | 300 MHz                       |

| 0     | 1     | 50 MHz               | 300 MHz                       |

| 1     | 0     | 50 MHz               | 267 MHz                       |

| 1     | 1     | 50 MHz               | 400 MHz                       |

| 0     | 0     | 66 MHz               | 267 MHz                       |

| 0     | 1     | 66 MHz               | 400 MHz                       |

| 1     | 0     | 66 MHz               | 356 MHz                       |

| 1     | 1     | 33 MHz               | 267 MHz                       |

Table 1B: CLK and CLKB example frequencies

# **Selection Logic**

| Mult0 | Mult1 | А  | В |

|-------|-------|----|---|

| 0     | 0     | 4  | 1 |

| 0     | 1     | 6  | 1 |

| 1     | 0     | 16 | 3 |

| 1     | 1     | 8  | 1 |

Table 2: PLL Divider Selection

### **Selection Logic (Cont.)**

Table 2 shows the logic for selecting the PLL prescaler and feedback dividers to determine the multiply ratio for the PLL from the input Refclk. Divider A sets the feedback and divider B sets the prescaler, so the PLL output is set by: PLLclk = Refclk\*A/B.

| Mode     | StopB | Clk          | ClkB         |

|----------|-------|--------------|--------------|

| Normal   | 1     | PAclk        | PAclkB       |

| Clk Stop | 0     | $V_{X,STOP}$ | $V_{X,STOP}$ |

Table 3: Clk Stop Mode Selection

Table 3 shows the logic for enabling the clock outputs, using the StopB input signal. When StopB is high, the DRCG is in its normal mode, and Clk and ClkB are complementary outputs following the Phase Aligner output (PAclk). When StopB is low, the DRCG is in the Clk Stop mode, the output drivers are both disabled (set to Hi-Z), and the Clk and ClkB outputs both drive DC voltages ( $V_{X,STOP}$ ) as given in Table 11. The level of  $V_{X,STOP}$  is set by internal resistor dividers.

| Mode             | S0 | S1 | S2 | Bypclk (Int.) | Clk    | ClkB    |

|------------------|----|----|----|---------------|--------|---------|

| Normal           | 0  | 0  | 0  | Gnd           | PAclk  | PAclkB  |

| Bypass           | 1  | 0  | 0  | PLLclk        | PLLclk | PLLclkB |

| Test             | 1  | 1  | 0  | Refclk        | Refclk | RefclkB |

| Vendor Test A    | 0  | 0  | 1  | -             | -      | -       |

| Vendor Test B    | 1  | 0  | 1  | -             | -      | -       |

| Reserved         | 1  | 1  | 1  | -             | -      | -       |

| Output Test (OE) | 0  | 1  | Х  | -             | Hi-Z   | Hi-Z    |

Table 4: Bypass and Test Mode Selection

### **Power Management Functions**

| Mode      | PwrDnB | Clk   | ClkB   |

|-----------|--------|-------|--------|

| Normal    | 1      | PAclk | PAclkB |

| PowerDown | 0      | Gnd   | Gnd    |

Table 5: Powerdown Mode Selection

Table 5 shows the logic for selecting the Powerdown mode, using the PwrDnB input signal. PwrDnB is active low (enabled when 0). When PwrDnB is disabled, the DRCG is in its normal mode. When PwrDnB is enabled, the DRCG is put into a powered-off state, and the Clk and ClkB outputs are both low (ground).

### **Power Management Functions (Cont.)**

The device is able to turn off the Rambus Channel clock to minimize power for mobile and other power-sensitive applications. In the "clock off" mode, the device remains on while the output is disabled, allowing fast transitions between the clock-off and clock-on states. This mode could be used in conjunction with the Nap mode of the RDRAMs and Rambus ASIC Cell (RAC). When output clocks are in a power down mode they are driven to and held at a logic low level by the device.

In the "power down" mode, the device is completely powered down for minimum power dissipation. This mode is used in conjunction with the power down modes of the RDRAMs and RAC.

The device has three operating states: Normal, Clock off and Powerdown. In normal mode, the clock source is on, and the output is enabled. In Clock off mode, the clock source is on, but the output is disabled (StopB asserted). In powerdown mode, the device is powered down with the control signal PwrDnB equal to 0. the control signals Mult0, Mult1, S0, S1, and S2 must be stable before power is applied to the device, and can only be changed in power-down mode (PwrDnB=0).

### **Power Management Modes**

| State     | PwrDnB | StopB |

|-----------|--------|-------|

| Normal    | 1      | 1     |

| Clock Off | 1      | 0     |

| Powerdown | 0      | Х     |

Table 6: Control Signals for Clock Source States

Upon applying power to the device, the device can enter any state, depending on the settings of the control signals, PwrDnB and StopB. the clock source output need not be glitch-free during state transitions.

### **State Transitions**

The clock source has three fundamental operating states. Figure 5 shows the state diagram with each transition labeled A through J. Note that the clock source output need NOT be glitch-free during state transitions.

Figure 5: Clock Source State Diagram

Upon powering up the device, the device can enter any state, depending on the settings of the control signals PwrDnB and StopB.

In Powerdown mode, the clock source is powered down with the control signal, PwrDnB, equal to 0. The control signals S0, S1, and S2 must be stable before power is applied to the device, and can only be changed in Powerdown mode (PwrDnB=0). The reference inputs, VddIR and VddIPd, may remain on or may be grounded during the Powerdown mode.

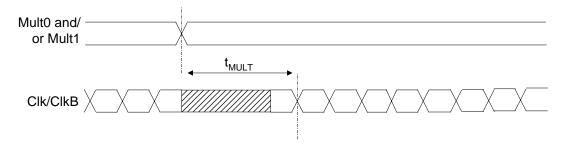

The control signals Mult0, Mult1 can be used in two ways. If they are changed during Powerdown mode, then the Powerdown transition timings determine the settling time of the DRCG. However, the Mult0 and Mult1 control signals can also be changed during Normal mode. When the Mult control signals are "hot swapped" in this manner, the Mult transition timings determine the settling time of the DRCG.

In Clk Stop mode, the clock source is on, but the output is disabled (StopB de-asserted). The VddIPD reference input may remain on or may be grounded during the Clk Stop mode. The VddIR reference input must remain on during the Clk Stop mode.

## **State Transitions Timing Diagrams**

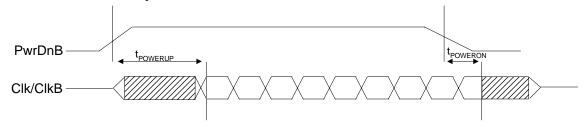

### **Powerdown Exit and Entry**

Figure: 6

# StopB Clk/ClkB Output clock not specified, glitches may occur. Clock enabled and glitch free Clock output settled within 50 pS of the phase before disabled.

Figure: 7

# **Mult Transition Timing Diagrams**

Figure: 8

# **Transition Specifications**

| Transition | From                  | То        | Transition Latency (target spec) |              | Description                                                                                          |

|------------|-----------------------|-----------|----------------------------------|--------------|------------------------------------------------------------------------------------------------------|

|            |                       |           | Symbol                           | Max          |                                                                                                      |

| А          | Powerdown             | Normal    | tPOWERUP                         | 3 ms         | Time from PwrDnB ↑ to Clk/ClkB output settled (excluding tDISTLOCK).                                 |

| С          | Powerdown             | Clk Stop  | tPOWERUP                         | 3 ms         | Time from PwrDnB \(\hat{\tau}\) to when the internal PLL and clock has turned on and settled.        |

| G          | Vdd on                | Normal    | tPOWERUP                         | 3 ms         | Time from Vdd is applied and settled to Clk/ClkB output settled (excluding tDISTLOCK).               |

| Н          | Vdd on                | Clk Stop  | tPOWERUP                         | 3 ms         | Time from Vdd is applied and settled to the internal PLL and clock has turned on and settled.        |

| J          | Normal                | Normal    | tMULT                            | 1 ms         | Time from Mult0 or Mult1 change to Clk/ClkB output re-settled (excluding tDISTLOCK).                 |

| Е          | Clk Stop              | Normal    | tCLKON                           | 10 ns        | Time from StopB ↑ to when Clk/ClkB provides glitch-free clock edges.                                 |

| E          | Clk Stop              | Normal    | tCLKSETL                         | 20<br>cycles | Time from stopB 1 to Clk/ClkB output settled to within 50 ps of the phase before StopB was disabled. |

| F          | Normal                | Clk Stop  | tCLKOFF                          | 5 ns         | Time from StopB √to Clk/BlkB output disabled.                                                        |

| B,D        | Normal or<br>Clk Stop | Powerdown | tPOWERDN                         | 1ms          | Time from PwerDnB √ to the device in Powerdown.                                                      |

Table 7: State Transition Latency Specifications

### **Transition Specifications (Cont.)**

Figure 7 shows that the Clk Stop to Normal transition goes through three phases. During tCLKON, the clock output is not specified and can have glitches. For tCLKON < t<tCLKSETL, the clock output is enabled and must be glitchfree. For t>tCLKSETL, the clock output phase must be settled to within 50 ps of the phase before the clock output was disabled. At this time, the clock output must also meet the voltage and timing specifications in Table 11. The outputs are in a high impedance state during the Clk Stop mode (see Table 7). The above specification apply when the output has been held in the ClkStop state for less than tSTOP of Table 8.

| Symbol | Min | Max | Units | Description                                                              |

|--------|-----|-----|-------|--------------------------------------------------------------------------|

| tSTOP  |     | 100 | μS    | Max time in Clk Stop (StopB=0) before re-entering Normal mode (StopB=1). |

| tON    | 100 |     | nS    | Min time in Normal mode (StopB=1) before re-entering Clk Stop (StopB=0)  |

Table 8: StopB Control Timing

After the DRCG PLL has settled, the distributed loop containing the phase aligner must also settle. This settling time depends on components in the distributed loop which are outside of the clock source. Therefore, this settling time is not a component specification.

The maximum lock time for the distributed loop is specified in Table 9 below. Note that the total time for the output clock to settle from the Powerdown state to the Normal state is the sum of tPOWERUP plus tDISTLOCK. Similarly, if the Mult0 and Mult1 control signals are changed during the Normal state, the total time for the output clock to resettle is the sum of tMULT plus tDISTLOCK.

| Symbol    | Min | Max | Units | Description                                                                                                                                      |

|-----------|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| tDISTLOCK |     | 5   | mS    | Time from when Clk/ClkB output is settled to when the phase error between SynClkN and PclkM falls with the t <sub>ERR-PD</sub> spec in Table 11. |

Table 9: Distributed Loop Lock Time Specification

### **Maximum Ratings**

| Voltage Relative to VSS: | -0.3V          |

|--------------------------|----------------|

| Voltage Relative to VDD: | 0.3V           |

| Storage Temperature:     | 0°C to + 125°C |

| Ambient Temperature:     | 0°C to +70°C   |

| Maximum Power Supply:    | 7V             |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range:

VSS<(Vin or Vout)<VDD

Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

### **DC Parameters**

| Characteristic                                                | Symbol          | Min     | Тур              | Max       | Units  | Conditions |

|---------------------------------------------------------------|-----------------|---------|------------------|-----------|--------|------------|

| Supply Voltage                                                | $V_{DD}$        | 3.135   | -                | 3.465     | V      |            |

| Input (scalable CMOS)<br>Signal Low Voltage                   | V <sub>IL</sub> | -       | -                | 0.3       | Vdd    |            |

| Input (scalable CMOS)<br>Signal High Voltage                  | V <sub>IH</sub> | 0.7     | -                | -         | Vdd    |            |

| Refclk Input Low Voltage                                      | $V_{IL,R}$      | -       | -                | 0.3       | VddlR  |            |

| Refclk Input High Voltage                                     | $V_{IH,R}$      | 0.7     | -                | -         | VddlR  |            |

| Input Low Voltage                                             | $V_{IL,PD}$     | -       | -                | 0.3       | VddIPD |            |

| Input High Voltage                                            | $V_{IH,PD}$     | 0.7     | -                | -         | VddIPD |            |

| Input Supply Reference                                        | $V_{DDI,R,}$    | 1.235   | -                | 3.465     | V      |            |

| Input Supply Reference for PD inputs                          | $V_{DDI,PD}$    | 1.235   |                  | 2.625     | V      |            |

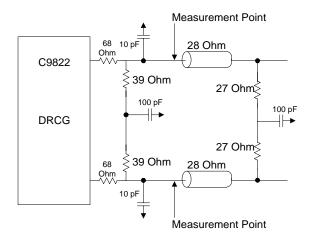

| Channel Impedance                                             | Z <sub>CH</sub> |         | 28               |           | ohms   |            |

| Tri-State leakage Current                                     | loz             |         |                  | 50        | uA     |            |

| Current in Powerdown state                                    | Ipowerdown      |         |                  | 200       | uA     |            |

| (PwrDnB=0)                                                    |                 |         |                  |           |        |            |

| Current in Clk Stop state (stopB = 0)                         | Iclkstop        |         |                  | 50        | mA     |            |

| Current in Normal state (stopB = 1)                           | Inormal         |         |                  | 100       | mA     |            |

| Reference Current in<br>Powerdown state<br>(PwrDnB=0)         | Iref,pwdn       |         |                  | 50        | μА     |            |

| Reference Current in<br>Normal or ClkStop state<br>(PwrDnB=1) | Iref,norm       |         |                  | 2         | mA     |            |

|                                                               |                 | =3.3V±5 | 5 <b>%, TA</b> = | 0°C to +7 | 70°C   |            |

Note 1. DC bias = 0.9V, and  $V_{AC}$  < 100mV

Table 10: Electrical Characteristics

### **Device Parameters**

| Characteristic                                                                                                                 | Symbol                            | Min  | Тур | Max  | Units   | Conditions |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|-----|------|---------|------------|

| Output Duty Cycle over 10,000 cycles                                                                                           | DC                                | 40%  | 50% | 60%  | t cycle |            |

| Clock cycle time                                                                                                               | t <sub>CYCLE</sub>                | 2.5  | -   | 3.75 | nS      |            |

| Jitter over 1-6 clock cycles at 400 Mhz <sup>a</sup>                                                                           |                                   | -    |     | 100  | pS      |            |

| Jitter over 1-6 clock cycles at 356 Mhz <sup>a</sup>                                                                           | tj                                | -    |     | 140  | pS      |            |

| Jitter over 1-6 clock cycles at 300 Mhz <sup>a</sup>                                                                           |                                   | -    |     | 140  | pS      |            |

| Jitter over 1-6 clock cycles at 267 MHz <sup>a</sup>                                                                           |                                   | -    |     | 160  | pS      |            |

| Phase Aligner phase step size (at Clk/ClkB)                                                                                    | t <sub>STEP</sub>                 | 2    |     |      | pS      |            |

| Phase Detector phase error for distributed loop<br>Measured at PcklM-SynclkN (rising edges) (does not<br>include clock Jitter) | t <sub>ERR,PD</sub>               | -100 | -   | 100  | pS      |            |

| PLL output phase error when tracking SSC                                                                                       | t <sub>ERR,SSC</sub>              | -100 | -   | 100  | pS      |            |

| Output voltage during Clk Stop (StopB=0)                                                                                       | $V_{X,STOP}$                      | 1.1  | -   | 2.0  | V       |            |

| Output crossing-point voltage                                                                                                  | $V_X$                             | 1.3  | -   | 1.8  | V       |            |

| Output voltage swing <sup>b</sup>                                                                                              | V <sub>cos</sub>                  | 0.4  | -   | 0.6  | V       |            |

| Output high voltage                                                                                                            | V <sub>OH</sub>                   | -    | -   | 2.0  | V       |            |

| Output low voltage                                                                                                             | V <sub>OL</sub>                   | 1.0  | -   | -    | V       |            |

| Output dynamic resistance (at pins) <sup>c</sup>                                                                               | R <sub>OUT</sub>                  | 12   | -   | 50   | Ω       |            |

| Output current during Hi-Z (S0=1, S1=1)                                                                                        | I <sub>OZ</sub>                   | -    | -   | 50   | μА      |            |

| Output current during Clk Stop (StopB=0)                                                                                       | I <sub>OZ,STOP</sub>              | -    |     | 500  | μА      |            |

| Cycle-to-cycle duty cycle error at 400 MHz                                                                                     |                                   | -    | -   | 50   | pS      |            |

| Cycle-to-cycle duty cycle error at 300 MHz                                                                                     | t <sub>DC,ERR</sub>               | -    | -   | 70   | pS      |            |

| Cycle-to-cycle duty cycle error at 267 MHz                                                                                     |                                   | -    | -   | 80   | pS      |            |

| Output rise and fall times (measured at 20% - 80% of output voltage)                                                           | t <sub>CR</sub> , t <sub>CF</sub> | 160  | -   | 400  | pS      |            |

| Difference between rise and fall times on the same pin of a single device (20% - 80%)                                          | t <sub>CR</sub> , t <sub>CF</sub> | -    |     | 100  | pS      |            |

$=3.3V \pm 5\%$ , TA = 0% to +70%

Table 11: Device Characteristics

a. Output short term jitter spec is peak to peak. b.  $V_{COS} = V_{OH} - V_{OL}$

c.  $R_{OUT} = \Delta V_O/\Delta I_O$ . This is defined at the output pins, not at the measurement point.

## **AC Operating Conditions**

| Characteristic                                                                              | Symbol                           | Min  | Тур | Max              | Units                 |

|---------------------------------------------------------------------------------------------|----------------------------------|------|-----|------------------|-----------------------|

| Refclk Input Cycle Time                                                                     | t <sub>CYCLE,IN</sub>            | 10   | -   | 40               | nS                    |

| Faster speed bin for Refclk input cycle time <sup>a</sup>                                   |                                  | 6ª   | -   | 40               | nS                    |

| Input Cycle-to-cycle jitter <sup>b</sup>                                                    | t <sub>J,IN</sub>                | -    | -   | 250              | pS                    |

| Input Duty Cycle over 10,000 cycles                                                         | D <sub>CIN</sub> <sup>c</sup>    | 40%  | -   | 60%              | t <sub>CYCLE</sub>    |

| Input Frequency of Modulation                                                               | f <sub>MIN,IN</sub> <sup>C</sup> | 30   | -   | 33               | kHz                   |

| Modulation index for triangular modulation                                                  | P <sub>M,IN</sub> <sup>c</sup>   | -    | -   | 0.6              | %                     |

| Modulation index for non-triangular modulation                                              |                                  | -    | -   | 0.5 <sup>d</sup> | %                     |

| Phase Detector Input Cycle time at PclkM and SynclkN                                        | t <sub>CYCLE, PD</sub>           | 30   | -   | 100              | nS                    |

| Initial Phase Error at Phase Detector Inputs (required range of phase aligner)              | t <sub>ERR,INIT</sub>            | -0.5 | -   | 0.5              | t <sub>CYCLE,PD</sub> |

| Phase Detector Input Duty Cycle over 10,000 Cycles                                          | D <sub>CIN,PD</sub>              | 25%  | -   | 75%              | t <sub>CYCLE,PD</sub> |

| Input Slew Rate (measured at 20% - 80% of input voltage) for PclkM, SynclkN, and Refclk     | $t_{l,SR}$                       | 1    | -   | 4                | V/nS                  |

| Input Capacitance at PclkM, SynclkN, and Refclke                                            | $C_{IN,PD}$                      | -    | -   | 7                | pF                    |

| Input Capacitance Matching at PclkM and SynclkNe                                            | $\Delta C_{IN,PD}$               | -    | -   | 0.5              | pF                    |

| Input Capacitance at Scalable CMOS Pins (excluding PclkM, SynclkN, and Refclk) <sup>e</sup> | C <sub>IN,CMOS</sub>             | -    | -   | 10               | pF                    |

- a. Faster speed bin for future systems (not a requirement now), and applicable for V<sub>DDLR</sub>>1.7V only

- b. Refclk jitter measured at V<sub>DDI,R</sub>(nom)/2

- c. If input modulation is used; input modulation is allowed but not required.

- d. The amount of allowed spreading for any non-triangular modulation is determined by the induced downstream tracking skew, which cannot exceed the skew generated by the specified 0.6% triangular modulation. Typically, the amount of allowed non-triangular modulation is about 0.5%.

- e. Capacitance measured at Freq = 1 MHz, DC bias = 0.9V, and V<sub>AC</sub><100mV

Table 12: AC Operating Conditions

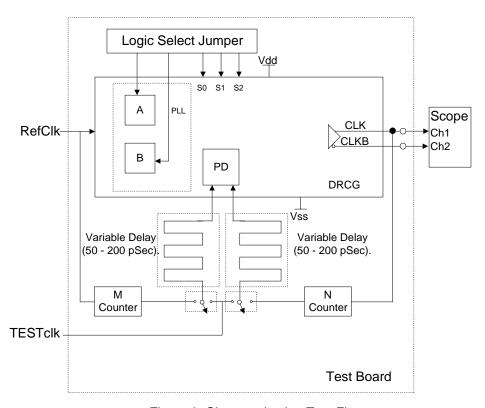

### **Test Circuit**

Figure 9: Characterization Test Fixture

# **Output Buffer Termination**

Figure 10: Output Termination

# Direct Rambus<sup>®</sup> III Clock Generator

## **Package Drawing and Dimensions**

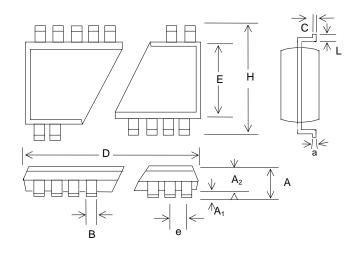

### 24 Pin QSOP Outline Dimensions

Document#: 38-07093 Rev. \*\*

|                |       | INCHES    |       | MILLIMETERS |       |       |

|----------------|-------|-----------|-------|-------------|-------|-------|

| SYMBOL         | MIN   | NOM       | MAX   | MIN         | NOM   | MAX   |

| Α              | 0.053 | 0.064     | 0.069 | 1.35        | 1.63  | 1.75  |

| A <sub>1</sub> | 0.004 | 0.006     | 0.010 | 0.102       | 0.152 | 0.254 |

| A2             | 0.055 | -         | 0.059 | 1.40        | -     | 1.50  |

| В              | 0.008 | -         | 0.012 | 0.203       | -     | 0.305 |

| С              | 0.007 | -         | 0.010 | 0.178       | -     | 0.254 |

| D              | 0.337 | 0.341     | 0.344 | 8.56        | 8.66  | 8.74  |

| Е              | 0.150 | 0.154     | 0.157 | 3.81        | 3.91  | 3.99  |

| е              |       | 0.025 BS0 |       | 0.635 BSC   |       |       |

| Н              | 0.228 | 0.235     | 0.244 | 5.79        | 5.97  | 6.20  |

| L              | 0.016 | 0.025     | 0.050 | 0.406       | 0.635 | 1.27  |

| а              | 00    | -         | 80    | 00          | -     | 80    |

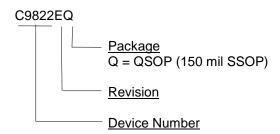

## **Ordering Information**

| Part Number | Package Type | Production Flow          |

|-------------|--------------|--------------------------|

| C9822EQ     | 24 PIN QSOP  | Commercial, 0°C to +70°C |

Note: The ordering part number is formed by a combination of device number, device revision, package style,

and screening as shown below.

Marking: Example: Date Code

C9822EQ Lot #

### **Notice**

Cypress Semiconductor Corporation reserves the right to make changes to its products in order to improve design, performance or reliability. Cypress Semiconductor Corporation assumes no responsibility for the use of its products in life supporting and medical applications where the failure or malfunction of the product could cause failure of the life supporting and medical systems. Products are not authorized for use in such applications unless a written approval is requested by the manufacturer and an approval is given in writing by Cypress Semiconductor Corporation for the use of its products in the life supporting and medical applications.

|      | Document Title: C9822 Direct Rambus® III Clock Generator Document Number: 38-07093 |               |                 |                             |  |  |

|------|------------------------------------------------------------------------------------|---------------|-----------------|-----------------------------|--|--|

| Rev. | ECN<br>No.                                                                         | Issue<br>Date | Orig. of Change |                             |  |  |

| **   | 107129                                                                             | 06/12/01      | IKA             | Convert from IMI to Cypress |  |  |