# bq4847/bq4847Y

# **RTC Module With CPU Supervisor**

#### **Features**

- ➤ Real-Time Clock counts seconds through years in BCD format

- ➤ Integrated battery and crystal

- ➤ On-chip battery-backup switchover circuit with nonvolatile control for an external SRAM

- ➤ 130mAh battery capacity

- ➤ ±1 minute per month clock accuracy

- ➤ Less than 500nA of clock operation current in backup mode

- ➤ Microprocessor reset valid to V<sub>CC</sub> = V<sub>SS</sub>

- Independent watchdog timer with a programmable time-out period

- ➤ Power-fail interrupt warning

- Programmable clock alarm interrupt active in battery-backup mode

- ➤ Programmable periodic interrupt

- ➤ Battery-low warning

### **General Description**

The bq4847 Real-Time Clock Module is a low-power microprocessor peripheral that integrates a time-of-day clock, a 100-year calendar, a CPU supervisor, a battery, and a crystal in a 28-pin DIP module. The part is ideal for fax machines, copiers, industrial control systems, point-of-sale terminals, data loggers, and computers.

The bq4847 contains an internal battery and crystal. Through the use of the conditional chip enable output  $(\overline{CE}_{OUT})$  and battery voltage output  $(V_{OUT})$  pins, the bq4847 can write-protect and make nonvolatile an external SRAM. The backup cell powers the real-time clock and maintains SRAM information in the absence of system voltage.

The bq4847 contains a temperature-compensated reference and comparator circuit that monitors the status of its voltage supply. When an out-of-tolerance condition is detected, the bq4847 generates an interrupt warning and subsequently a microprocessor reset. The reset stays active for 200ms after  $V_{CC}$  rises within

tolerance to allow for power supply and processor stabilization.

The bq4847 also has a built-in watchdog timer to monitor processor operation. If the microprocessor does not toggle the watchdog input (WDI) within the programmed time-out, the bq4847 asserts WDO and RST. WDI unconnected disables the watchdog timer.

The bq4847 can generate other interrupts based on a clock alarm condition or a periodic setting. The alarm interrupt can be set to occur from once per second to once per month. The alarm can be made active in the battery-backup mode to serve as a system wake-up call. For interrupts at a rate beyond once per second, the periodic interrupt can be programmed with periods of 30.5µs to 500ms

#### Caution:

Take care to avoid inadvertent discharge through  $V_{\text{OUT}}$  and  $\overrightarrow{\text{CE}}_{\text{OUT}}$  after battery isolation has been broken.

### **Pin Connections**

|                   |    |    | 1                 |  |  |

|-------------------|----|----|-------------------|--|--|

| Vout □            | 1  | 28 | □ vcc             |  |  |

| NC □              | 2  | 27 | □ WE              |  |  |

| NC 🗆              | 3  | 26 | □ CEIN            |  |  |

| WDO [             | 4  | 25 | □ CEOUT           |  |  |

| ĪNT □             | 5  | 24 | □ NC              |  |  |

| RST □             | 6  | 23 | □ WDI             |  |  |

| A3 🗆              | 7  | 22 | □ <del>OE</del>   |  |  |

| A2 🗆              | 8  | 21 | ⊐ <del>cs</del>   |  |  |

| A <sub>1</sub> □  | 9  | 20 | □ NC              |  |  |

| A0 🗆              | 10 | 19 | □ DQ <sub>7</sub> |  |  |

| DQ <sub>0</sub> □ | 11 | 18 | □ DQ <sub>6</sub> |  |  |

| DQ1 □             | 12 | 17 | □ DQ5             |  |  |

| DQ2 □             | 13 | 16 | □ DQ4             |  |  |

| Vss □             | 14 | 15 | □ DQ <sub>3</sub> |  |  |

|                   |    |    |                   |  |  |

| 28-Pin DIP Module |    |    |                   |  |  |

| PN484701.eps      |    |    |                   |  |  |

|                   |    |    |                   |  |  |

Sept. 1996

### **Pin Names**

| $A_0 - A_3$                        | Clock/Control address       | NC                      | No connect             |

|------------------------------------|-----------------------------|-------------------------|------------------------|

| in                                 | inputs                      | $V_{\mathrm{OUT}}$      | Back-up battery output |

| DQ <sub>0</sub> –DQ <sub>7</sub>   | Data inputs/outputs         | $\overline{\text{INT}}$ | Interrupt output       |

| $\overline{	ext{WE}}$              | Write enable                | $\overline{\text{RST}}$ | Microprocessor reset   |

| $\overline{\text{OE}}$             | Output enable               | WDI                     | Watchdog input         |

| CS                                 | Chip select input           | $\overline{	ext{WDO}}$  | Watchdog output        |

| $\overline{\text{CE}}_{\text{IN}}$ | External RAM chip enable    | $V_{CC}$                | +5V supply             |

| CE <sub>OUT</sub>                  | Conditional RAM chip enable | $V_{SS}$                | Ground                 |

# bq4847/bq4847Y

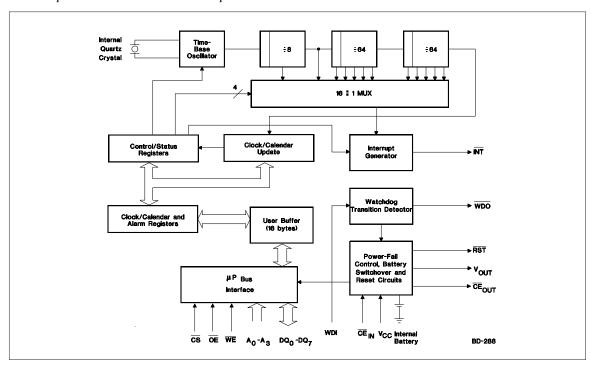

### **Functional Description**

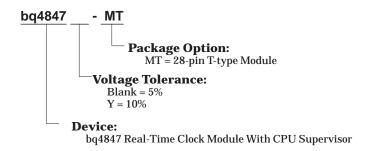

Figure 1 is a block diagram of the bq4847. The bq4847 is functionally equivalent to the bq4845 except that the battery (20, 24) and crystal (2, 3) pins are not accessible. The pins are connected internally to a coin cell and quartz crystal. The coin cell provides  $130 \underline{m} Ah$  of capacity. It is internally isolated from  $V_{OUT}$  and  $\overline{CE}_{OUT}$  until the initial application of  $V_{CC}$ . Once  $V_{CC}$  rises above  $V_{PFD}$ , this isolation is broken, and the backup cell provides power to  $V_{OUT}$  and  $\overline{CE}_{OUT}$  for the external SRAM. The real-time clock keeps time to within one minute per month at

room temperature. For a complete description of features, operating conditions, electrical characteristics, bus timing, and pin descriptions, see the bq4845 data sheet. Valid part types for ordering are bq4847MT (5%) and bq4847YMT (10%).

Figure 2 illustrates the address map for the bq4847. Table 1 is a map of the bq4847 registers, and Table 2 describes the register bits.

Figure 1. Block Diagram

### **Truth Table**

| Vcc                                         | CS                | OE           | WE       | CE <sub>OUT</sub>                  | Vout              | Mode     | DQ               | Power               |

|---------------------------------------------|-------------------|--------------|----------|------------------------------------|-------------------|----------|------------------|---------------------|

| < V <sub>CC</sub> (max.)                    | $V_{\mathrm{IH}}$ | X            | X        | $\overline{\text{CE}}_{\text{IN}}$ | V <sub>OUT1</sub> | Deselect | High Z           | Standby             |

|                                             | $V_{\rm IL}$      | X            | $V_{IL}$ | $\overline{\text{CE}}_{\text{IN}}$ | V <sub>OUT1</sub> | Write    | D <sub>IN</sub>  | Active              |

| > V <sub>CC</sub> (min.)                    | $V_{\rm IL}$      | $V_{\rm IL}$ | $V_{IH}$ | $\overline{\text{CE}}_{\text{IN}}$ | V <sub>OUT1</sub> | Read     | D <sub>OUT</sub> | Active              |

|                                             | $V_{\rm IL}$      | $V_{IH}$     | $V_{IH}$ | $\overline{\text{CE}}_{\text{IN}}$ | V <sub>OUT1</sub> | Read     | High Z           | Active              |

| < V <sub>PFD</sub> (min.) > V <sub>SO</sub> | X                 | X            | X        | Voh                                | V <sub>OUT1</sub> | Deselect | High Z           | CMOS standby        |

| ≤ V <sub>SO</sub>                           | X                 | X            | X        | V <sub>OHB</sub>                   | V <sub>OUT2</sub> | Deselect | High Z           | Battery-backup mode |

Sept. 1996

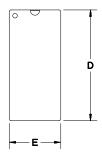

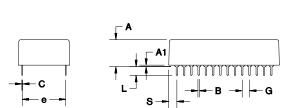

# MT: 28-Pin T-Type Module

## 28-Pin MT (T-Type Module)

|           | Inches |       | Millimeters |       |  |  |  |  |

|-----------|--------|-------|-------------|-------|--|--|--|--|

| Dimension | Min.   | Max.  | Min.        | Max.  |  |  |  |  |

| A         | 0.360  | 0.390 | 9.14        | 9.91  |  |  |  |  |

| A1        | 0.015  | -     | 0.38        | -     |  |  |  |  |

| В         | 0.015  | 0.022 | 0.38        | 0.56  |  |  |  |  |

| С         | 0.008  | 0.013 | 0.20        | 0.33  |  |  |  |  |

| D         | 1.520  | 1.535 | 38.61       | 38.99 |  |  |  |  |

| E         | 0.710  | 0.740 | 18.03       | 18.80 |  |  |  |  |

| e         | 0.590  | 0.620 | 14.99       | 15.75 |  |  |  |  |

| G         | 0.090  | 0.110 | 2.29        | 2.79  |  |  |  |  |

| L         | 0.110  | 0.130 | 2.79        | 3.30  |  |  |  |  |

| S         | 0.100  | 0.120 | 2.54        | 3.05  |  |  |  |  |

# **Ordering Information**

Sept. 1996

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated