# BtT9170

# Intelligent T1 Controller

## **Product Description**

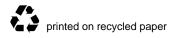

The BtT9170 Intelligent T1 Controller is a microprocessor (MPU) controlled device which implements a T1 interface between the multiplexed digital DS1 signal and the PCM highway of digital voice and data system equipment. The BtT9170 handles both D4 (SF) and D5 (ESF) standards with Facility Data Link (FDL) used in T1, ISDN primary-rate, and digital carrier systems.

Designers are provided a cost-effective solution for T1/ISDN primary-rate interface that integrates complex functions to minimize system development time, component count, board space, and cost. Combining dedicated control pins with MPU-addressable registers, maximum functional control is achieved with minimal MPU intervention. The BtT9170 provides direct control over the Bt8069-series line interface unit (LIU).

Use of a memory-mapped microprocessor bus interface minimizes the host MPU real-time requirement. Direct MPU access to T1 control and monitor functions in the BtT9170 register map allows software access without complicated serial message protocols.

## **BtT9170 Functional System Interface**

#### **Distinguishing Features**

- Intelligent Single-Device DS1 T-Carrier Transceiver (1.544 MHz)

- Compatible with ANSI Standard T1.403 Covering Facility Data Link Operations:

- Priority Codeword Handling

- Near-End and Far-End Performance Monitoring

- Extracted Link Data Handling

- Signalling Register Bank

- Independent Transmit and Receive Per-Channel Conditioning

- Automatic Conditioning of Receive Trunk and Signalling During CGA

- Unconditional Replacement of Transmit or Receive Trunk and Signalling

- Dedicated per-channel control register for each time slot

- 80x88-Compatible Parallel Microprocessor Bus Interface

- 8-Bit Address/Data Bus for Accessing Control and Status Information

- Separate Serial Interfaces for DS1 Transmit & Receive Data

- Microprocessor-Accessible Registers

- 16 Control and Monitor

- 14 Facility Data Link

- 24 Per-Channel Control

- 12 Received Signalling

- User-Maskable Interrupt Request Generated on Specified Alarm and Error Conditions

- Independent Transmit and Receive Functions, Each With a Separate Timebase

- Off-line Framer Flywheel Timebase Option

- Implements T1 Formats With and Without Signalling

- ESF: 24 Frames/Multiframe

- SF: 12 Frames/Multiframe

- N: 4 Frames/Multiframe

- continued

#### **Distinguishing Features** (continued)

- Zero-Suppression Modes

- Bit-7 Stuffing

- B8ZS Line Coding

- Transparent

- Meets CCITT G.733 (1.544 MHz) and Applicable Sections of G.703

- Compatible with AT&T Technical Advisories on ESF and Clear-Channel Operation With B8ZS

- Alarm Generation and Detection

- · Remote and Locally Controlled Payload Loopback

- Pin-For-Pin Compatible with BtP9170, Intelligent El Framer

- Direct Interface and Control of the Bt8069-series Line Interface Unit (LIU)

- Direct Interface to the Bt8071A 32-Channel HDLC Controller

- · Packages:

- 40-pin Plastic (DIP)

- 44-pin Plastic (PLCC) Package

- Operates From a Single +5 Vdc ±5% Power Supply

- CMOS/TTL-Compatible Inputs and Outputs

- Low-Power CMOS Technology

#### **Ordering Information**

| Model Number                                             | lodel Number Package Ambient                                         |                            |  |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------|----------------------------|--|--|--|--|

| BtT9170KP                                                | 40-pin Plastic DIP                                                   | 0° C to 70° C (Commercial) |  |  |  |  |

| BtT9170KPJ                                               | 44-pin Plastic Leaded Chip Carrier (PLCC) 0° C to 70° C (Commercial) |                            |  |  |  |  |

| Consult factory about extended temperature availability. |                                                                      |                            |  |  |  |  |

Copyright © 1993 Brooktree Corporation. All rights reserved.

Print date: January, 1997

Brooktree reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished by Brooktree Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Brooktree Corporation for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent or patent rights of Brooktree Corporation.

Brooktree products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Brooktree product can reasonably be expected to result in personal injury or death. Brooktree customers using or selling Brooktree products for use in such applications do so at their own risk and agree to fully indemnify Brooktree for any damages resulting from such improper use or sale.

Brooktree is a registered trademark of Brooktree Corporation. Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

Specifications are subject to change without notice.

PRINTED IN THE UNITED STATES OF AMERICA

# **Table of Contents**

| List of Figures  | v                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Tables . | vii                                                                                                                                                      |

| Product Descri   | <b>ption</b>                                                                                                                                             |

|                  | Microprocessor Interface                                                                                                                                 |

| Pin Infor        | mation                                                                                                                                                   |

| Functional Des   | scription 11                                                                                                                                             |

| Introduct        | ion                                                                                                                                                      |

|                  | Section.13Transmit Input Register13Transmit Frame/Multiframe Timing Generator14Transmit Multiplexer14Transmit Output Register16                          |

|                  | Section17Receive Input Register/B8ZS Decoder and Bipolar Violation Detector17Receive Extractor18Receive Multiplexer22Off-line Framer/RSYNC Multiplexer23 |

| •                | Data Link Section24Transmit FDL Data Flow25Receive FDL Data Flow26                                                                                       |

|                  | rface Unit (LIU) Control Section                                                                                                                         |

| Peripher         | al I/O Section                                                                                                                                           |

| Micropro         | cessor Interface                           | 29 |

|------------------|--------------------------------------------|----|

| ,                | Asynchronous MPU Reads                     | 30 |

| (                | Control and Monitor Register Array         | 31 |

| I                | Per-Channel Control Register Array         | 32 |

| I                | Received Signalling Registers              | 32 |

| F                | Performance Registers                      | 32 |

| Internal Registo | ers                                        | 33 |

| Monitor F        | Registers                                  | 37 |

| Γ                | Monitor Register 0 (MR0)                   | 37 |

| ſ                | Monitor Register 1 (MR1)                   | 38 |

| 1                | Monitor Register 2 (MR2)                   | 39 |

| Priority C       | odeword Registers                          | 40 |

| ſ                | Receive Priority Codeword Register (RPCR)  | 40 |

| -                | Transmit Priority Codeword Register (TPCR) | 41 |

| Control R        | egisters                                   | 41 |

| (                | Control Register 0 (CR0)                   | 41 |

| (                | Control Register 1 (CR1)                   | 42 |

| (                | Control Register 2 (CR2)                   | 43 |

| (                | Control Register 3 (CR3)                   | 44 |

|                  | Control Register 4 (CR4)                   |    |

|                  | Control Register 5 (CR5)                   |    |

|                  | Idle Register (IR)                         |    |

|                  | Default Signalling Register (DSR)          |    |

|                  | Registers                                  |    |

|                  | Alarm Enable Register (AER)                |    |

|                  | Interrupt Enable Register (IER)            |    |

| l                | Interrupt Cause Register (ICR)             | 50 |

|                  | nel Control Registers                      |    |

| ,                | Architecture Control                       | 51 |

|                  | Application Control                        |    |

|                  | Default Operations                         |    |

|                  | Transmit Data Flow Control                 |    |

|                  | Receive Data Flow Control                  |    |

|                  | Data Conditioning                          |    |

|                  | Signalling Conditioning or Force           |    |

|                  | Data Force                                 |    |

|                  | Receive Signalling Array Operations        |    |

|                  | Signalling Registers                       |    |

|                  | Receive Signalling Array A (RSA)           |    |

|                  | Receive Signalling Array B (RSB)           |    |

|                  | Receive Signalling Array C (RSC)           | 53 |

| L L              |                                            |    |

BtT9170 Table of Contents

| Near-End Monitor Registers                              | 54 |

|---------------------------------------------------------|----|

| Near-End Monitor Registers 1 and 2 (NEMR1 and NEMR2)    | 54 |

| Near-End Monitor Registers 3 and 4 (NEMR3 and NEMR4)    | 54 |

| Near-End Monitor Registers 5 and 6 (NEMR5 and NEMR6)    | 55 |

| Far-End Performance Registers                           | 55 |

| Far-End Performance Registers 1 and 2 (FEPR1 and FEPR2) | 55 |

| Far-End Performance Registers 3 and 4 (FEPR3 and FEPR4) | 56 |

| Far-End Performance Registers 5 and 6 (FEPR5 and FEPR6) |    |

| Far-End Performance Registers 7 and 8 (FEPR7 and FEPR8) | 56 |

| Switching Characteristics                               | 57 |

| Microprocessor Interface                                | 57 |

| Transmit Timing                                         | 60 |

| Receiver Timing                                         | 62 |

| Clock and Data Timing                                   | 65 |

| Reset Timing                                            |    |

| Reframe Time                                            |    |

| Extracted Link DataTiming–ESF Mode                      |    |

| Receive Link Data Timing–ESF Mode                       |    |

| Alarm-to-Interrupt Delay                                | 69 |

| RRED Interrupt—MPU Read and Clear                       | 69 |

| Transmit Priority Codeword Response Timing              | 70 |

| Absolute Maximum Ratings                                | 70 |

| Electrical Characteristics                              | 71 |

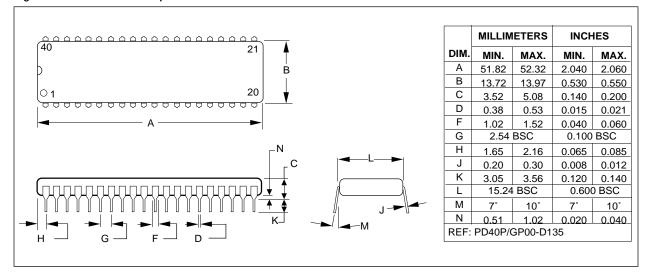

| Package Information                                     | 73 |

| Mechanical Drawings                                     | 73 |

| Revision History                                        | 74 |

| Appendix A                                              | 75 |

| TI Overview                                             | 75 |

| General                                                 | 75 |

| Signalling Data                                         | 75 |

| Alarms and Error Conditions                             | 76 |

| Clock Recovery                                          | 76 |

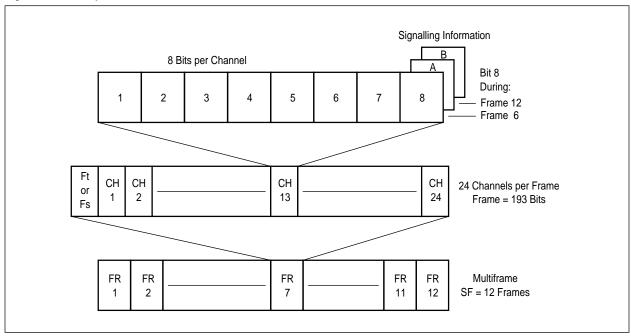

| Superframe Format (SF)                                  | 77 |

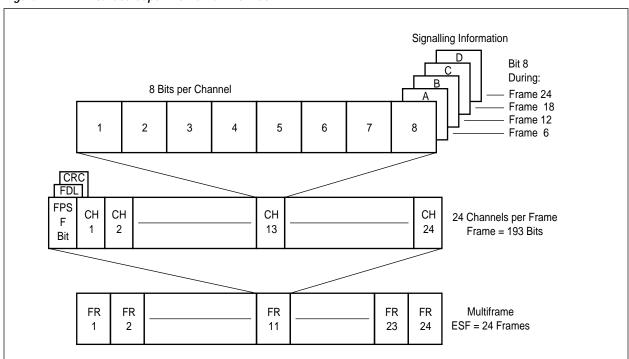

| Extended Superframe Format (ESF)                        | 79 |

| Nonsignalling Format (N)                                | 81 |

| Appendix B                                              | 83 |

| Facility Data Link (FDL)                                | 83 |

| Bit-Oriented Data (Priority Codeword)                   |    |

| Message-Oriented Data (Performance Reports)             |    |

List of Figures BtT9170

# **List of Figures**

| Figure 1.  | BtT9170 Functional Interface Signals        | . 1 |

|------------|---------------------------------------------|-----|

| Figure 2.  | BtT9170 Pin Assignments                     | . 3 |

| Figure 3.  | BtT9170 Detailed Block Diagram              | 12  |

| Figure 4.  | Transmit Section Functional Block Diagram   | 13  |

| Figure 5.  | Transmit Multiplexer Data Flow              | 14  |

| Figure 6.  | Receive Section Functional Block Diagram    | 17  |

| Figure 7.  | General Synchronization Flow Chart          | 19  |

| Figure 8.  | Performance Report Message Structure        | 21  |

| Figure 9.  | Receive Multiplexer Block Diagram           | 22  |

| Figure 10. | Transmit FDL Data Flow                      | 24  |

| Figure 11. | Receive FDL Data Flow                       | 25  |

| Figure 12. | Line Interface Unit Interface Signals       | 28  |

| Figure 13. | Peripheral I/O Port                         | 29  |

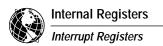

| Figure 14. | MPU Bus Interface Read Waveforms            | 58  |

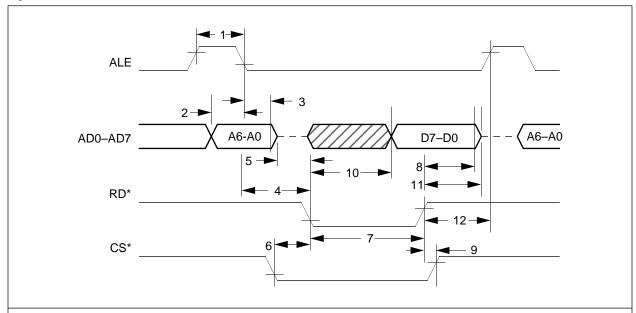

| Figure 15. | MPU Bus Interface Write Timing              | 59  |

| Figure 16. | Transmit Interface Timing–SF Mode           | 60  |

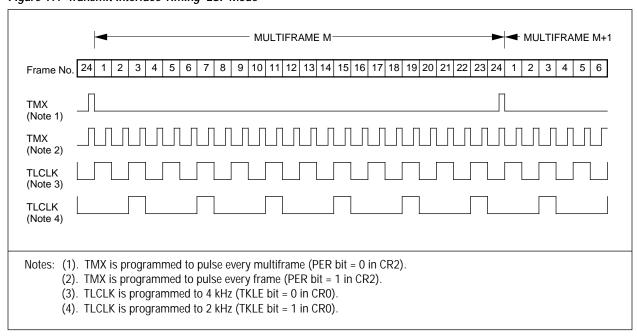

| Figure 17. | Transmit Interface Timing–ESF Mode          | 60  |

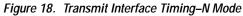

| Figure 18. | Transmit Interface Timing–N Mode            | 61  |

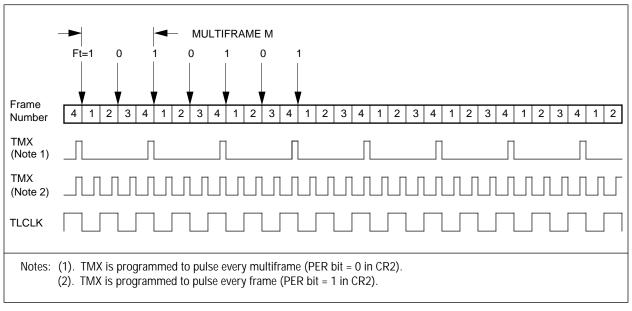

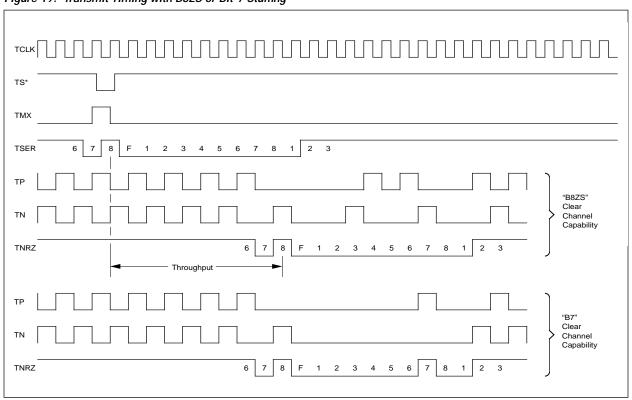

| Figure 19. | Transmit Timing with B8ZS or Bit-7 Stuffing | 61  |

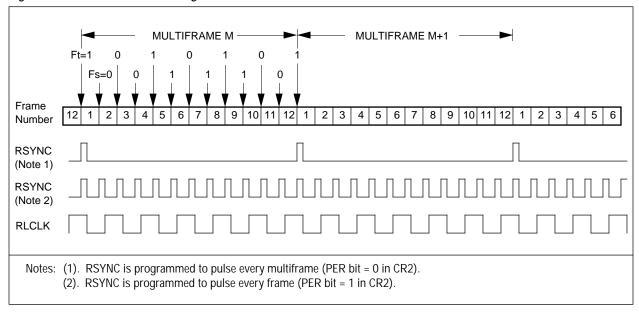

| Figure 20. | Receive Interface Timing–SF Mode            | 62  |

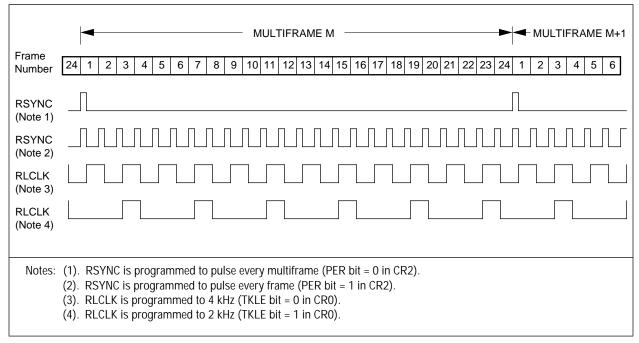

| Figure 21. | Receive Interface Timing–SF Mode            | 62  |

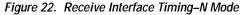

| Figure 22. | Receive Interface Timing–N Mode             | 63  |

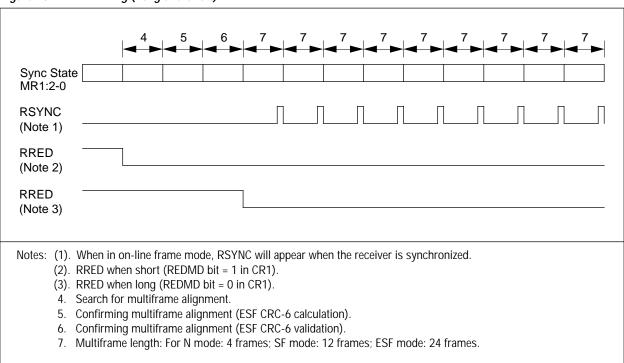

| Figure 23. | RRED Timing (Long and Short)                | 63  |

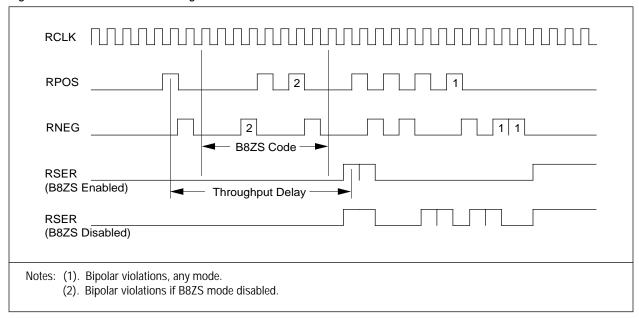

| Figure 24. | Receiver B8ZS Decoding                      | 64  |

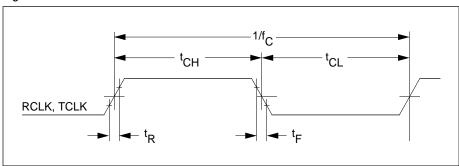

| Figure 25. | Minimum Clock Pulse Widths                  | 65  |

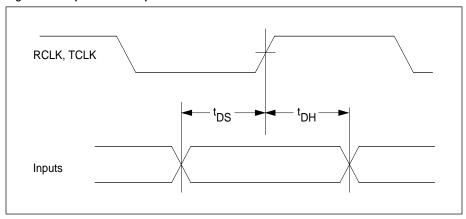

| Figure 26. | Input Data Setup and Hold Times             | 65  |

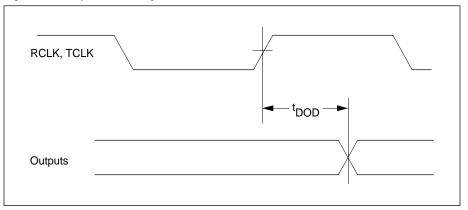

| Figure 27. | Output Data Delay Time                      | 66  |

| Figure 28. | Minimum Reset Time                          | 67  |

| Figure 29. | Extracted Link Data Timing–ESF Mode         | 68  |

| Figure 30. | Receive Link DataTiming-FSF Mode            | 68  |

vi Brooktree<sup>®</sup>

BtT9170 List of Figures

| Figure 31.  | Alarm-to-Interrupt Delay                       | 69 |

|-------------|------------------------------------------------|----|

| Figure 32.  | RRED Interrupt–MPU Read and Clear              | 69 |

| Figure 33.  | Transmit Priority Codeword Response Timing     | 70 |

| Figure 34.  | 44-Pin Plastic Lid Chip Carrier (PLCC) Package | 73 |

| Figure 35.  | 40-Pin Plastic Dip                             | 74 |

| Figure A-1. | TI Super Frame PCM Format                      | 77 |

| Figure A-2  | T1 Extended Super Frame PCM Format             | 79 |

List of Tables BtT9170

# **List of Tables**

| Table 1.   | BtT9170 Pin Assignments            | 4  |

|------------|------------------------------------|----|

| Table 2.   | BtT9170 Pin Definitions            | 6  |

| Table 3.   | RD-Only Register Updates           | 30 |

| Table 4.   | BtT9170 Internal Register Map      | 34 |

| Table 5.   | F-Bit Control Options              | 47 |

| Table 6a.  | PCCR Coding Structure Architecture | 48 |

| Table 6b.  | PCCR Coding Structure Application  | 49 |

| Table 7.   | MPU Bus Interface Read Timing      | 57 |

| Table 8.   | MPU Bus Interface Write Timing     | 58 |

| Table 9.   | Clock Timing                       |    |

| Table 10.  | Reframe Timing                     | 67 |

| Table 11.  | Absolute Maximum Ratings           | 70 |

| Table 12.  | Electrical Characteristics         |    |

| Table A-1. | F-Bit Assignment–SF Mode           | 78 |

| Table A-2. | F-Bit Assignment–ESF Mode          | 80 |

| Table A-3. | F-Bit Assignment–N Mode            | 81 |

viii Brooktree<sup>®</sup>

# **Product Description**

# Microprocessor Interface

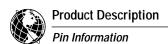

The BtT9170 provides the intelligent functions of T1 mode control, signalling control, error and alarm reporting, and handling of the facility data link through internal registers via the 8-bit parallel, memory-mapped MPU interface. The BtT9170 has 66 registers to provide intelligent interface control. The BtT9170 also provides a maskable interrupt-request output for handling of alarm and error conditions. The BtT9170 functional interface signals are shown in Figure 1.

INTR' LIU ELS1 PUP<sup>3</sup> Control 3 Control ELS3 ALE Bus MPU RD\* MODE & WR\* LOOP Bus Status Bt8069 CS\* ES0-BtT9170 Address/ Line AD0 Intelligent Data Bus Interface AD7 **RPOS** T1 Receive Unit **RNEG** Controller T1 Data (LIU) **RCLK** Clock **RSER** TP/TNRZ≺ Transmit **RSYNC** Receive T1 T1 Data TN/TMX **RRED TCLK** Serial Data Clock Processor Transmit **TSER** TLCLK Transmit TS\*/TMX Data Extracted **EXDATA** Clock Link Receive **RLCLK** Protocol **RLINK** Data Clock

Figure 1. BtT9170 Functional Interface Signals

# **Facility Data Link**

Control over the ESF Facility Data Link (FDL) is managed by the BtT9170, which adheres to ANSI standard T1.403-1989 and emerging standards for primary rate access. The FDL is user selectable as either a 4 kbps or 2 kbps channel. The BtT9170 supports priority codeword handling, automatic performance monitoring and reporting, and user-supplied link data handling. The ESF data link may be used for user-supplied extracted-link protocol transmission when it is not being used for yellow alarms, priority codewords, or performance messages; four pins are provided for this purpose.

#### Per-Channel Control

Twenty-four internal registers provide individual control of each T1 channel. Users can control trunk and signalling conditioning on a per-channel basis. Robbed bit signalling (2-, 4-, or 16-code "ABCD" signalling) or non-signalling can be implemented on a per-channel basis. Trunk conditioning substitutions may be made on a per-channel basis to include IDLE (both user-specified and standard IDLE codes), BUSY, VACANT, and digital milliwatt codes.

# Transceiver and Off-line Framer (Flywheel Timebase)

The BtT9170 has independent transmit and receive sections. The receiver incorporates a robust framing algorithm, which prevents false synchronization on patterns that mimic the framing bits in ESF mode. Transceiver functions also include zero suppression, alarm generation and detection, and loopback modes.

An off-line framer mode provides continuity of synchronized functions during frame searches. In this mode, the receiver output signals are derived from the offline framer, which also provides timing for receive trunk and signalling conditioning.

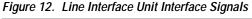

#### **Line Interface Unit Control**

The BtT9170 provides dedicated I/O pins that allow direct MPU software access to a Bt8069-series LIU. The BtT9170 T1 operating mode is selected by configuring the framing mode and the line code.

# Framing Modes

Superframe Format (SF) Mode

The SF mode implements the standard D4 PCM format at 1.544 Mbps with 12 frames per multiframe.

Extended Superframe

Format (ESF)

The ESF mode implements the standard D5 PCM format at 1.544 Mbps with 24 frames per multiframe. This mode is sometimes referred to as ESF, Fe, or D5.

The transmitter generates the framing pattern sequence (FPS), computes the cyclic redundancy check (CRC) checksum, and formats the facility data link (FDL) bits. The receiver recovers the FPS to establish framing, checks the CRC against the data, and provides a facility data link control (FDLC) report via the far-end monitor registers. "ABCD" robbed bit signalling is controlled via the perchannel control registers and stored in the received signalling registers.

Non-Signalling Superframe Format (N) Mode The N mode implements the standard D4 PCM format at 1.544 Mbps with four frames per multiframe, without signalling.

# Line Codes/Zero Suppression

To satisfy the ones-density requirement, either B8ZS line coding or bit-7 stuffing techniques can be selected. Zero suppression may be disabled to allow transparent operation.

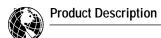

# Pin Information

The BtT9170 pin assignments are shown in Figure 2 and are listed in Table 1. The BtT9170 hardware interface signals are defined in Table 2.

Figure 2. BtT9170 Pin Assignments

Table 1. BtT9170 Pin Assignments (1 of 2)

| Pin No.<br>(40-Pin DIP) | Pin No.<br>(44-Pin PLCC) | Pin Label | I/O |

|-------------------------|--------------------------|-----------|-----|

| 1                       | 1                        | RD*       | I   |

| 2                       | 2                        | WR*       | I   |

| 3                       | 3                        | ALE       | I   |

| 4                       | 4                        | CS*       | I   |

| 5                       | 5                        | PUP*      | I   |

| 6                       | 6                        | TCLK      | I   |

| 7                       | 7                        | RCLK      | I   |

| 8                       | 8                        | ELS3      | 0   |

| 9                       | 9                        | ESL2      | 0   |

| 10                      | 10                       | ELS1      | 0   |

| -                       | 11                       | PI00*     | 1/0 |

| 11                      | 12                       | VCC       | PWR |

| 12                      | 13                       | VSS       | GND |

| _                       | 14                       | PIO1*     | 1/0 |

| 13                      | 15                       | ES1       | I   |

| 14                      | 16                       | ES0       | I   |

| 15                      | 17                       | RNEG      | I   |

| 16                      | 18                       | RPOS      | I   |

| 17                      | 19                       | TN/TMX    | 0   |

| 18                      | 20                       | TP/TNRZ   | 0   |

| 19                      | 21                       | MODE      | 0   |

| 20                      | 22                       | LOOP      | 0   |

| 21                      | 23                       | TS*/TMX   | I/O |

| 22                      | 24                       | TSER      | I   |

| 23                      | 25                       | TLCLK     | 0   |

| 24                      | 26                       | EXDATA    | I   |

| 25                      | 27                       | RLINK     | 0   |

| 26                      | 28                       | RLCLK     | 0   |

| 27                      | 29                       | RSER      | 0   |

| 28                      | 30                       | RSYNC     | 0   |

| 29                      | 31                       | RRED      | 0   |

|                         | 32                       | PIO2*     | 1/0 |

| 30                      | 33                       | VSS       | GND |

Table 1. BtT9170 Pin Assignments (2 of 2)

| Pin No.<br>(40-Pin DIP) | Pin No.<br>(44-Pin PLCC) | Pin Label | I/O |

|-------------------------|--------------------------|-----------|-----|

| 31                      | 34                       | VCC       | PWR |

| -                       | 35                       | PIO3*     | I/O |

| 32                      | 36                       | INTR*     | 0   |

| 33                      | 37                       | AD0       | I/O |

| 34                      | 38                       | AD1       | I/O |

| 35                      | 39                       | AD2       | I/O |

| 36                      | 40                       | AD3       | I/O |

| 37                      | 41                       | AD4       | I/O |

| 38                      | 42                       | AD5       | I/O |

| 39                      | 43                       | AD6       | I/O |

| 40                      | 44                       | AD7       | I/O |

Table 2. BtT9170 Pin Definitions (1 of 4)

|                               | Pin Label | Signal Names         | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|-----------|----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor Interface Pins | AD0-AD7   | Address/Data Bus     | I/O | Multiplexed address and data pins (AD0-AD7) are used to specify the address of the BtT9170 internal register accessed during an MPU read or write cycle, and to transfer data between the MPU and the BtT9170. The BtT9170 will service only register addresses 00H to 7FH; addresses outside this range are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

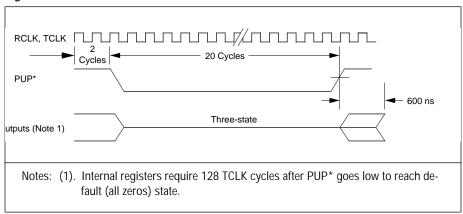

|                               | PUP*      | Power-Up             | 1   | This active low input asynchronously three-states all BtT9170 outputs. Outputs assume their normal impedance state within 600 ns after PUP* returns high.  PUP* is also sampled by the rising edge of TCLK and may be applied synchronously to initialize all BtT9170 internal registers. To properly initialize the registers, PUP* must be held high for at least 20 TCLK cycles before going low. Initialization is completed within 128 TCLK cycles after PUP* transitions from high to low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                               | RD*       | Read                 | I   | This active low control input is strobed low during the MPU read cycle. During the MPU read cycle, data from the addressed BtT9170 internal register is output to the MPU data lines. Read data outputs reflect the content of the addressed register after a given period of time has elapsed (Refer to tRLDV timing parameter #10a, Table 7). An additional 1/2 TCLK cycle must elapse (Refer to tRLDL timing parameter #10b, Table 7) before read data outputs become latched and are guaranteed not to change. MPU read cycles using long read strobes (RD* asserted for a period > tRLDL) can guarantee data bus setup/hold times.  Short MPU read strobes (RD* asserted for a period > tRLDV) cannot guarantee data bus setup/hold times, but can use faster read cycles without compromising system performance. Reference the software guidelines provided in the MPU interface section of this datasheet for an explanation of the necessary procedures. |

|                               | WR*       | Write                | I   | This active low control input is strobed low during the MPU write cycle. During the write cycle, data from the MPU data lines is written into the addressed BtT9170 internal register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                               | ALE       | Address Latch Enable | I   | This active high control input enables the BtT9170 to capture the address from the multiplexed address/data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                               | CS*       | Chip Select          | I   | This active low control input is low during MPU bus access to the BtT9170.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                               | INTR*     | Interrupt Request    | 0   | This open-drain output is used to interrupt the MPU when any one of the Interrupt Cause Register (ICR) bits and its respective Interrupt Enable Register (IER) bits are set. The open-drain output allows the interrupt request output line from several devices to connect to the common MPU interrupt request line. This output requires an external pull-up resistor to VCC (recommended pull-up resistance is 4.7K $\Omega$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 2. BtT9170 Pin Definitions (2 of 4)

|                                    | Pin Label | Signal Names             | I/O | Description                                                                                                                                                                                    |  |  |

|------------------------------------|-----------|--------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                    | ELS3-ELS1 | Equalization Line Select | 0   | Outputs that control the cable-length equalization for the attached Bt8069-series LIU. Line equalization is selected through register CR4.                                                     |  |  |

|                                    |           |                          |     | ELS3 ELS2 ELS1 Cable Length                                                                                                                                                                    |  |  |

|                                    |           |                          |     | 0 0 0 0–110 ft                                                                                                                                                                                 |  |  |

|                                    |           |                          |     | 0 0 1 110–220 ft                                                                                                                                                                               |  |  |

| S .                                |           |                          |     | 0 1 0 220–330 ft                                                                                                                                                                               |  |  |

| Pin                                |           |                          |     | 0 1 1 330–440 ft                                                                                                                                                                               |  |  |

| gce                                |           |                          |     | 1 0 0 440–550 ft                                                                                                                                                                               |  |  |

| Interfa                            |           |                          |     | 1 0 1 550–660 ft                                                                                                                                                                               |  |  |

| Line Interface Unit Interface Pins | ES1, ES0  | Error Status             | I   | Error status inputs from the Bt8069-series LIU.                                                                                                                                                |  |  |

| nterfa                             |           |                          |     | ES1 ES0 Indication                                                                                                                                                                             |  |  |

| l el                               |           |                          |     | 0 0 AIS detected                                                                                                                                                                               |  |  |

| =                                  |           |                          |     | 0 1 Elastic Buffer limit                                                                                                                                                                       |  |  |

|                                    |           |                          |     | 1 0 Loss of signal                                                                                                                                                                             |  |  |

|                                    |           |                          |     | 1 1 Normal Operation                                                                                                                                                                           |  |  |

|                                    | LOOP      | Loop Select              | 0   | Loop Select.                                                                                                                                                                                   |  |  |

|                                    | MODE      | Mode Select              | 0   | Loop and mode outputs determine the Bt8069-series LIU mode of operation. (Refer to the specific LIU datasheet for LOOP and MODE definitions.)                                                  |  |  |

|                                    | TLCLK     | Transmit Link Clock      | 0   | TLCLK is an output used to clock EXDATA. Either edge of TLCLK may be used to make EXDATA available to the BtT9170.                                                                             |  |  |

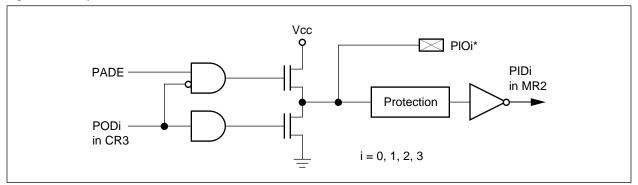

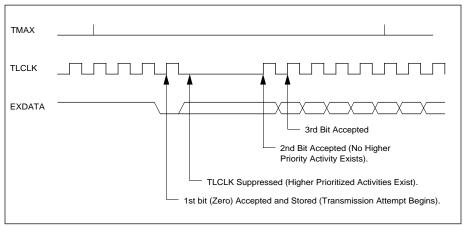

| ink Pins                           | EXDATA    | Extracted Link Data      | I   | The EXDATA input is a high-impedance pin that provides the extracted link protocol bit stream data. EXDATA is sampled on the rising edge of TCLK during TSER FDL or Fs bit while TLCLK is low. |  |  |

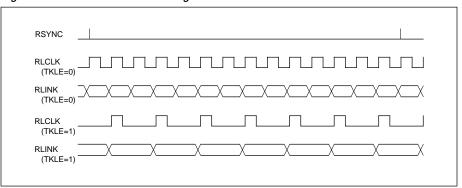

| Extracted Link Pins                | RLCLK     | Received Link Clock      | 0   | RLCLK is an output that systems may use to sample the RLINK bit stream. Either the rising or falling edge, or the high level of RLCLK may be used to store the RLINK data.                     |  |  |

|                                    | RLINK     | Received Link Data       | 0   | RLINK is an output that provides the link data. The data is stable one RCLK period before the rising edge of RLCLK and is centered around the falling edge of RLCLK.                           |  |  |

Table 2. BtT9170 Pin Definitions (3 of 4)

|                  | Pin Label | Signal Names                                       | I/O | Description                                                                                                                                                                                                                                                                                  |

|------------------|-----------|----------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | TCLK      | Transmit Clock                                     | I   | TCLK is the transmitter clock input and must be unconditionally present. TCLK must be in the range of 100 kHz–3.1 MHz and will normally be 1.544 MHz. All transmit inputs are sampled by the rising edge of TCLK, and all transmit output transitions are caused by the rising edge of TCLK. |

|                  | TSER      | Transmit Serial Data                               | I   | TSER is the serial input for the transmitted channel data and optionally the transmitted signalling data. Each bit is sampled on the rising edge of TCLK.                                                                                                                                    |

|                  | TN/TMX    | Transmit Negative/Trans-<br>mit Maximum            | 0   | A bimodal pin whose function is controlled by the ETRNZ bit in register CR5. After power-up or software reset, this pin defaults to "transmit negative."                                                                                                                                     |

| S                |           | Transmit Negative (TN)                             |     | The transmit output bit stream encoded for alternate mark inversion. The output sequences normally with a one on TP followed by a one on TN, followed by a one on TP, and so on. This sequence is deliberately broken when a B8ZS substitution takes place.                                  |

| tter Pin         |           | Transmit Maximum<br>(TMX)                          |     | This output pulses high for one bit time and is coincident with the sampling of the last serial bit of a multiframe.                                                                                                                                                                         |

| Transmitter Pins | TP/TNRZ   | Transmit Positive/Trans-<br>mit Non-Return to Zero | 0   | A bimodal output pin whose function is controlled by the ETRNZ bit in register CR5. After power-up or software reset, this pin defaults to "transmit positive."                                                                                                                              |

|                  |           | Transmit Positive (TP)                             |     | The transmit output bit stream encoded for alternate mark inversion. This output complements the Transmit Negative (TN) pin as described above.                                                                                                                                              |

|                  |           | Transmit Non-Return to<br>Zero (TNRZ)              |     | TNRZ is the unipolar output for transmitted data. TNRZ includes the results of bit-7 stuffing (if enabled) but does not include B8ZS encoding.                                                                                                                                               |

|                  | TS*/TMX   | Transmit Sync/Transmit<br>Maximum                  | I/O | A bidirectional pin whose function is controlled by the MASTER bit in register CR5. After power-up or software reset, this pin defaults to "transmit sync" input.                                                                                                                            |

|                  |           | Transmit Sync (TS*)                                |     | A low on this input synchronously resets the transmit timebase. Following the rising edge of transmit sync, the first bit of a multiframe will be sampled by the BtT9170.                                                                                                                    |

|                  |           | Transmit Maximum<br>(TMX)                          |     | This output pulses high for one bit time and is coincident with the sampling of the last serial bit of a multiframe.                                                                                                                                                                         |

Table 2. BtT9170 Pin Definitions (4 of 4)

|                       | Pin Label     | Signal Names                          | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----------------------|---------------|---------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Receiver Pins         | RCLK          | Receive Clock                         | I   | RCLK is the receive clock input and must be present for normal operation. RCLK must be in the range of 100 kHz–3.1 MHz awill normally be 1.544 MHz. All receive inputs are sampled by rising edge of RCLK, and all receive output transitions are cause by the rising edge of RCLK.                                                                                                                                                                                                                                      |  |

|                       | RPOS,<br>RNEG | Receive Positive,<br>Receive Negative | 1   | RPOS and RNEG are the (alternate unipolar) inputs for the received data recovered from the positive and negative AMI line pulses. RPOS and RNEG may be of either NRZ or RZ form. When receiving a single unipolar data stream, the data is connected to both RPOS and RNEG simultaneously.                                                                                                                                                                                                                               |  |

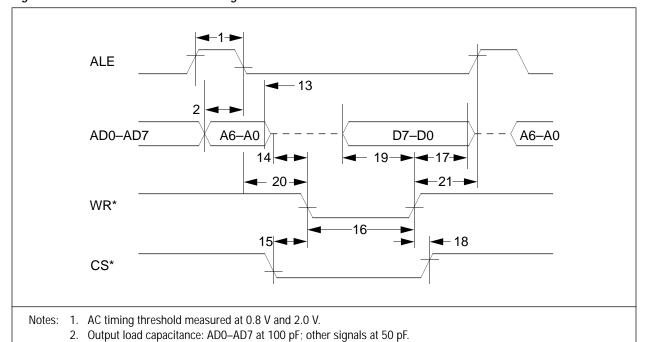

|                       | RSYNC         | Receive Synchronization               | 0   | The RSYNC output pin provides a synchronization signal whose nature depends on the receive master state, off-line framer selection (controlled by OLFRE bit in register CR1), and period mode selection (controlled by PER bit in register CR2). RSYNC will pulse at the first bit of each multiframe. From initialized condition, the first RSYNC pulse appears only after the receiver attains synchronization.                                                                                                        |  |

|                       | RSER          | Receive Serial Data                   | 0   | RSER is the output that represents the received serial data bit stream. This bit stream includes all received bit positions and any B8ZS corrections. The user can substitute RSER with other predefined data by programming the various internal registers.                                                                                                                                                                                                                                                             |  |

|                       | RRED          | Receive Red Alarm                     | 0   | The RRED output pin indicates the condition of the receive synchronizer. The function of this pin is controlled by the REDMD bit in register CR1. When REDMD is reset to a zero, the RRED output will be high when the BtT9170 is not multiframe aligned; RRED output will be low when the BtT9170 is both frame and multiframe aligned. If REDMD is set to a one, RRED will be high when the BtT9170 is not frame aligned and low if frame aligned. RRED transitions one bit time after the F-bit is available at RSER. |  |

| Power and Ground Pins | Vcc           | +5 Vdc Power                          | I   | +5 Vdc ±5% power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                       | Vss           | Ground                                | I   | Power and signal ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

# Introduction

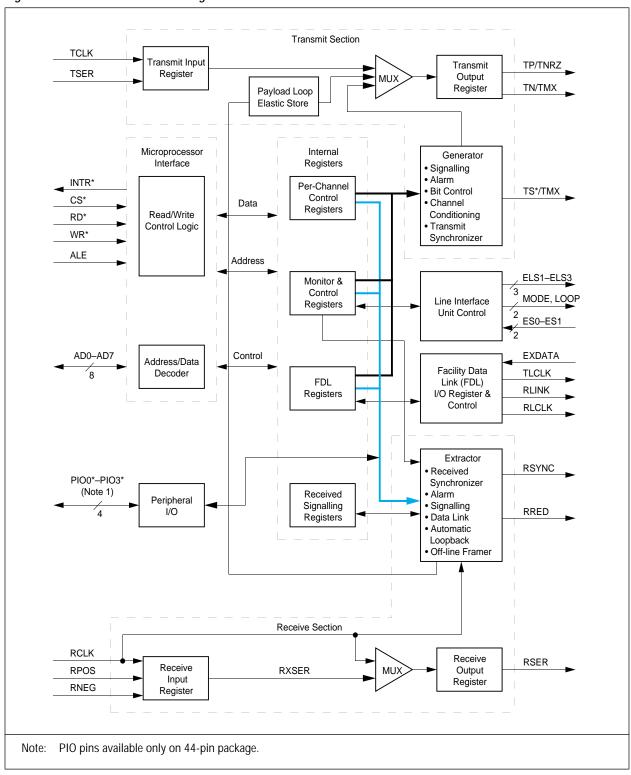

The BtT9170 consists of the following major sections:

- 1 Transmit Section

- 2 Receive Section

- 3 Facility Data Link Section

- 4 Line Interface Unit Control Section

- 5 Peripheral I/O Section

- 6 Microprocessor Interface Section

The major signal interfaces to these sections are shown in Figure 3.

Figure 3. BtT9170 Detailed Block Diagram

# Transmit Section

The BtT9170 transmit section provides the transmitter synchronization, frame/multiframe data formatting, transmit signalling, and yellow-alarm transmission functions. In addition, the transmit section also converts the transmitted data to paired alternate unipolar in support of AMI line codes. The transmit section is composed of the following subsections (Figure 4):

- 1 Transmit Input Register

- 2 Transmit Frame/Multiframe Timing Generator

- 3 Transmit Multiplexer

- 4 Transmit Output Register/Zero Suppressor

Figure 4. Transmit Section Functional Block Diagram

# Transmit Input Register

The serial T1 data to be transmitted enters the BtT9170 at the TSER input pin. Data is clocked into the transmit input register on the rising edge of the transmit clock (TCLK). TCLK has the nominal frequency of 1.544 MHz and is provided by the system. The unconditioned and unformatted (raw) data is sent to both the transmit multiplexer and the transmit frame/multiframe timing generator.

# Transmit Frame/Multiframe Timing Generator

The transmit frame/multiframe timing generator provides both data pattern and timing for frame and multiframe alignment, CRC-6 bits, signalling, facility data link, and yellow alarm. These bits are sent to the transmit multiplexer, where they are added to the raw data stream to format the raw data into the appropriate T1 format according to the selected mode of operation.

Frame and multiframe counters in the transmit frame/multiframe timing generator generate the timing and framing bits. The required F-bit (Fs, Ft, or FPS) can be generated internally or be supplied externally via TSER and EXDATA. The frame and multiframe counter may be reset to the first bit of the multiframe when the Transmit Synchronize (TS\*) input is pulsed low.

This section also generates the Transmit Max (TMX) output, which pulses high for one bit time during the last serial bit of a multiframe, based on the time-base set by the TS\* input, or the arbitrary timebase set after power-up.

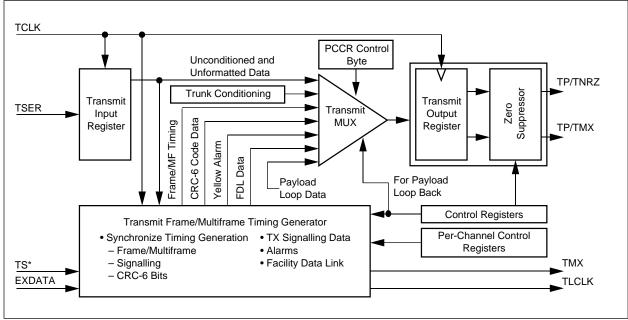

# **Transmit Multiplexer**

The transmit multiplexer inserts the appropriate F-bit into the transmit data stream. If "payload loop-back" is active, the raw received data replaces the raw transmit data and becomes the transmit output. The output goes to the transmit output register/zero suppressor and is subsequently transmitted to the LIU in the form of a paired unipolar signal, ready for conversion to a true AMI signal.

The transmit multiplexer consists of five submultiplexers (see Figure 5):

- 1 Trunk Conditioning Multiplexer

- 2 FORCE Conditioning Multiplexer

- 3 Signalling Multiplexer

- 4 Payload Control Multiplexer

- 5 Timing Control Multiplexer

Figure 5. Transmit Multiplexer Data Flow

#### Trunk Conditioning Multiplexer

The first multiplexer encountered by the unconditioned raw transmit serial T1 data is the trunk conditioning multiplexer. The trunk conditioning multiplexer allows the replacement of the unconditioned raw T1 data stream in any given channel on a per-channel basis. The type of channel conditioning is determined by the control byte in the specific channel's per-channel control register (PCCR). Trunk conditioning allows the replacement of channel data with either BUSY code (0111 1111), VACANT code (1111 1111), custom IDLE code as specified in Idle Register (IR), DDS IDLE code (1111 1110), or DDS DATA mode (XXXX XXX1; where X indicates that the channel data remains unchanged). The specific channel's PCCR can also be set up to bypass the channel conditioning and allow the channel data to pass without trunk conditioning.

## FORCE Conditioning Multiplexer

The FORCE conditioning multiplexer expands the available trunk-conditioning options. The type of FORCE conditioning is determined by the control byte in the specific channel's PCCR. FORCE conditioning allows the replacement of channel data with either MOOF (Mux-Out-Of-Frame), BUSY (0111111S), or VACANT (1111111) codes. The PCCR control byte structure prevents the enabling of both the TRUNK and FORCE conditioning multiplexers.

#### Signalling Multiplexer

The transmit serial T1 data stream then enters the signalling multiplexer. The signalling multiplexer allows the BtT9170 to implement robbed-bit signalling in any given channel on a per-channel basis. Robbed-bit signalling substitution is enabled by the PQX bit combinations in the individual channel's PCCR. The type of robbed-bit signalling selected for any given channel is determined by control code bits E, D, C, B, A in the specific channel's PCCR.

In SF mode, control code bits E, D, C, B, A can select either no signalling, 2-code signalling (substituting the least significant bit (LSB) of the specific channel in frame 6 and 12 with the content of the A-bit of the PCCR), or 4-code signalling (substituting the LSB of channel data in frames 6 with the A-bit and the LSB of channel data in frame 12 with the B-bit of the specific channel's PCCR). If 16-code signalling is selected, the BtT9170 uses only the A-bit and the B-bit information in the SF mode.

In ESF mode, control code bits E, D, C, B, A can select no signalling, 2-code signalling (substituting the LSB of the channel data in frames 6, 12, 18, and 24 with the content of the A-bit of the PCCR), 4-code signalling (substituting the LSB of the channel data in frames 6 and 18 with the content of A-bit of the PCCR while the LSB of the channel data in frames 12 and 24 are substituted with the content of B-bit of the PCCR), or 16-code signalling (which allows the LSB of the channel data in frames 6, 12, 18, and 24 to be substituted with the contents of A-, B-, C-, and D-bits of the PCCR, respectively).

In N mode, no robbed-bit signalling is selected, and the transmit serial data stream remains unchanged.

## Payload Control Multiplexer

The payload loopback feature allows the BtT9170 to internally loopback the unconditioned received raw data. When loopback is selected (PLOOP = 1 in CR5), the received serial data (excluding the framing bits) becomes the transmit serial data. When loopback is not selected, the serial T1 data stream output from the signalling multiplexer is passed directly to the timing control multiplexer.

In ESF mode, when payload loop automatic is selected (PLAUTO = 1 in CR5), the loopback can be controlled from the far-end via the priority codeword in the facility data link.

#### Timing Control Multiplexer

The timing control multiplexer injects the appropriate framing bits into the serial T1 data stream for the selected operating mode. The data is then sent to the transmit output register/zero suppressor.

In SF mode, the timing control multiplexer inserts Ft and Fs bits into the serial T1 data stream.

In ESF mode, the timing control multiplexer takes data generated by the transmit frame/multiframe generator and inserts the FPS, CRC-6, and FDL bits.

In N mode, the timing control multiplexer inserts only the Ft bit pattern into the serial T1 data stream. The Fs bit may be in the TSER input data stream or in the EXDATA input.

The BtT9170 also allows the user to bypass the internally generated F-bit, FDL, and CRC-6 bit patterns. Bypassing the internally generated timing bits requires that the data stream entering the TSER input contain all the bypassed bits. Setting FBYPAS = 1 in CR5 allows F-bits to be provided via the TSER input. Bypassing the internally generated FDL bits requires setting LBYPAS = 1 in CR5, while setting CBYPAS = 1 in CR5 allows bypass of the internally generated CRC bits.

The timing control multiplexer also controls the transmission of an alarm indication signal (AIS). When SAIS = 1 in CR4, AIS is transmitted, which forces the timing control multiplexer to transmit unframed all-ones data.

# **Transmit Output Register**

The output of the transmit multiplexer, with the appropriate bits inserted into the original unconditioned data stream, is clocked out of the transmit section on the rising edge of TCLK. The data is output to the TP/TNRZ and TN/TMX dual-function pins. The ETNRZ bit in CR5 selects the function of pins. When ETNRZ = 0, the pins function as alternate mark inverted (AMI) output data on TP and TN. When ETNRZ = 1, the pins function as TNRZ and TMX outputs.

When AMI output is selected, the transmit output register clocks the data in and converts it to the equivalent alternate unipolar-pair output on TP and TN. These outputs are then subjected to zero-suppression encoding as selected by the LCM1 and LCM0 bits in CR0. The BtT9170 encodes data with B8ZS line codes or Bit-7 stuffing, or performs no encoding (transparent mode). After power-up or software reset, the BtT9170 defaults to B8ZS.

In TNRZ output mode, bit-7 stuffing is the only zero-suppression coding available.

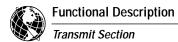

# Receive Section

The BtT9170 receive section provides the synchronization, signalling, and alarm indication functions. The receiver is composed of the following subsections (see Figure 6):

- 1 Receive Input Register/B8ZS Decoder and Bipolar Violation Detector

- 2 Receive Extractor

- 3 Receive Multiplexer

- 4 Receive Output Register

- 5 Off-line Framer

Figure 6. Receive Section Functional Block Diagram

# Receive Input Register/B8ZS Decoder and Bipolar Violation Detector

T1 data from the LIU enters the BtT9170 on the RPOS and RNEG pins. This paired unipolar received data is clocked into the receive input register by the rising edge of RCLK and is sent to the receive multiplexer and the receive extractor. Incoming data is first decoded for B8ZS code (if enabled). There is no algorithm to decode Bit-7 stuffing. The data is then checked for bipolar violations. Bipolar violations are counted and reported to the MPU via the near-end monitor registers.

#### **Receive Extractor**

The receive extractor extracts specific information from the bit stream of the receiver input register. The extracted information is placed into the appropriate internal registers for the MPU to access. Receiver timing synchronization from the incoming data is also extracted. Receiver synchronization is handled by a multi-stage process which singles out the correct synchronization lock point. Other information extracted is not valid unless the receiver has achieved valid synchronization.

Upon achieving valid synchronization, other extracted information is valid for the MPU to use. This information includes received signalling, FDL, and remote alarms. Received signalling is stored into the received signalling registers (RSR1–RSR15). FDL information is placed in the appropriate registers (FEPR1–FEPR8 and RPCR) and routed to the RLINK output. Alarm conditions are reported to the MPU via the monitor registers (MR0–MR2), and error counts are stored in the appropriate near-end monitor registers (NEMR1–NEMR6).

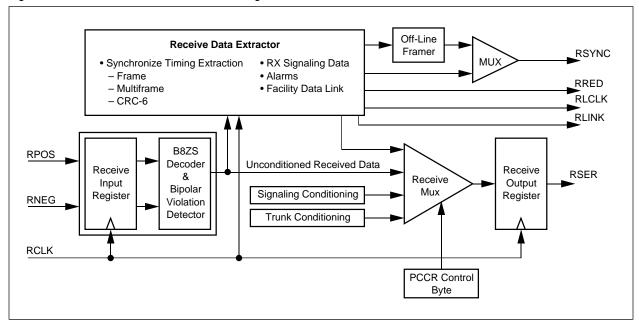

# Receiver Synchronization

After power-up (PUP\*), software reset (RESET = 1 in CR2), or a receiver frame-synchronization restart (RFSR = 1 in CR2), or when a framing-error condition is detected, the receiver begins to search for candidates for frame and multiframe alignment. In ESF mode, the receiver does not achieve full synchronization until the data has gone through a qualifying period. In the qualifying period, CRC-6 block checks are used to ensure that the chosen synchronizing candidate is valid. This qualifying period ensures that the BtT9170 achieves correct frame alignment and synchronization even in the presence of data patterns that mimic the framing patterns. (Intentional framing mimics may prevent frame synchronization.) The general synchronization flow is illustrated in Figure 7.

When synchronization is achieved, the receiver monitors alignment signals for errors. A red alarm is generated if frame alignment is lost. The criteria for loss of frame alignment in all modes is two out of five errors in the Ft or FPS bit pattern.

The receiver can be forced to restart a synchronization search (RFSR = 1 in CR2) or to prevent a resynchronization search when synchronization has been achieved (SL = 1 in CR1).

With framed random data inputs, synchronization is achieved within 10 ms of the initialization of a framing search.

Figure 7. General Synchronization Flow Chart

#### **Signalling Extraction**

When synchronization is achieved, signalling bits (also known as robbed-bit signalling) can be extracted from the incoming data. Signalling bits are then stored into the appropriate internal registers (RSR1–RSR15). If frame alignment is subsequently lost, the receiver stops updating the received signalling registers.

In the SF mode, the A- and B-bit signalling is available to the MPU by way of the received signalling subarray A (registers RSR1–RSR3) and subarray B (registers RSR5–RSR7), respectively. Whenever two-code signalling is selected, the signalling data contained in signalling channels A and B are both placed in subarray A. An interrupt request may also be generated at the end of a multiframe in which a change of signalling data has occurred.

In the ESF mode, the A-, B-, C-, and D-bit signalling is available to the MPU by way of the received signalling subarray A (registers RSR1–RSR3), subarray B (registers RSR5–RSR7), subarray C (registers RSR9–RSR11), and subarray D (registers RSR13–RSR15), respectively. Whenever 16-code signalling is selected, the data from each signalling channel is placed into its respective subarray. Whenever four-code signalling is selected, the A signalling data contained in signalling channels A and C is placed in subarray A; and the signalling data contained in signalling, the signalling data contained in signalling channels A, B, C, and D is placed in subarray A. An interrupt request may be generated at the end of a multiframe in which a change of signalling data has occurred. In the N mode, no robbed-bit signalling is used.

#### Facility Data Link Extractor

The facility data link extractor function is available only in the ESF mode, in which the F-bit structure is shared between the framing, CRC-6, and the facility data link. The received FDL information is made available to the MPU via the receive priority codeword register (RPCR) or, in the form of an error report, through the far-end performance message registers (FEPR1–FEPR8). In addition, FDL data is extracted and output in serial form on the RLINK pin where it can be sampled at the falling edge of RLCLK. The FDL can be selected to operate at 4 kbps or 2 kbps.

FEPR1–FEPR8 are updated whenever a complete and valid report is received. If the FDL is not carrying higher priority messages, such as yellow alarm or priority codewords, a complete report is expected every second. Figure 8 illustrates the performance report message structure specified by ANSI standard T1.403-1989.

Figure 8. Performance Report Message Structure

| Octet No.                                                                                                                              | LSB                          |     |    |    |    |    |    | MSB |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|----|----|----|----|----|-----|

| 1                                                                                                                                      | FLAG                         |     |    |    |    |    |    |     |

| 2                                                                                                                                      |                              | C/R | EA |    |    |    |    |     |

| 3                                                                                                                                      | TEI                          |     |    |    |    |    |    |     |

| 4                                                                                                                                      | CONTROL                      |     |    |    |    |    |    |     |

| 5                                                                                                                                      | G3                           | LV  | G4 | U1 | U2 | G5 | SL | G6  |

| 6                                                                                                                                      | FE                           | SE  | LB | G1 | R  | G2 | Nm | NI  |

| 7                                                                                                                                      | G3                           | LV  | G4 | U1 | U2 | G5 | SL | G6  |

| 8                                                                                                                                      | FE                           | SE  | LB | G1 | R  | G2 | Nm | NI  |

| 9                                                                                                                                      | G3                           | LV  | G4 | U1 | U2 | G5 | SL | G6  |

| 10                                                                                                                                     | FE                           | SE  | LB | G1 | R  | G2 | Nm | NI  |

| 11                                                                                                                                     | G3                           | LV  | G4 | U1 | U2 | G5 | SL | G6  |

| 12                                                                                                                                     | FE                           | SE  | LB | G1 | R  | G2 | Nm | NI  |

| 13                                                                                                                                     | FCS (Most Significant Byte)  |     |    |    |    |    |    |     |

| 14                                                                                                                                     | FCS (Least Significant Byte) |     |    |    |    |    |    |     |

| Notes: 1. The 1-second report consists of octets 5–12. 2. R, U1, and U2 are reserved for future standardization and should be set to 0 |                              |     |    |    |    |    |    |     |

R, U1, and U2 are reserved for future standardization and should be set to C (see Control Register CR3).

## Alarm Condition Extractor

The alarm condition extractor examines the incoming T1 data for alarm conditions. When an alarm condition is detected, corresponding bits are set in the monitor registers (MR0–MR2). The possible alarms are:

| Alarm  | Framing<br>Mode | Description                                                                         |  |  |  |

|--------|-----------------|-------------------------------------------------------------------------------------|--|--|--|

| RRED   | All             | Red alarm loss of frame alignment                                                   |  |  |  |

| RYEL   | All             | Yellow alarm (transmitted by the far end)                                           |  |  |  |

| AISDET | All             | All-ones condition detected                                                         |  |  |  |

| FERR   | All             | Framing error(s)                                                                    |  |  |  |

| ALTF   | N, SF           | 1 of 5 Ft alternation error detected (possibly caused by two frame controlled slip) |  |  |  |

| LOST   | All             | Lost carrier                                                                        |  |  |  |

| BPVS   | All             | Bipolar violation(s)                                                                |  |  |  |

| COFA   | All             | Change of frame alignment                                                           |  |  |  |

| CRCS   | ESF             | CRC-6 block error(s)                                                                |  |  |  |

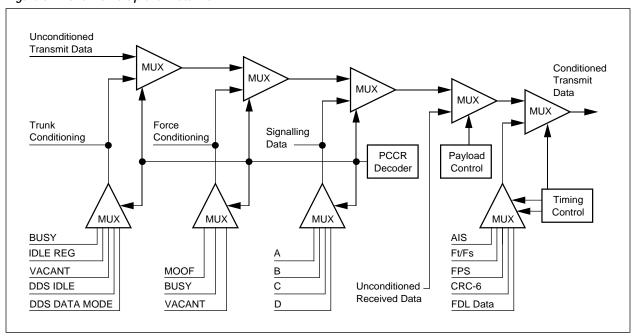

# **Receive Multiplexer**

Internally generated data can be substituted for the actual received data. The data substitution on individual channels is controlled by the MPU through the perchannel control registers (PCCR1–PCCR24), which allow the received data to be replaced on a channel-by-channel basis. The actual substitution of received data is accomplished by the receive multiplexer as controlled by red alarm and control registers.

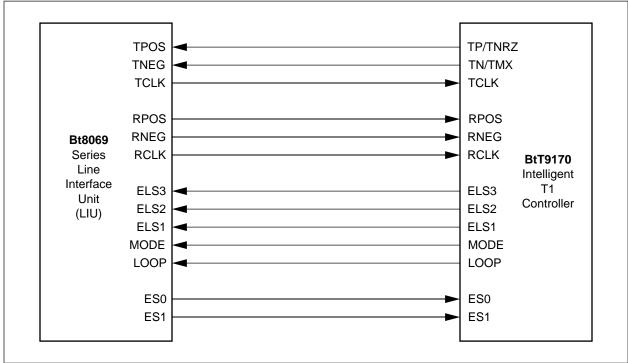

The data entering the receive multiplexer arrives from the receive input register/B8ZS decoder as an unconditioned serial data stream (see Figure 9). The data goes through three levels of multiplexers prior to being sent to the receive output register. The three multiplexers perform receive trunk conditioning, receive FORCE conditioning, receive signaling conditioning, and receive output register.

Receive Unconditioned Data Receive Conditioned MUX Receive Data MUX Receive Trunk MUX Receive Conditioning **FORCE** Signalling Conditioning Conditioning **PCCR PCCR PCCR** Decoder Decoder Decoder MUX **IDLE DDS IDLE** D16 1s IDLE D4 IR 1s D2 **MOOF** IR A. B VACANT **MILLIWATT** 1s VACANT

Figure 9. Receive Multiplexer Block Diagram

#### Receive Trunk Conditioning

The unconditioned received data is substituted with trunk conditioning on an individual channel basis. The per-channel trunk conditioning is established by the PQX bit combination in the selected channel's PCCR register and enabled by either the TCE bit (when RRED is active) or the CGA bit in CR2. Trunk conditioning options are:

- 1 **No-Trunk Conditioning**. The received data is passed through without trunk conditioning substitution.

- 2 **Standard Idle-Code Conditioning**. The chosen channel data is replaced with the standard idle code (0111 1111).

- 3 **All-Ones Conditioning**. The chosen channel data is replaced with all ones (1111 1111).

- 4 **MOOF Code Conditioning**. The chosen channel data is replaced with the MUX Out-Of-Frame (MOOF) code (0101 1000).

- 5 **Custom Idle-Code Conditioning.** The chosen channel data is replaced with the user's custom Idle code previously written from the MPU to the Idle Register (IR).

## Receive FORCE Conditioning

Data from the receive trunk conditioning multiplexer can be replaced with digital milliwatt, DDS IDLE, and other codes. The substitution is enabled by the PQX bit combination set in the selected channel's PCCR, and is independent of the CGA and TCE bits in CR2. The PCCR control byte structure prevents enabling both the receive TRUNK and receive FORCE conditioning multiplexers.

# Receive Signalling Conditioning

Replacement of the data from the Receive FORCE conditioning multiplexer with receive signalling conditioning is enabled by the PQX bit combination in the specific channel's PCCR if the CGA bit in CR2 is also set. Signalling conditioning options are:

- 1 **No-Signalling Conditioning**. The received data is passed through transparently (without replacement).

- 2 Signalling Conditioning. The actual signalling bits in the data stream are replaced with signalling bits from the default signalling register (DSR) or from the A-bit and B-bit in the selected channel's PCCR.

- 3 **All-Ones Conditioning**. The chosen channel's signalling bit(s) are replaced with ones.

#### **Receive Output Register**

The conditioned output data from the receive multiplexer is fed directly to the receive output register. The data is then clocked out as serial data on the RSER pin by the rising edge of RCLK. This serial data is the recovered data after B8ZS decoding (if enabled) and all appropriate conditioning of data and signalling.

# Off-line Framer/RSYNC Multiplexer

The off-line framer can generate the RSYNC timing signal when the on-line framer loses synchronization. The off-line framer is a flywheel timebase, initially synchronized by the on-line framer RSYNC output. If the off-line framer is enabled (OLFRE bit = 1 in CR1), the RSYNC output is driven from the off-line framer. If the off-line framer is not enabled (OLFRE bit = 0), the RSYNC output is driven by the RSYNC signal derived from on-line framer timing.

The off-line framer also supplies the timebase (for bit, frame, and multiframe timing) for insertion of trunk and signalling conditioning into the receive bit stream (RSER). This occurs whether the off-line framer is enabled or disabled.

The RSYNC output can be selected to pulse at every frame boundary (PER bit = 1 in CR2) or at every multiframe boundary (PER bit = 0).

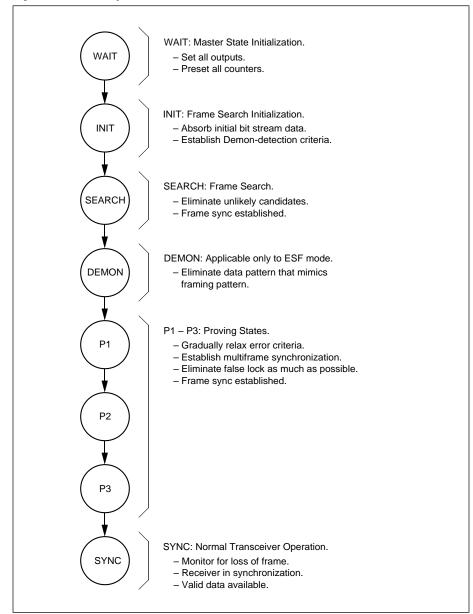

# Facility Data Link Section

The facility data link is generated and decoded by the facility data link section. FDL information is available only in the ESF mode. It is generally grouped into either bit-oriented or message-oriented data. Bit-oriented data carries a higher priority than message-oriented data and always preempts message-oriented data transmission. The transmit FDL data flow is illustrated in Figure 10 and the receive FDL data flow is illustrated in Figure 11.

The incoming facility data link is extracted from the incoming bit stream and is placed into the internal registers. The FDL is also output on RLINK and can be sampled by the system.

Outgoing FDL data can be entered either through the EXDATA input, TSER, or the FDL data can be generated internally. When the internal FDL message-oriented transmission is bypassed (LBYPAS bit = 1 in CR5), the FDL bits are supplied by the TSER input. If the internal FDL generator is selected (LBYPAS bit = 0 in CR5), the BtT9170 provides the message-oriented information and the bit-oriented information to the FDL multiplexer. Flags, EXDATA, and performance reports are lost when LBYPAS = 1; the link bypass function does not override yellow alarm or other bit-oriented functions.

Figure 10. Transmit FDL Data Flow

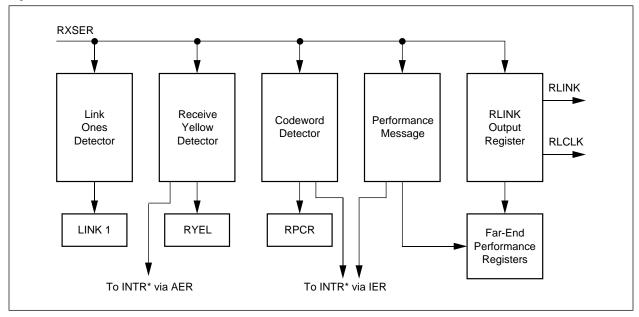

Figure 11. Receive FDL Data Flow

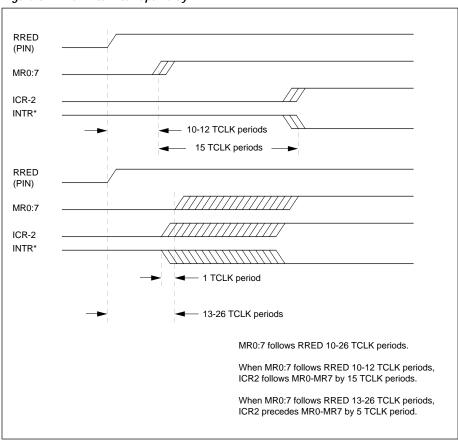

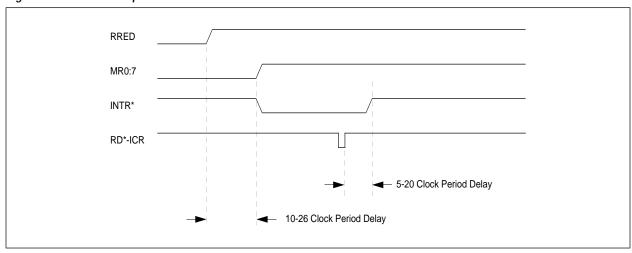

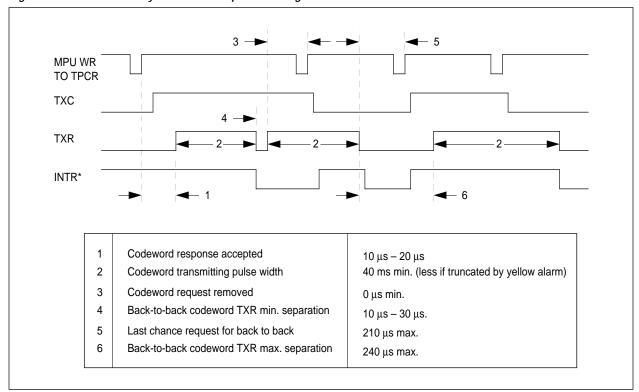

#### Transmit FDL Data Flow