## Advance

This document contains information on a product under development.

Information is not warranted and is subject to change.

# Bt2166

## High-Performance PCI/AGP 3D Video/Graphics Controller

### Applications

- Microsoft Windows 95 DirectX acceleration

- Consumer appliance PCs

- Living room PCs

- Microsoft Simply Interactive PCs

- Video conferencing

- Multimedia applications

### Feature Summary

- Microsoft Windows 95 Direct3D accelerator

- Programmable 3D triangle set up coprocessor

- Triangle parameter edge traversal/interpolation

- Data/address fetch for texture, color, alpha and Z values per triangle or tri-strip

- Scaled and rotated sprites

- Perspective-correct texture mapping

- Bilinear and trilinear texture filtering

- MIP mapping

- Texture transparency and translucency

- True Color and Palletized texture support

- Alpha blending translucency, fog, depth queuing

- Z-buffering and double buffering

- Flat and Gouraud shading

- Microsoft Windows 95 DirectDraw accelerator

- High-performance 2D graphics acceleration

- 64KB GUI command queue

- Transparent BLT

- Microsoft Windows 95 DirectVideo accelerator

- Hardware-accelerated video playback with sharpness control

- multi-tap horizontal/vertical interpolation filtering for video display

- Two hardware video windows

- Hardware double-buffering

- Chroma and color keying

- Host bus interfaces

- PCI 2.1 with bus mastering

- 3.3 V 66 MHz Intel Accelerated Graphics Port (AGP)

- Integrated 173 MHz RAMDAC for all VESA display modes up to 1600 x 1200 at 65 Hz

- 64-bit SGRAM and SDRAM (2 MB to 4 MB)

- Supports 85 MHz bus

- TV/MPEG video display and capture support

- Glueless connection for Brooktree Video-Stream and MPEG decoders

- 3rd generation TrueView™ technology for interlaced video sources

- VBI data capture and decoding for Intercast

- 32 KB to 1 MB of Flash ROM

- Full VGA compatibility

- 208-pin PQFP

# PREFACE

---

## Document Contents

This hardware specification contains the following chapters.

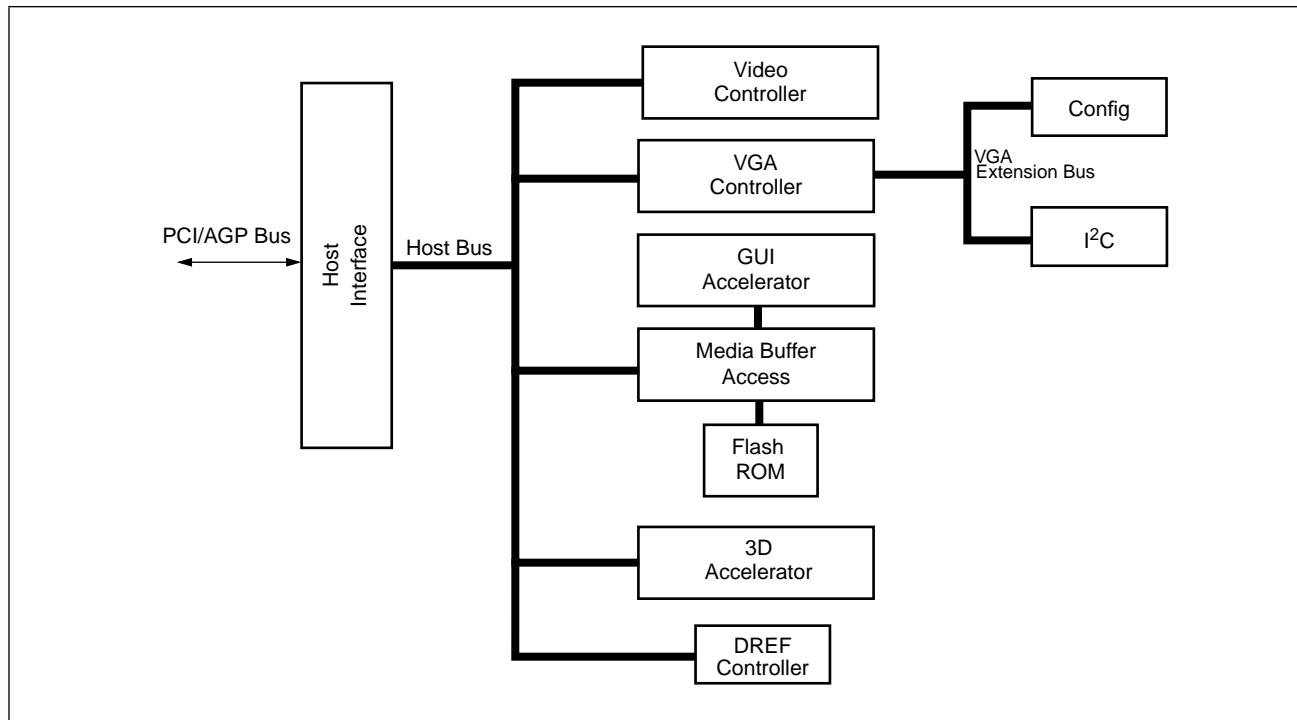

**Product Description**—Provides an overview of the Bt2166 Graphics/Video Controller, including a summary of the pin assignments.

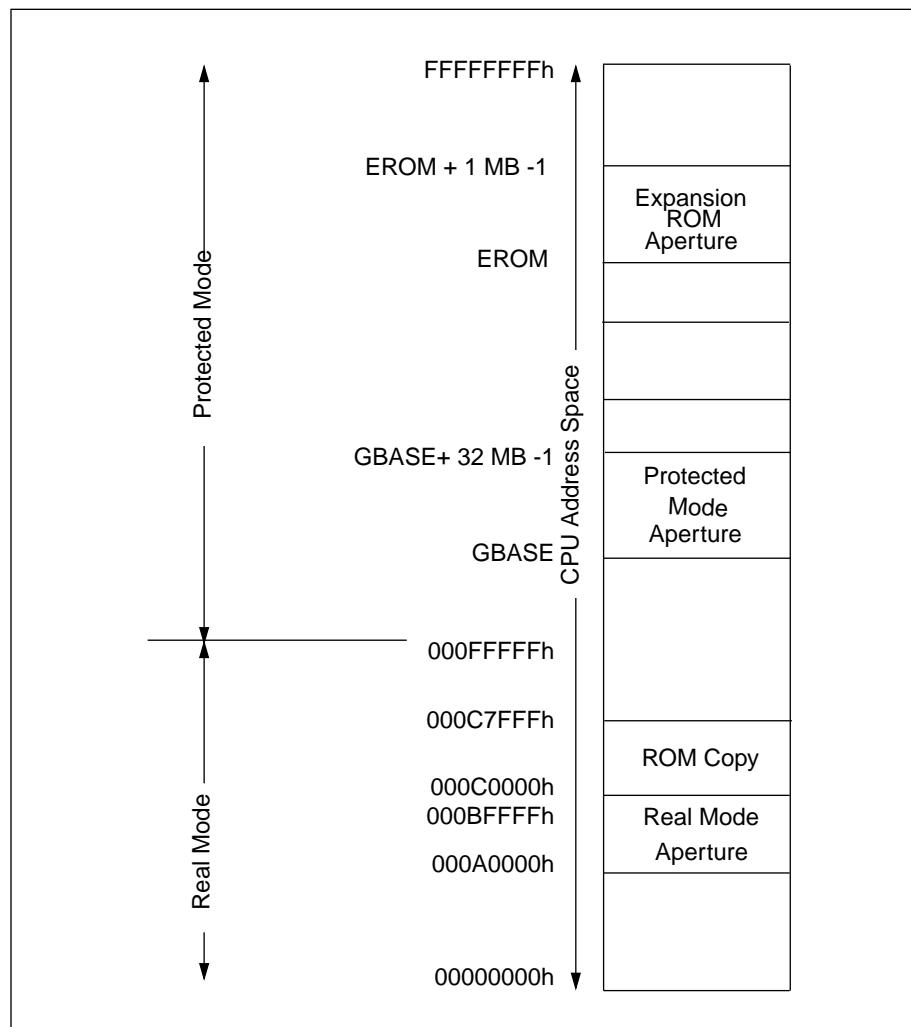

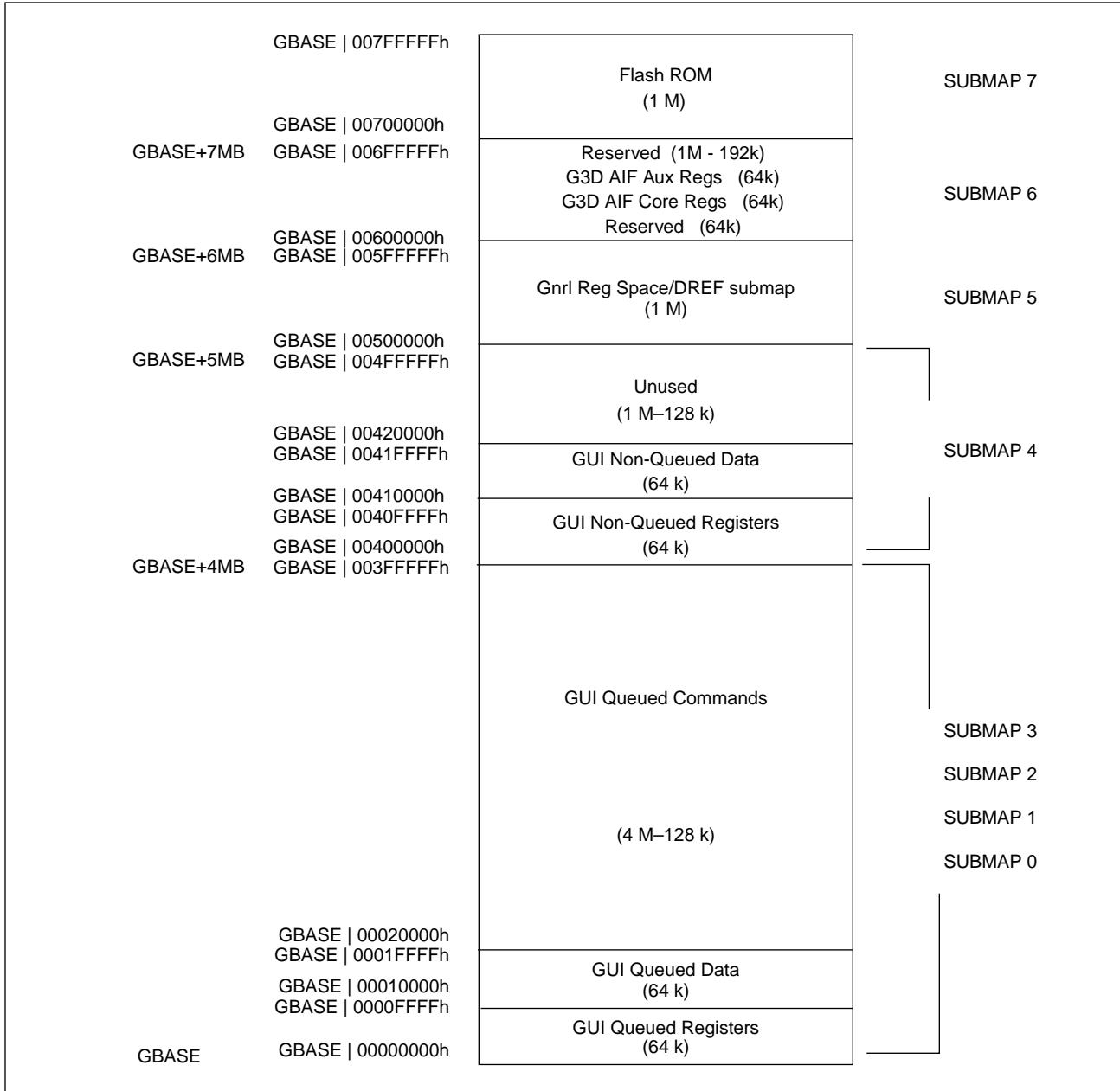

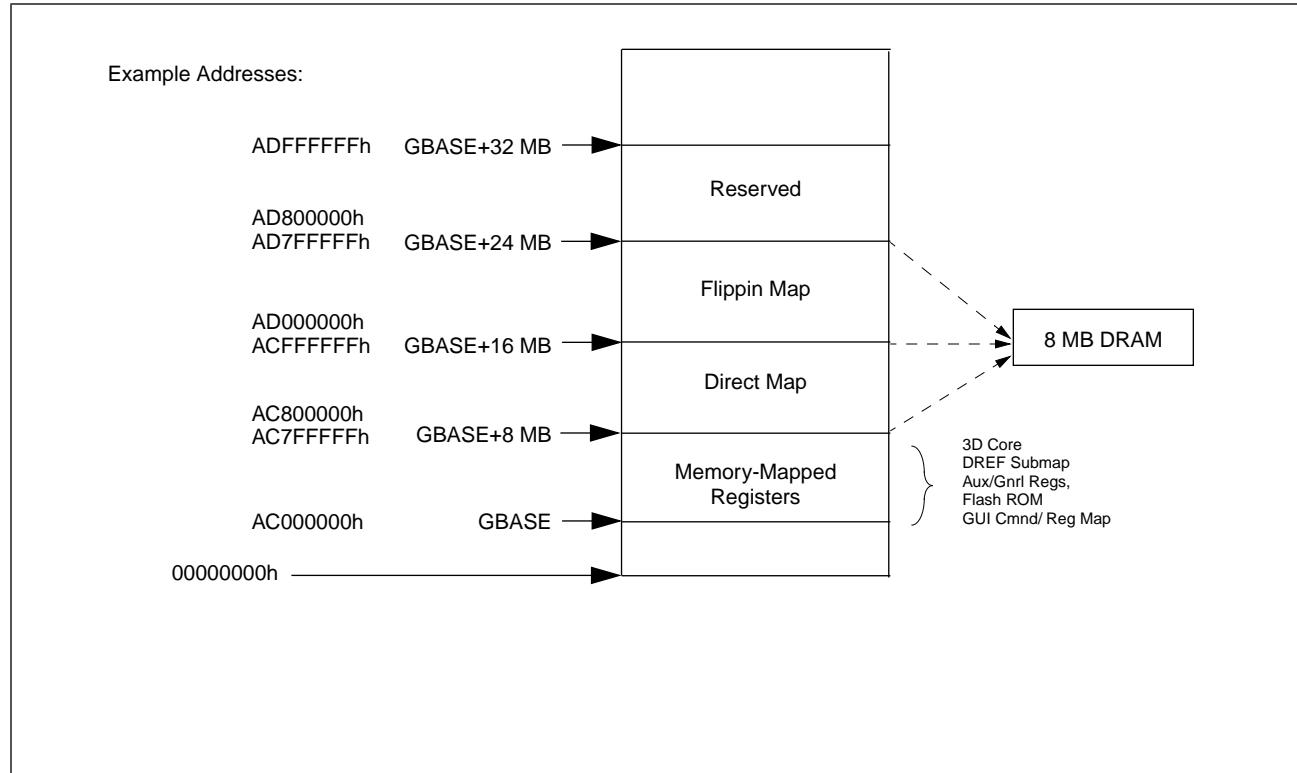

**CPU Address Space Apertures**—Describes the programming interface to the Bt2166 Graphics/Video accelerator, the Media Buffer, and BIOS ROM.

**VGA Implementation**—Describes the compatibility and operation of the VGA within the Bt2166 controller.

**I<sup>2</sup>C Register Definitions**—Specifies the programming interface to the Bt2166 I<sup>2</sup>C master and slave modules, and defines the I<sup>2</sup>C registers.

**PCI Configuration Space Register Definitions**—Contains the definitions of registers mapped to the PCI Configuration Space.

**GUI Accelerator**—Describes the CPU addressing to the GUI and defines GUI accelerator and GUI aperture registers.

**Interrupt Register Definitions**—Contains the definitions of the memory-mapped interrupt registers.

**Configuration and PLL Register Definitions**—Contains the definitions of the general configuration and PLL-related registers.

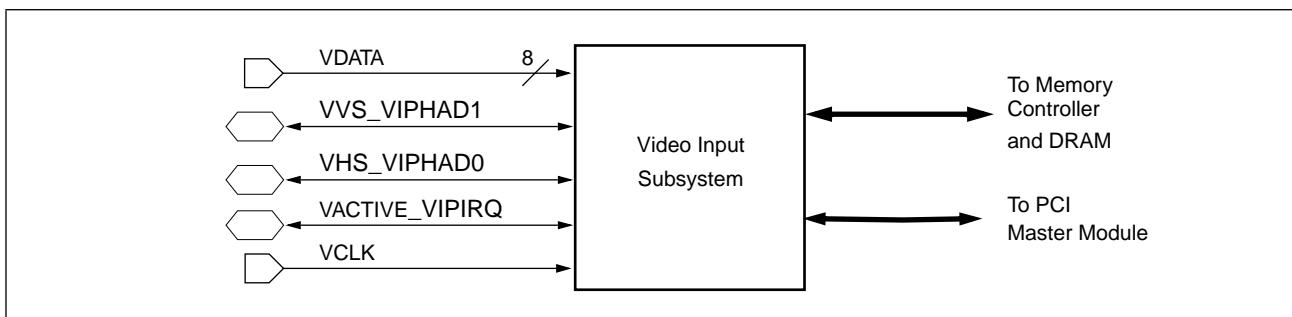

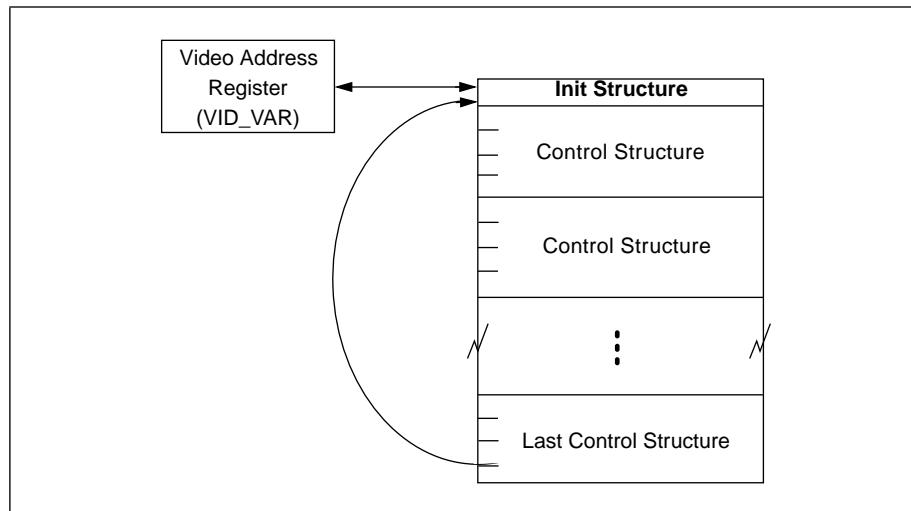

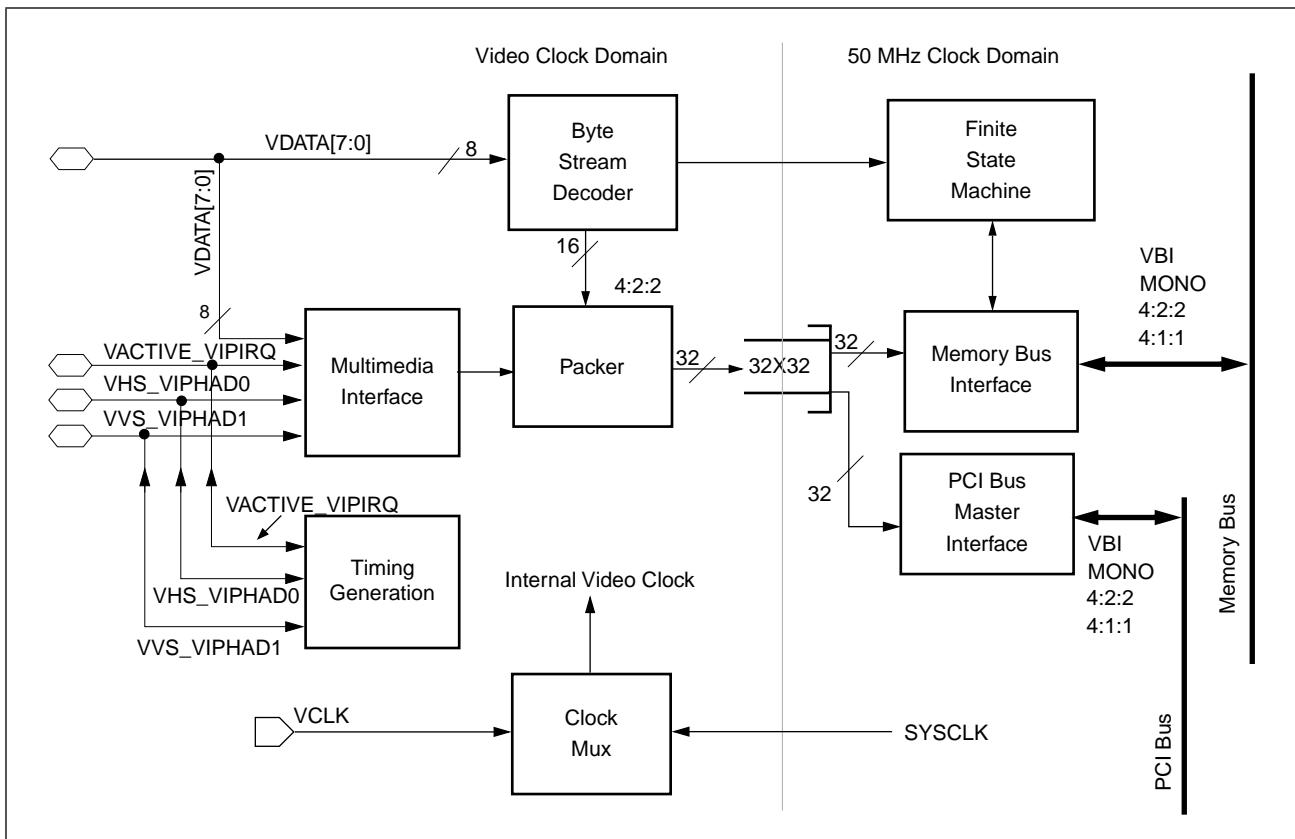

**Video Input Subsystem**—Describes the interfaces between the Bt2166 Graphics/Video Controller and the VideoStream Decoder, and between the Bt2166 and other video sources. Contains the definitions of the video input and Video Interface Port (VIP) registers.

**Display Refresh Controller**—Describes the module responsible for fetching display memory data for generating screen outputs and for generating CRT timing signals. This includes back-end video upscaling and mixing, chroma and color keying, and cursor overlay.

**3D Accelerator**—Describes the 3D graphics accelerator and pixel rendering engine. Contains the definitions for the 3D interface registers and the 3D accelerator and pixel rendering engine registers.

**PCI Configuration Space Register Definitions**—Contains the definitions of registers mapped to the PCI Configuration Space.

**CPU Host Bus Interface**—Describes PCI/AGP bus interface between the Bt2166 and the host CPU. Defines the PCI signal pins and provides timing diagrams.

**Synchronous Memory Interface**—Describes the interface between the Bt2166 and the SGRAM/SDRAM, which provides access to ROM and multimedia data and control information. Includes timing diagrams and connection diagrams.

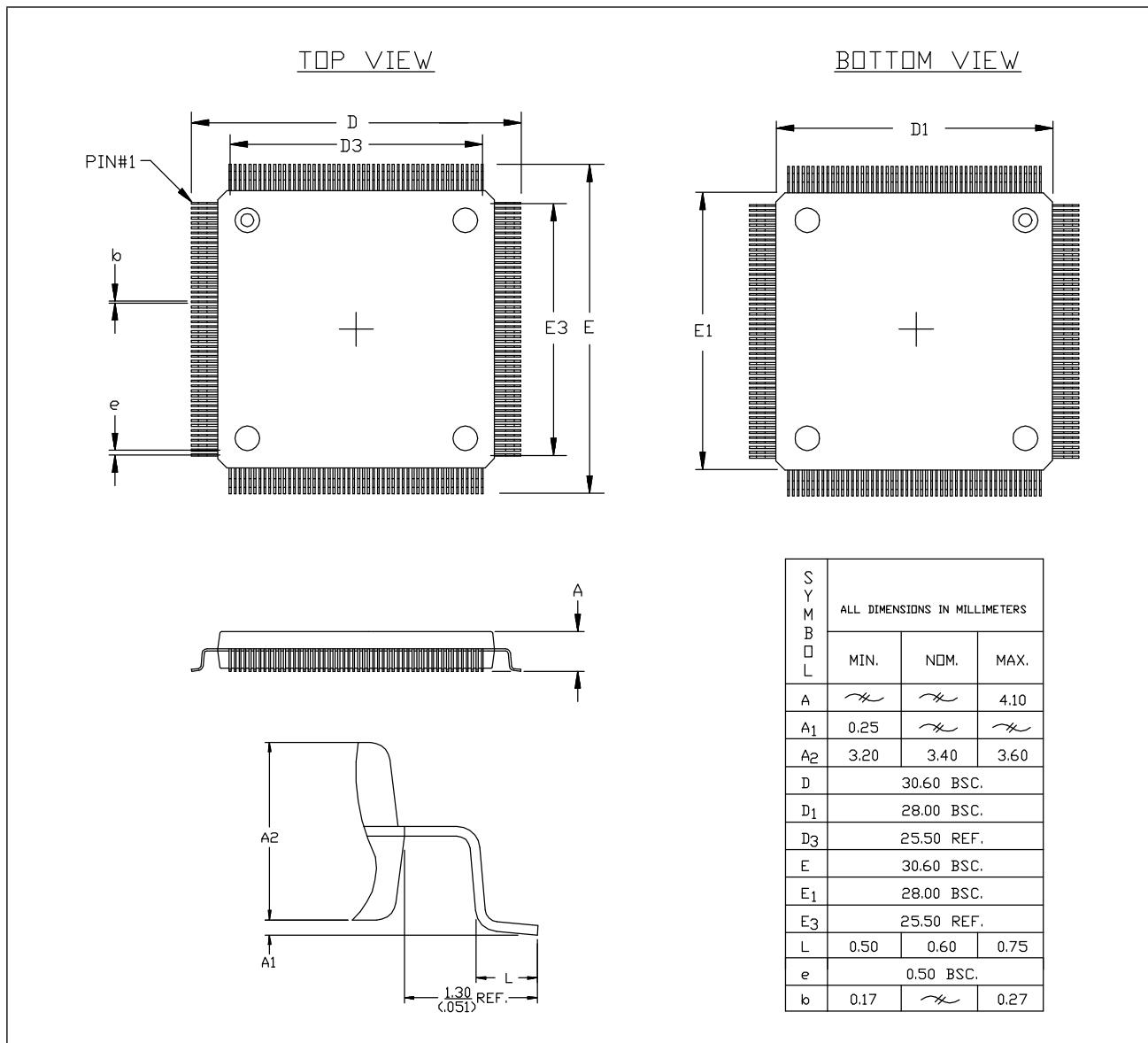

**Bt2166 Operating Specifications**—Provides the operating specifications for the Bt2166, including electrical, thermal, and packaging. Provides PLL tables for the pixel, memory, system, and GUI clocks.

## Related Documents

Bt829A VideoStream II Decoder Specification — Rockwell Semiconductor Systems, Brooktree Division

PCI Local Bus Specification, Revision 2.1 — PCI Special Interest Group

Accelerated Graphics Port (AGP) Interface Specification, Revision 1.0 — Intel Corporation

The I<sup>2</sup>C Bus Reference Guide — Rockwell Semiconductor Systems, Brooktree Division

Richard F. Ferraro, *Programmer's Guide to the EGA and VGA Cards*, Second Edition (Addison-Wesley Publishing Company, Inc., 1990)

Bradley Dyck Kliewer, *EGA/VGA: A Programmer's Reference Guide* (Intertext Publications, McGraw-Hill Publishing Company, New York, 1990)

## Notation Conventions

| Example                   | Description                                                                                                                                                                                                                                                            |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\overline{\text{RESET}}$ | The overbar above a signal or pin (or a portion of the signal or pin) indicates active-LOW.                                                                                                                                                                            |

| 8'hAD                     | Hexadecimal notation used by hardware designers, in the format:<br>$<\text{num bits}>'h<\text{value}>$<br>Where:<br>$<\text{num bits}>$ = number of bits in hex value<br>$'h$ = hexadecimal<br>$<\text{value}>$ = hex value, each alphanumeric digit represents 4 bits |

| 6'b01011                  | Binary notation used by hardware designers, in the format:<br>$<\text{num bits}>'b<\text{value}>$<br>Where:<br>$<\text{num bits}>$ = number of bits in binary value<br>$'b$ = binary<br>$<\text{value}>$ = binary value of each bit                                    |

| AB31h                     | Hexadecimal notation used by assembler programmers, in the format:<br>$<\text{value}>h$<br>Where:<br>$<\text{value}>$ = hex value, each alphanumeric digit represents 4 bits<br>$h$ = hexadecimal                                                                      |

| 0x000AC100                | Hexadecimal notation used by C programmers, in the format:<br>$0x<\text{value}>$<br>Where:<br>$0x$ = hexadecimal<br>$<\text{value}>$ = hex value, each alphanumeric digit represents 4 bits                                                                            |

# TABLE OF CONTENTS

---

|                                                 |       |

|-------------------------------------------------|-------|

| <b>Preface</b> .....                            | iii   |

| <b>Document Contents</b> .....                  | iii   |

| <b>Related Documents</b> .....                  | .v    |

| <b>Notation Conventions</b> .....               | vi    |

| <b>Table of Contents</b> .....                  | vii   |

| <b>List of Figures</b> .....                    | xxiii |

| <b>List of Tables</b> .....                     | xxv   |

| <b>Product Description</b> .....                | 1     |

| <b>Introduction</b> .....                       | 1     |

| High-Performance 3D Graphics Acceleration ..... | 2     |

| High-Performance 2D Graphics Acceleration ..... | 4     |

| Video Playback and Display .....                | 4     |

| <b>Interface Description</b> .....              | 7     |

| CPU/Host Interface .....                        | 7     |

| Programmable Multimedia Interface .....         | 7     |

| Memory Interface.....                           | 8     |

| BIOS ROM Interface .....                        | 8     |

| I2C Interface .....                             | 8     |

| Display Mode Support.....                       | 8     |

| <b>Bt2166 Pin Layout and Descriptions</b> ..... | 9     |

| <b>CPU Address Space Apertures</b> .....        | 15    |

| <b>Aperture Space Theory of Operation</b> ..... | 15    |

| <b>Protected Mode Aperture</b> .....            | 18    |

|                                                               |    |

|---------------------------------------------------------------|----|

| <b>Media Buffer Maps</b> . . . . .                            | 20 |

| Direct Map . . . . .                                          | 20 |

| Flippin Map . . . . .                                         | 21 |

| BIOS ROM Support . . . . .                                    | 23 |

| <b>Real Mode Aperture</b> . . . . .                           | 25 |

| <b>VGA Implementation</b> . . . . .                           | 27 |

| <b>VGA Compatibility</b> . . . . .                            | 27 |

| <b>VGA Operation</b> . . . . .                                | 28 |

| Simultaneous Operation with Other Bt2166 Modules . . . . .    | 28 |

| VGA and DREF . . . . .                                        | 28 |

| VGA and Pixel Clock PLL . . . . .                             | 31 |

| <b>VGA Extension Register Control and Status</b> . . . . .    | 32 |

| Enable VGA CRT Controller Mechanism . . . . .                 | 32 |

| Enable VGA CRT Controller DREF Programming . . . . .          | 32 |

| 25 MHz PLL Select . . . . .                                   | 32 |

| 28 MHz PLL Select . . . . .                                   | 32 |

| Attribute Index Status . . . . .                              | 33 |

| VGA CRT Generation Status . . . . .                           | 33 |

| VGA Read Latches . . . . .                                    | 33 |

| VGA DAC Mode . . . . .                                        | 33 |

| <b>Configuration for VGA</b> . . . . .                        | 34 |

| <b>Support for VESA BIOS Extension Modes</b> . . . . .        | 35 |

| VBE Modes . . . . .                                           | 35 |

| Frame Buffer Models . . . . .                                 | 35 |

| DREF register Programming and High-Resolution Modes . . . . . | 35 |

| Mode Setting Procedure . . . . .                              | 36 |

| Logical Window Control . . . . .                              | 36 |

| DAC Palette Format . . . . .                                  | 36 |

| <b>I/O Mapped Register Definitions</b> . . . . .              | 37 |

| <b>Introduction</b> . . . . .                                 | 37 |

| <b>VGA Graphics Registers</b> . . . . .                       | 39 |

| Graphics Index Port . . . . .                                 | 39 |

| <i>register name: GRP_INDEX</i>                               |    |

| Graphics Data Port . . . . .                                  | 39 |

| <i>register name: GRP_DATA</i>                                |    |

| Set/Reset Register . . . . .                                  | 39 |

| <i>register name: GRP_SR</i>                                  |    |

| Enable Set/Reset Register . . . . .                           | 40 |

| <i>register name: GRP_ESR</i>                                 |    |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| Color Compare Register . . . . .                            | 40        |

| <i>register name: GRP_CC</i>                                |           |

| Data Rotate Register . . . . .                              | 41        |

| <i>register name: GRP_ROT</i>                               |           |

| Read Map Select Register . . . . .                          | 41        |

| <i>register name: GRP_RDPLN</i>                             |           |

| Mode Register . . . . .                                     | 42        |

| <i>register name: GRP_MODE</i>                              |           |

| Graphics Miscellaneous Register . . . . .                   | 43        |

| <i>register name: GRP_MISC</i>                              |           |

| Color Don't Care Register . . . . .                         | 43        |

| <i>register name: GRP_CCX</i>                               |           |

| Bit Mask Register . . . . .                                 | 44        |

| <i>register name: GRP_BITMASK</i>                           |           |

| <b>Extension Registers Accessed Via VGA Space . . . . .</b> | <b>45</b> |

| VGA Configuration Register . . . . .                        | 45        |

| <i>register name: GRP_VGACFG</i>                            |           |

| Chip ID Registers . . . . .                                 | 45        |

| <i>register name: GRP_CID[1:0]</i>                          |           |

| PLL25 Select Registers . . . . .                            | 45        |

| <i>register name: GRP_25PLL[1:0]</i>                        |           |

| PLL28 Select Registers . . . . .                            | 46        |

| <i>register name: GRP_28PLL[1:0]</i>                        |           |

| GUI Base Address Registers . . . . .                        | 46        |

| <i>register name: GRP_GUI_BASE[3:0]</i>                     |           |

| Read Latch Registers . . . . .                              | 48        |

| <i>register name: GRP_RDLAT[3:0]</i>                        |           |

| VGA Status Register . . . . .                               | 48        |

| <i>register name: GRP_VGASTAT</i>                           |           |

| I/O Aperture Shadow Register . . . . .                      | 48        |

| <i>register name: GRP_IOAP</i>                              |           |

| GRP_PIO_ENABLE Register . . . . .                           | 49        |

| <i>register name: GRP_PIO_ENABLE</i>                        |           |

| PIO Data Register . . . . .                                 | 50        |

| <i>register name: GRP_PIO_DATA</i>                          |           |

| Configuration Registers . . . . .                           | 51        |

| <i>register name: GRP_CFG[A:0]</i>                          |           |

| <b>VGA Sequencer/Extension Registers . . . . .</b>          | <b>56</b> |

| Sequencer Index Register . . . . .                          | 56        |

| <i>register name: SEQ_INDEX</i>                             |           |

| Sequencer Data Port . . . . .                               | 56        |

| <i>register name: SEQ_DATA</i>                              |           |

| Reset Register . . . . .                                    | 56        |

| <i>register name: SEQ_RST</i>                               |           |

| Clocking Mode Register . . . . .                            | 56        |

| <i>register name: SEQ_CLK</i>                               |           |

|                                           |    |

|-------------------------------------------|----|

| Map Mask Register . . . . .               | 57 |

| <i>register name: SEQ_WPMASK</i>          |    |

| Character Map Select Register . . . . .   | 58 |

| <i>register name: SEQ_CFS</i>             |    |

| Memory Mode Register . . . . .            | 59 |

| <i>register name: SEQ_MMODE</i>           |    |

| Unlock Register . . . . .                 | 60 |

| <i>register name: SEQ_UNLOCK</i>          |    |

| <b>VGA CRT Controller</b> . . . . .       | 62 |

| CRTC Color Index . . . . .                | 62 |

| <i>register name: CRT_INDEX_C</i>         |    |

| CRTC Monochrome Index . . . . .           | 62 |

| <i>register name: CRT_INDEX_M</i>         |    |

| CRTC Color Data . . . . .                 | 62 |

| <i>register name: CRT_DATA_C</i>          |    |

| CRTC Monochrome Data. . . . .             | 62 |

| <i>register name: CRT_DATA_M</i>          |    |

| Horizontal Total Register . . . . .       | 62 |

| <i>register name: CRT_HTOT</i>            |    |

| Horizontal Display End Register. . . . .  | 63 |

| <i>register name: CRT_HDSP_END</i>        |    |

| Start Horizontal Blank Register . . . . . | 63 |

| <i>register name: CRT_HBLANK_ST</i>       |    |

| End Horizontal Blank Register . . . . .   | 63 |

| <i>register name: CRT_HBLANK_END</i>      |    |

| Start Horizontal Sync Register. . . . .   | 63 |

| <i>register name: CRT_HSYNC_ST</i>        |    |

| End Horizontal Sync Register . . . . .    | 64 |

| <i>register name: CRT_HSYNC_END</i>       |    |

| Vertical Total Register. . . . .          | 64 |

| <i>register name: CRT_VTOT</i>            |    |

| Overflow Register. . . . .                | 64 |

| <i>register name: CRT_OVERFLOW</i>        |    |

| Preset Row Scan Register. . . . .         | 65 |

| <i>register name: CRT_PRE_RS</i>          |    |

| Character Height Register . . . . .       | 65 |

| <i>register name: CRT_CHEIGHT</i>         |    |

| Cursor Start Register . . . . .           | 65 |

| <i>register name: CRT_CUR_ST</i>          |    |

| Cursor End Register. . . . .              | 66 |

| <i>register name: CRT_CUR_END</i>         |    |

| Start Address High Register . . . . .     | 66 |

| <i>register name: CRT_SCREEN_STH</i>      |    |

| Start Address Low Register . . . . .      | 66 |

| <i>register name: CRT_SCREEN_STL</i>      |    |

| Cursor Location High Register . . . . .   | 67 |

| <i>register name: CRT_CUR_LOCH</i>        |    |

|                                                 |    |

|-------------------------------------------------|----|

| Cursor Location Low Register . . . . .          | 67 |

| <i>register name: CRT_CUR_LOCL</i>              |    |

| Start Vertical Sync Register . . . . .          | 67 |

| <i>register name: CRT_VSYNC_ST</i>              |    |

| End Vertical Sync Register . . . . .            | 68 |

| <i>register name: CRT_VSYNC_END</i>             |    |

| Vertical Display End Register . . . . .         | 68 |

| <i>register name: CRT_VDSP_END</i>              |    |

| Offset Register . . . . .                       | 68 |

| <i>register name: CRT_OFFSET</i>                |    |

| Underline Register . . . . .                    | 69 |

| <i>register name: CRT_UNDERLINE</i>             |    |

| Start Vertical Blank Register . . . . .         | 69 |

| <i>register name: CRT_VBLANK_ST</i>             |    |

| End Vertical Blank Register . . . . .           | 69 |

| <i>register name: CRT_VBLANK_END</i>            |    |

| Mode Control Register . . . . .                 | 70 |

| <i>register name: CRT_MODE_CTL</i>              |    |

| Line Compare Register . . . . .                 | 70 |

| <i>register name: CRT_LINECMP</i>               |    |

| <b>VGA Attribute Controller</b> . . . . .       | 71 |

| Attribute Index and Data Port . . . . .         | 71 |

| <i>register name: ATT_ADDR</i>                  |    |

| Read Data Port . . . . .                        | 72 |

| <i>register name: ATT_RD</i>                    |    |

| Palette Registers . . . . .                     | 72 |

| <i>register name: ATT_PAL_REG[15:0]</i>         |    |

| Mode Control Register . . . . .                 | 73 |

| <i>register name: ATT_MODE</i>                  |    |

| Overscan Color Register . . . . .               | 73 |

| <i>register name: ATT_OVRS</i>                  |    |

| Color Plane Enable Register . . . . .           | 74 |

| <i>register name: ATT_CPE</i>                   |    |

| Horizontal Panning Register . . . . .           | 74 |

| <i>register name: ATT_HPAN</i>                  |    |

| Color Select Register . . . . .                 | 75 |

| <i>register name: ATT_CLRSEL</i>                |    |

| <b>VGA General/External Registers</b> . . . . . | 76 |

| Input Status #0 Register . . . . .              | 76 |

| <i>register name: INP_STAT0</i>                 |    |

| Color Input Status #1 Register . . . . .        | 76 |

| <i>register name: INP_STAT_C</i>                |    |

| Monochrome Input Status #1 Register . . . . .   | 76 |

| <i>register name: INP_STAT_M</i>                |    |

| Write Miscellaneous Output Register . . . . .   | 77 |

| <i>register name: MISC_OUT_W</i>                |    |

|                                                              |     |

|--------------------------------------------------------------|-----|

| Read Miscellaneous Output Register.....                      | 77  |

| <i>register name: MISC_OUT_R</i>                             |     |

| Feature Control Register .....                               | 78  |

| <i>register name: FC</i>                                     |     |

| <b>VGA Color Registers</b> .....                             | 79  |

| DAC Mask Register .....                                      | 79  |

| <i>register name: DAC_MASK</i>                               |     |

| DAC State Register .....                                     | 79  |

| <i>register name: DAC_STATE</i>                              |     |

| DAC Read Address Register .....                              | 79  |

| <i>register name: DAC_RDADDR</i>                             |     |

| DAC Write Address Register .....                             | 80  |

| <i>register name: DAC_WRADDR</i>                             |     |

| DAC Data Register.....                                       | 80  |

| <i>register name: DAC_DATA</i>                               |     |

| <b>I<sup>2</sup>C Register Definitions</b> .....             | 81  |

| <b>I<sup>2</sup>C Master and Slave Controllers</b> .....     | 81  |

| I <sup>2</sup> C Control WRITE Register.....                 | 83  |

| <i>register name: GRP_I2C_CTRLW</i>                          |     |

| I <sup>2</sup> C Control READ Register .....                 | 84  |

| <i>register name: GRP_I2C_CTRLR</i>                          |     |

| <b>I<sup>2</sup>C Master Module Software Interface</b> ..... | 85  |

| I <sup>2</sup> C Master Data Register.....                   | 85  |

| <i>register name: GRP_I2C_MDATA</i>                          |     |

| I <sup>2</sup> C Master Control Read Register .....          | 86  |

| <i>register name: GRP_I2C_MCTRLR</i>                         |     |

| I <sup>2</sup> C Master Control Write Register .....         | 88  |

| <i>register name: GRP_I2C_MCTRLW</i>                         |     |

| <b>I<sup>2</sup>C Slave Module Software Interface</b> .....  | 94  |

| I <sup>2</sup> C Slave Data Register.....                    | 94  |

| <i>register name: GRP_I2C_SDATA</i>                          |     |

| I <sup>2</sup> C Slave Control Read Register .....           | 95  |

| <i>register name: GRP_I2C_SCTRLR</i>                         |     |

| I <sup>2</sup> C Slave Control Write Register .....          | 97  |

| <i>register name: GRP_I2C_SCTRLW</i>                         |     |

| <b>GUI Accelerator</b> .....                                 | 103 |

| <b>GUI Theory Of Operation</b> .....                         | 103 |

| Retained Bitmap Context.....                                 | 103 |

| Raster Operation .....                                       | 103 |

| BLT Transparency.....                                        | 104 |

| <b>GUI Command/Register Map</b> .....                        | 105 |

| <b>CPU Addressing of GUI</b> .....                           | 109 |

|                                             |     |

|---------------------------------------------|-----|

| <b>GUI Commands</b> . . . . .               | 112 |

| RWREGISTER Command . . . . .                | 114 |

| BITBLT Command . . . . .                    | 114 |

| TEXTBLT Command . . . . .                   | 115 |

| RWGUIDATA Command . . . . .                 | 115 |

| LINE Draw Command . . . . .                 | 116 |

| QMARK Command . . . . .                     | 117 |

| <b>GUI Accelerator Registers</b> . . . . .  | 118 |

| Bitmap Context Registers . . . . .          | 120 |

| GUI Command Register . . . . .              | 123 |

| <i>register name</i> : GUIREG_CMD           |     |

| GUI Configuration Register . . . . .        | 123 |

| <i>register name</i> : GUIREG_CFG           |     |

| Foreground Color Register . . . . .         | 126 |

| <i>register name</i> : GUIFG_COLOR          |     |

| Background Color Register . . . . .         | 126 |

| <i>register name</i> : GUIBG_COLOR          |     |

| Destination XY Increment Register . . . . . | 127 |

| <i>register name</i> : GUIDST_XY_INC        |     |

| Blit Control (Direction) Register . . . . . | 128 |

| <i>register name</i> : GUIBLT_CONTROL       |     |

| LINE Control Register . . . . .             | 129 |

| <i>register name</i> : GUILINE_CONTROL      |     |

| Line Pattern Register . . . . .             | 130 |

| <i>register name</i> : GUILINE_PATT         |     |

| Bresenham 0, Address Register . . . . .     | 130 |

| <i>register name</i> : GUI_BRES0_ADDR       |     |

| Bresenham 0, Error Register . . . . .       | 131 |

| <i>register name</i> : GUI_BRES0_ERR        |     |

| Bresenham 0, K1 Register . . . . .          | 131 |

| <i>register name</i> : GUI_BRES0_K1         |     |

| Bresenham 0, K2 Register . . . . .          | 131 |

| <i>register name</i> : GUI_BRES0_K2         |     |

| Bresenham 0, Increment 1 Register . . . . . | 132 |

| <i>register name</i> : GUI_BRES0_INC1       |     |

| Bresenham 0, Increment 2 Register . . . . . | 132 |

| <i>register name</i> : GUI_BRES0_INC2       |     |

| Bresenham 0, Length Register . . . . .      | 132 |

| <i>register name</i> : GUI_BRES0_LENGTH     |     |

| <b>GUI Aperture Registers</b> . . . . .     | 133 |

| GUI FIFO Register . . . . .                 | 133 |

| <i>register name</i> : GUIREG_FIFO          |     |

| GUI FIFO Depth Register . . . . .           | 135 |

| <i>register name</i> : GUIREG_DEPTH         |     |

| MBA Control Register . . . . .              | 136 |

| <i>register name</i> : GUIREG_MBA           |     |

|                                                          |     |

|----------------------------------------------------------|-----|

| <b>Interrupt Register Definitions</b> .....              | 137 |

| <b>Interrupt Register Definitions</b> .....              | 137 |

| Interrupt Status Register .....                          | 137 |

| <i>register name: INT_SR</i>                             |     |

| Interrupt Mask Register .....                            | 138 |

| <i>register name: INT_MR</i>                             |     |

| Interrupt State Register .....                           | 138 |

| <i>register name: INT_STR</i>                            |     |

| Interrupt Firing Register .....                          | 138 |

| <i>register name: INT_FR</i>                             |     |

| <b>Configuration and PLL Register Definitions</b> .....  | 141 |

| <b>Configuration and PLL Registers</b> .....             | 141 |

| General Configuration Register .....                     | 141 |

| <i>register name: GEN_CFG</i>                            |     |

| Memory Configuration Register .....                      | 143 |

| <i>register name: MEM_CFG</i>                            |     |

| General Status Register .....                            | 145 |

| <i>register name: GEN_STATUS</i>                         |     |

| Memory Clock PLL Register .....                          | 145 |

| <i>register name: MEMCLK_PLL</i>                         |     |

| Pixel Clock PLL Register .....                           | 146 |

| <i>register name: PIXCLK_PLL</i>                         |     |

| GUI Clock PLL Register .....                             | 146 |

| <i>register name: GUICLK_PLL</i>                         |     |

| System Clock PLL Register .....                          | 147 |

| <i>register name: SYSCLK_PLL</i>                         |     |

| Memory Delay Register .....                              | 147 |

| <i>register name: MEM_DELAY</i>                          |     |

| <b>Video Input Subsystem</b> .....                       | 149 |

| <b>Introduction</b> .....                                | 149 |

| <b>INIT STRUCTURE Definition</b> .....                   | 152 |

| Capture Control Structure Definition .....               | 153 |

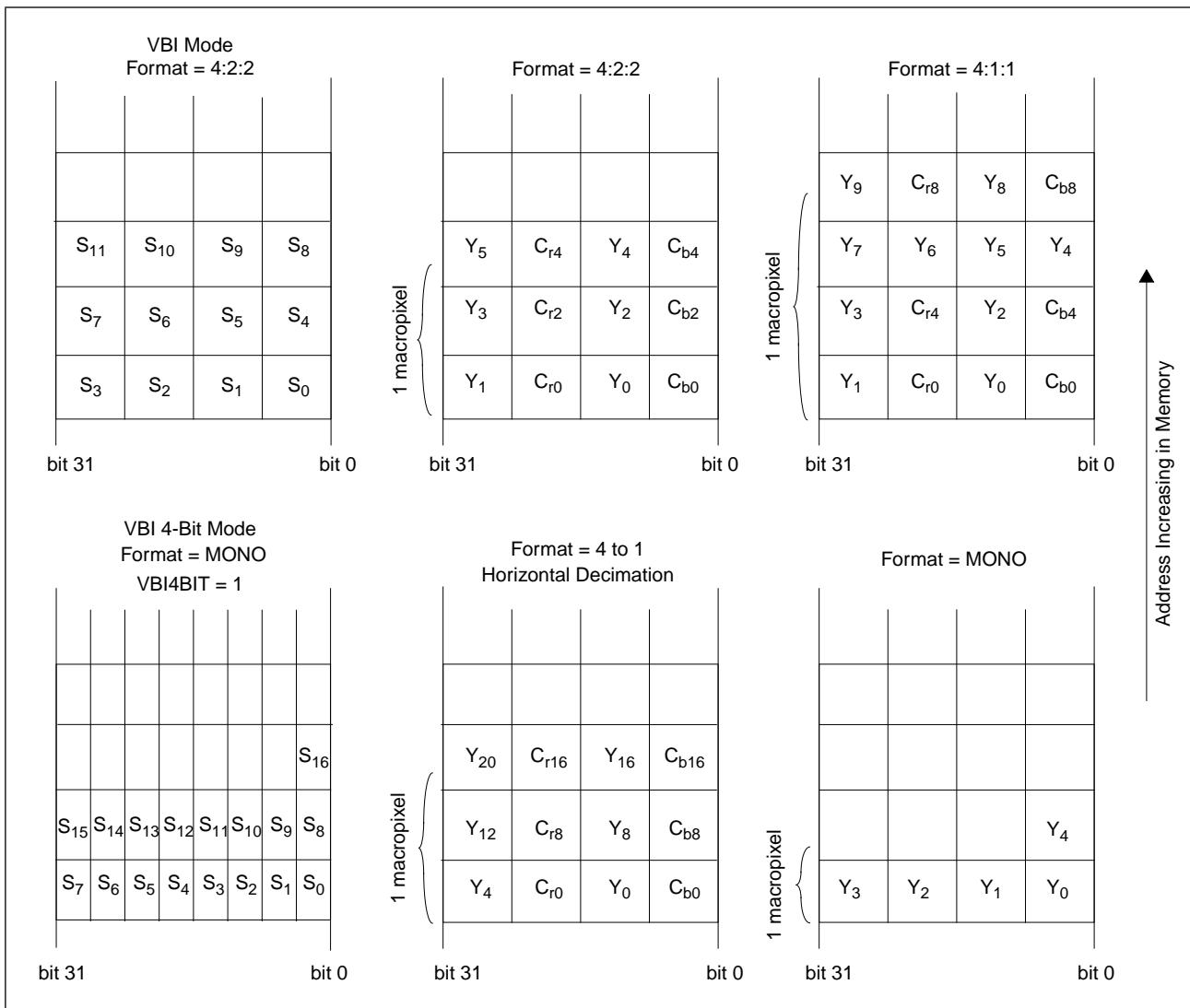

| VBI Mode Capture .....                                   | 155 |

| Video Formatting .....                                   | 156 |

| <b>Line Numbering System</b> .....                       | 157 |

| <b>Live Video Input</b> .....                            | 158 |

| <b>Closed Captioning Capture With A Video Icon</b> ..... | 158 |

| <b>Single Frame Record Example</b> .....                 | 159 |

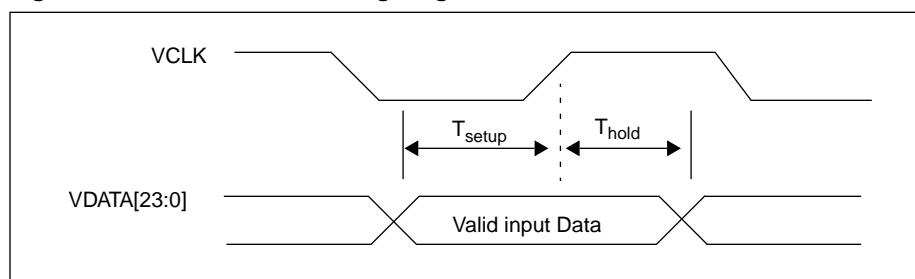

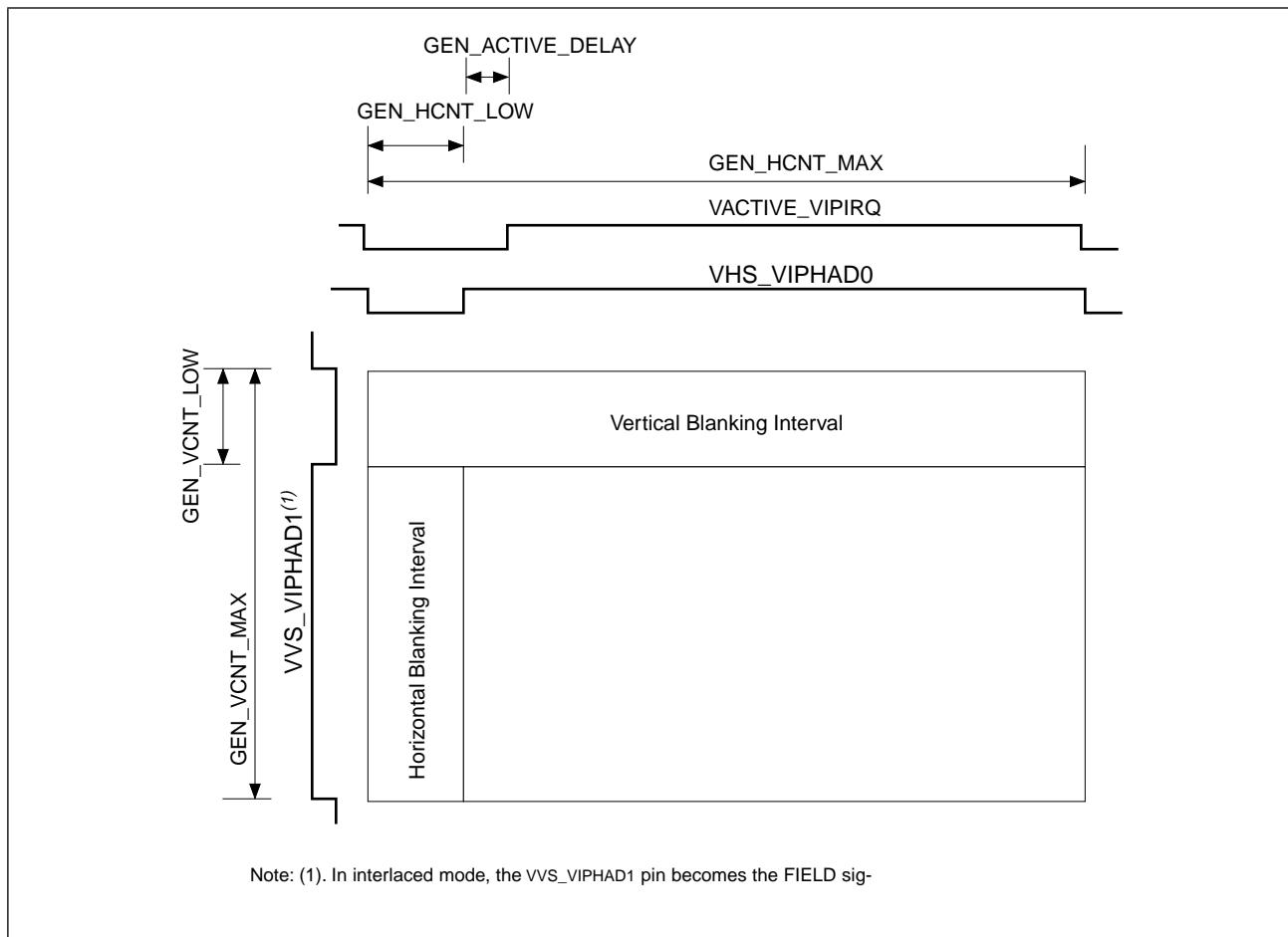

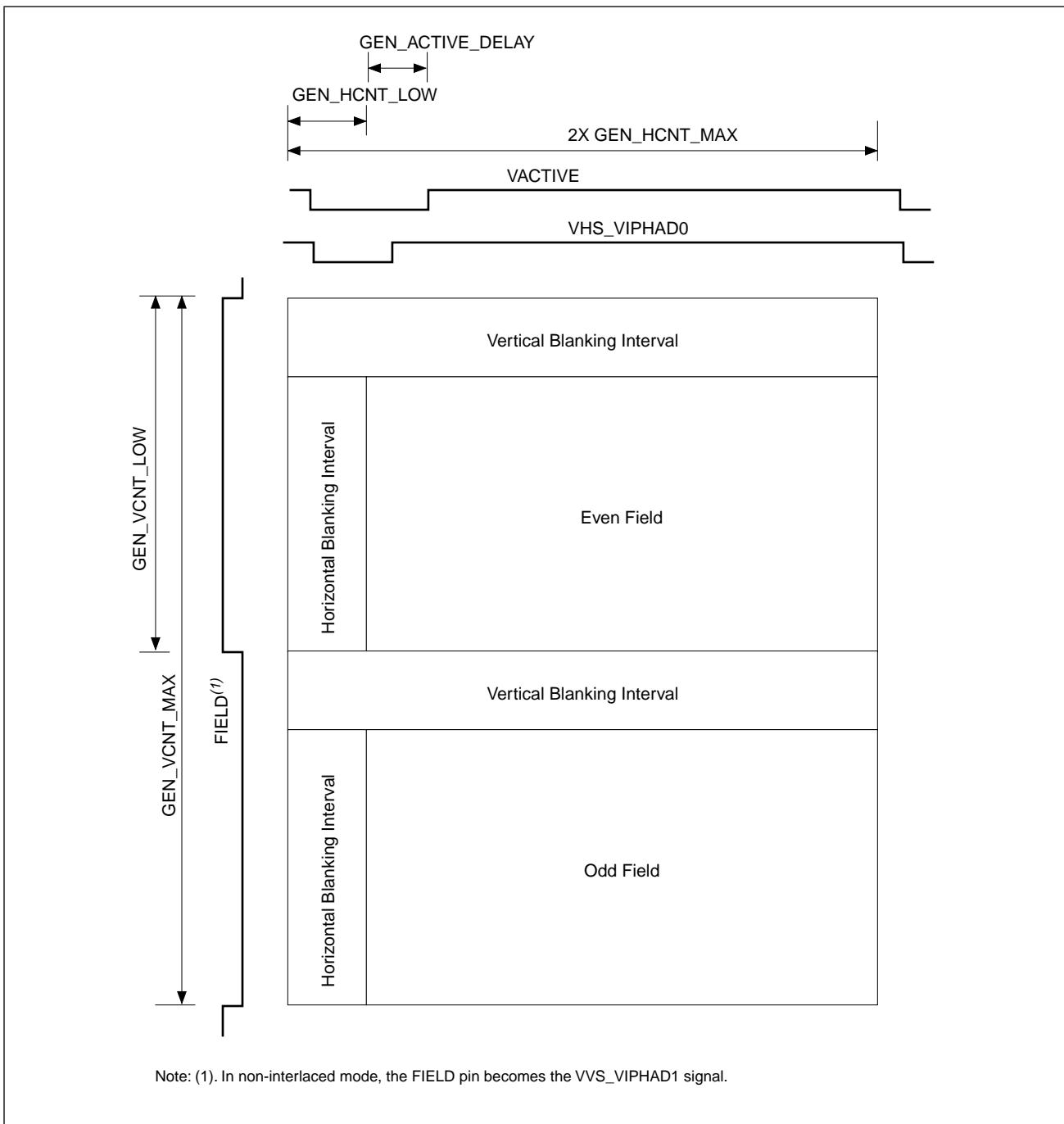

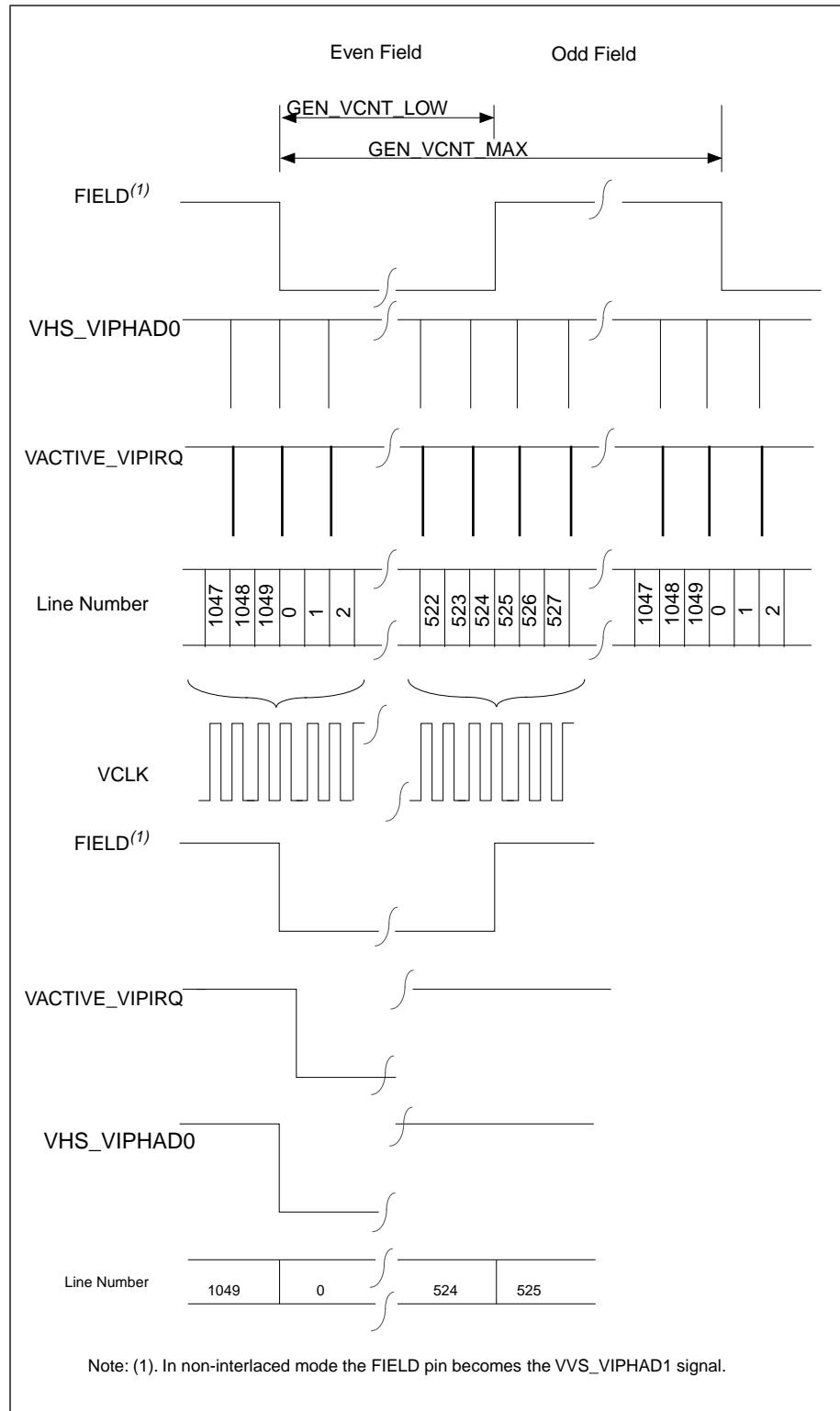

| Video Interface Timing .....                             | 159 |

|                                                   |     |

|---------------------------------------------------|-----|

| <b>Video Interface Port</b> .....                 | 164 |

| FIFO Command Register.....                        | 167 |

| <i>register name: FIFO_COMMAND</i>                |     |

| FIFO Address Register .....                       | 167 |

| <i>register name: FIFO_ADDR</i>                   |     |

| VIP Register Write .....                          | 167 |

| <i>register name: REG_WR_DATA</i>                 |     |

| VIP Command and Byte Count Register .....         | 168 |

| <i>register name: REG_COMMAND</i>                 |     |

| VIP Register Read.....                            | 168 |

| <i>register name: REG_RD_DATA</i>                 |     |

| VIP Configuration Register .....                  | 168 |

| <i>register name: VIP_CNFG</i>                    |     |

| <b>Video Buffer Management Hardware</b> .....     | 170 |

| Video Control Register.....                       | 170 |

| <i>register name: VID_VCR</i>                     |     |

| Video One Register .....                          | 171 |

| <i>register name: VID_V1R</i>                     |     |

| Video Two Register .....                          | 171 |

| <i>register name: VID_V2R</i>                     |     |

| Video Three Register.....                         | 172 |

| <i>register name: VID_V3R</i>                     |     |

| Video Address Register.....                       | 172 |

| <i>register name: VID_VAR</i>                     |     |

| Video DDA Register.....                           | 173 |

| <i>register name: VID_DDA</i>                     |     |

| Video Status Register .....                       | 174 |

| <i>register name: VID_STAT</i>                    |     |

| <b>Programmable Multimedia Interface</b> .....    | 175 |

| Video Timing Generation Vertical Register .....   | 175 |

| <i>register name: VID_GNV</i>                     |     |

| Video Timing Generation Horizontal Register ..... | 176 |

| <i>register name: VID_GNH</i>                     |     |

| Video Timing Generation Control Register .....    | 176 |

| <i>register name: VID_GNC</i>                     |     |

| <b>Display Refresh Controller</b> .....           | 179 |

| <b>Introduction</b> .....                         | 179 |

| <b>Features</b> .....                             | 179 |

| <b>Internal Memory Map</b> .....                  | 180 |

| Configuration Register.....                       | 185 |

|                                                                   |     |

|-------------------------------------------------------------------|-----|

| <b>Memory Control Interface Function</b> .....                    | 187 |

| Start Address Registers .....                                     | 187 |

| Vertical Upscale Handling .....                                   | 188 |

| Interlaced Mode Handling for Graphics .....                       | 188 |

| Interlaced Mode Handling for Cursor .....                         | 189 |

| Graphics Line Doubling .....                                      | 189 |

| <b>Register Interface Function</b> .....                          | 190 |

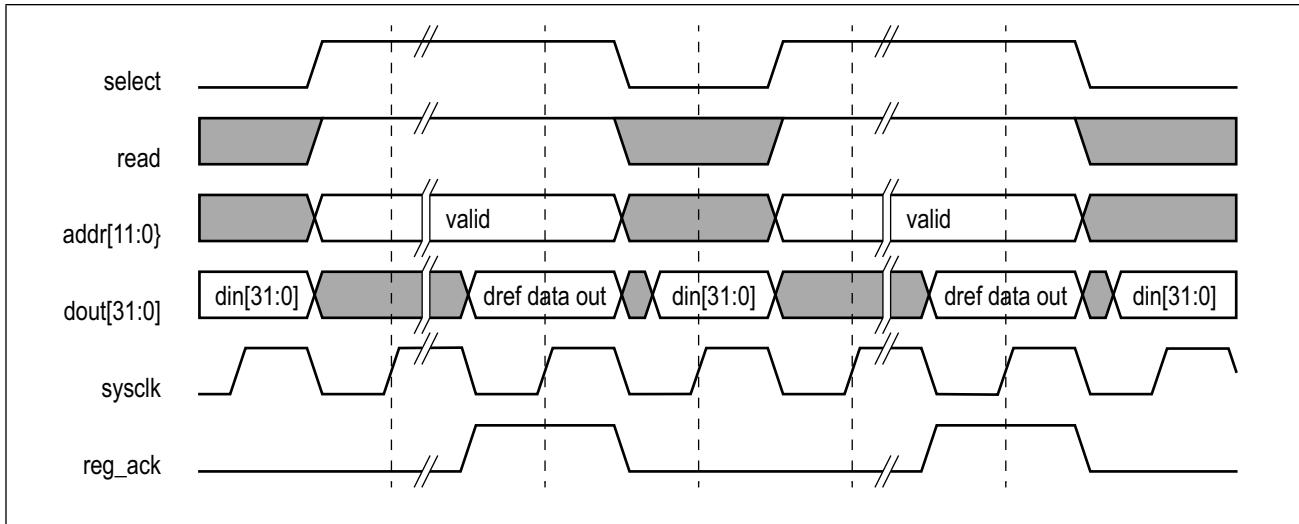

| Read Cycles .....                                                 | 190 |

| Write Cycles .....                                                | 190 |

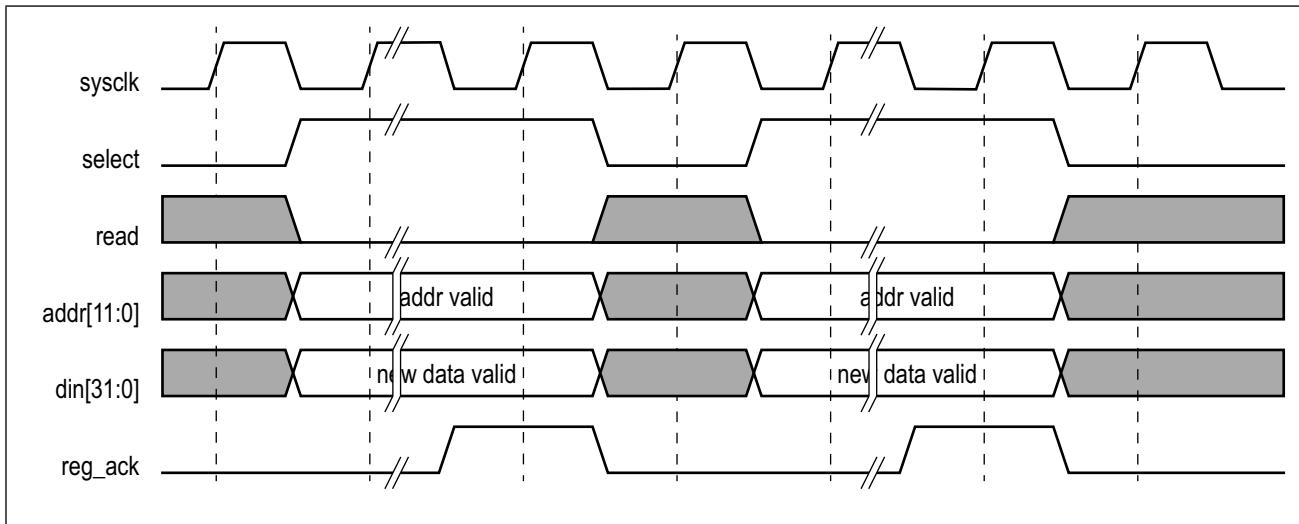

| Register Access Timing .....                                      | 190 |

| Color Palette Accessing .....                                     | 190 |

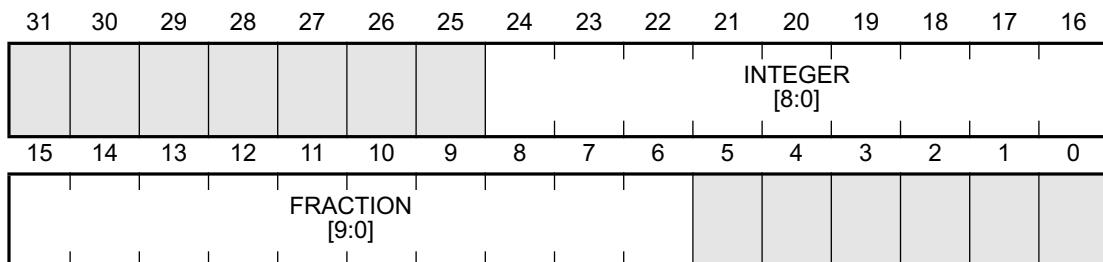

| Luma Correction .....                                             | 191 |

| Status Register .....                                             | 191 |

| <b>Timing Generator Function</b> .....                            | 193 |

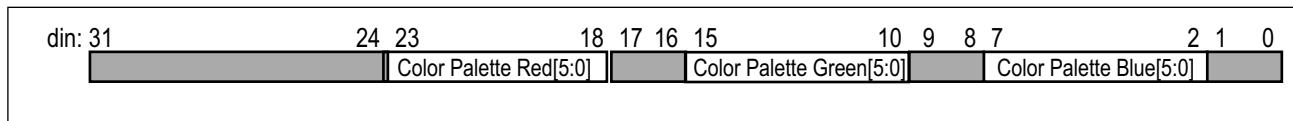

| Non-Interlaced Mode .....                                         | 194 |

| Horizontal Timing Generation .....                                | 195 |

| Vertical Timing Generation .....                                  | 196 |

| Interrupts .....                                                  | 198 |

| <b>Graphics Data Path</b> .....                                   | 199 |

| 4-bit Pseudocolor .....                                           | 200 |

| 8-bit Pseudocolor .....                                           | 200 |

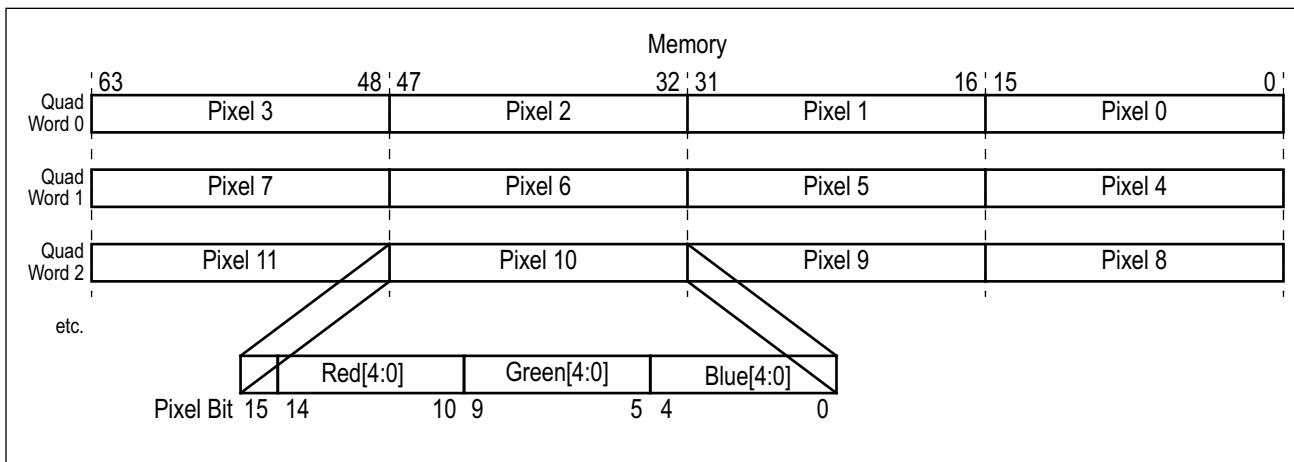

| 5-5-5 Truecolor .....                                             | 201 |

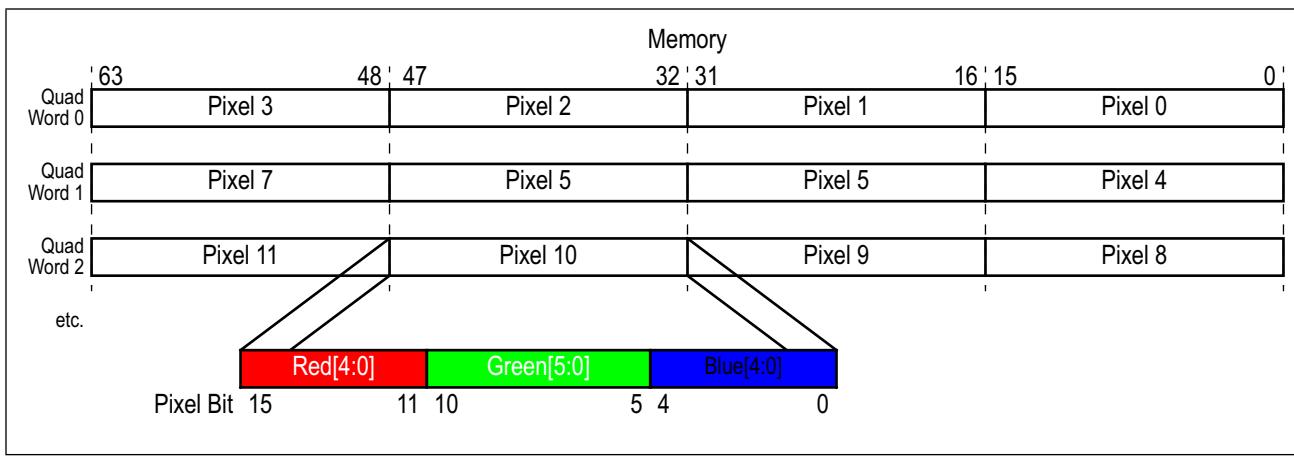

| 5-6-5 Truecolor .....                                             | 201 |

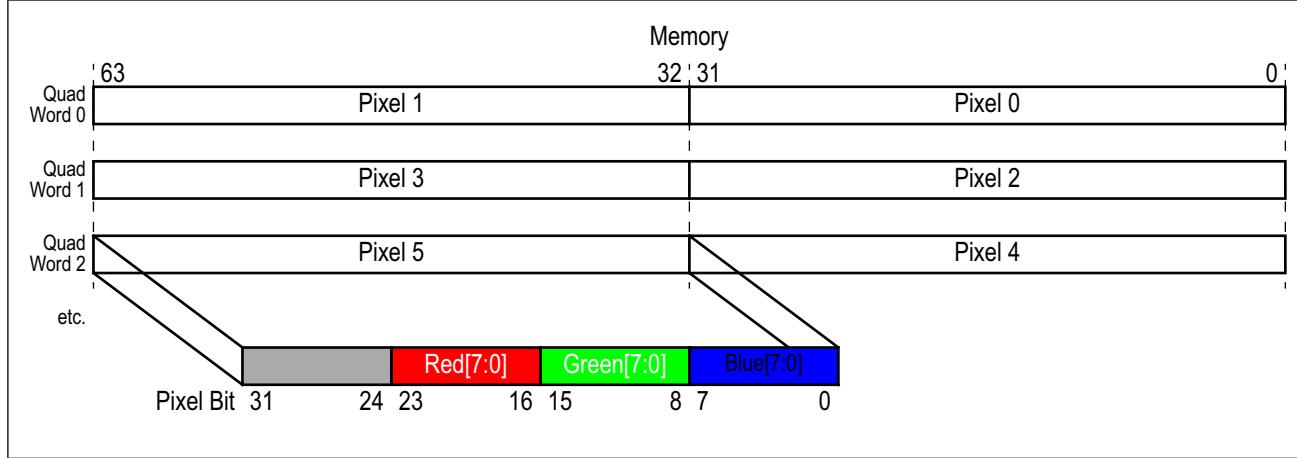

| 8-8-8 Truecolor, Planar .....                                     | 202 |

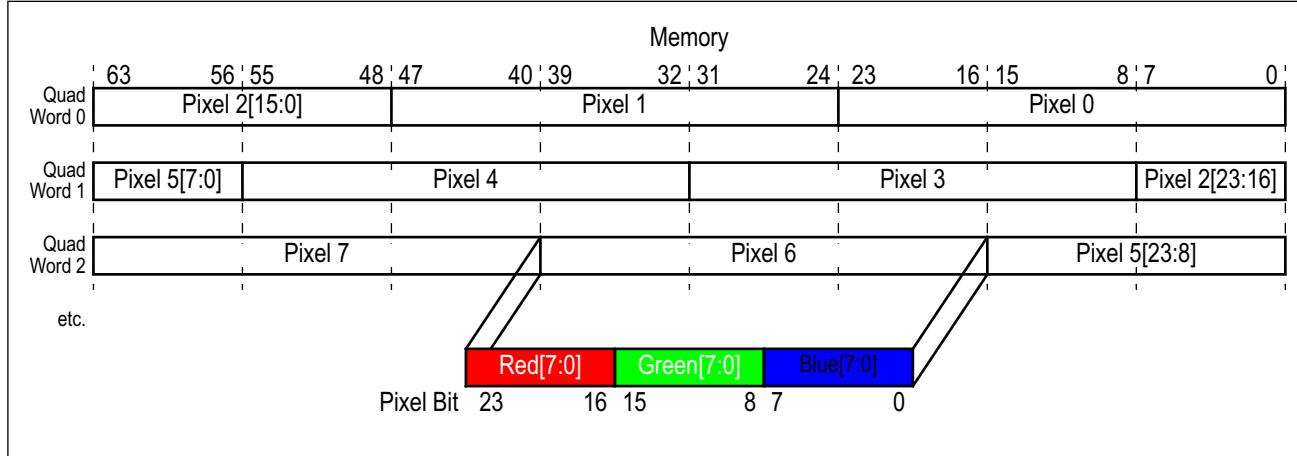

| 8-8-8 Truecolor, Packed .....                                     | 202 |

| Border Color Controls .....                                       | 203 |

| <b>Cursor Data Path</b> .....                                     | 204 |

| Cursor Modes .....                                                | 204 |

| Cursor Positioning .....                                          | 205 |

| <b>Video Data Path</b> .....                                      | 206 |

| Video Control Register .....                                      | 206 |

| 4:2:2 Video Format .....                                          | 208 |

| Color Key Using Graphics Source .....                             | 208 |

| Chroma Key Using Video Source .....                               | 209 |

| Display Priority .....                                            | 209 |

| YC <sub>r</sub> C <sub>b</sub> Luma Correction .....              | 210 |

| YC <sub>r</sub> C <sub>b</sub> /RGB Color Space Conversions ..... | 210 |

| Source Count .....                                                | 211 |

| Horizontal Upscaling .....                                        | 212 |

| Vertical Upscaling .....                                          | 212 |

| Upscale Initial and Increment Computation .....                   | 213 |

| Vertical Upscaling Interlaced Format Considerations .....         | 214 |

|                                                                      |            |

|----------------------------------------------------------------------|------------|

| 5-5-5 True Color Video Format . . . . .                              | 214        |

| 5-6-5 True Color Video Format . . . . .                              | 214        |

| 24-Bit True Color Video Format . . . . .                             | 215        |

| Video Start Buffer and Vertical Upscale Initial Management . . . . . | 216        |

| <b>    Sharpness Control Function . . . . .</b>                      | <b>217</b> |

| <b>    Signature Analysis Register . . . . .</b>                     | <b>218</b> |

| <b>    DREF Timing Diagrams . . . . .</b>                            | <b>219</b> |

| <br><b>3D Graphics Accelerator . . . . .</b>                         | <b>221</b> |

| <b>3D Interface . . . . .</b>                                        | <b>221</b> |

| 3D Core Interface Registers . . . . .                                | 221        |

| <i>register name: 3D_CORE</i>                                        |            |

| 3D Interface Auxiliary Registers . . . . .                           | 222        |

| <i>register name: 3D_AUX</i>                                         |            |

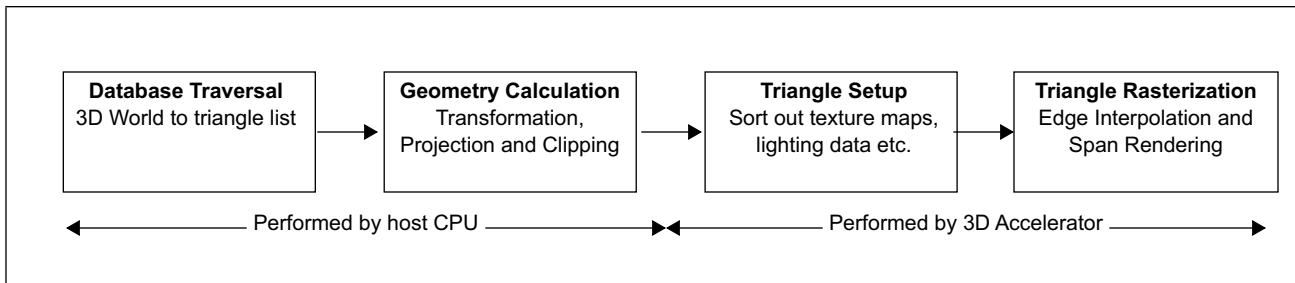

| <b>3D Graphics Pipeline . . . . .</b>                                | <b>223</b> |

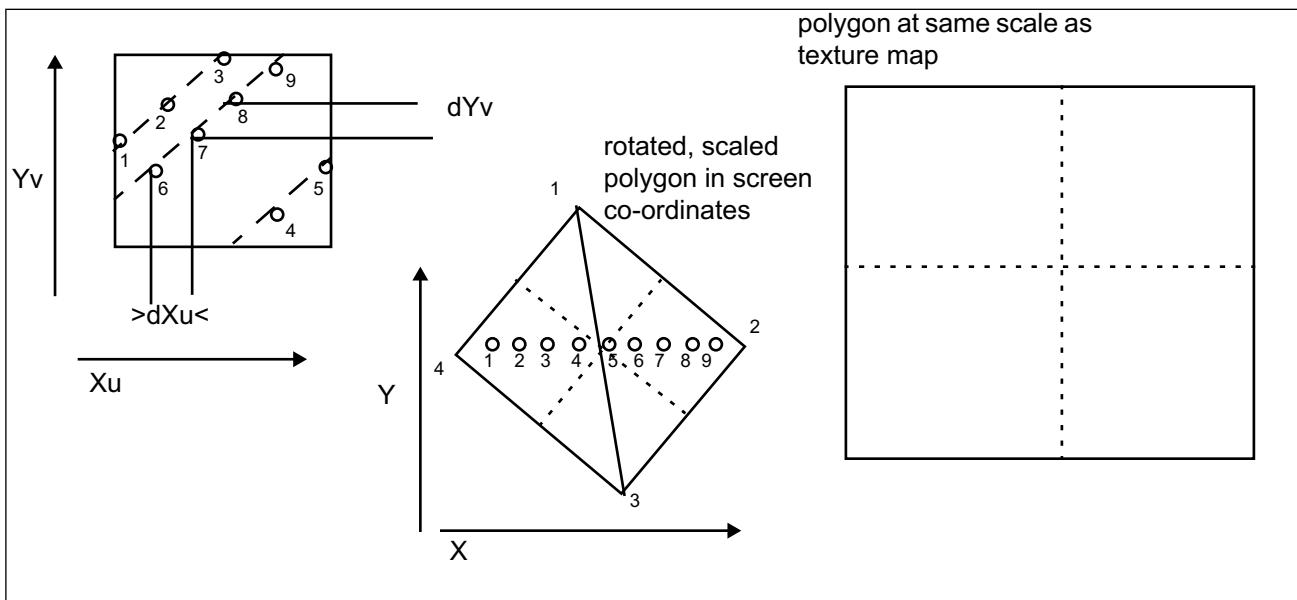

| Database Traversal . . . . .                                         | 223        |

| Geometry Calculation . . . . .                                       | 223        |

| Triangle Material and Lighting Set-up . . . . .                      | 223        |

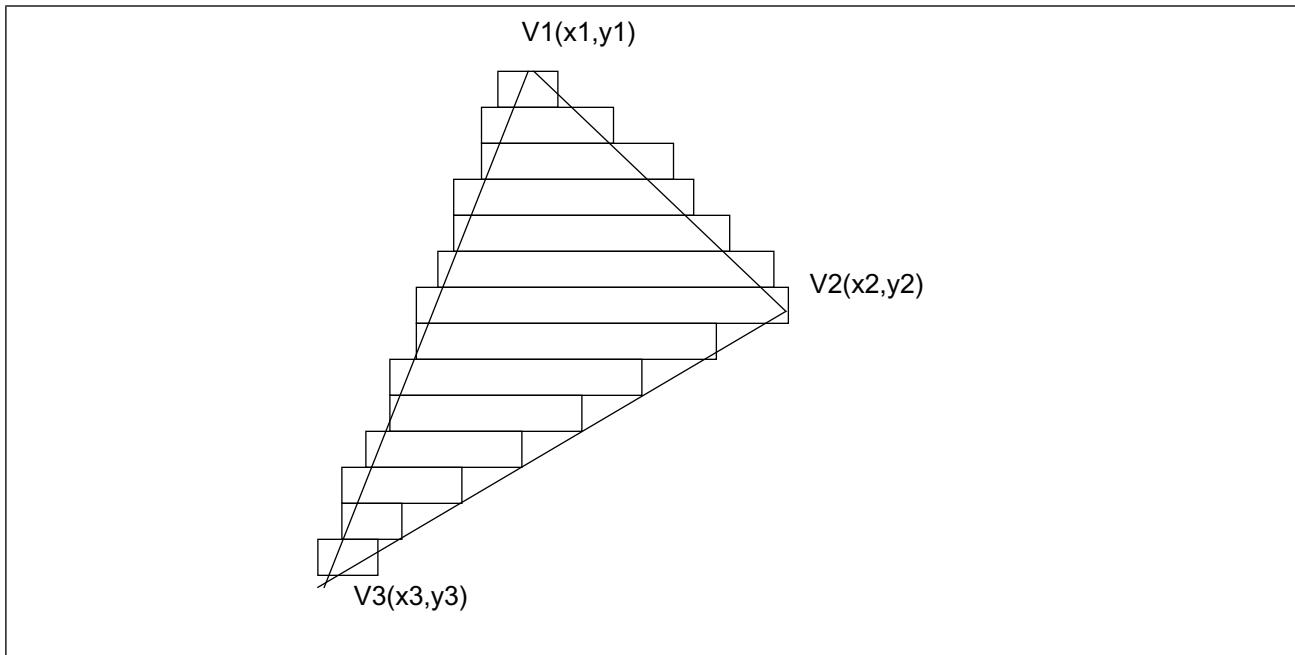

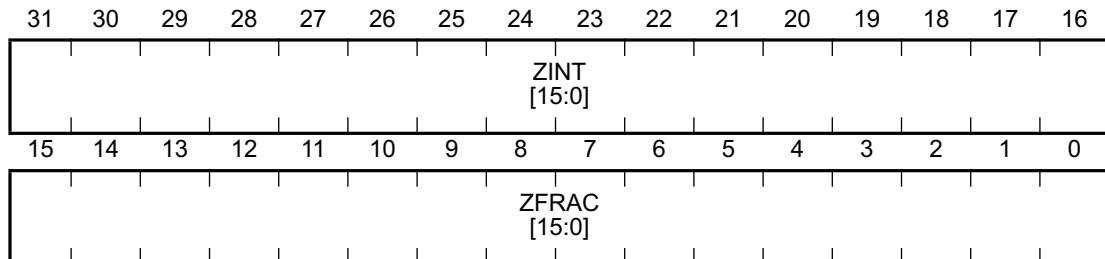

| Triangle Rasterization . . . . .                                     | 224        |

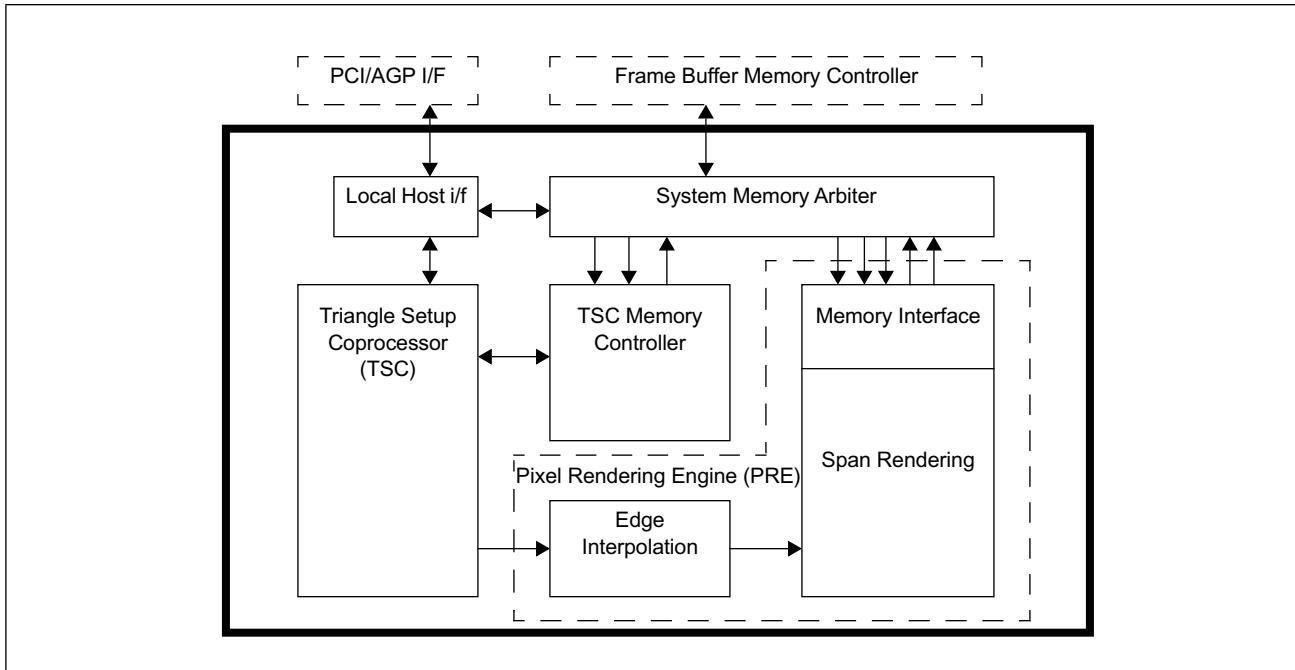

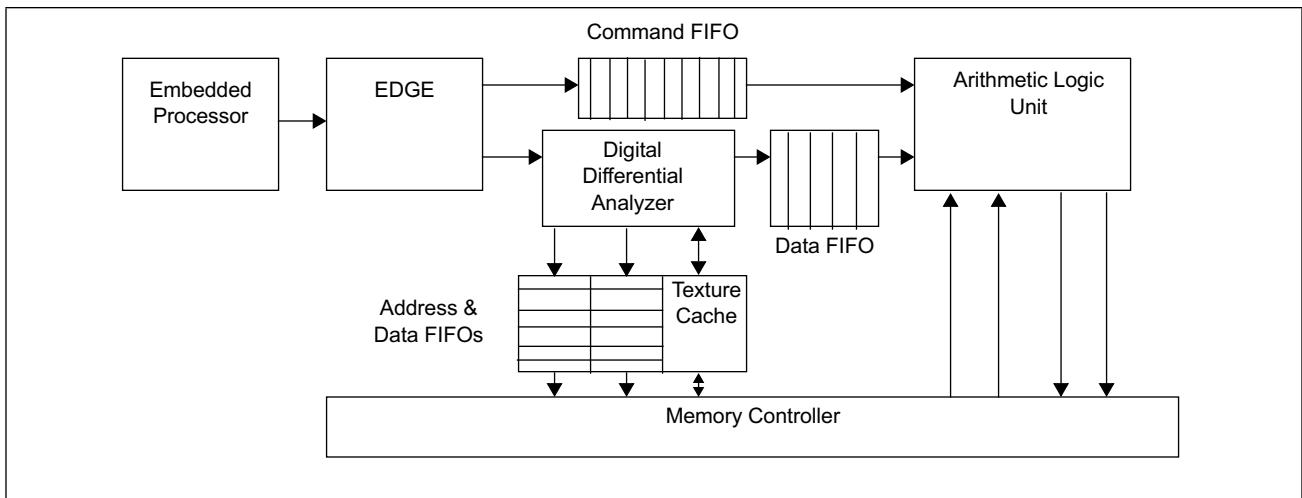

| 3D Graphics Accelerator . . . . .                                    | 226        |

| <b>Pixel Rendering Engine . . . . .</b>                              | <b>227</b> |

| PRE Key Features . . . . .                                           | 227        |

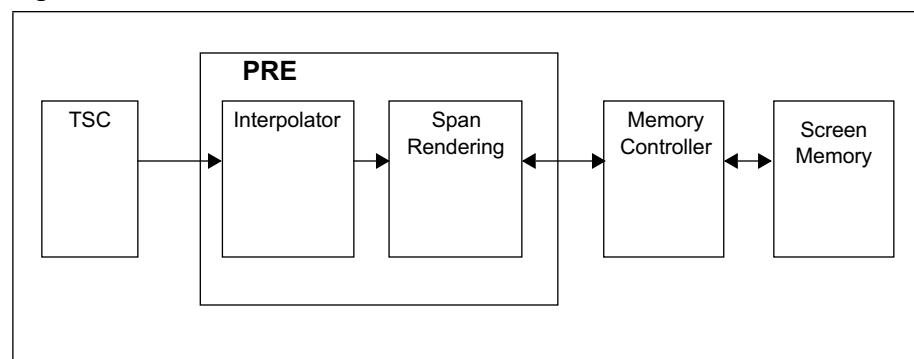

| Basic Architecture . . . . .                                         | 228        |

| Supported Algorithms . . . . .                                       | 228        |

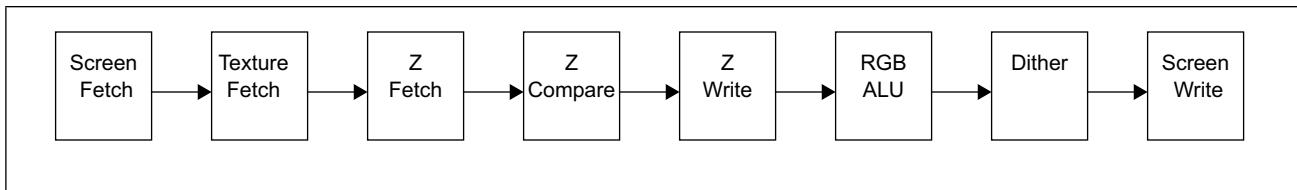

| <b>PRE Data Flow Pipeline . . . . .</b>                              | <b>230</b> |

| Screen Fetch . . . . .                                               | 230        |

| Texture Fetch . . . . .                                              | 230        |

| Z Fetch . . . . .                                                    | 230        |

| Z Compare . . . . .                                                  | 230        |

| Z Write . . . . .                                                    | 230        |

| Color RGB ALU . . . . .                                              | 230        |

| Dither . . . . .                                                     | 230        |

| Screen Write . . . . .                                               | 230        |

| <b>PRE Programming Model . . . . .</b>                               | <b>231</b> |

| FIFO Update of Registers . . . . .                                   | 232        |

| The Register Set . . . . .                                           | 232        |

| Synchronization with the TSC . . . . .                               | 232        |

|                                                       |     |

|-------------------------------------------------------|-----|

| <b>Memory Access</b> . . . . .                        | 233 |

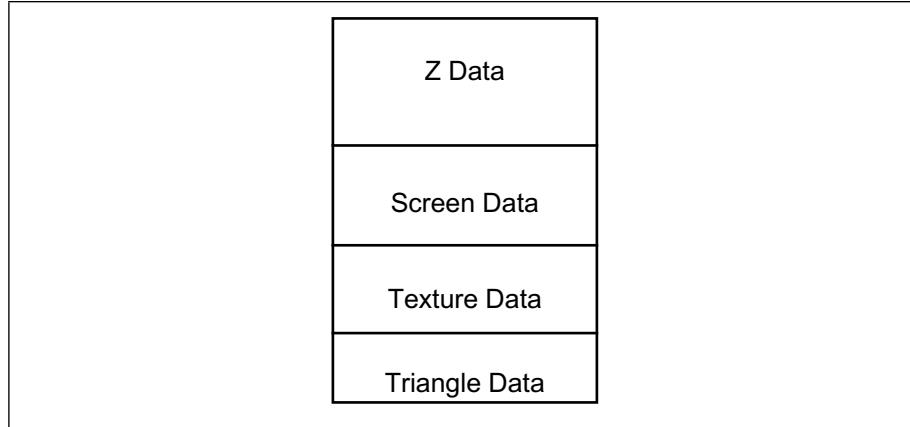

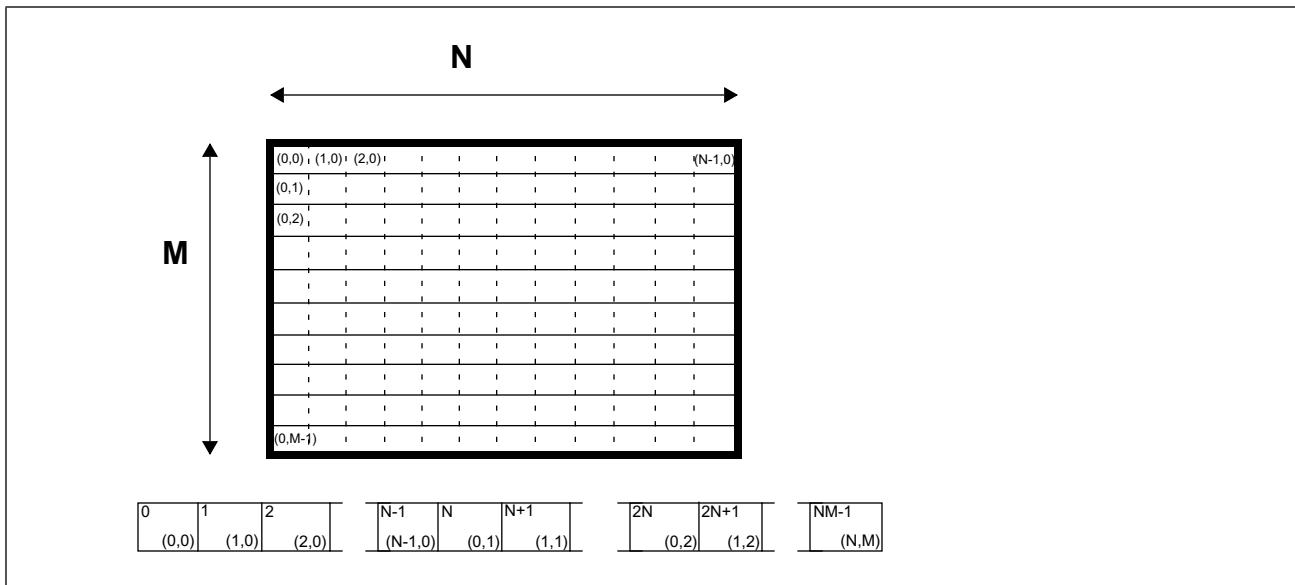

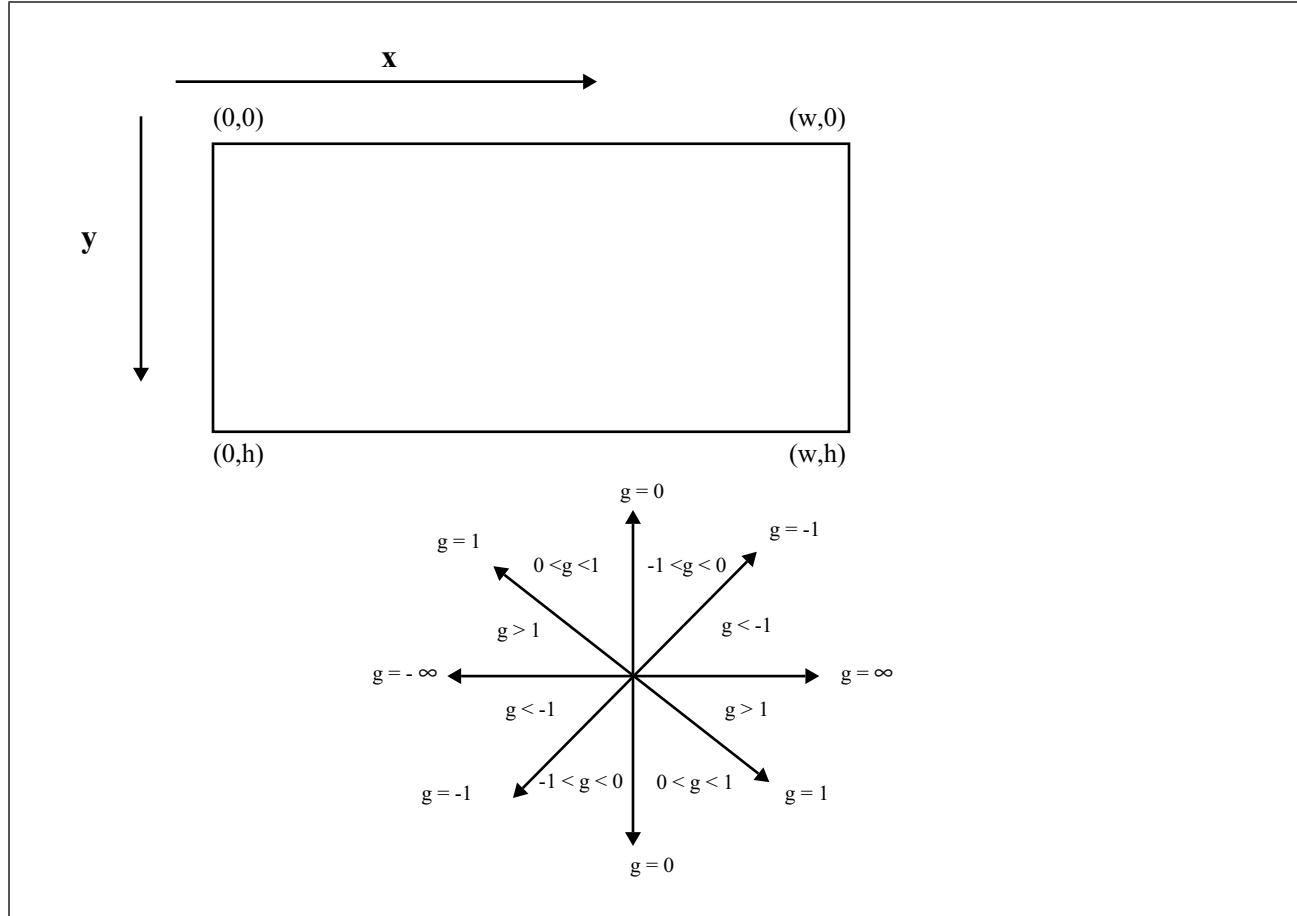

| Data Organization and Addressing . . . . .            | 233 |

| Screen Buffer . . . . .                               | 233 |

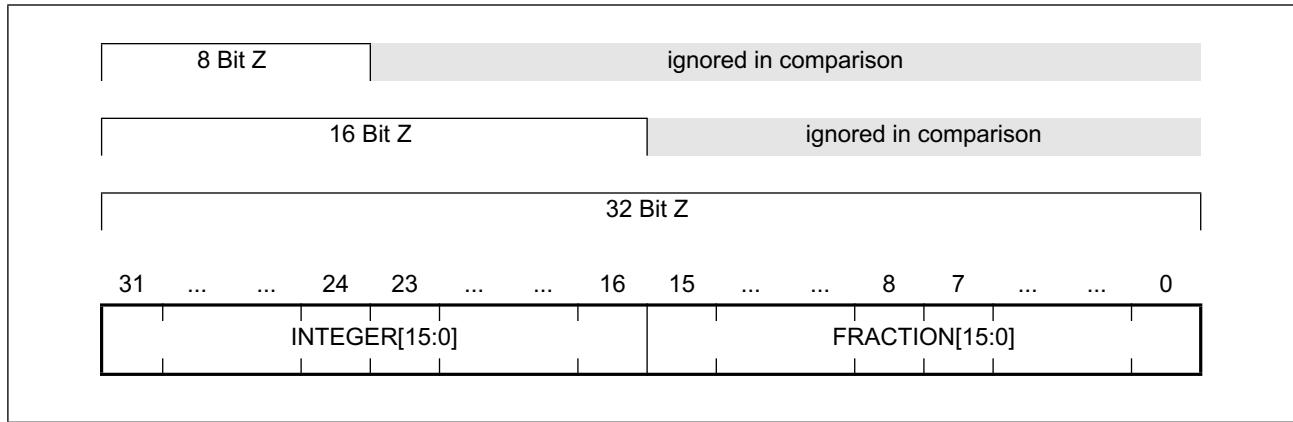

| Z Data Buffer . . . . .                               | 236 |

| Texture Data Buffer . . . . .                         | 236 |

| Polygon Data . . . . .                                | 240 |

| Example Memory Map . . . . .                          | 240 |

| PRE Memory Controller Interface . . . . .             | 240 |

| <b>Register Table</b> . . . . .                       | 242 |

| <b>Register Set Details</b> . . . . .                 | 245 |

| <b>PRE 3D Registers</b> . . . . .                     | 246 |

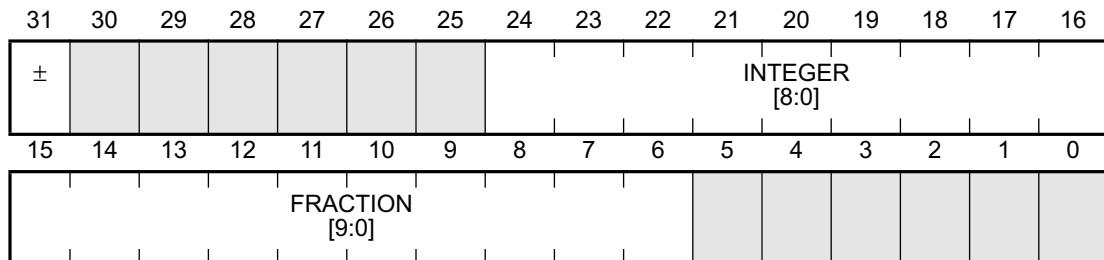

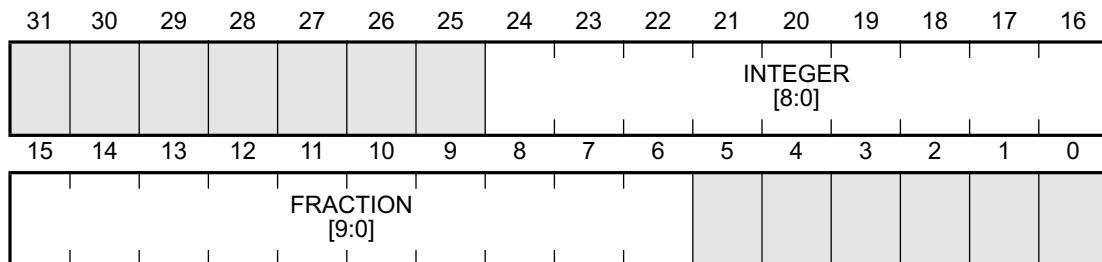

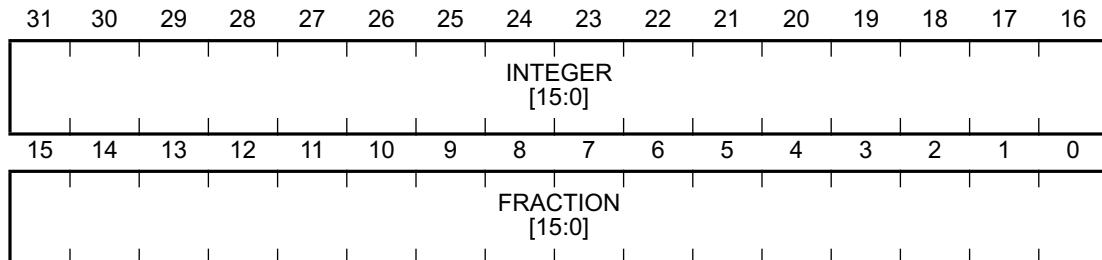

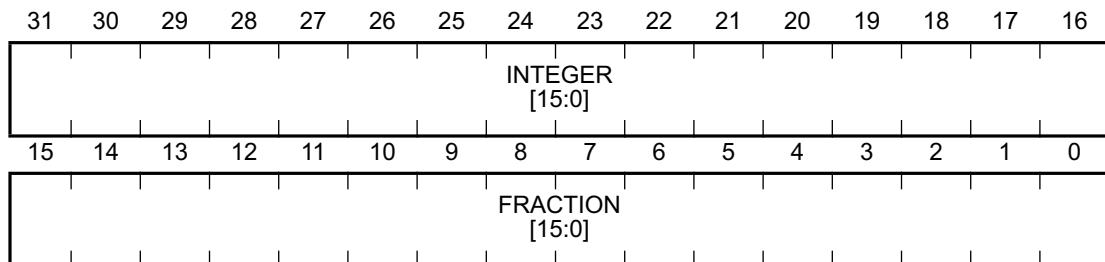

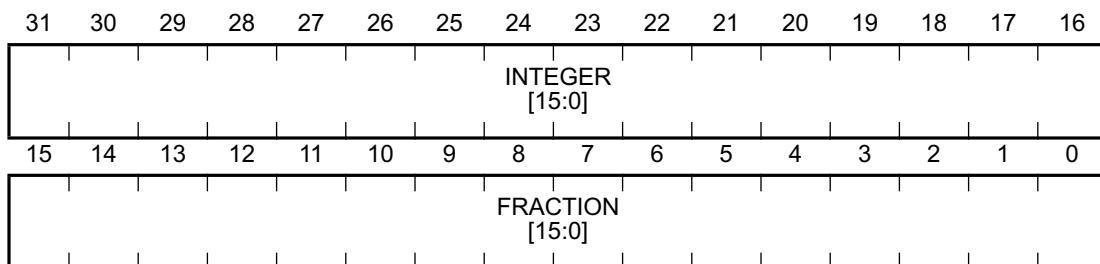

| Intensity Pixel Increment Register . . . . .          | 246 |

| <i>register name: A_DX</i>                            |     |

| Intensity Span Increment Register . . . . .           | 247 |

| <i>register name: A_DY</i>                            |     |

| Intensity Register . . . . .                          | 248 |

| <i>register name: AVAL</i>                            |     |

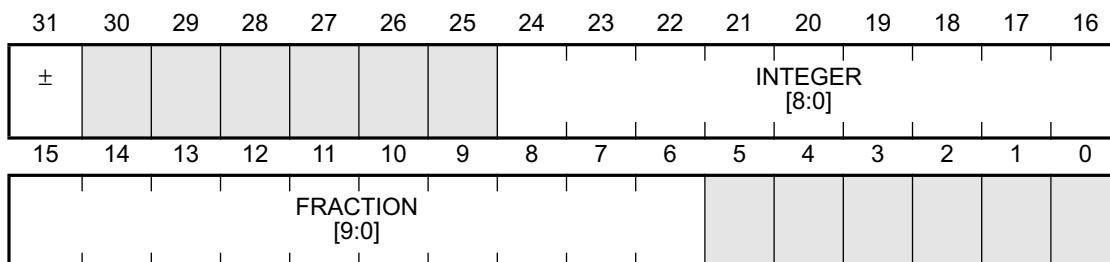

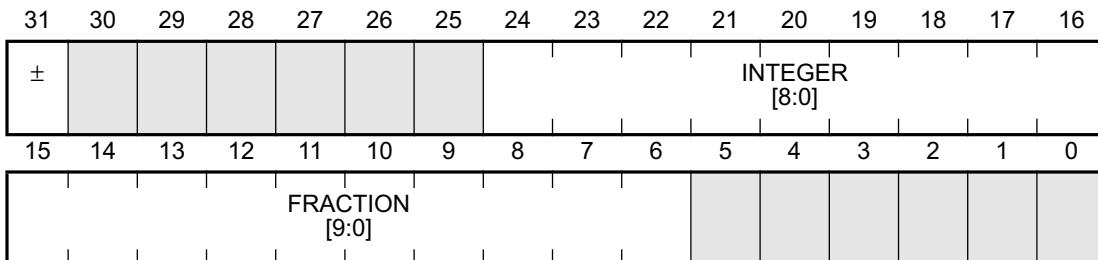

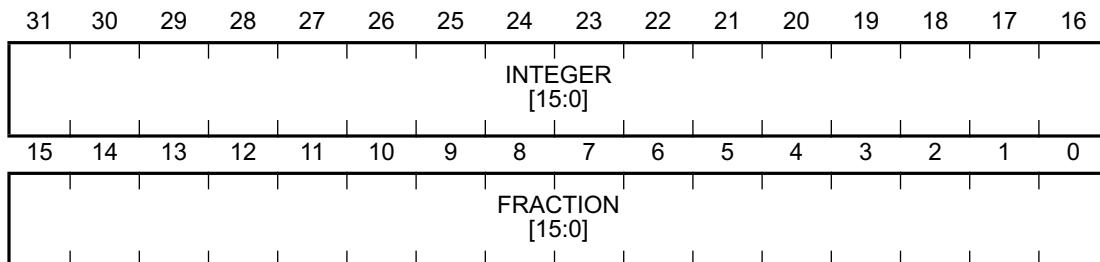

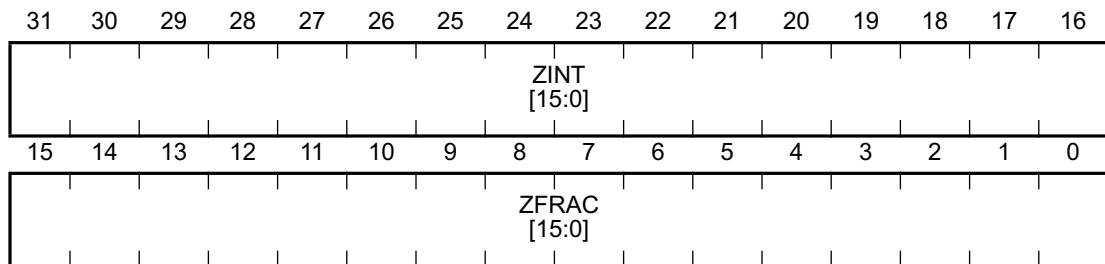

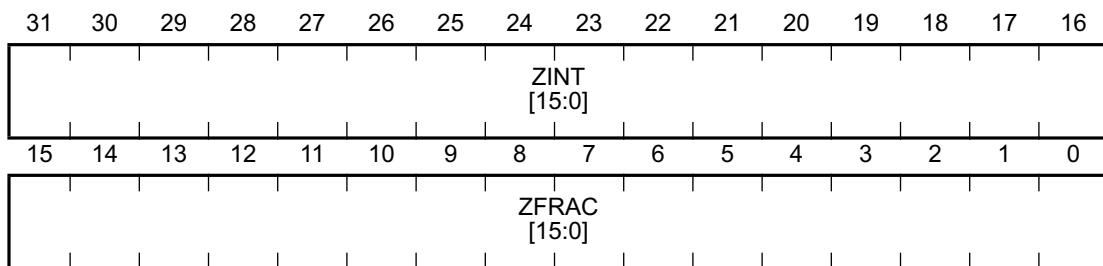

| Blue Light-source Pixel Increment Register . . . . .  | 249 |

| <i>register name: B_DX</i>                            |     |

| Blue Light-source Span Increment Register . . . . .   | 250 |

| <i>register name: B_DY</i>                            |     |

| Blue Light Source Component Register . . . . .        | 251 |

| <i>register name: BALF</i>                            |     |

| Fixed Background Colour Register . . . . .            | 252 |

| <i>register name: FIXC</i>                            |     |

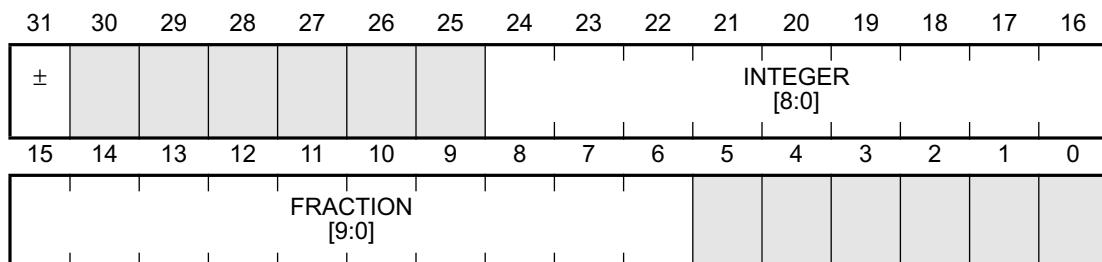

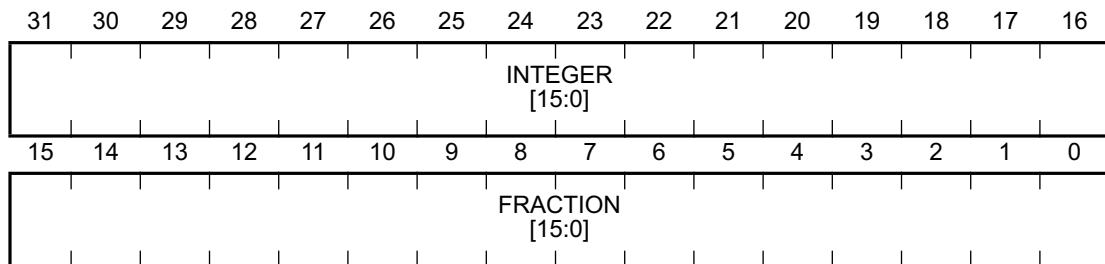

| Green Light-source Pixel Increment Register . . . . . | 253 |

| <i>register name: G_DX</i>                            |     |

| Green Light-source Span Increment Register . . . . .  | 254 |

| <i>register name: G_DY</i>                            |     |

| Green Light Source Component Register . . . . .       | 255 |

| <i>register name: GALF</i>                            |     |

| Screen Source Address Register . . . . .              | 256 |

| <i>register name: IBASE</i>                           |     |

| Invalidate Texture Cache Register . . . . .           | 257 |

| <i>register name: IVTC</i>                            |     |

| Look-up Write Register . . . . .                      | 258 |

| <i>register name: LKUP</i>                            |     |

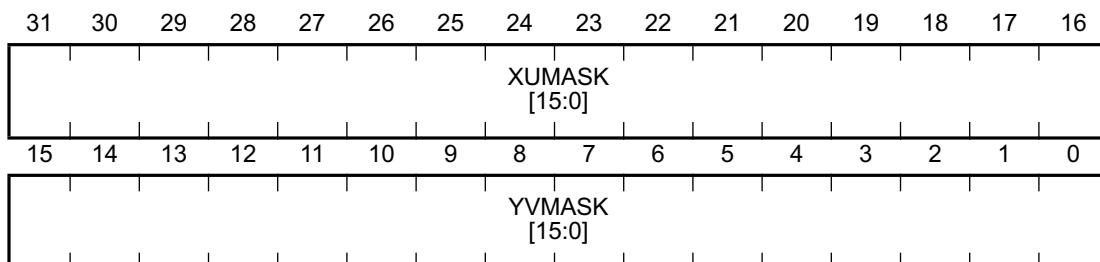

| Xu and Yv Mask Register . . . . .                     | 259 |

| <i>register name: MASK</i>                            |     |

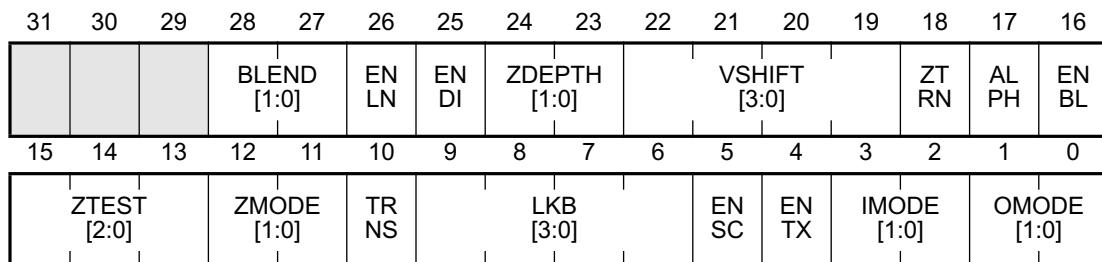

| Mode Register . . . . .                               | 260 |

| <i>register name: MODE</i>                            |     |

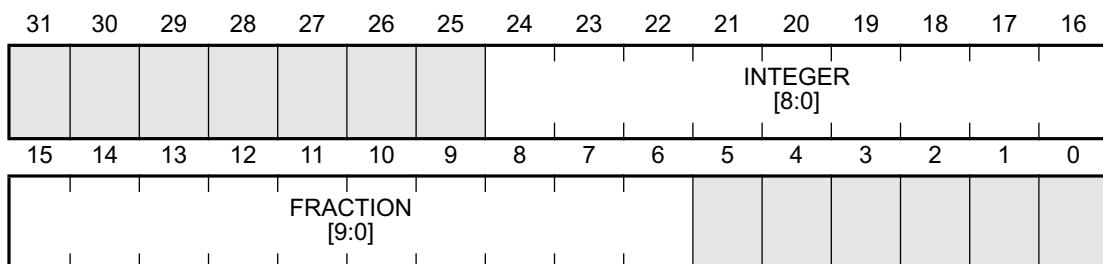

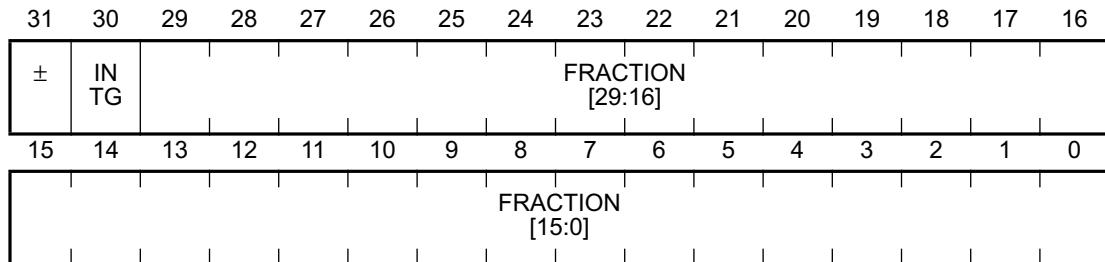

| Homogenous Q Pixel Increment Register . . . . .       | 262 |

| <i>register name: Q_DX</i>                            |     |

|                                                     |     |

|-----------------------------------------------------|-----|

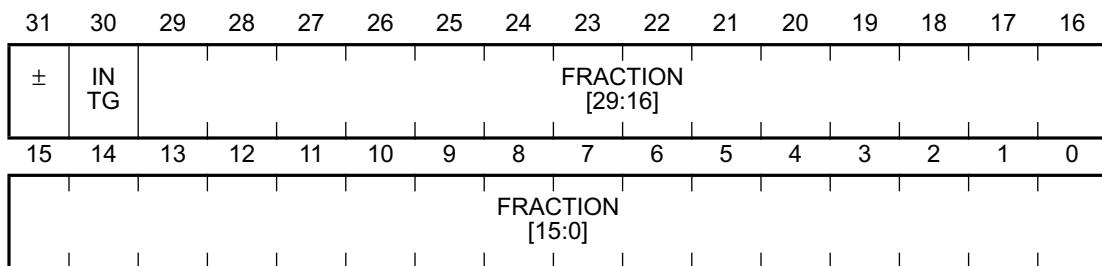

| Homogenous Q Span Increment Register . . . . .      | 263 |

| <i>register name: Q_DY</i>                          |     |

| Homogenous Coordinate Register . . . . .            | 264 |

| <i>register name: QVAL</i>                          |     |

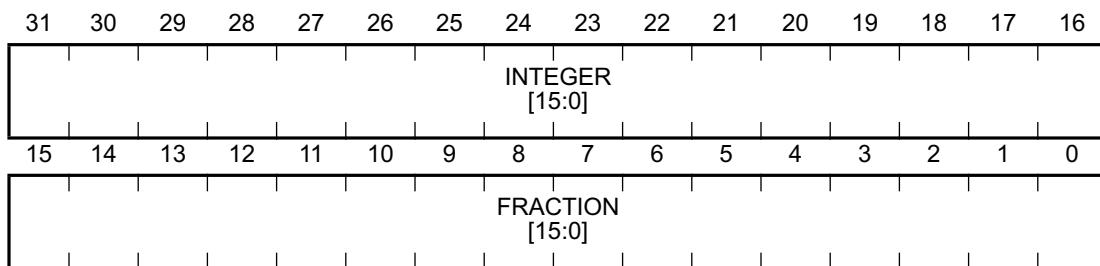

| Red Light-source Pixel Increment Register . . . . . | 265 |

| <i>register name: R_DX</i>                          |     |

| Red Light-source Span Increment Register. . . . .   | 266 |

| <i>register name: R_DY</i>                          |     |

| Red Light Source Component Register. . . . .        | 267 |

| <i>register name: RALF</i>                          |     |

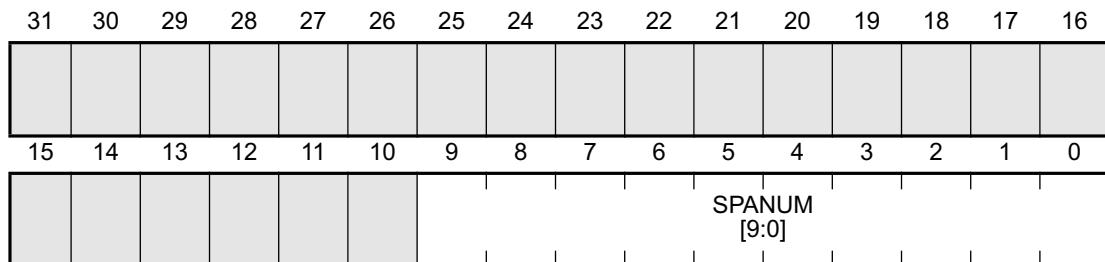

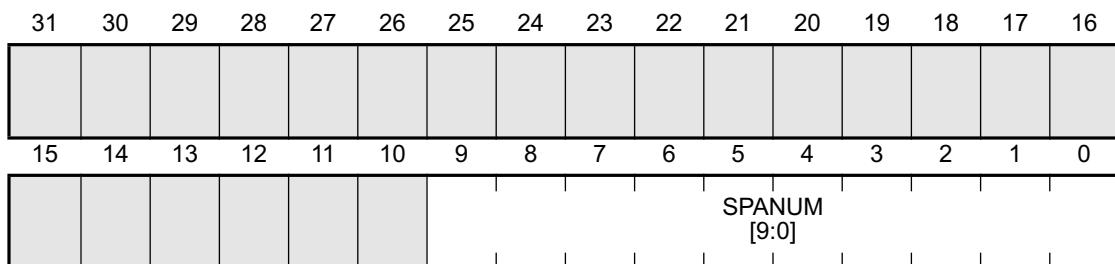

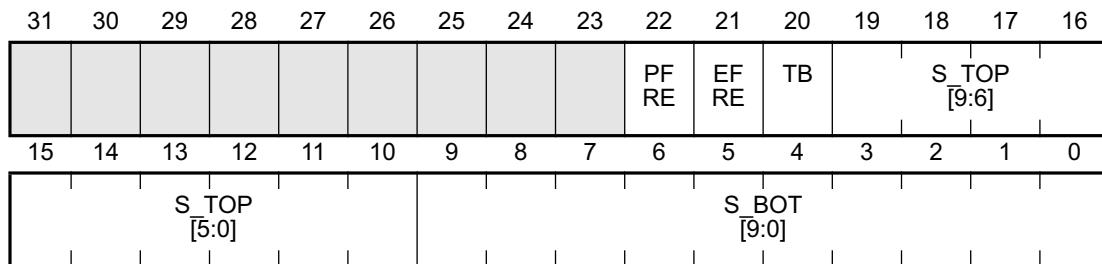

| Spans in Bottom Triangle Register. . . . .          | 268 |

| <i>register name: S_BOT</i>                         |     |

| Spans in Top Triangle Register . . . . .            | 269 |

| <i>register name: S_TOP</i>                         |     |

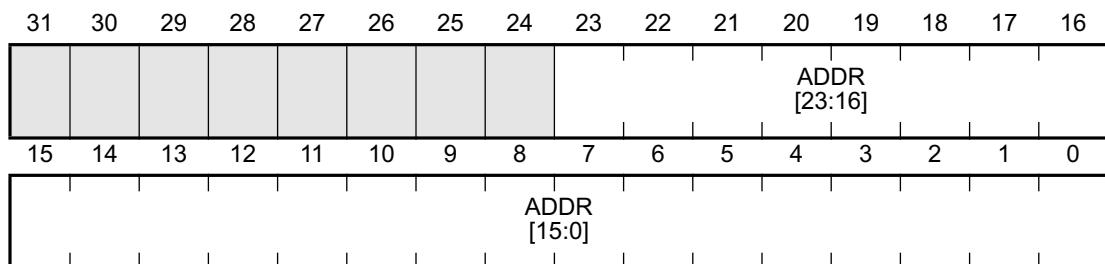

| Screen Output Address Register. . . . .             | 270 |

| <i>register name: SBASE</i>                         |     |

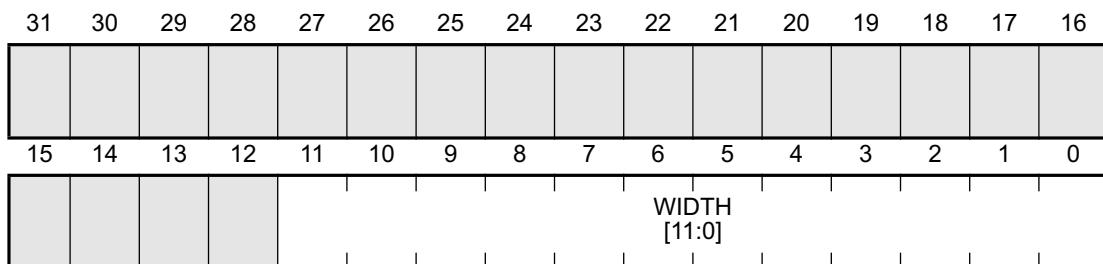

| Screen Width in Pixels Register. . . . .            | 271 |

| <i>register name: SCRW</i>                          |     |

| Status Register . . . . .                           | 272 |

| <i>register name: STATUS</i>                        |     |

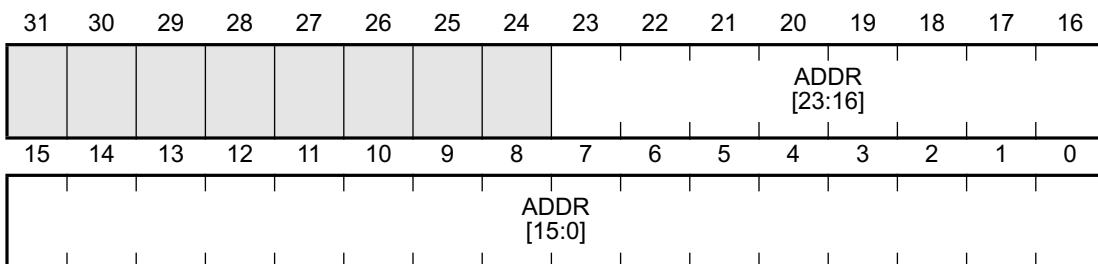

| Texture Base Address Register . . . . .             | 273 |

| <i>register name: TBASE</i>                         |     |

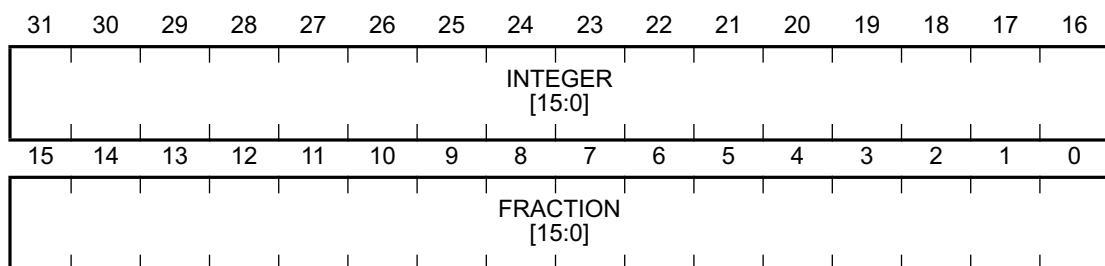

| Xu Pixel Increment Register . . . . .               | 274 |

| <i>register name: U_DX</i>                          |     |

| Xu Span Increment Register . . . . .                | 275 |

| <i>register name: U_DY</i>                          |     |

| Texture Source Xu Register. . . . .                 | 276 |

| <i>register name: UVAL</i>                          |     |

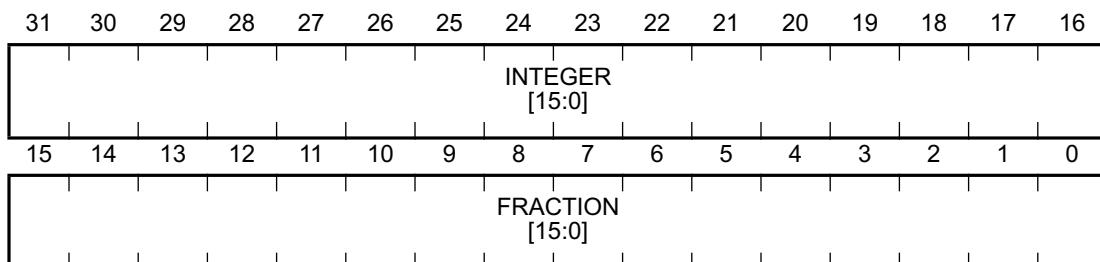

| Yv Pixel Increment Register . . . . .               | 277 |

| <i>register name: V_DX</i>                          |     |

| Yv Span Increment Register . . . . .                | 278 |

| <i>register name: V_DY</i>                          |     |

| Texture Source Yv Register . . . . .                | 279 |

| <i>register name: VVAL</i>                          |     |

| X End Span Increment Register . . . . .             | 280 |

| <i>register name: XB_DY</i>                         |     |

| X End Coordinate/Bottom Register . . . . .          | 281 |

| <i>register name: XENDB</i>                         |     |

| X End Coordinate/Top Register . . . . .             | 282 |

| <i>register name: XENDT</i>                         |     |

| X Start Span Increment Register. . . . .            | 283 |

| <i>register name: XS_DY</i>                         |     |

| X Start Coordinate Register. . . . .                | 284 |

| <i>register name: XSTART</i>                        |     |

| X End Span Increment/Top Register . . . . .         | 285 |

| <i>register name: XT_DY</i>                         |     |

|                                                   |     |

|---------------------------------------------------|-----|

| Z Value Pixel Increment Register . . . . .        | 286 |

| <i>register name: Z_DX</i>                        |     |

| Z Value Span Increment Register . . . . .         | 287 |

| <i>register name: Z_DY</i>                        |     |

| Z Buffer Base Address Register . . . . .          | 288 |

| <i>register name: ZBASE</i>                       |     |

| Current Z Value Register . . . . .                | 289 |

| <i>register name: ZVAL</i>                        |     |

| <b>PRE Programming</b> . . . . .                  | 291 |

| Initialization and Default Value Set-up . . . . . | 291 |

| Starting . . . . .                                | 291 |

| Pixel Output . . . . .                            | 291 |

| Register Grouping . . . . .                       | 292 |

| Typical Rendering Shapes . . . . .                | 294 |

| <b>PRE Programming Examples</b> . . . . .         | 295 |

| Flat Shading . . . . .                            | 295 |

| Z Buffering . . . . .                             | 296 |

| Gouraud Shading . . . . .                         | 297 |

| Dithering . . . . .                               | 298 |

| Translucency . . . . .                            | 299 |

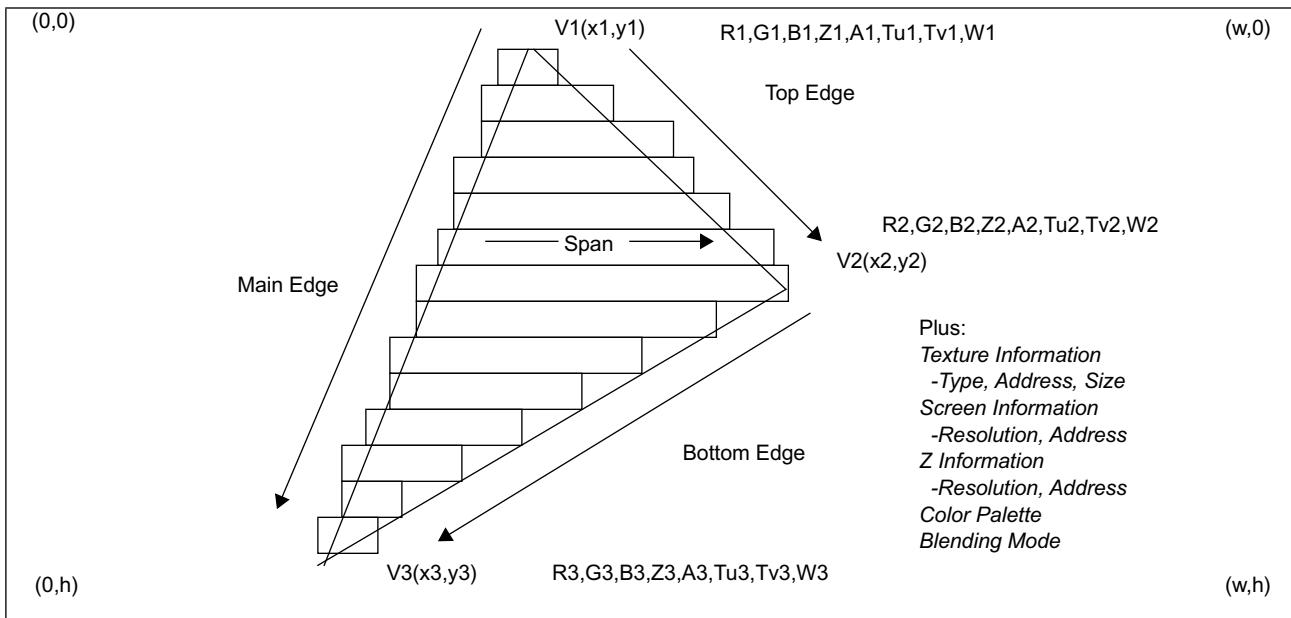

| Texture Mapping . . . . .                         | 300 |

| Control of Texture Mapping . . . . .              | 301 |

| Texture Compression . . . . .                     | 303 |

| Texture with Perspective Correction . . . . .     | 304 |

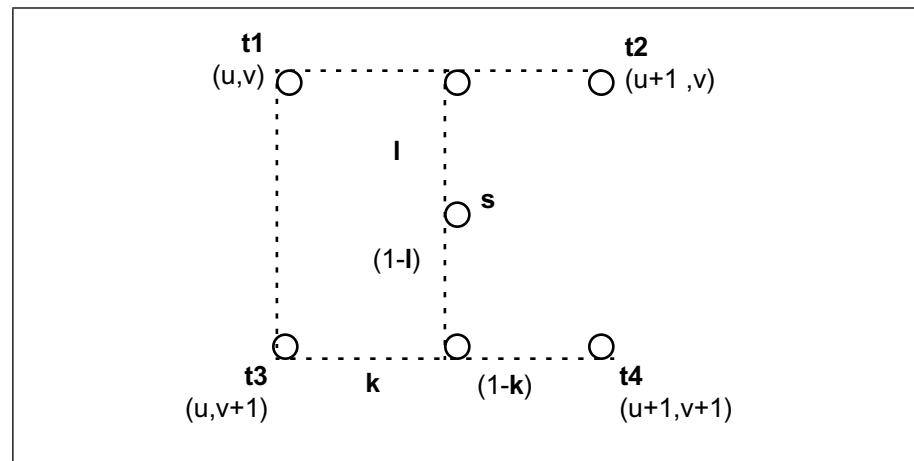

| Bilinear Interpolation . . . . .                  | 306 |

| Texture Transparency . . . . .                    | 307 |

| Texture Translucency . . . . .                    | 308 |

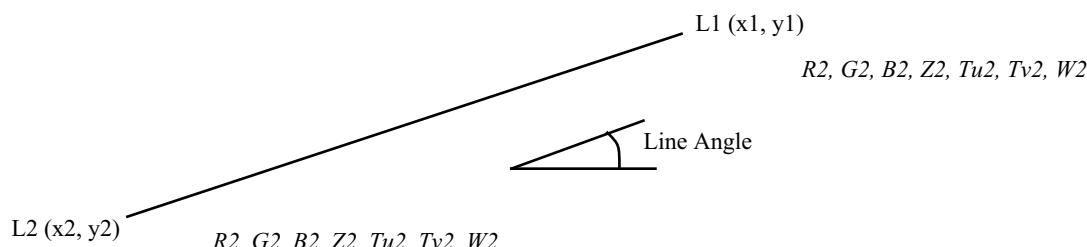

| Line Drawing . . . . .                            | 308 |

| Work Out Gradient, dx/dy . . . . .                | 309 |

| Parameter Values . . . . .                        | 309 |

| <b>Supplemental Information</b> . . . . .         | 311 |

| Terms . . . . .                                   | 311 |

| Parameter Nomenclature . . . . .                  | 312 |

| Gradient Nomenclature in PRE . . . . .            | 314 |

|                                                              |     |

|--------------------------------------------------------------|-----|

| <b>PCI Configuration Space Register Definitions</b> .....    | 315 |

| <b>PCI Configuration Space</b> .....                         | 315 |

| PCI Vendor ID Register .....                                 | 316 |

| <i>register name: PCI_VENDOR_ID</i>                          |     |

| PCI Device ID Registers .....                                | 317 |

| <i>register name: PCI_DEVICE_ID0, PCI_DEVICE_ID1</i>         |     |

| PCI Command Registers .....                                  | 317 |

| <i>register name: PCI_COMMAND0, PCI_COMMAND1</i>             |     |

| PCI Status Registers .....                                   | 319 |

| <i>register name: PCI_STATUS</i>                             |     |

| PCI Revision ID Register .....                               | 319 |

| <i>register name: PCI_REVISION_ID</i>                        |     |

| PCI Class Code Registers .....                               | 320 |

| <i>register name: PCI_CLASS0_ID, PCI_CLASS1_ID</i>           |     |

| PCI Cache Line Size .....                                    | 320 |

| <i>register name: PCI_CACHE_SZ</i>                           |     |

| PCI Latency Timer .....                                      | 320 |

| <i>register name: PCI_LATENCY_TIMER0, PCI_LATENCY_TIMER1</i> |     |

| PCI Header Type .....                                        | 321 |

| <i>register name: PCI_HEADER_TYPE</i>                        |     |

| PCI BIST .....                                               | 321 |

| <i>register name: PCI_BIST</i>                               |     |

| PCI Base Address Register Zero .....                         | 321 |

| <i>register name: PCI_BASE0</i>                              |     |

| PCI Base Address Register 1 .....                            | 322 |

| <i>register name: PCI_BASE1</i>                              |     |

| PCI Subsystem Vendor ID .....                                | 322 |

| <i>register name: PCI_SUBSYS_VENDOR_ID</i>                   |     |

| PCI Subsystem ID .....                                       | 323 |

| <i>register name: PCI_SUBSYS_ID</i>                          |     |

| PCI ROM Base Address Register .....                          | 323 |

| <i>register name: PCI_ROM_BASE</i>                           |     |

| PCI Interrupt Line Register .....                            | 323 |

| <i>register name: PCI_INT_LINE0, PCI_INT_LINE1</i>           |     |

| PCI Interrupt Pin Register .....                             | 323 |

| <i>register name: PCI_INT_PIN0, PCI_INT_PIN1</i>             |     |

| PCI Subsystem ID Write Register .....                        | 324 |

| <i>register name: PCI_SUBSYSID_WR</i>                        |     |

| PCI Subsystem ID Mode Register .....                         | 324 |

| <i>register name: PCI_SUBSYSID_MODE</i>                      |     |

|                                                                        |     |

|------------------------------------------------------------------------|-----|

| <b>CPU Host Bus Interface</b> . . . . .                                | 325 |

| <b>PCI/AGP Local Bus Interface</b> . . . . .                           | 325 |

| PCI/AGP Functionality . . . . .                                        | 326 |

| PCI Address and Data Bus . . . . .                                     | 326 |

| PCI Bus Command and Byte Enables . . . . .                             | 326 |

| PCI Parity . . . . .                                                   | 326 |

| PCI Clock . . . . .                                                    | 326 |

| PCI Reset . . . . .                                                    | 326 |

| PCI Cycle Frame . . . . .                                              | 326 |

| PCI Initiator Ready . . . . .                                          | 327 |

| PCI Target Ready . . . . .                                             | 327 |

| PCI Stop . . . . .                                                     | 327 |

| PCI Initialization Device Select . . . . .                             | 327 |

| PCI Device Select . . . . .                                            | 327 |

| PCI Interrupt A . . . . .                                              | 327 |

| PCI Master Request . . . . .                                           | 327 |

| PCI Master Grant . . . . .                                             | 327 |

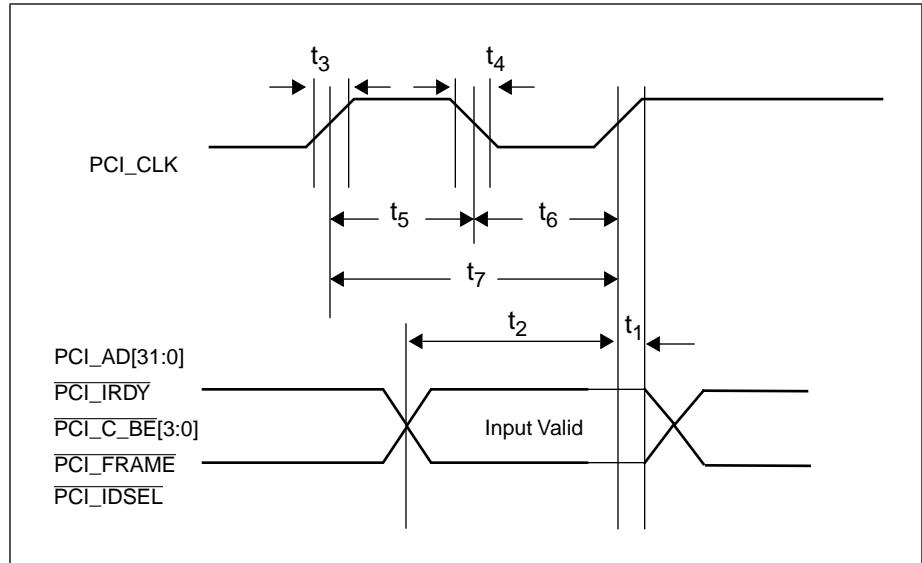

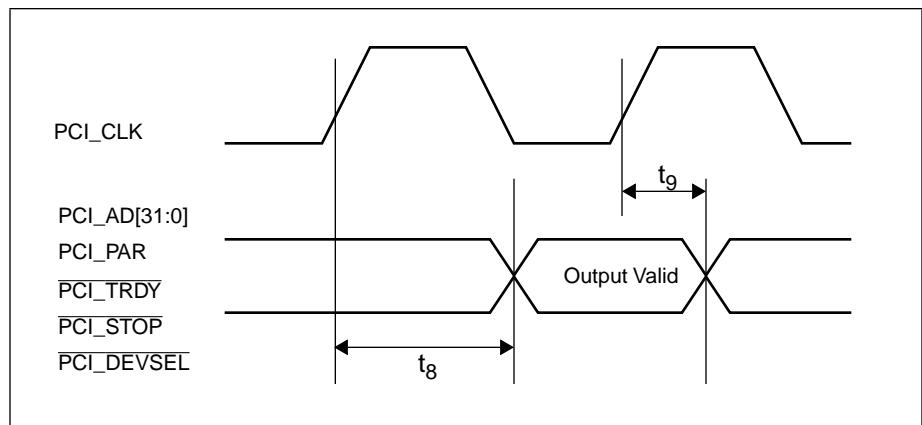

| <b>PCI/AGP Bus Timing</b> . . . . .                                    | 328 |

| <b>Synchronous Memory Interface</b> . . . . .                          | 331 |

| <b>Overview</b> . . . . .                                              | 331 |

| Memory-Related Pin Descriptions . . . . .                              | 333 |

| <b>External Configuration/Memory Configuration Resistors</b> . . . . . | 334 |

| <b>Internal Configuration</b> . . . . .                                | 337 |

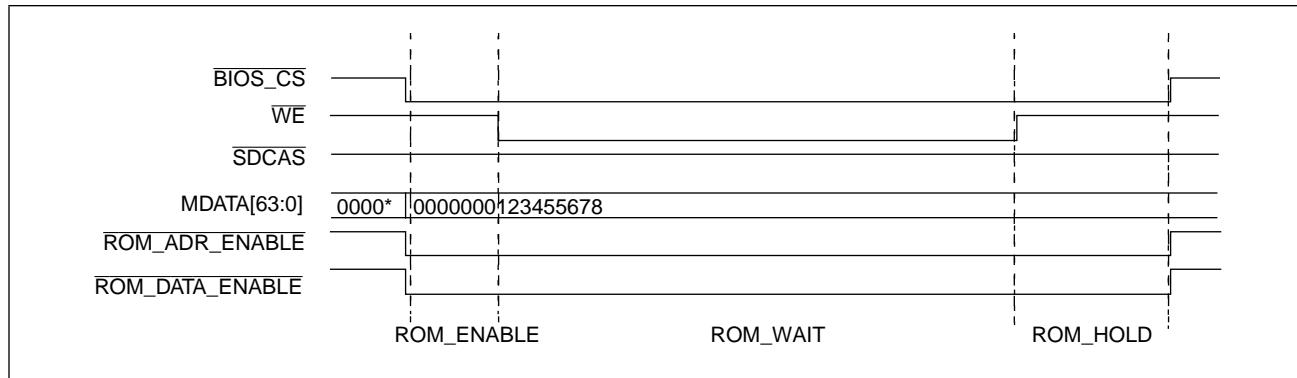

| <b>ROM Interface</b> . . . . .                                         | 338 |

| <b>Memory Map Information</b> . . . . .                                | 340 |

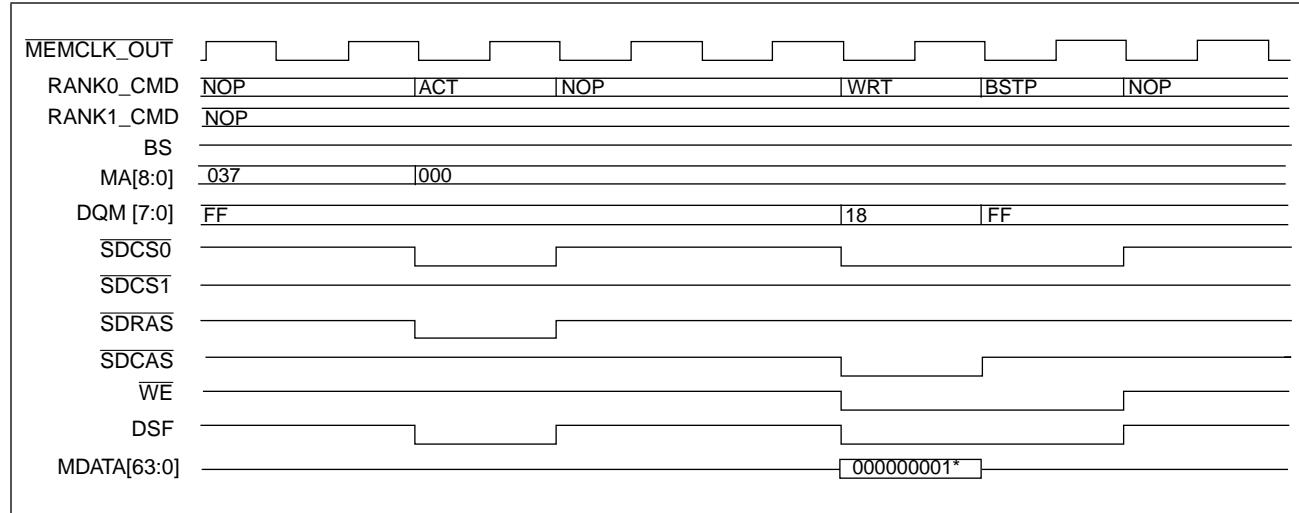

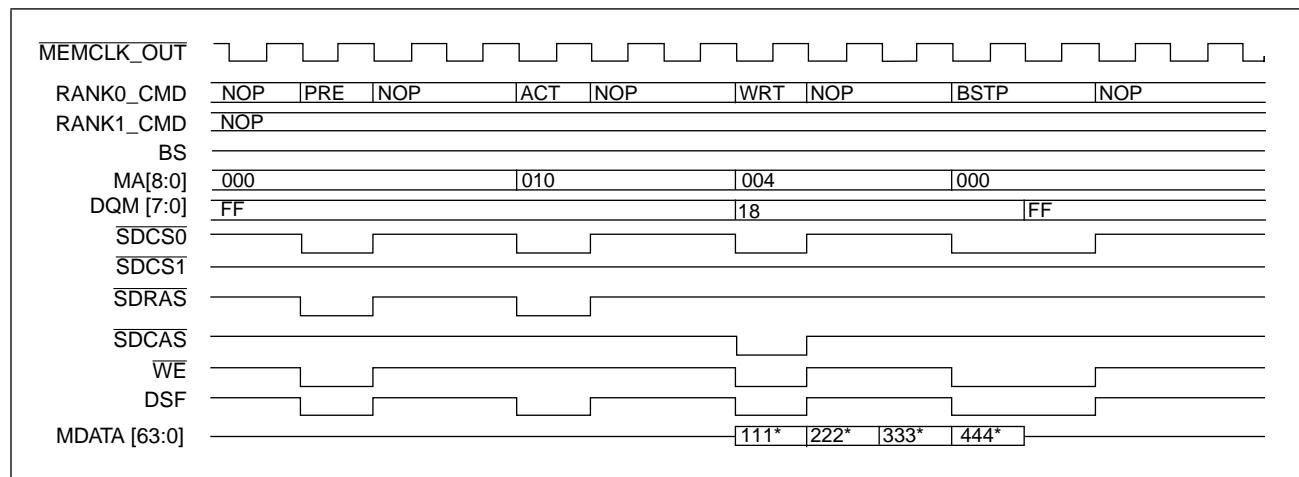

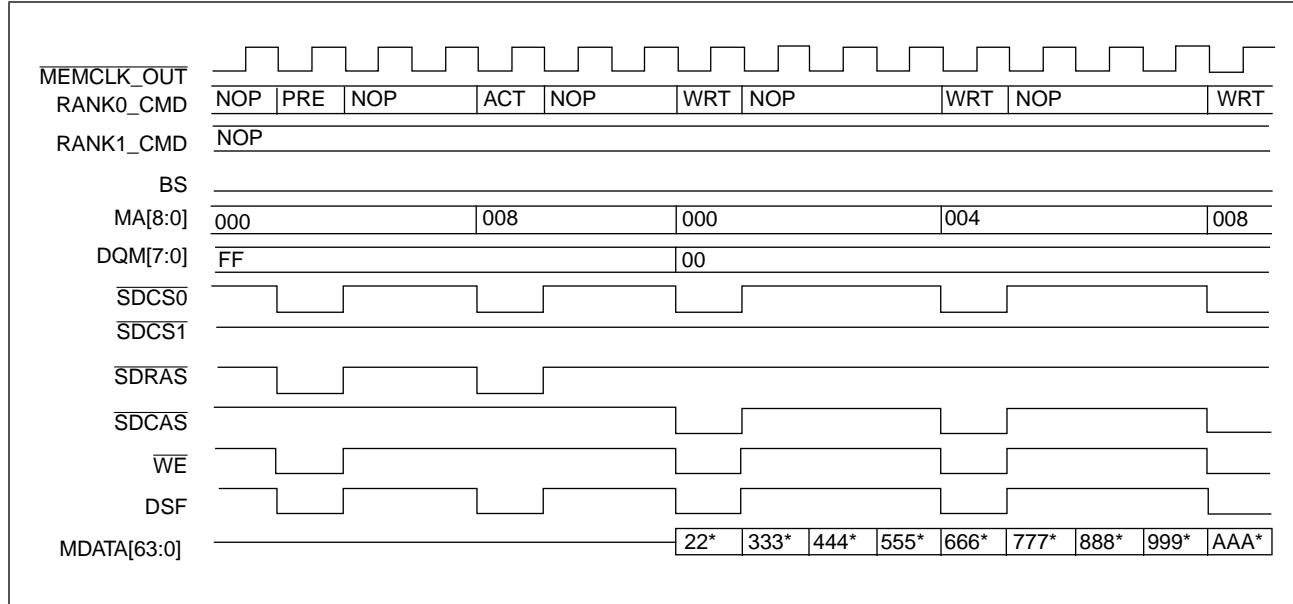

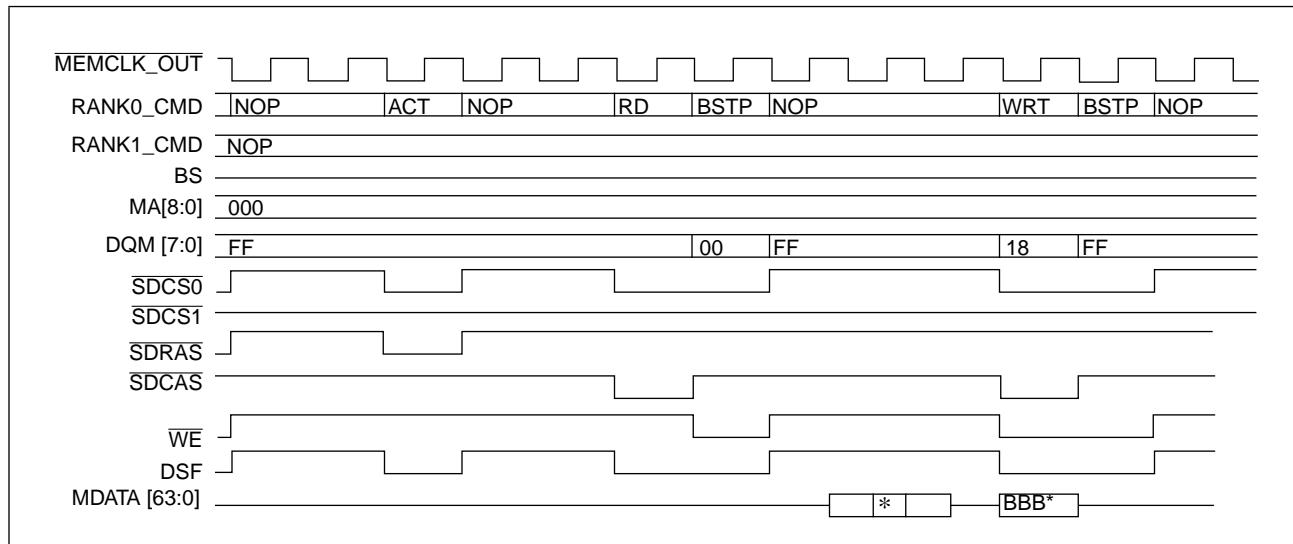

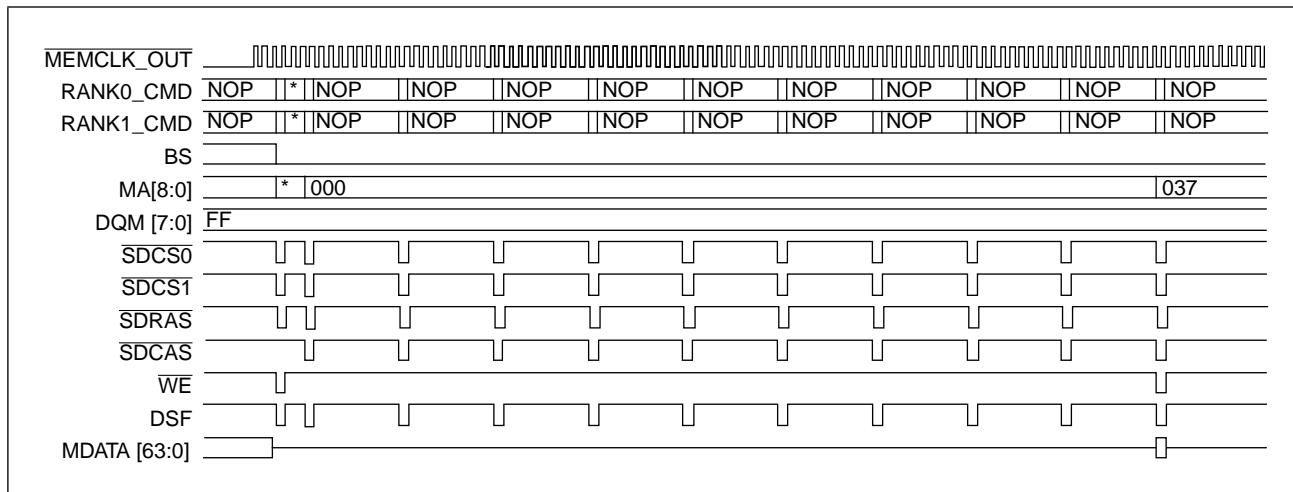

| <b>Timing Diagrams</b> . . . . .                                       | 341 |

| <b>Operating Specifications</b> . . . . .                              | 349 |

| <b>Absolute Maximum Ratings</b> . . . . .                              | 350 |

| <b>Recommended Operating Conditions</b> . . . . .                      | 351 |

| <b>Target DC Characteristics</b> . . . . .                             | 352 |

| <b>GUI, MEM, and SYS Clock PLL Rate Selection</b> . . . . .            | 355 |

| <b>Pixel Clock PLL Rate Selection</b> . . . . .                        | 358 |

| <b>Bt2166 Packaging Specifications</b> . . . . .                       | 371 |

## List of Figures

|                                                                                       |     |

|---------------------------------------------------------------------------------------|-----|

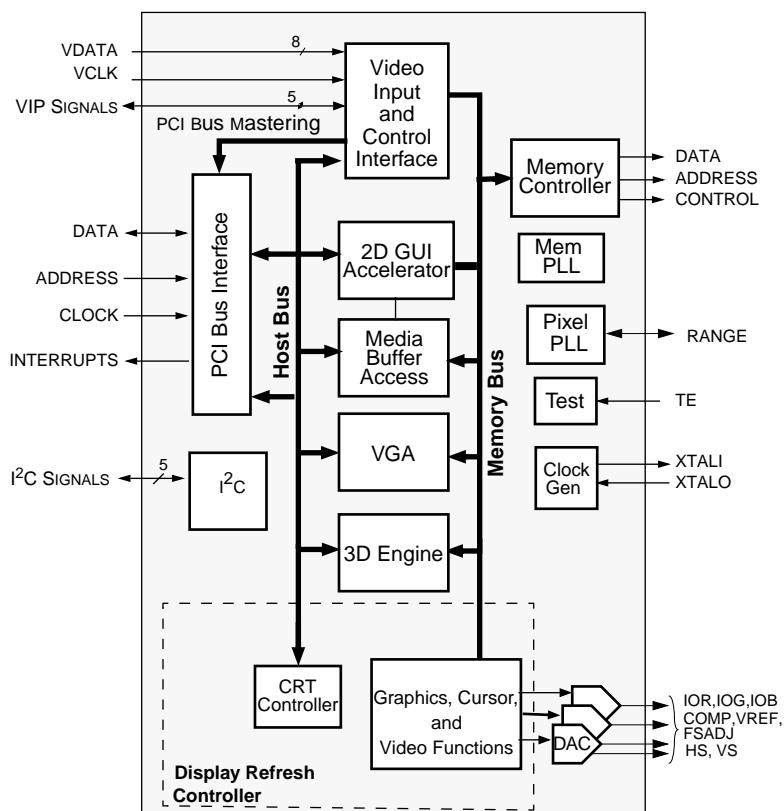

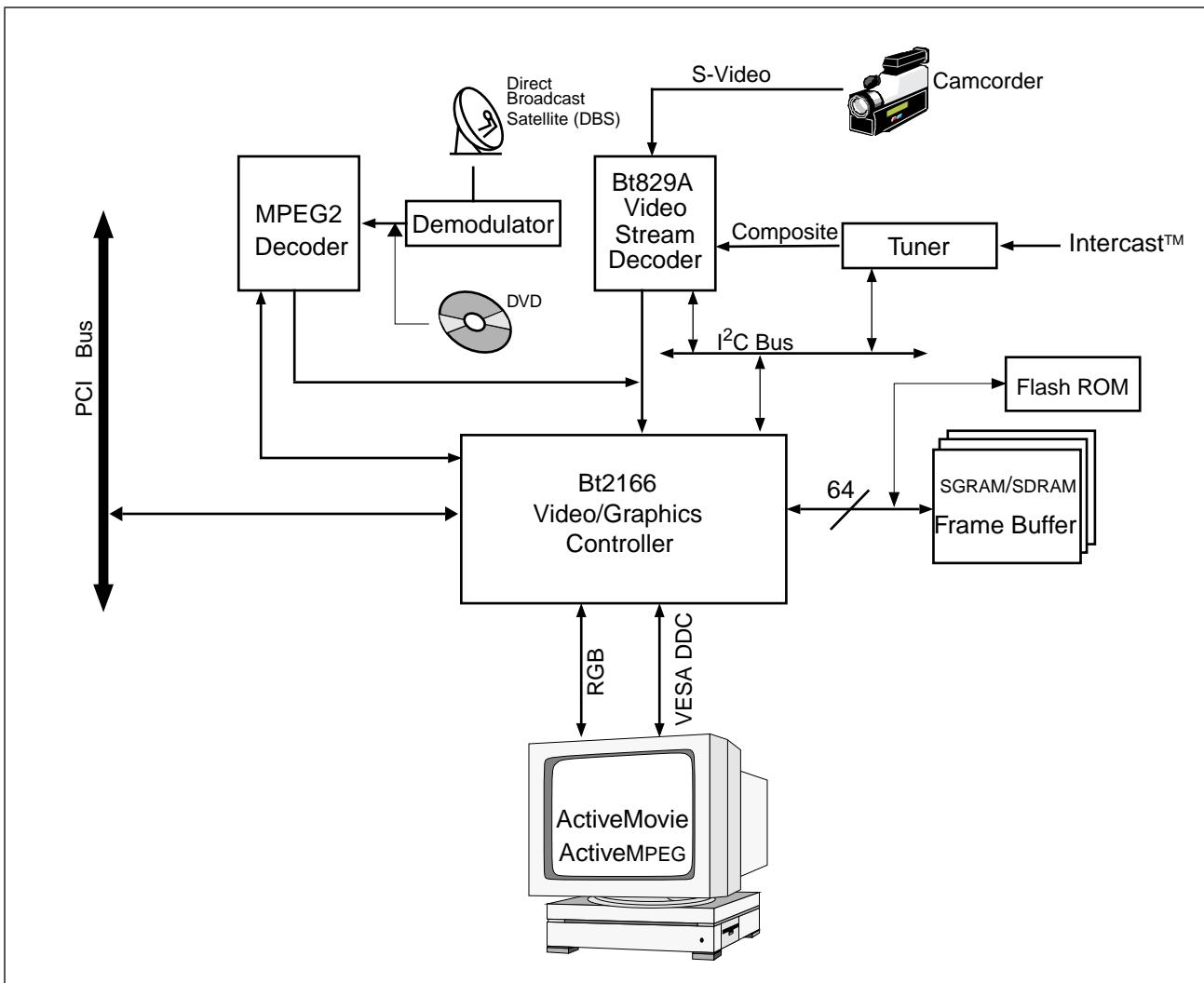

| Figure 1. Bt2166 Configuration .....                                                  | 5   |

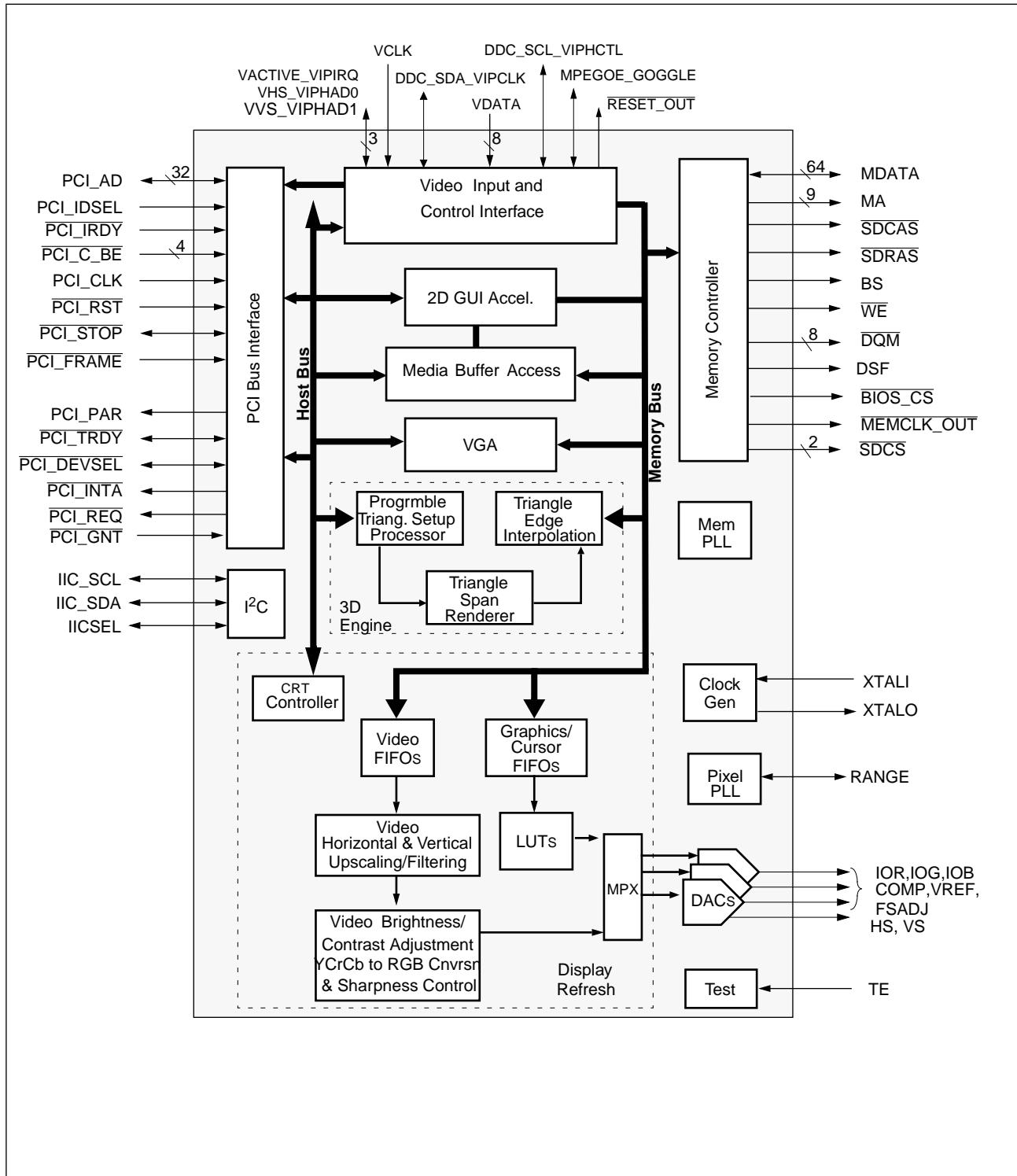

| Figure 2. Bt2166 Block Diagram .....                                                  | 6   |

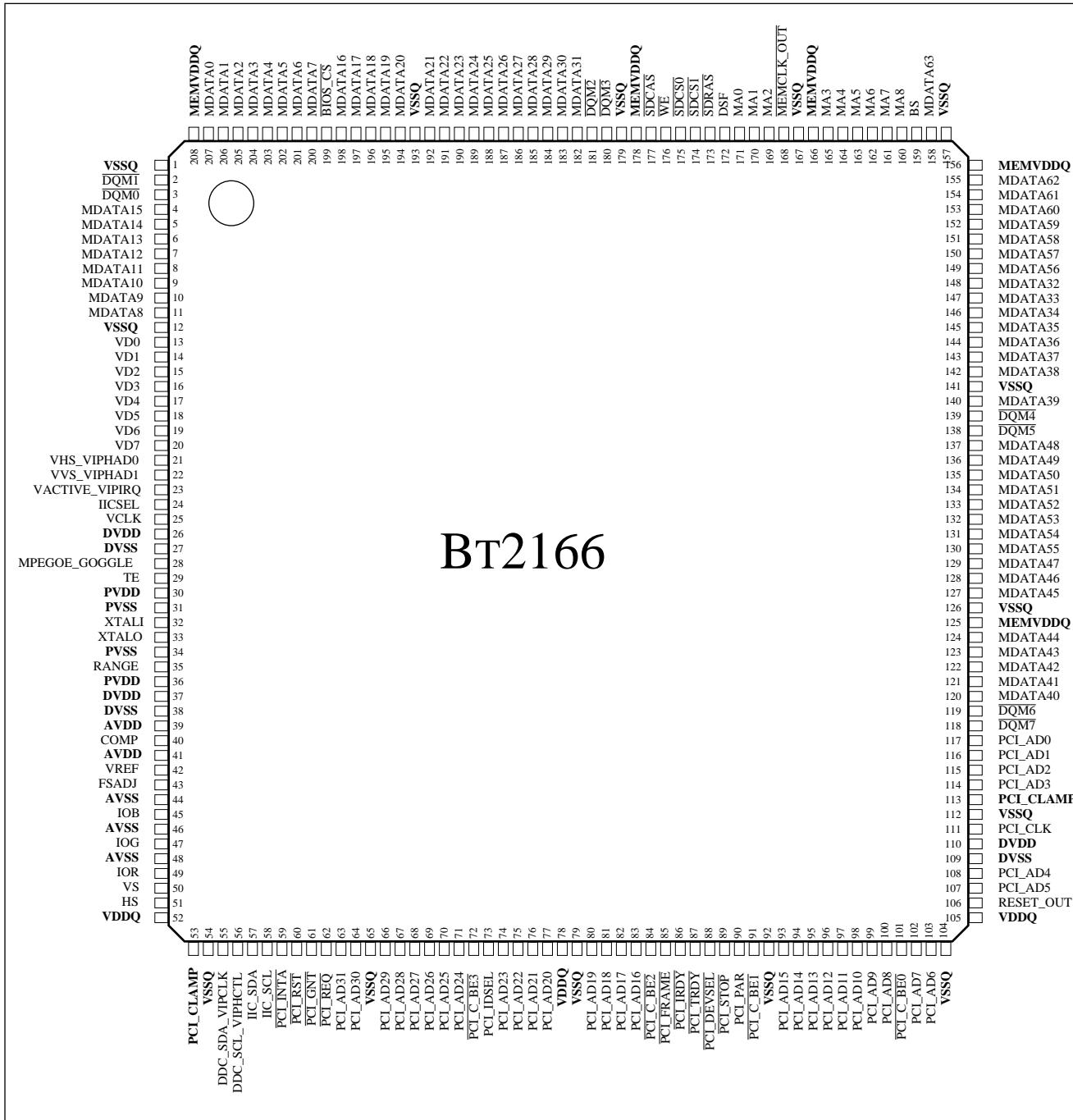

| Figure 3. Bt2166 PCI-Bus Pin Layout .....                                             | 9   |

| Figure 4. CPU Apertures on a PCI/AGP System.....                                      | 16  |

| Figure 5. Memory Map .....                                                            | 17  |

| Figure 6. Bt2166 HBUS Agents.....                                                     | 18  |

| Figure 7. Protected Mode Aperture Mapping To DRAM .....                               | 19  |

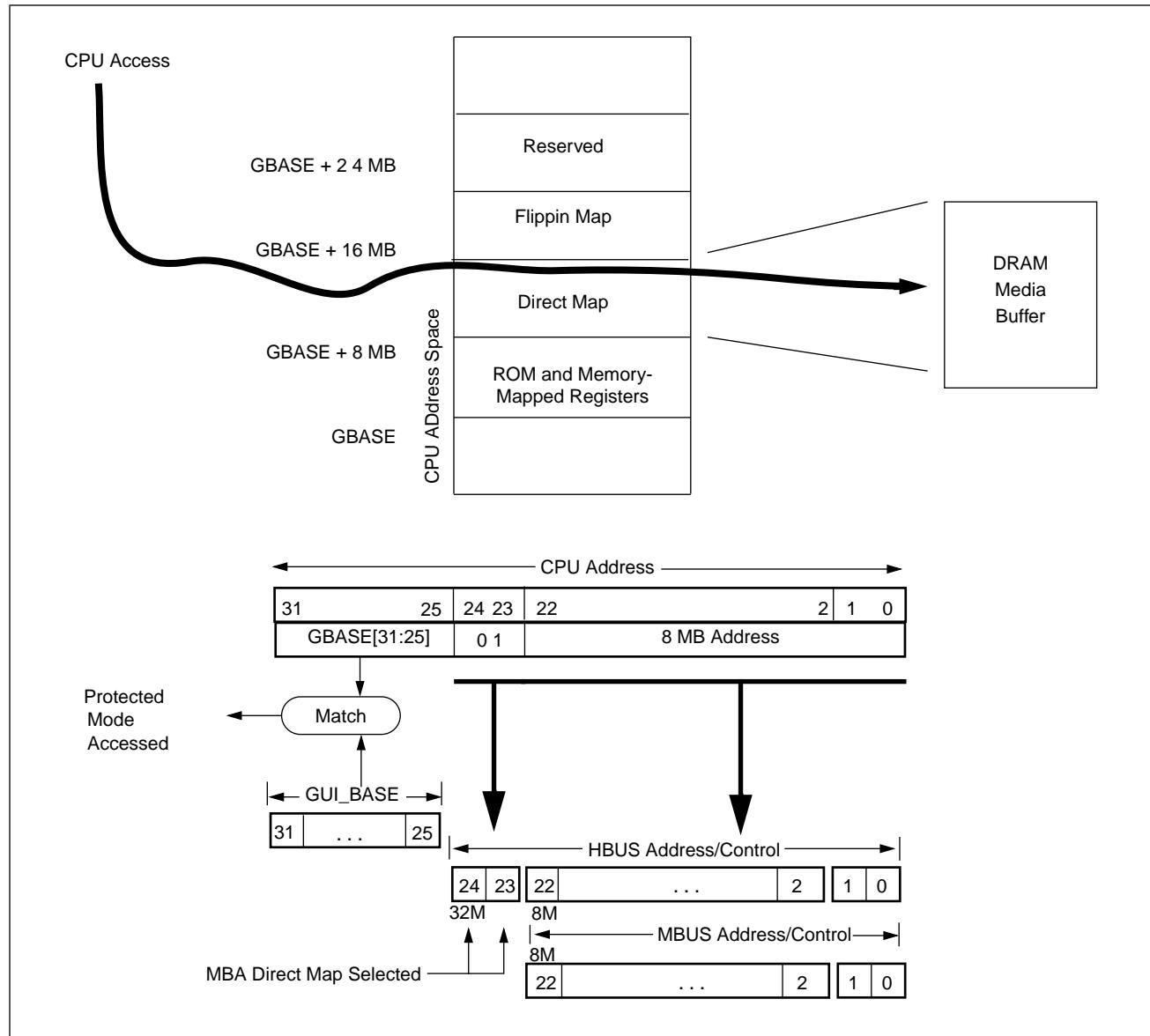

| Figure 8. Media Buffer Access Via Direct Map .....                                    | 21  |

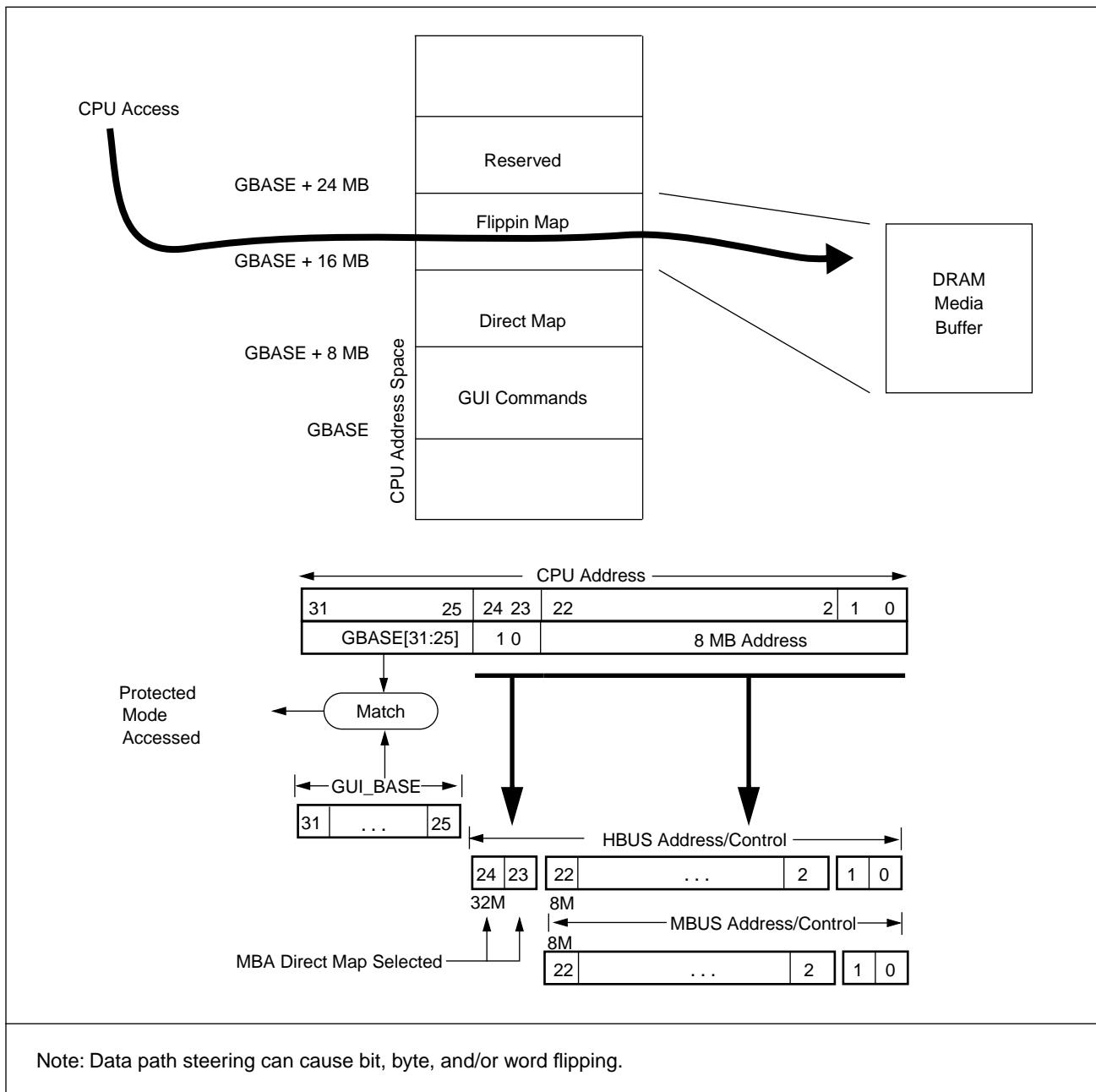

| Figure 9. Media Buffer Access Via Flippin Map.....                                    | 22  |

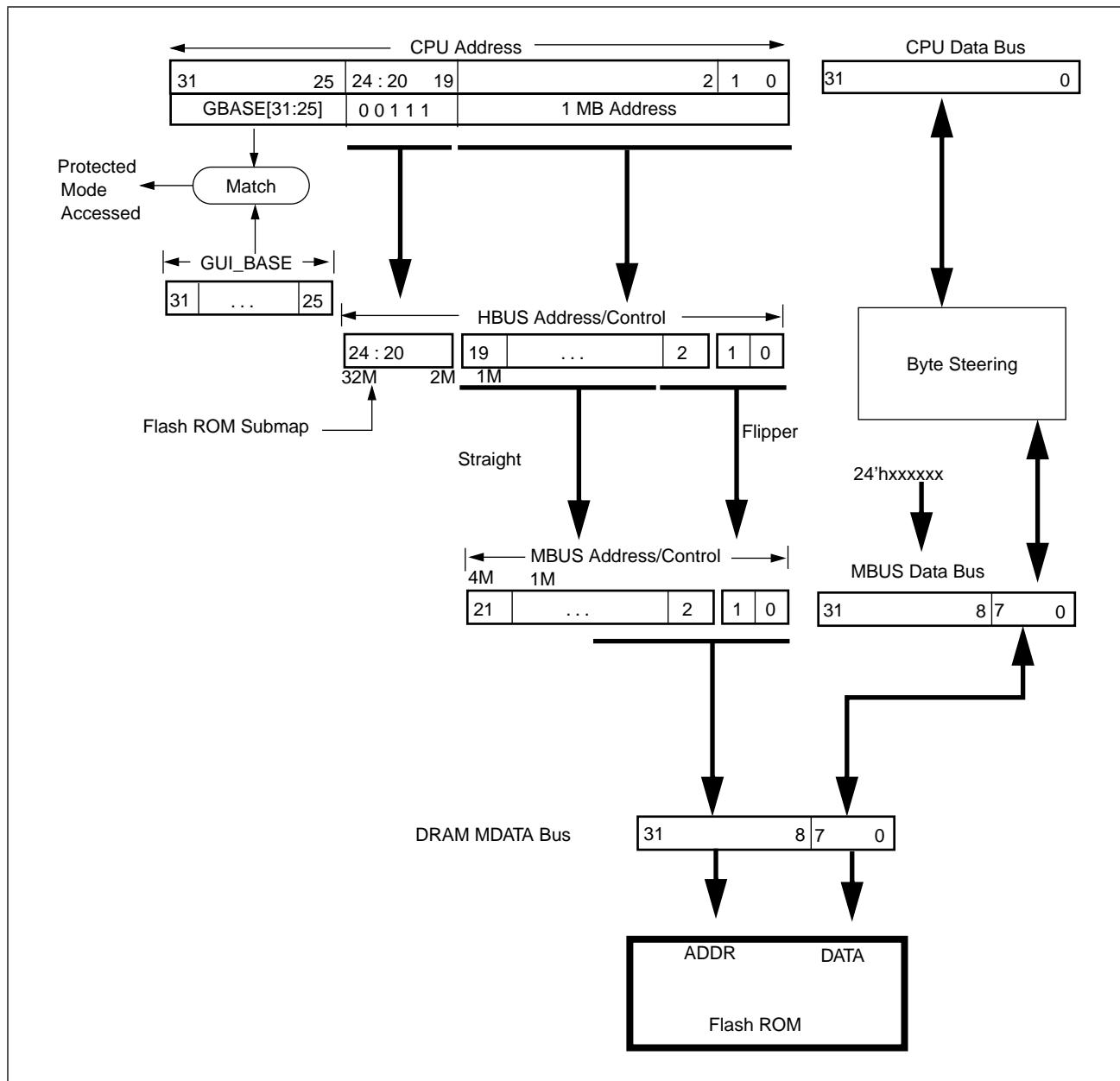

| Figure 10. Flash ROM Access Address Mapping .....                                     | 24  |

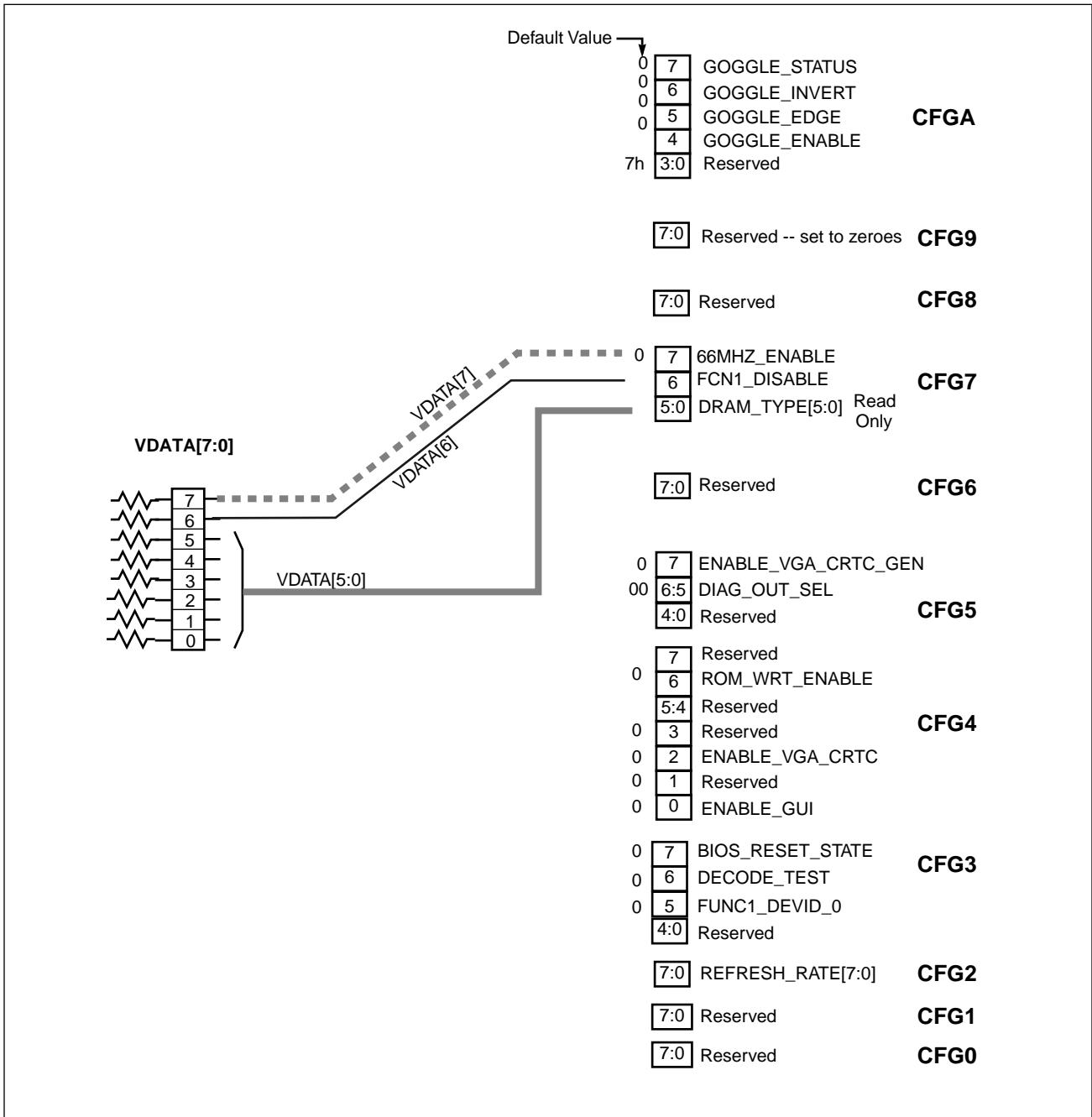

| Figure 11. Configuration Registers (GRP_CFG[A:0]) and Strapping Bits for Bt2166 ..... | 55  |

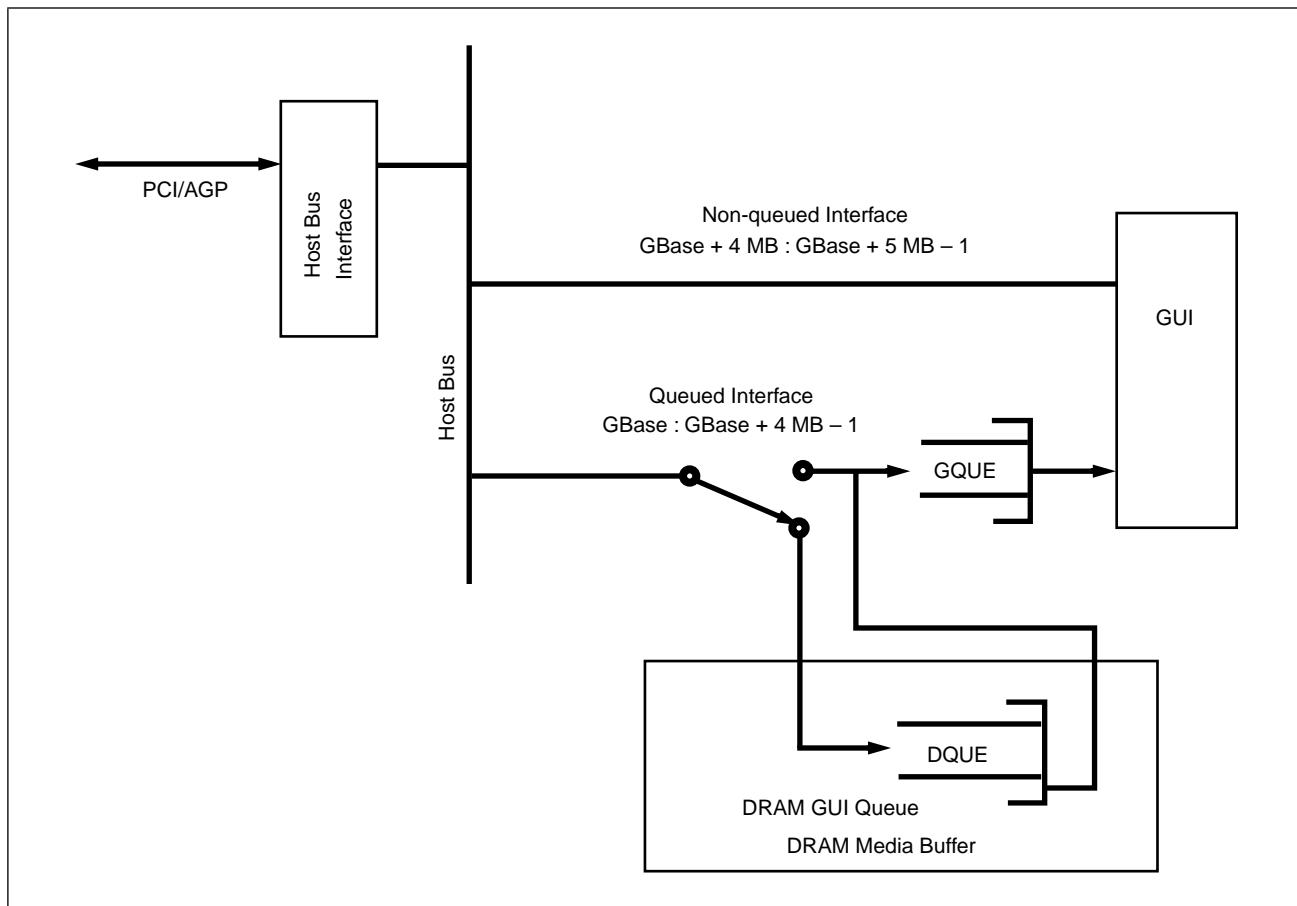

| Figure 12. Non-queued, Queued And DRAM Queued GUI Interface .....                     | 106 |

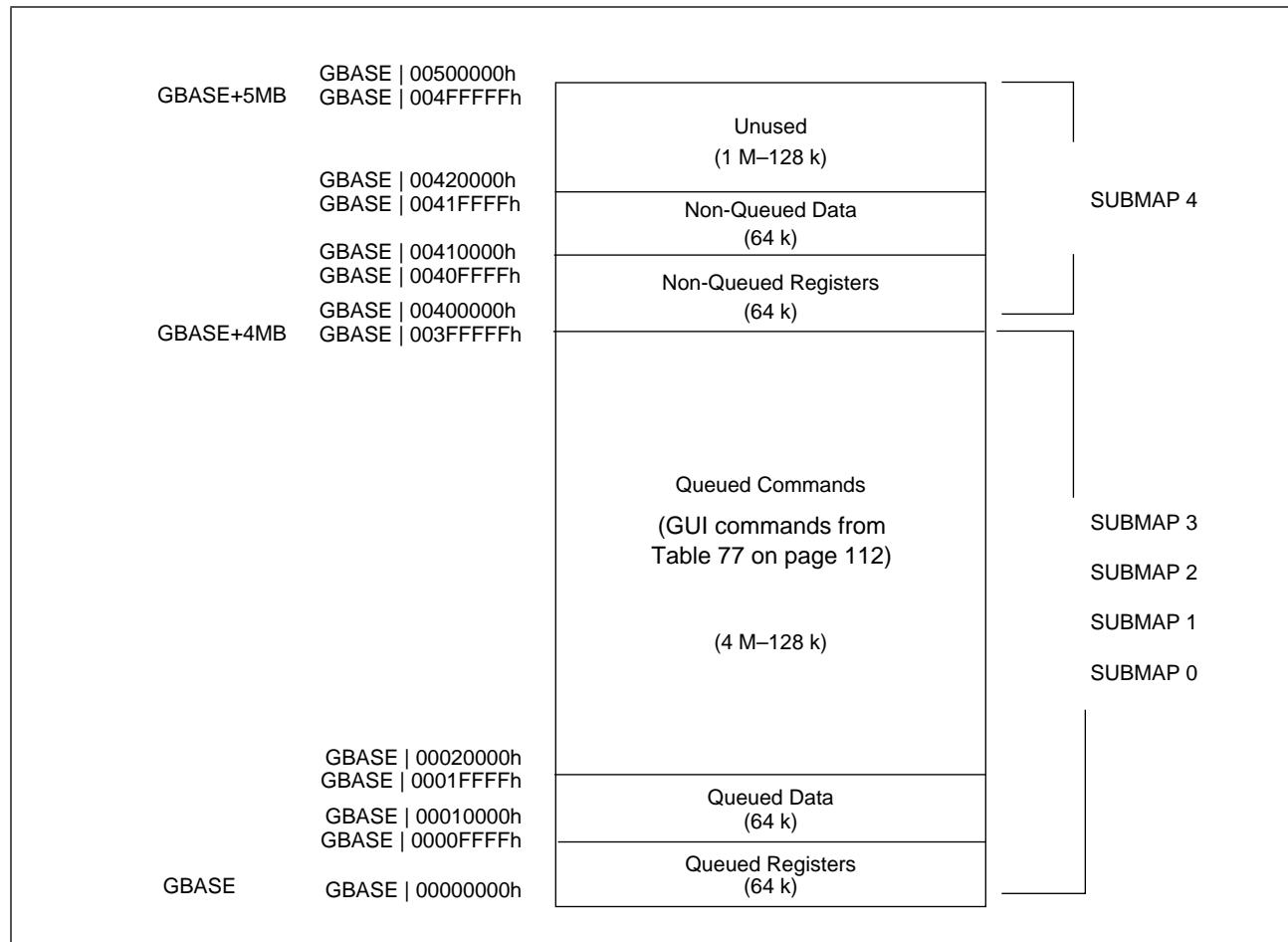

| Figure 13. GUI Command/Register Map .....                                             | 107 |

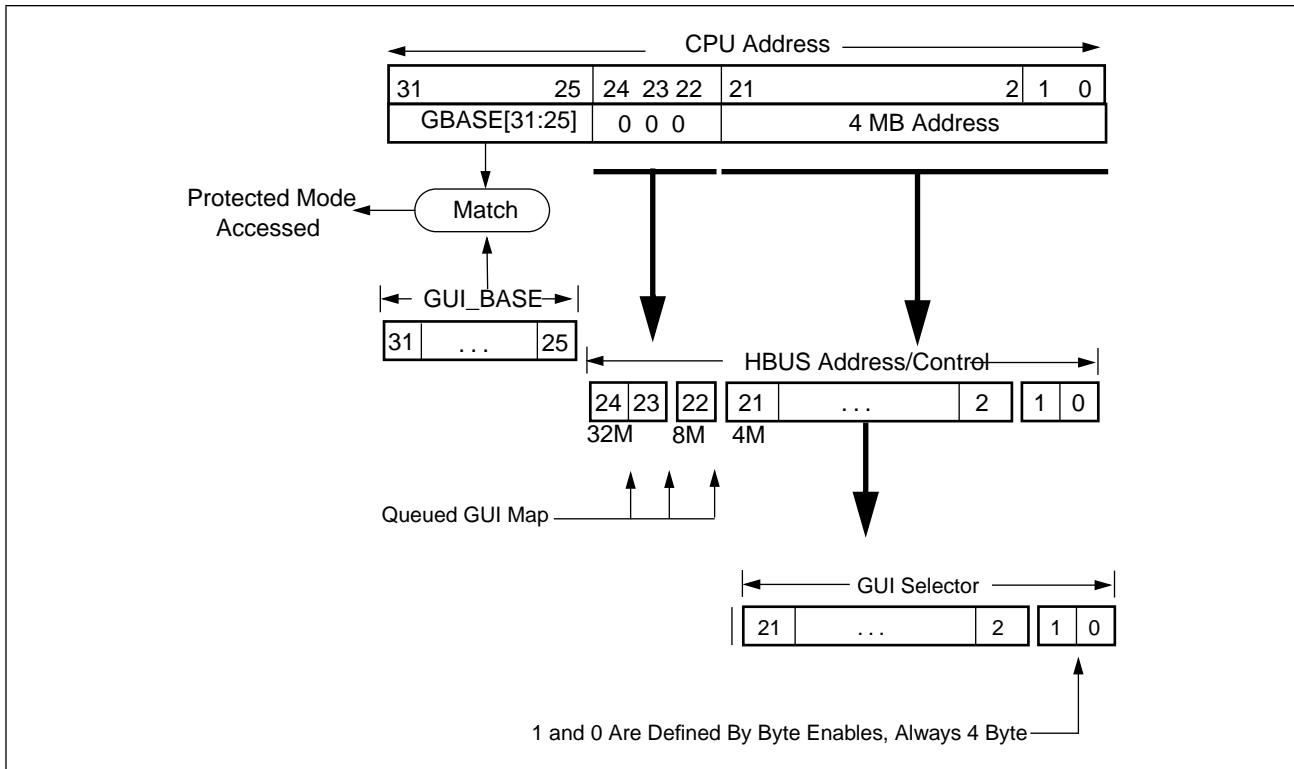

| Figure 14. Queued GUI Address Mapping .....                                           | 109 |

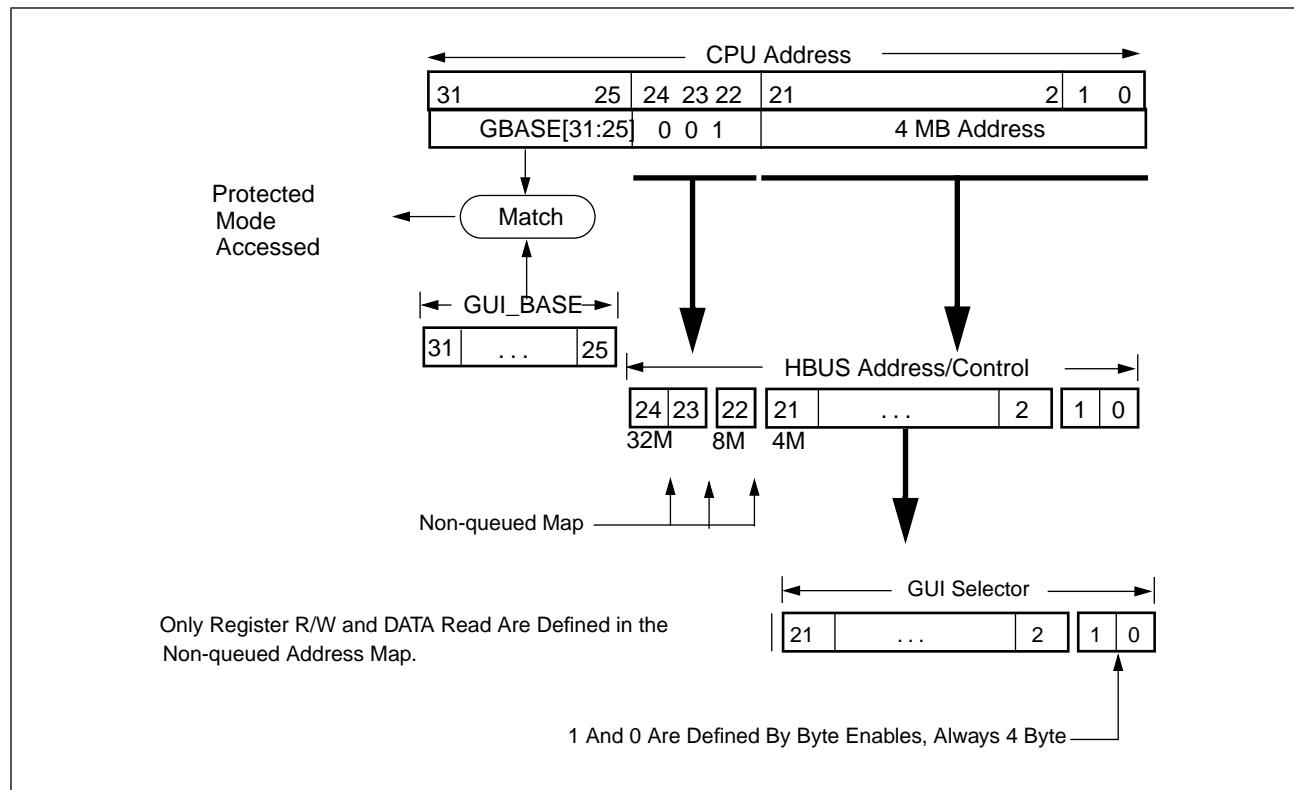

| Figure 15. Non-queued GUI Address Mapping .....                                       | 111 |

| Figure 16. Video Input Subsystem .....                                                | 149 |

| Figure 17. Video Input Control Structures .....                                       | 150 |

| Figure 18. Video Input Subsystem Block Diagram .....                                  | 151 |

| Figure 19. Formatting of Video Data in Memory .....                                   | 156 |

| Figure 20. Video Interface Timing Diagram .....                                       | 159 |

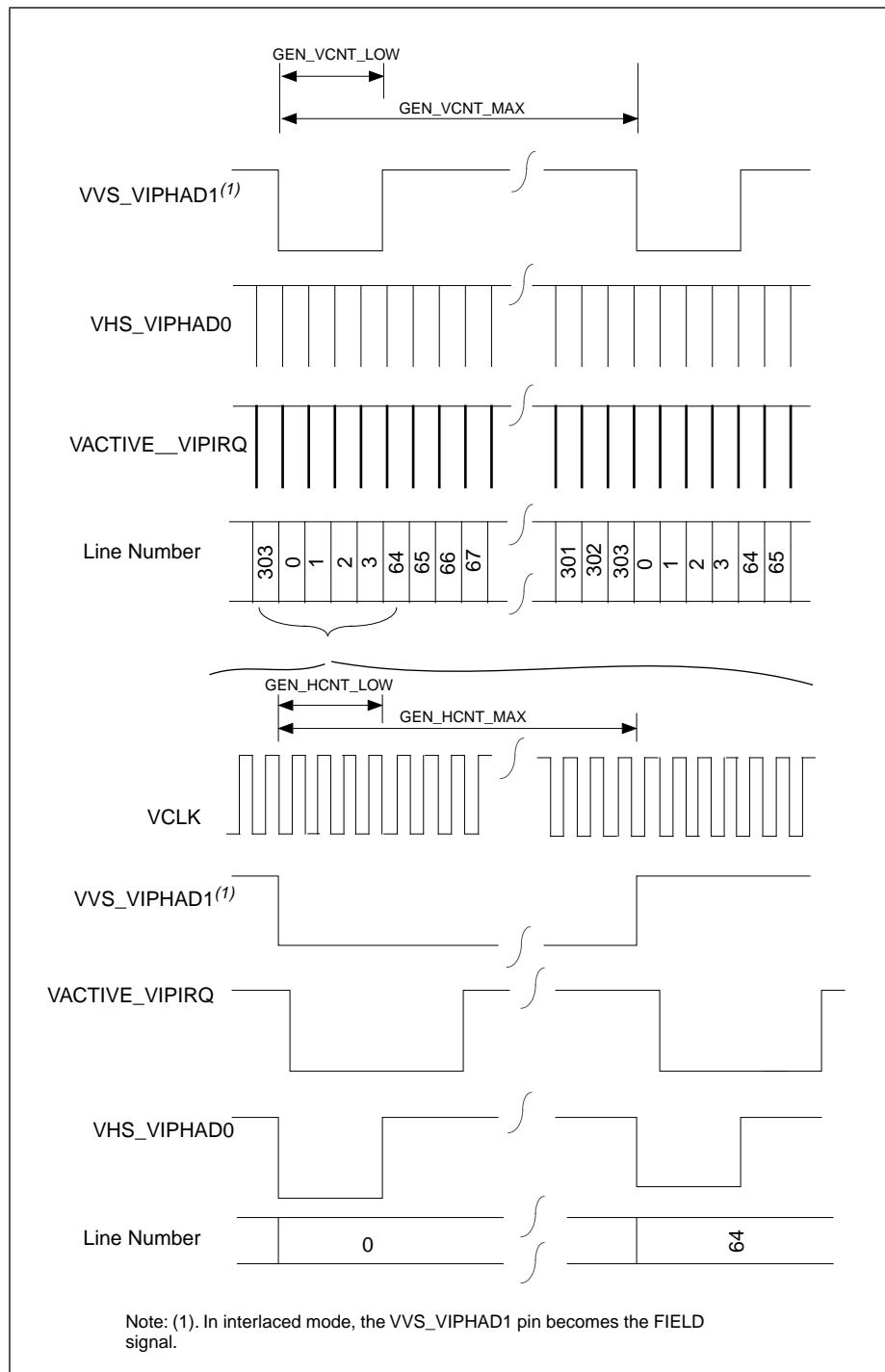

| Figure 21. Generation of VHS_VIPHAD0 and VVS_VIPHAD1 in Non-Interlaced Mode.....      | 160 |

| Figure 22. Generation of VHS_VIPHAD0 and FIELD in Interlaced Mode.....                | 161 |

| Figure 23. Timing of VHS_VIPHAD0 and FIELD in Interlaced Mode .....                   | 162 |

| Figure 24. Timing of VHS_VIPHAD0 and FIELD in Non-Interlaced Mode .....               | 163 |

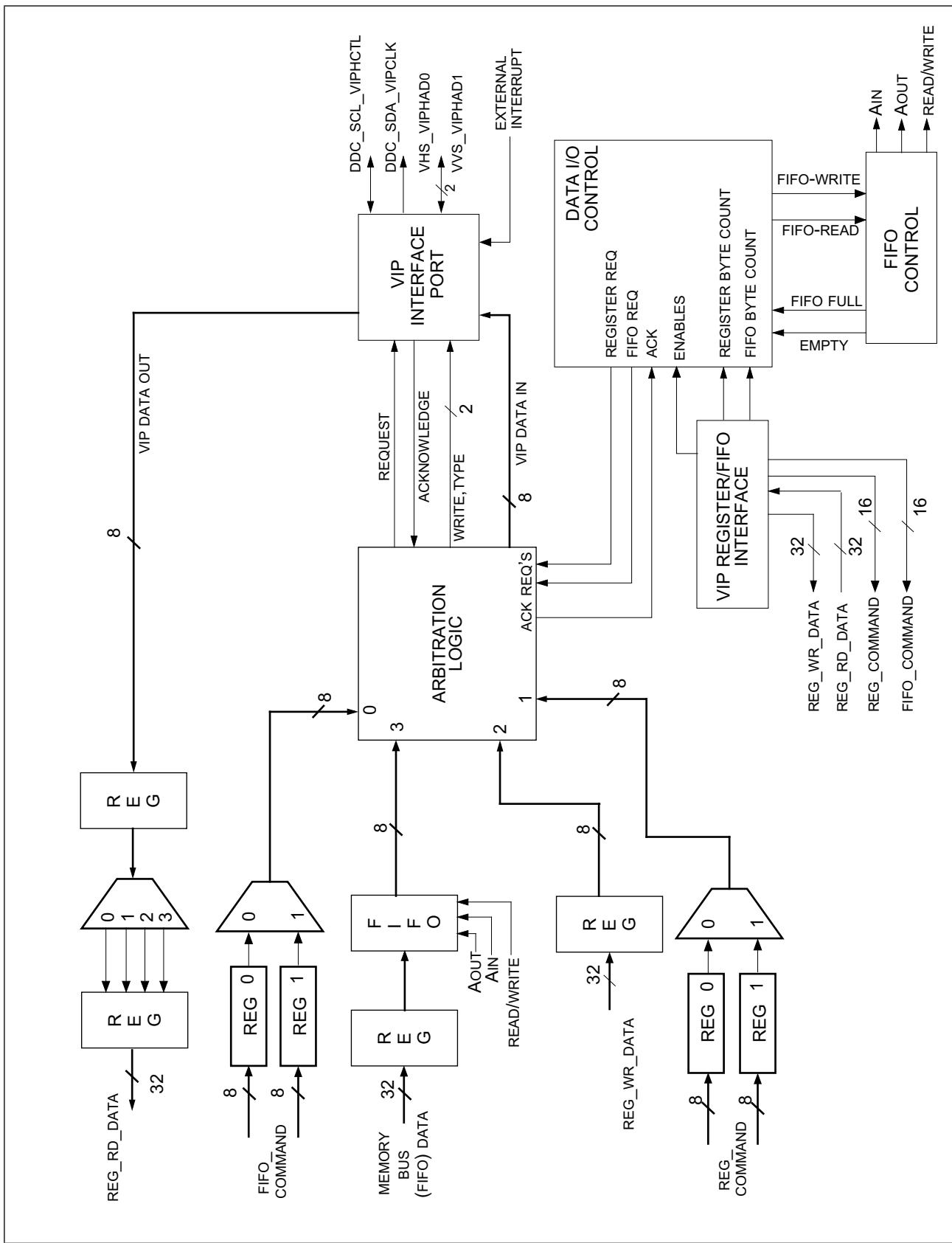

| Figure 25. VIP Subsystem Block Diagram .....                                          | 166 |

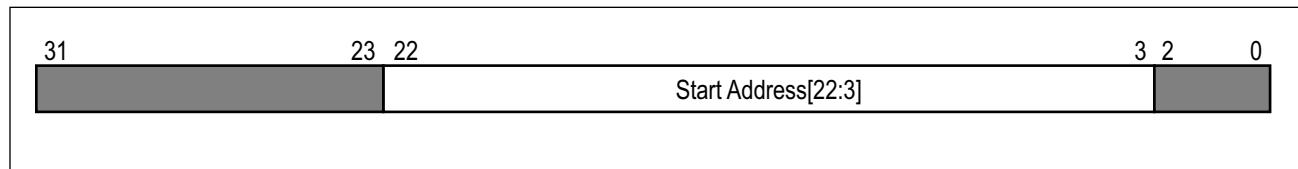

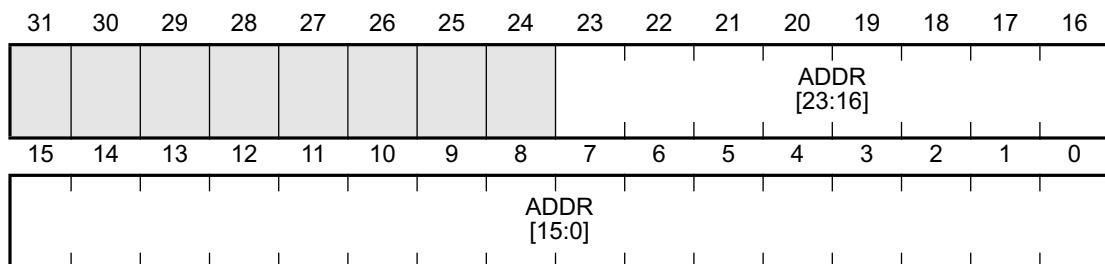

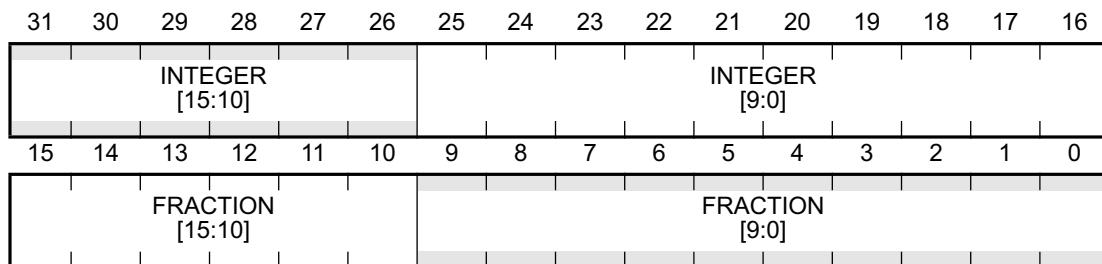

| Figure 26. Graphics/Video/Cursor Start Address Register Bit Mapping .....             | 187 |

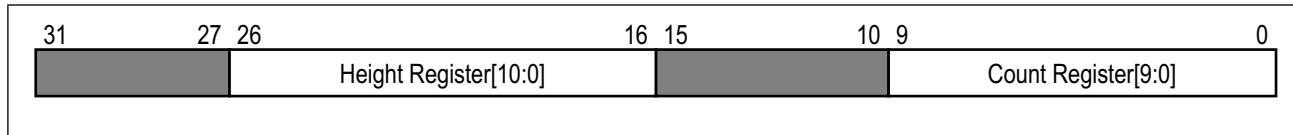

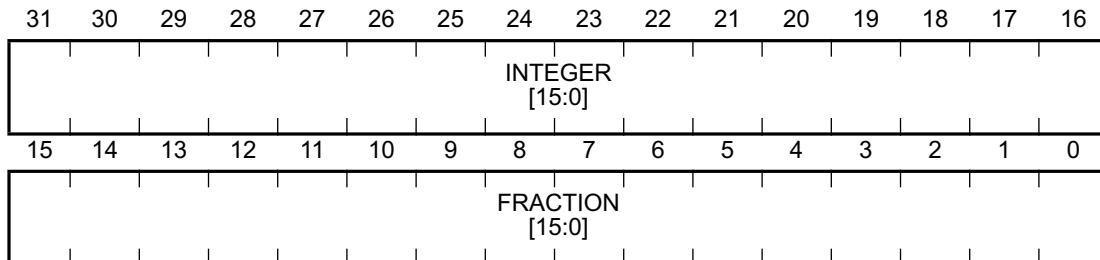

| Figure 27. Video Size Register Bit Mapping .....                                      | 188 |

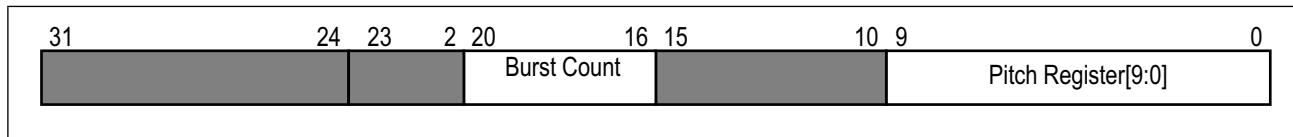

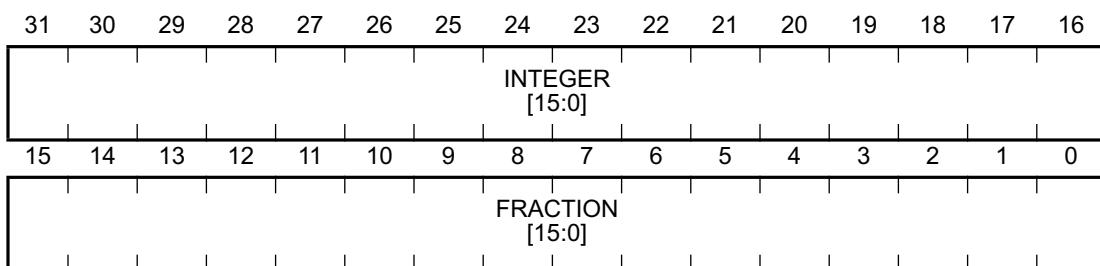

| Figure 28. Graphics and Video Pitch and Burst Count Register Bit Mapping .....        | 188 |

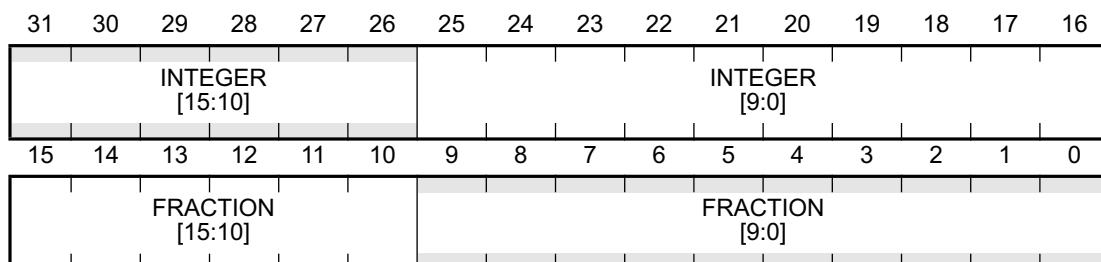

| Figure 29. Cursor Size Register Bit Mapping .....                                     | 188 |

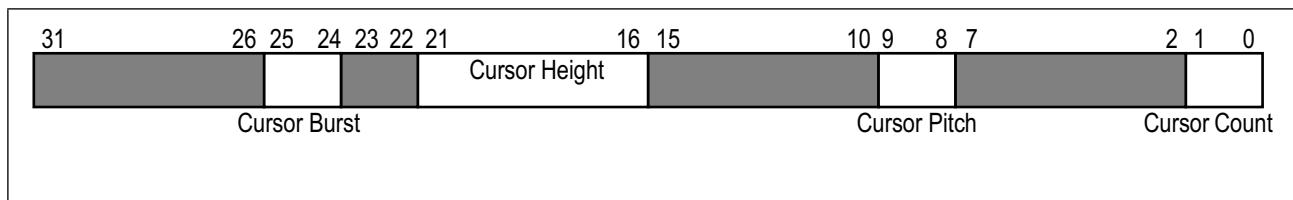

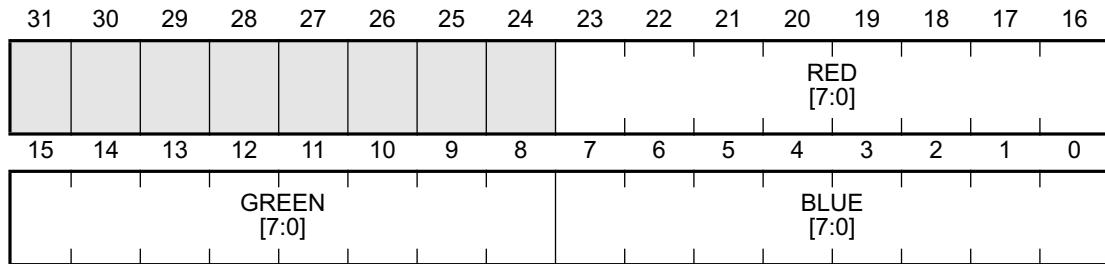

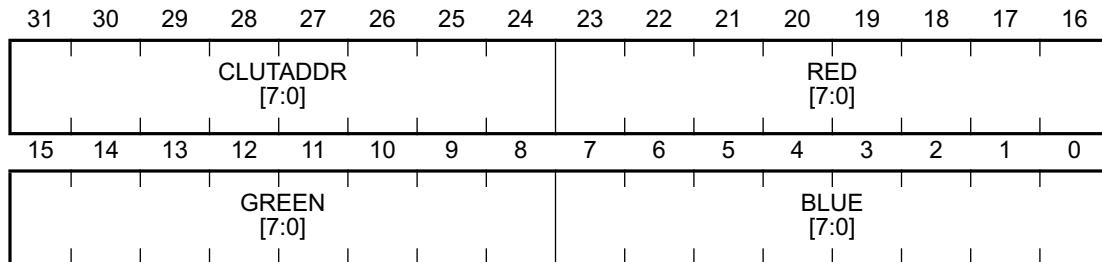

| Figure 30. Color Palette Ram Bit Mapping .....                                        | 190 |

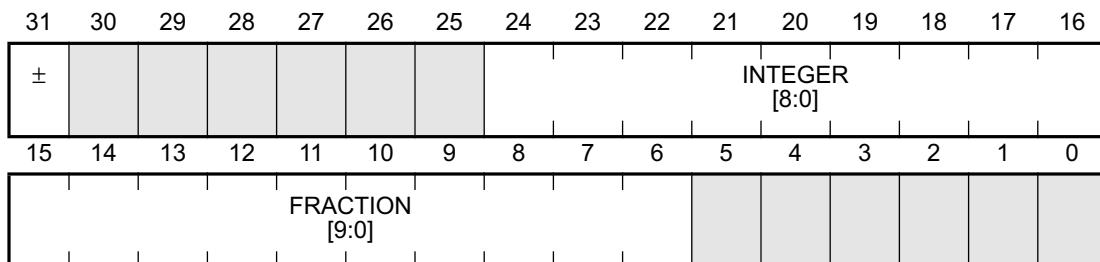

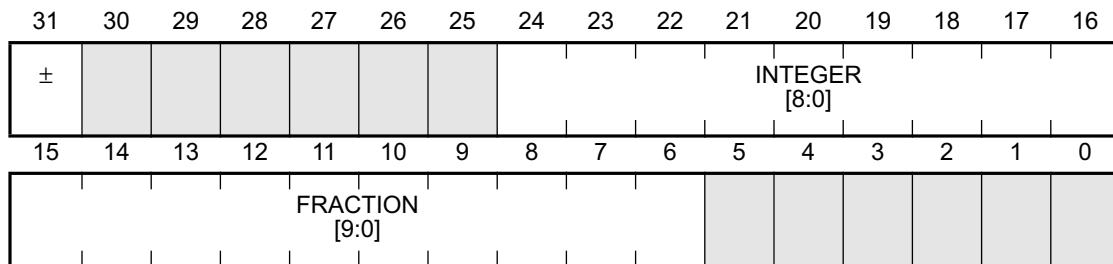

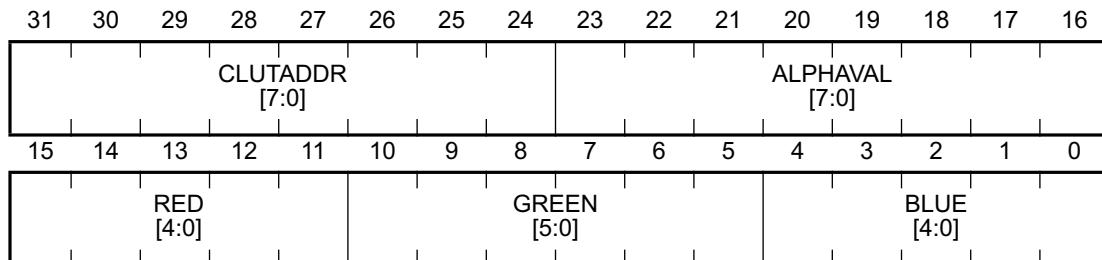

| Figure 31. Luma Correction Ram Write Bit Mapping.....                                 | 191 |

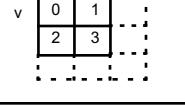

| Figure 32. Timing Generator Waveforms, Non-interlaced.....                            | 194 |

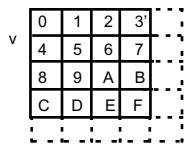

| Figure 33. 4-Bit Pseudocolor Graphics Data Format.....                                | 200 |

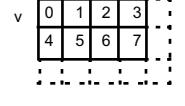

| Figure 34. 8-Bit Pseudocolor Graphics Data Format.....                                | 200 |

| Figure 35. 16-Bit 5-5-5 Truecolor Graphics/Video Data Format .....                    | 201 |

| Figure 36. 16-Bit 5-6-5 Truecolor Graphics/Video Data Format .....                    | 201 |

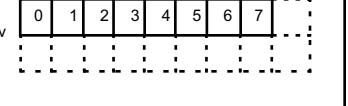

| Figure 37. 32-Bit Planar 8-8-8 Truecolor Graphics/Video Data Format .....             | 202 |

|                                                                            |     |

|----------------------------------------------------------------------------|-----|

| Figure 38. 24-Bit Packed 8-8-8 Truecolor Graphics Data Format . . . . .    | 202 |

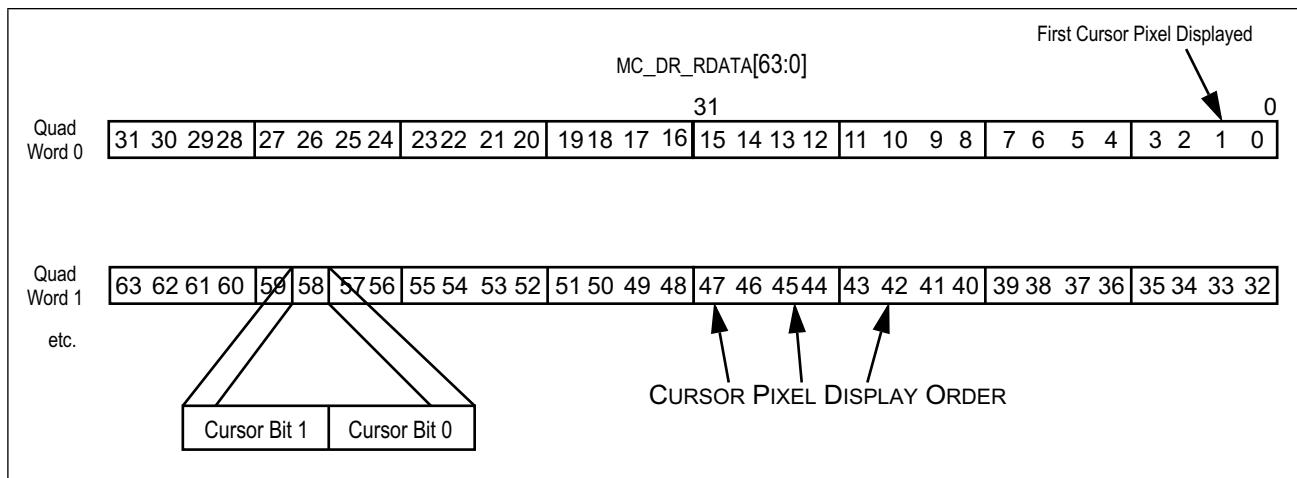

| Figure 39. Cursor Memory Format . . . . .                                  | 204 |

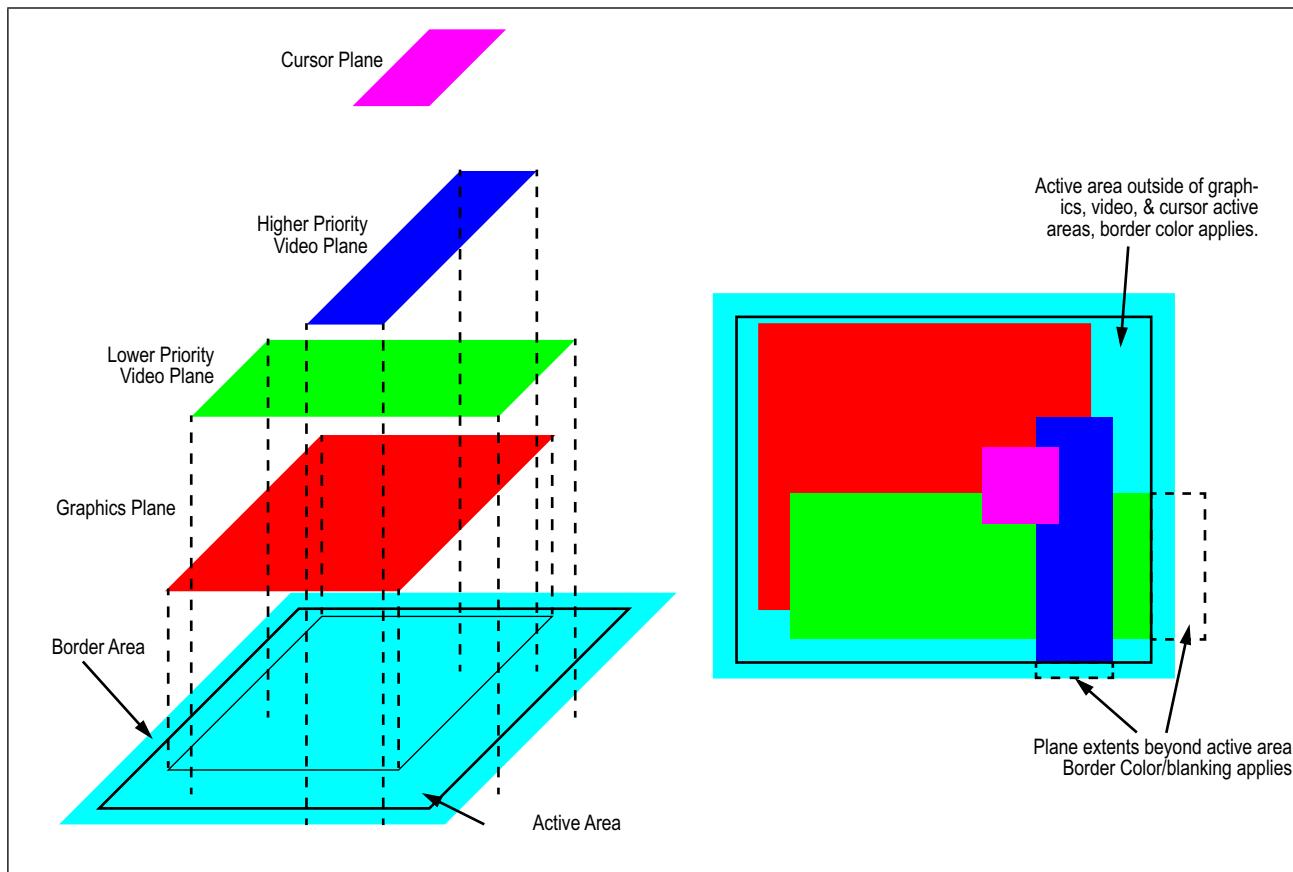

| Figure 40. Display Priority . . . . .                                      | 210 |

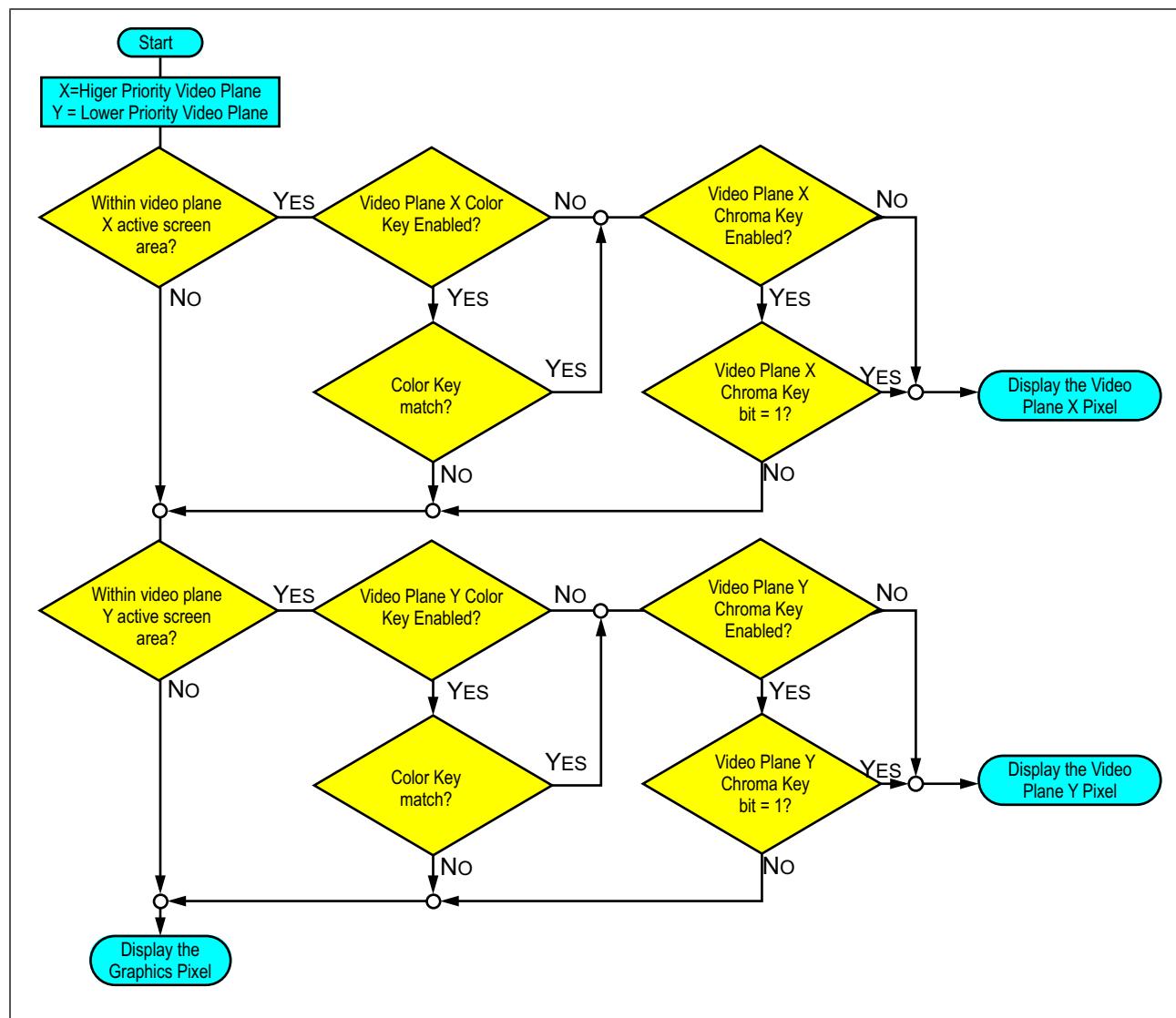

| Figure 41. Video Plane/Graphics Pixel Source Selection Flowchart . . . . . | 215 |

| Figure 42. Register Interface Read Cycle Timing Diagram . . . . .          | 219 |

| Figure 43. Register Interface Write Cycle Timing Diagram . . . . .         | 219 |

| Figure 44. Typical 3D Graphics Pipeline . . . . .                          | 223 |

| Figure 45. Sample Triangle . . . . .                                       | 224 |

| Figure 46. 3D Accelerator Architecture . . . . .                           | 226 |

| Figure 47. PRE Basic Architecture. . . . .                                 | 228 |

| Figure 48. PRE Data Flow Pipeline . . . . .                                | 230 |

| Figure 49. PRE Architecture with Embedded Processor and Memory . . . . .   | 231 |

| Figure 50. Z Data Buffer. . . . .                                          | 236 |

| Figure 51. Texture Map Formats . . . . .                                   | 237 |

| Figure 52. Example Memory Map . . . . .                                    | 240 |

| Figure 53. PRE Memory Interface . . . . .                                  | 240 |

| Figure 54. Formatted Pixel Output . . . . .                                | 292 |

| Figure 55. Polygon Texture Mapping. . . . .                                | 300 |

| Figure 56. Texture Mapping. . . . .                                        | 301 |

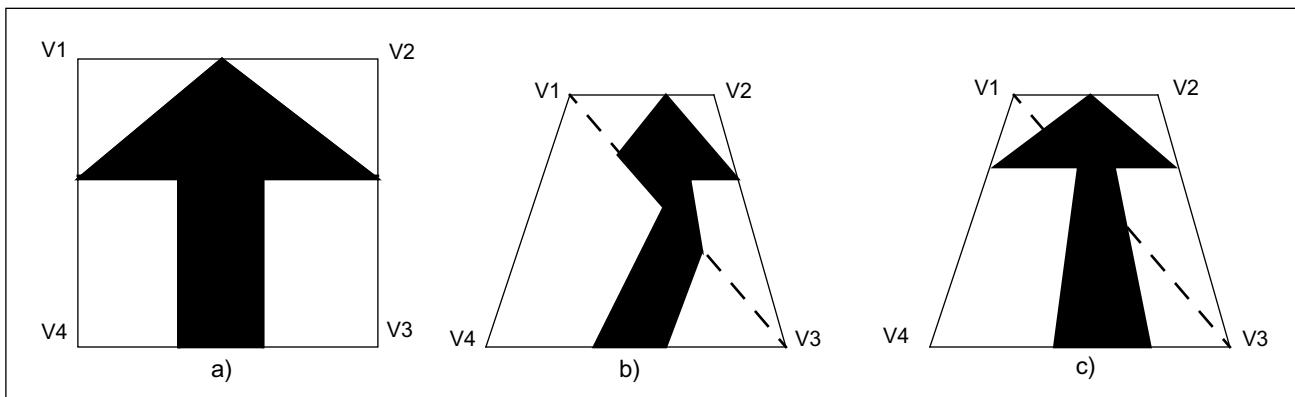

| Figure 57. Image Without Perspective Correction . . . . .                  | 304 |

| Figure 58. Bilinear Interpolation. . . . .                                 | 306 |

| Figure 59. Example Line Drawing . . . . .                                  | 308 |

| Figure 60. Example Gradient Lines . . . . .                                | 314 |

| Figure 61. PCI Configuration Space Header . . . . .                        | 316 |

| Figure 62. PCI/AGP Input Timing Diagram . . . . .                          | 329 |

| Figure 63. PCI/AGP Output Timing Diagram . . . . .                         | 329 |

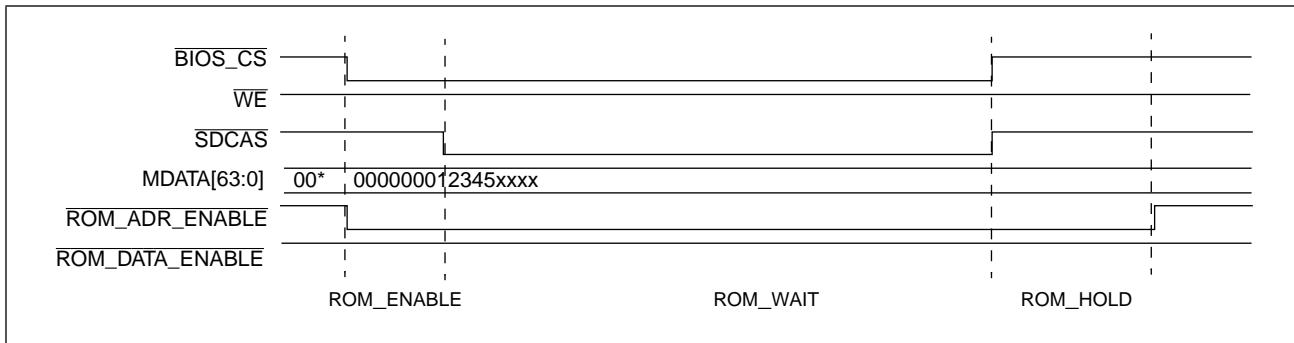

| Figure 64. ROM Write Cycle . . . . .                                       | 338 |

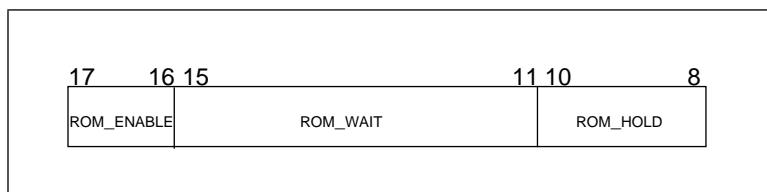

| Figure 65. ROM Configuration Bits (GEN_CFG[17:8]) . . . . .                | 338 |

| Figure 66. ROM Read Cycle . . . . .                                        | 339 |

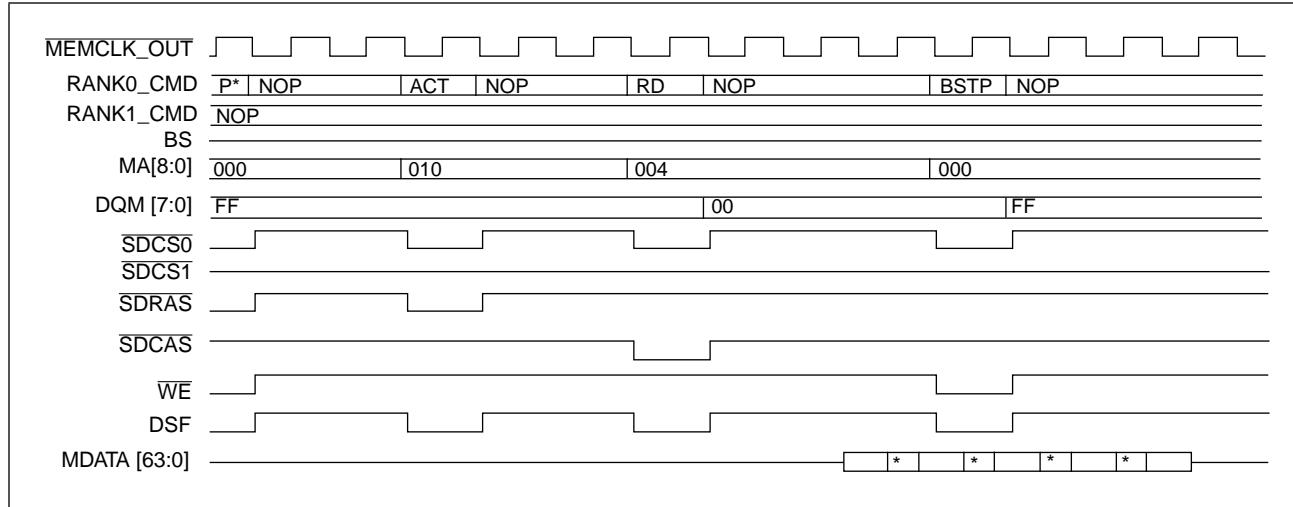

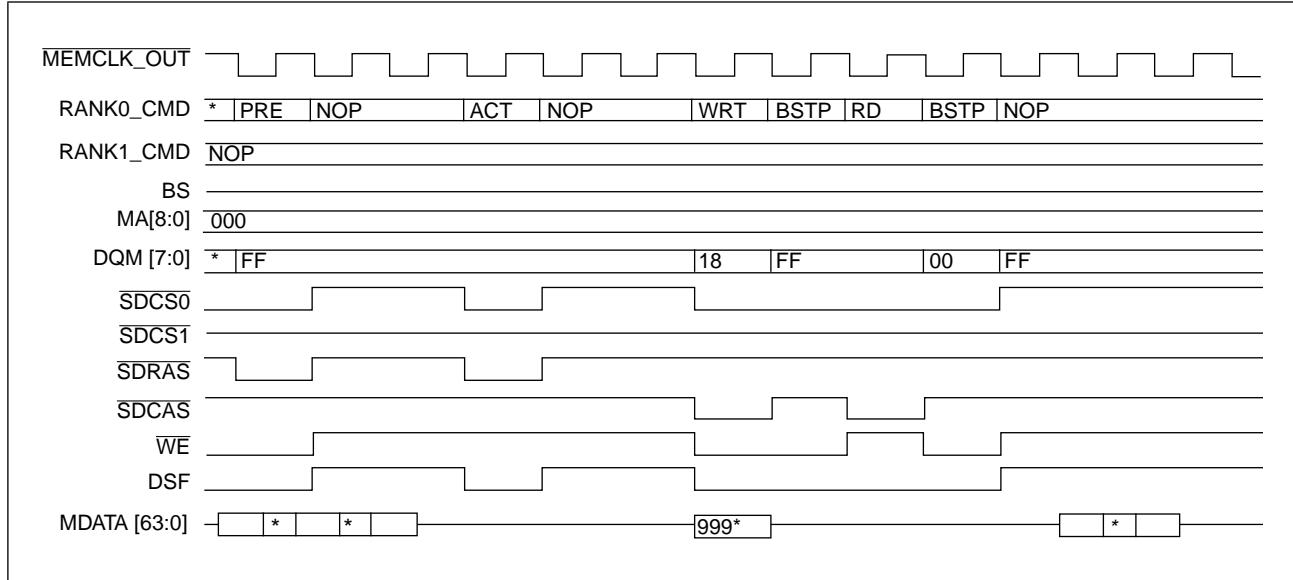

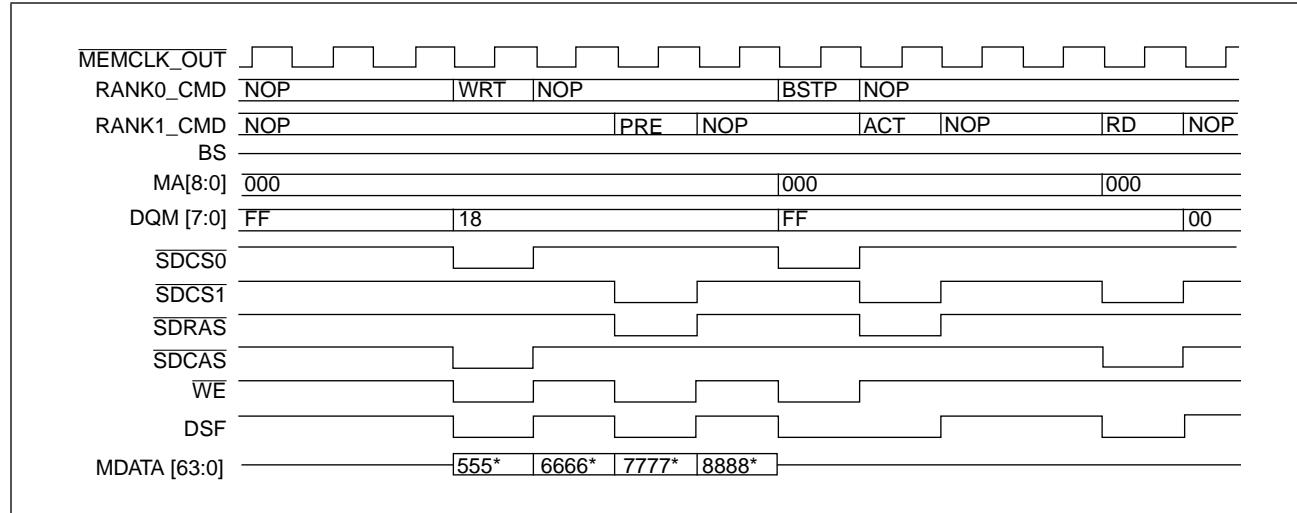

| Figure 67. Single Quadword Read Cycle - Page Miss. . . . .                 | 341 |

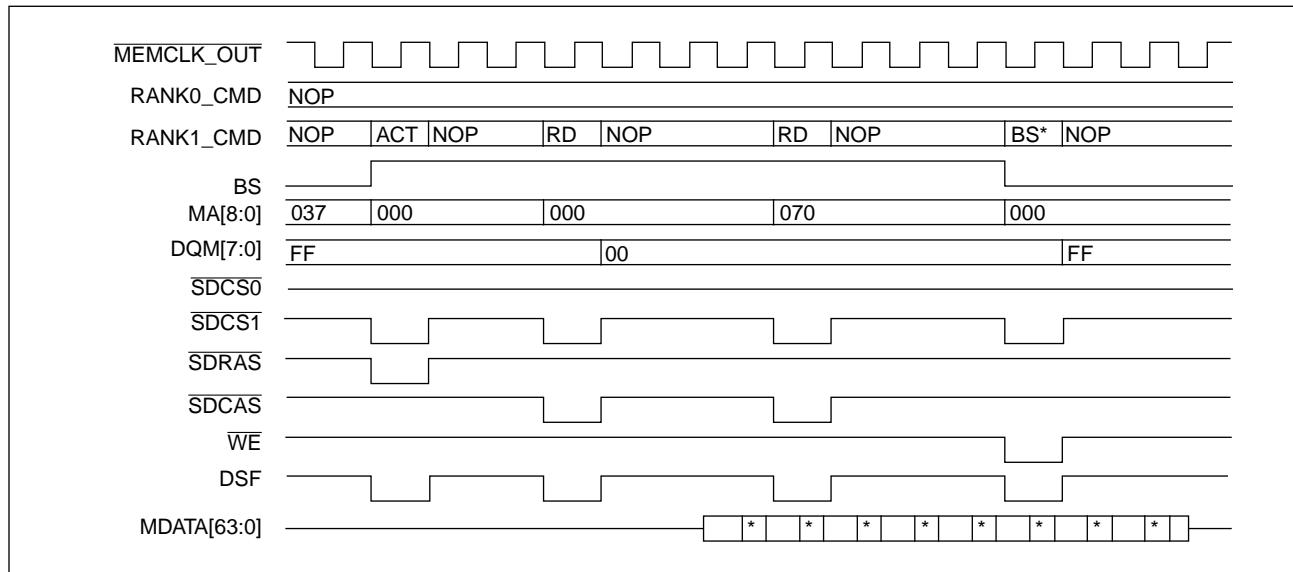

| Figure 68. Burst Read Cycle - Page Miss . . . . .                          | 342 |

| Figure 69. Page Mode Read Cycle . . . . .                                  | 342 |

| Figure 70. Single Quadword Write Cycle. . . . .                            | 343 |

| Figure 71. Burst Write Cycle - Page Miss . . . . .                         | 343 |

| Figure 72. Page Mode Write Cycle . . . . .                                 | 344 |

| Figure 73. Page Mode Read Followed by Write . . . . .                      | 344 |

| Figure 74. Page Mode Write Followed by Read . . . . .                      | 345 |

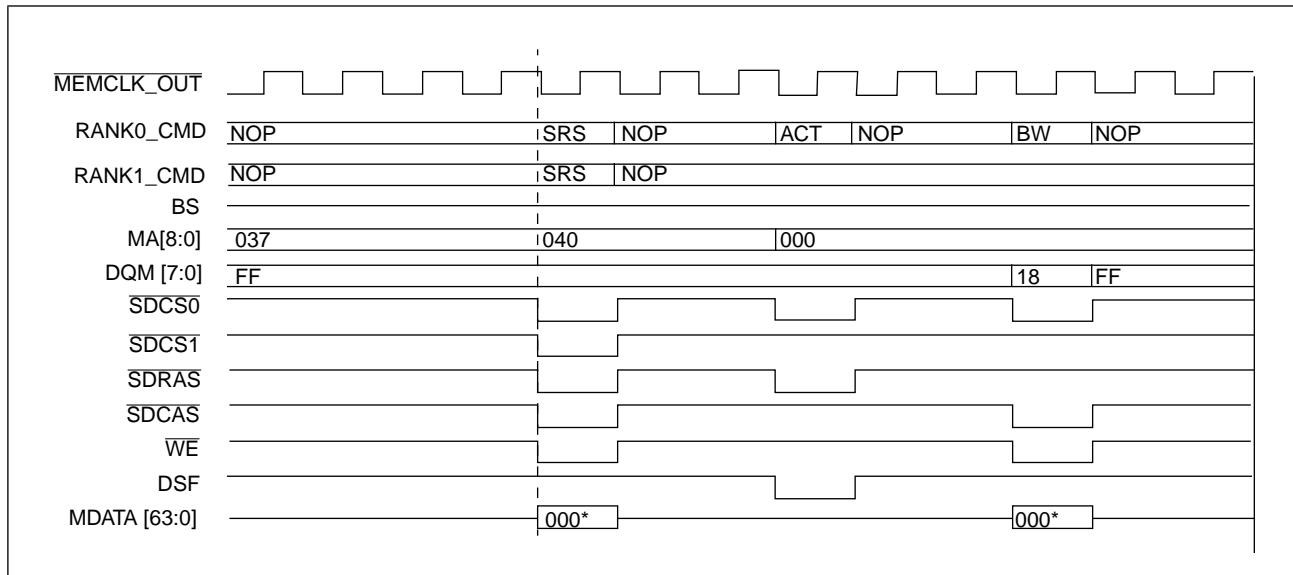

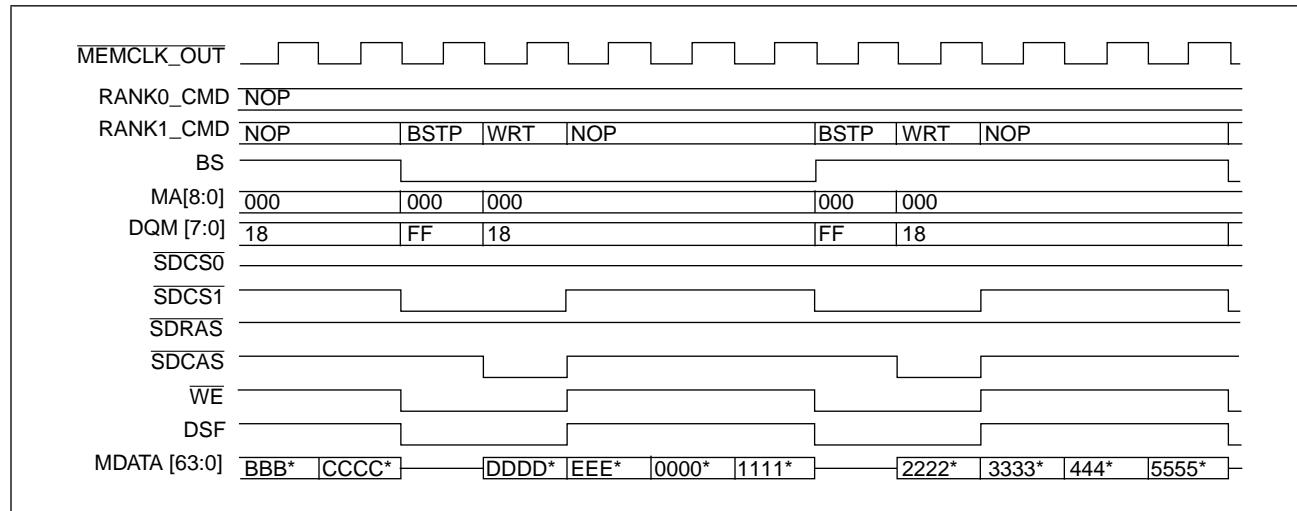

| Figure 75. LCR Command Followed by Block Write . . . . .                   | 345 |

| Figure 76. Burst Write with Hidden Precharge Command. . . . .              | 346 |

| Figure 77. Multibank Write . . . . .                                       | 346 |

| Figure 78. Bt2166 Memory Initialization Sequence . . . . .                 | 347 |

| Figure 79. Bt2166AHF Packaging Diagram. . . . .                            | 372 |

## List of Tables

|                                                                                |    |

|--------------------------------------------------------------------------------|----|

| Table 1. Bt2166 PCI/AGP-Bus Pin Descriptions . . . . .                         | 10 |

| Table 2. DREF Registers Programmed by VGA CRT . . . . .                        | 29 |

| Table 3. VGA Register Writes — Trigger CRT DREF Programming Sequence . . . . . | 30 |

| Table 4. Other VGA Writes that Trigger DREF Registers Writes . . . . .         | 30 |

| Table 5. Bt2166 I/O Address Map . . . . .                                      | 37 |

| Table 6. Set/Reset Register . . . . .                                          | 39 |

| Table 7. Enable Set/Reset Register . . . . .                                   | 40 |

| Table 8. Color Compare Register . . . . .                                      | 40 |

| Table 9. Data Rotate Register . . . . .                                        | 41 |

| Table 10. Read Map Select Register . . . . .                                   | 41 |

| Table 11. Mode Register . . . . .                                              | 42 |

| Table 12. Graphics Controller: Miscellaneous Register . . . . .                | 43 |

| Table 13. Color Don't Care Register . . . . .                                  | 43 |

| Table 14. Bit Mask Register . . . . .                                          | 44 |

| Table 15. PLL 25 MHz and 28 MHz Select Registers . . . . .                     | 46 |

| Table 16. GRP_GUI_BASE Address Register . . . . .                              | 47 |

| Table 17. VGA Status Register . . . . .                                        | 48 |

| Table 18. GRP_PIO_ENABLE Register . . . . .                                    | 49 |

| Table 19. GRP_PIO_DATA Register . . . . .                                      | 50 |

| Table 20. Configuration Register A (GRP_CFGA) . . . . .                        | 51 |

| Table 21. Configuration Register 9 (GRP_CFG9) . . . . .                        | 51 |

| Table 22. Configuration Register 8 (GRP_CFG8) . . . . .                        | 51 |

| Table 23. Configuration Register 7 (GRP_CFG7) . . . . .                        | 52 |

| Table 24. Configuration Register 6 (GRP_CFG6) . . . . .                        | 52 |

| Table 25. Configuration Register 5 (GRP_CFG5) . . . . .                        | 52 |

| Table 26. Configuration Register 4 (GRP_CFG4) . . . . .                        | 53 |

| Table 27. Configuration Register 3 (GRP_CFG3) . . . . .                        | 53 |

| Table 28. Configuration Register 2 (GRP_CFG2) . . . . .                        | 54 |

| Table 29. Configuration Register 1 (GRP_CFG1) . . . . .                        | 54 |

| Table 30. Configuration Register 0 (GRP_CFG0) . . . . .                        | 54 |

| Table 31. Clocking Mode Register . . . . .                                     | 56 |

| Table 32. Shift and Load Control Bits . . . . .                                | 57 |

| Table 33. Map Mask Register . . . . .                                          | 57 |

| Table 34. Character Map Select Register . . . . .                              | 58 |

| Table 35. Secondary Font Selection . . . . .                                   | 58 |

| Table 36. Primary Font Selection . . . . .                                     | 59 |

|                                                                                                     |     |

|-----------------------------------------------------------------------------------------------------|-----|

| Table 37. Memory Mode Register .....                                                                | 59  |

| Table 38. Sequencer Unlock Register .....                                                           | 60  |

| Table 39. End Horizontal Blank Register .....                                                       | 63  |

| Table 40. End Horizontal Sync Register .....                                                        | 64  |

| Table 41. Overflow Register .....                                                                   | 64  |

| Table 42. Preset Row Scan Register .....                                                            | 65  |

| Table 43. Character Height Register .....                                                           | 65  |

| Table 44. Cursor Start Register .....                                                               | 65  |

| Table 45. Cursor End Register .....                                                                 | 66  |

| Table 46. End Vertical Sync Register .....                                                          | 68  |

| Table 47. Underline Register .....                                                                  | 69  |

| Table 48. Mode Control Register .....                                                               | 70  |

| Table 49. Attribute Index/Data Port Register .....                                                  | 71  |

| Table 50. Read Data Port Register .....                                                             | 72  |

| Table 51. Palette Registers .....                                                                   | 72  |

| Table 52. Mode Control Register .....                                                               | 73  |

| Table 53. Color Plane Enable Register .....                                                         | 74  |

| Table 54. Horizontal Panning Register .....                                                         | 74  |

| Table 55. Allowable Pixel Pans .....                                                                | 75  |

| Table 56. Color Select Register .....                                                               | 75  |

| Table 57. Input Status #0 Register .....                                                            | 76  |

| Table 58. Input Status #1 Register .....                                                            | 77  |

| Table 59. Miscellaneous Output Register (Read and Write) .....                                      | 77  |

| Table 60. Color Registers: DAC State Register .....                                                 | 79  |

| Table 61. GRP_I2C_CTRLW Control Register .....                                                      | 83  |

| Table 62. GRP_I2C_CTRLR Control Register .....                                                      | 84  |

| Table 63. I <sup>2</sup> C Master Receive Data GRP_I2C_MDATA .....                                  | 85  |

| Table 64. I <sup>2</sup> C Master Read Control Register GRP_I2C_MCTRLR[7:0] Bit Descriptions .....  | 87  |

| Table 65. GRP_I2C_MCTRLR Current Bit .....                                                          | 88  |

| Table 66. Example of Reading GRP_I2C_MCTRLR Register .....                                          | 88  |

| Table 67. I <sup>2</sup> C Master Write Control Register GRP_I2C_MCTRLW[7:0] Bit Descriptions ..... | 89  |

| Table 68. Example of writing to GRP_I2C_MCTRLW .....                                                | 90  |

| Table 69. I <sup>2</sup> C Slave Receive DATA GRP_I2C_SDATA .....                                   | 94  |

| Table 70. I <sup>2</sup> C Slave Read Control Register GRP_I2C_SCTRLR[7:0] Bit Descriptions .....   | 95  |

| Table 71. GRP_I2C_SCTRLR Current Bit .....                                                          | 96  |

| Table 72. Examples of Reading GRP_I2C_SCTRLR[7:0] Bits .....                                        | 96  |

| Table 73. I <sup>2</sup> C Slave Write Control Register GRP_I2C_SCTRLW[7:0] Bit Descriptions .....  | 97  |

| Table 74. Example of Writing to GRP_I2C_SCTRLW .....                                                | 100 |

| Table 75. Submap Read/Write Characteristics .....                                                   | 108 |

| Table 76. Address Fields For GUI Accesses .....                                                     | 110 |

| Table 77. GUI Commands .....                                                                        | 112 |

|                                                                          |     |

|--------------------------------------------------------------------------|-----|

| Table 78. BLT Command .....                                              | 114 |

| Table 79. XY Address Format .....                                        | 115 |

| Table 80. RWGUIDATA Command .....                                        | 115 |

| Table 81. RWGUIDATA_LENGTH.....                                          | 116 |

| Table 82. LINE Command .....                                             | 116 |

| Table 83. QMARK Command.....                                             | 117 |

| Table 84. QMARK Command P0 Bit Definition .....                          | 117 |

| Table 85. GUI Register.....                                              | 118 |

| Table 86. Bitmap Context Registers.....                                  | 120 |

| Table 87. Bitmap Register OFFSET Field for DRAM .....                    | 121 |

| Table 88. Bitmap Register TYPE Field.....                                | 121 |

| Table 89. Bitmap Register OFFSET Field for PCI .....                     | 121 |

| Table 90. Bitmap Register PITCH Field.....                               | 122 |

| Table 91. Example Bitmap Context Register Allocation.....                | 122 |

| Table 92. GUI Command Register (GUIREG_CMD) .....                        | 123 |

| Table 93. GUI Configuration Register (GUIREG_CFG).....                   | 124 |

| Table 94. Foreground Color Register.....                                 | 126 |

| Table 95. Background Color Register .....                                | 126 |

| Table 96. Destination XY Increment.....                                  | 127 |

| Table 97. BLT Control Register .....                                     | 128 |

| Table 98. Line Control Register .....                                    | 129 |

| Table 99. Bresenham 0, Address Register .....                            | 130 |

| Table 100.Bresenham 0, Error Register .....                              | 131 |

| Table 101.Bresenham 0, Constant K1 .....                                 | 131 |

| Table 102.Bresenham 0, Constant K2 .....                                 | 131 |

| Table 103.Bresenham 0, Increment 1 and 2 Registers.....                  | 132 |

| Table 104.Bresenham 0 Length Register .....                              | 132 |

| Table 105.GUI FIFO Register (GUIREG_FIFO) .....                          | 133 |

| Table 106.GUI FIFO Depth Register (GUIREG_DEPTH).....                    | 135 |

| Table 107.GUI MBA Control Register.....                                  | 136 |

| Table 108. Interrupt Status, Mask, and State Register Bits (INT_SR)..... | 138 |

| Table 109.Interrupt Firing Register .....                                | 139 |

| Table 110. ROM, BIOS, Monitor, VGA Sleep, Sync Configuration.....        | 141 |

| Table 111. Synchronous Memory Configuration Register (MEM_CFG) .....     | 143 |

| Table 112.General Status Register (GEN_STATUS) .....                     | 145 |

| Table 113.Memory Clock PLL Register (MEMCLK_PLL) .....                   | 145 |

| Table 114.Pixel Clock PLL Register (PIXCLK_PLL) .....                    | 146 |

| Table 115.GUI Clock PLL Register (GUICLK_PLL) .....                      | 146 |

| Table 116.System Clock PLL Register (SYSCLK_PLL) .....                   | 147 |

| Table 117.Memory Delay Register (MEM_DELAY) .....                        | 147 |

| Table 118.INIT STRUCTURE .....                                           | 152 |

|                                                                        |     |

|------------------------------------------------------------------------|-----|

| Table 119. Capture Control Structure DWORD0 .....                      | 153 |

| Table 120. Capture Control Structure DWORD1 .....                      | 154 |

| Table 121. Capture Control Structure DWORD2 .....                      | 155 |

| Table 122. Capture Control Structure DWORD3 .....                      | 155 |

| Table 123. FIFO Command (FIFO_COMMAND) .....                           | 167 |

| Table 124. FIFO Address Register (FIFO_ADDR) .....                     | 167 |

| Table 125. VIP Register Write (REG_WR_DATA) .....                      | 167 |

| Table 126. VIP Command and Byte Count Register (REG_COMMAND) .....     | 168 |

| Table 127. VIP Register Read (REG_RD_DATA) .....                       | 168 |

| Table 128. VIP Configuration Register (VIP_CNFG) .....                 | 169 |

| Table 129. Video Control Register (VID_VCR) .....                      | 170 |

| Table 130. Video One Register (VID_V1R) .....                          | 171 |

| Table 131. Video Two Register (VID_V2R) .....                          | 171 |

| Table 132. Video Three Register (VID_V3R) .....                        | 172 |

| Table 133. Video Address Register (VID_VAR) .....                      | 172 |

| Table 134. Video DDA Register (VID_DDA) .....                          | 173 |

| Table 135. Video Status Register (VID_STAT) .....                      | 174 |

| Table 136. Video Timing Generation Vertical Register (VID_GNV) .....   | 175 |

| Table 137. Video Timing Generation Horizontal Register (VID_GNH) ..... | 176 |

| Table 138. Video Timing Generation Control Register (VID_GNC) .....    | 176 |

| Table 139. Internal Register Memory Mapping .....                      | 180 |

| Table 140. Configuration Register Bit Assignments .....                | 185 |

| Table 141. Graphics Size Register .....                                | 187 |

| Table 142. Status Register Bit Mapping .....                           | 191 |

| Table 143. Timing Generator Control Register Bit Mapping .....         | 193 |

| Table 144. Horizontal Sync Register .....                              | 195 |

| Table 145. Horizontal Blank Register .....                             | 195 |

| Table 146. Horizontal Active Register .....                            | 195 |

| Table 147. Horizontal Video Register .....                             | 196 |

| Table 148. Horizontal Midline Register .....                           | 196 |

| Table 149. Vertical Sync Register .....                                | 196 |

| Table 150. Vertical Blank Register .....                               | 197 |

| Table 151. Vertical Active Register .....                              | 197 |

| Table 152. Vertical Video Register .....                               | 197 |

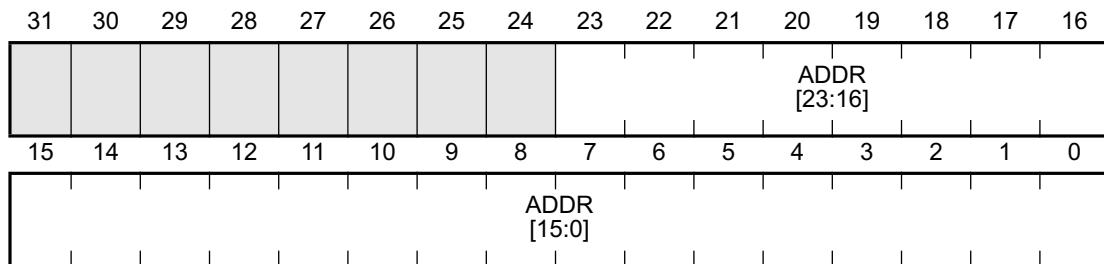

| Table 153. Timing Position Register .....                              | 197 |