## E1 Controller With Physical Line Interface

The Bt8510 is a highly integrated E1/CEPT transceiver that performs framing, control, and monitoring of E1 and Integrated Services Digital Network (ISDN) Primary Rate signals operating at 2.048 Mb/s. The Bt8510 is compatible with popular E1/CEPT framing standards such as ITU-T Recommendations G.704 (PCM-30), G.732 (CAS), and G.706 (CRC-4). The two-frame Pulse Code Modulation (PCM) slip buffer adapts the receive clock and data directly to the system serial bus timing. The signaling buffer provides signaling state freeze as well as resychronization to the system multiframe timing. The integral physical line interface features an adaptive analog receiver for clock and data recovery and a transmit line driver with pulse shaping (per G.703) for connecting to 75 or 120  $\Omega$  cables via external transformers.

Comprehensive ISDN D-channel support is provided for Time Slot 16 (TS16) via an integral LAPD controller with separate 16-byte transmit and receive buffers. The LAPD controller features zero stuffing and removal, flag and abort sequence detection and generation, and 16-bit Frame Check Sequence (FCS) generation and detection. Common Channel Signaling (CCS) or unformatted data may be processed through this buffer as well.

A parallel 8-bit microprocessor interface permits access to a series of 8-bit registers for control, error and alarm monitoring, and data link supervision. Error counters accumulate line code violations and CRC-4 and Frame Alignment Signal (FAS) errors. Access to Sa-bits and Far-End Block Error (FEBE) bits is provided for both transmit and receive directions. Per-channel control includes idle code word insertion, signaling insertion, and DS0 loopbacks to the network and equipment sides.

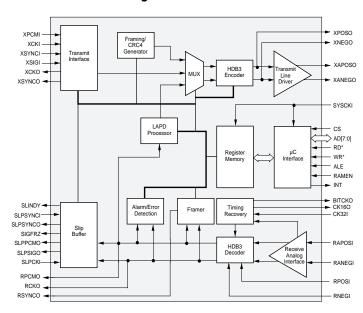

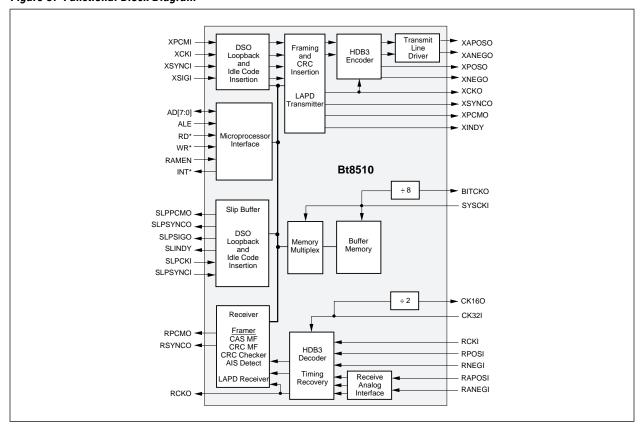

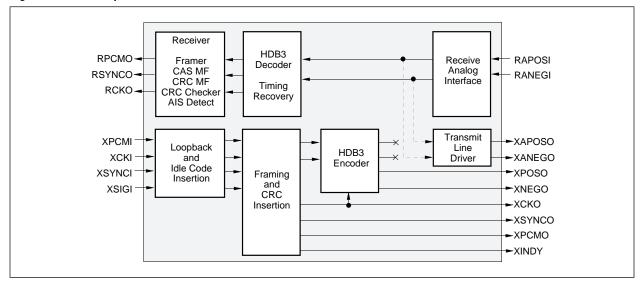

#### **Functional Block Diagram**

## Bt8510

#### **Distinguishing Features**

- Highly integrated E1/primary rate controller (2.048 Mb/s)

- Frames to E1/CEPT formats

- ITU-T G.704 (PCM-30)

- ITU-T G.732 (CAS)

- ITU-T G.706 (CRC-4)

- On-board physical line interface

- Receive clock and data recovery for up to 15 dB of cable attenuation

- Transmit line driver with G.703 pulse shaping

- Compatible with 75 and 120  $\Omega$  cables

- Two-frame slip buffer and rate converter

- Slip frame deletion/repetition

- Signaling freeze

- Compatible with the Bt8360 T1 controller (1.544 Mb/s)

- FEBE (E-bit) and Sa-bit access

- HDB3 zero-code suppression

- Parallel 8-bit microprocessor interface for control and status monitoring

- ISDN/Common Channel Signaling support

- 16-byte transmit and receive buffers

- Time Slot 16 LAPD processor

- Transparent unformatted mode

- Programmable transmit and receive time slot indication signals

- Counters for LCV, CRC-4, FAS errors

- Extensive per-channel control

- Programmable code word insertion

- Signaling insertion and extraction

- Diagnostic loopbacks

- Payload loopback to network

- Per DS0 channel loopback to network

- Local loopback to equipment side

#### **Applications**

- PCM Digital Switches

- E1 CSU/DSUs

- E1/E3 Multiplexers

- Digital Access Cross-connect Systems ISDN Primary Rate Access Ports

- SDH Add/Drop Multiplexers

- ATM Switches/Multiplexers

## **Ordering Information**

| Model Number | Package                                     | Ambient Temperature Range |  |

|--------------|---------------------------------------------|---------------------------|--|

| Bt8510EPJC   | 68-Pin Plastic Leaded Chip Carrier (J-Bend) | –40° to +85° C            |  |

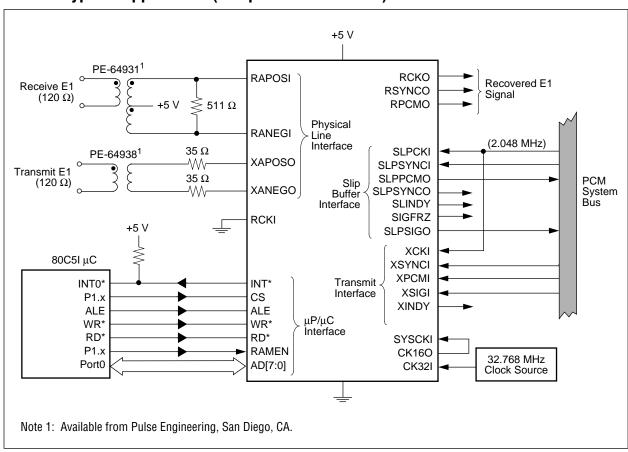

## **Bt8510 Typical Application (Simplified Schematic)**

Copyright © 1993, 1995 Brooktree Corporation. All rights reserved. Print date: 01/30/95

Brooktree reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished by Brooktree Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Brooktree Corporation for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent or patent rights of Brooktree Corporation.

Brooktree is a registered trademark of Brooktree Corporation. All other marks mentioned herein are the property of their respective holders

Specifications are subject to change without notice.

## **Table of Contents**

| esvi                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>S</b> vii                                                                                                                                                                                    |

| cription1                                                                                                                                                                                       |

| res and Modes of Operation                                                                                                                                                                      |

| escriptions 3                                                                                                                                                                                   |

| Description                                                                                                                                                                                     |

| iew11                                                                                                                                                                                           |

| Interface and Synchronization                                                                                                                                                                   |

| processor Interface14Control Interface14Address Map14Microprocessor Interrupts15                                                                                                                |

| nterface15Transmit Digital Line Interface17Receive Digital Line Interface17                                                                                                                     |

| mitter Operation18Input and Synchronization18Frame Alignment Signal and CRC Generation19Transmit Per-Channel Idle Code Insertion20External Signaling Insertion20Transmit Time Slot Indication21 |

| ver Operation                                                                                                                                                                                   |

| Timing Recovery 21 Bipolar-to-Unipolar Conversion 21 Receiver Output Timing 22 Framing Operation 22 Alarm Detection 23 AIS Signal Detection 23 Remote Frame Alarm Detection 23                  |

|                                                                                                                                                                                                 |

**Brooktree**®

Table of Contents Bt8510

|             | Status Data                                  | 23 |

|-------------|----------------------------------------------|----|

|             | Loss-of-Signal                               | 23 |

|             | Out-Of-Frame Alignment                       | 23 |

|             | Change of Frame Alignment                    | 23 |

|             | The Change of Multiframe Alignment           | 23 |

|             | Signaling Freeze Set                         | 24 |

|             | CRC Failure                                  | 24 |

|             | PCM Controlled Frame Slip                    | 24 |

|             | Uncontrolled Frame Slip                      | 24 |

|             | PCM Slip Buffer Operation                    | 24 |

|             | Slip Buffer Time Slot Indication             | 25 |

|             | Slip Buffer Short Delay Mode                 | 25 |

|             | Receive Signaling Buffer                     | 26 |

|             | Receive TS16 Signaling Insertion             | 26 |

| LAP         | PD Operation                                 | 27 |

|             | Transmitter                                  | 27 |

|             | Sending a Message                            |    |

|             | Aborting a Message                           |    |

|             | Transmitter Interrupts                       |    |

|             | Receiver                                     |    |

|             | Interrupts                                   | 30 |

|             |                                              |    |

| Registers . |                                              | 31 |

| Con         | itrol Registers                              | 31 |

|             | 0x00—Configuration Control Register (CR00)   |    |

|             | 0x01—Framer/Timing Control Register (CR01)   |    |

|             | 0x02—TS16 Control Register (CR02)            |    |

|             | CAS/CCS Mode Operation                       |    |

|             | LAPD Mode Operation                          |    |

|             | 0x03—Framing Pattern Control Register (CR03) |    |

|             | Sa-Bit Registers                             |    |

|             | 0x04—Sa4 Bits (CR04)                         |    |

|             | 0x05—Sa5 Bits (CR05)                         | 37 |

|             | 0x06—Sa6 Bits (CR06)                         | 37 |

|             | 0x07—Sa7 Bits (CR07)                         | 38 |

|             | 0x08—Sa8 Bits (CR08)                         | 38 |

|             | 0x0F—Interrupt Control Register (CR09)       | 38 |

| Stat        | tus Registers                                | ვი |

| Glai        | 0x10—Maintenance Status Register (SR00)      |    |

|             | 0x10—Maintenance Status Register (SR00)      |    |

|             | 0x12—TS16 Status Register (SR02)             |    |

|             | CAS/CCS Mode                                 |    |

|             | LAPD Mode Operation                          |    |

|             | L/N D WOUL Opticuon                          | ΤĹ |

iv Brooktree\*

Bt8510 Table of Contents

| UX 13—F              | ranning Pattern Status Register (SRO3)                    | 42 |

|----------------------|-----------------------------------------------------------|----|

| Sa-Bit R             | egisters                                                  |    |

|                      | 0x14–Sa4 Bits (SR04)                                      |    |

|                      | 0x15—Sa5 Bits (SR05)                                      |    |

|                      | 0x16—Sa6 Bits (SR06)                                      | 43 |

|                      | 0x17—Sa7 Bits (SR07)                                      | 43 |

|                      | 0x18—Sa8 Bits (SR08)                                      | 44 |

| 0x19—F               | Part Number and Hardware Version Register (SR09)          | 44 |

| Error Counters       |                                                           | 44 |

|                      | _ine Code Violation Counter (SR10)                        |    |

|                      | CRC Error Counter (SR11)                                  |    |

|                      | Frame Alignment Signal Error Counter (SR12)               |    |

|                      | nterrupt Status Register (SR13)                           |    |

|                      | egisters                                                  |    |

|                      |                                                           |    |

|                      | (0F, 0x10-0x1F—Per-Channel Control Registers (RXCR, TXCR) |    |

| UX2U-UX              | (3F—Receive Idle Code (RXIDLE)                            |    |

| 0.40 0.              | Receive Idle Code Word Format                             |    |

| UX4U-UX              | 45F—Receive PCM Buffer Low (RXLBUF)                       |    |

| 0,460 0,             | Low Slip Buffer PCM Word Format                           |    |

| 00000                | <7F—Receive PCM Buffer High (RXHBUF)                      |    |

| 0v80_0v              | 49F—Receive TS16 Buffer (RXTS16)                          |    |

| 0.00-0.2             | CAS or CCS Signaling Format                               |    |

|                      | LAPD Message Byte Format                                  |    |

| ΛνΔΛ_Λ               | KBF—Transmit Idle Code (TXIDLE)                           |    |

| 0AA0-07              | Transmit Idle Code Word Format                            |    |

| 0xC0=0x              | KDF—Transmit PCM Buffer (TXBUF)                           |    |

| 0,00 0,              | Transmit PCM Word Format                                  |    |

| 0xF0=0x              | KEF—Receive TS16 Signaling Insertion Buffer (RXTS16SIG)   |    |

| 0/L0 0/              | Receive TS16 Signaling Format                             |    |

| 0xF0-0x              | FF—Transmit TS16 Buffer (TXTS16)                          |    |

|                      | CAS or CCS Signaling Format                               |    |

|                      | LAPD Message Byte Format                                  |    |

| Register Summa       | ry                                                        | 51 |

| Electrical and Mecha | nical Specifications                                      | 57 |

| AC Characteristic    | cs                                                        | 57 |

|                      | cs                                                        |    |

|                      |                                                           |    |

|                      | nterface = 68HC11                                         |    |

| wiicroprocessor i    | nterface – 80C51                                          |    |

| Environmental C      | onditions                                                 |    |

|                      | Power Requirements and Temperature Range                  | 64 |

|                      |                                                           |    |

Table of Contents Bt8510

| Mechanical Specifications                                                        | 6  |

|----------------------------------------------------------------------------------|----|

| Appendix A                                                                       | 67 |

| Application Circuits                                                             | 67 |

| Transmitter                                                                      |    |

| Receiver                                                                         |    |

| Appendix B                                                                       | 69 |

| Bt8510 Analog Drop and Insert in a Local Area Network                            | 69 |

| Introduction                                                                     | 69 |

| Performance                                                                      |    |

| Network Timing                                                                   | 69 |

| Signaling and Control Protocol                                                   | 70 |

| Sa4[7:0]                                                                         | 70 |

| Sa5[7:0]                                                                         | 70 |

| Sa6[7:0]                                                                         | 70 |

| Sa7[7:0]                                                                         |    |

| Sa8[7:0]                                                                         |    |

| Maintenance                                                                      | 70 |

| Appendix C                                                                       | 7  |

| Bt8510 Return Loss, Receive Termination, and Receiver Jitter Tolerance           | 7  |

| Return Loss                                                                      |    |

| Receiver                                                                         | 7  |

| Transmitter                                                                      | 72 |

| Receive Termination                                                              | 73 |

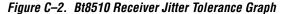

| Receiver Jitter Tolerance                                                        | 74 |

| Appendix D                                                                       | 75 |

| Bt8510 Receiver Sensitivity and Signal Reflection Immunity                       | 75 |

| Introduction                                                                     | 7  |

| Receiver Sensitivity                                                             |    |

| Signal Reflection Immunity                                                       | 70 |

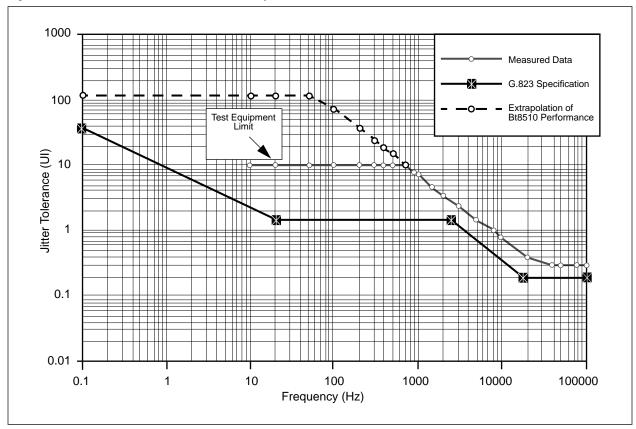

| Equipment                                                                        |    |

| Appendix E                                                                       | 77 |

| A Phase-Locked Loon (PLL) to Meet ITIL-T G. 823 .litter Attenuation Requirements | 77 |

Bt8510 List of Figures

## **List of Figures**

| Figure 1.   | Bt8510 Pinout Diagram                               | 3    |

|-------------|-----------------------------------------------------|------|

| Figure 2.   | Bt8510 Functional Pinout                            | 5    |

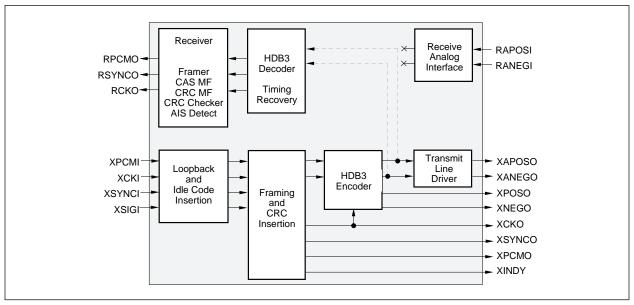

| Figure 3.   | Functional Block Diagram                            | 12   |

| Figure 4.   | Clock Signals                                       | . 13 |

| Figure 5.   | G.703 Isolated Pulse Template                       | . 16 |

| Figure 6.   | Transmitter Output                                  | . 17 |

| Figure 7.   | Clocked Receiver Input                              | . 17 |

| Figure 8.   | Unclocked Receiver Input                            | . 18 |

| Figure 9.   | Transmitter Input Timing and Synchronization Output | . 18 |

| Figure 10.  | Transmitter External Signaling Insertion            | . 20 |

| Figure 11.  | Receiver Output Timing                              | . 22 |

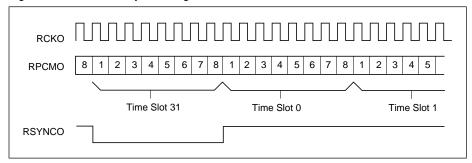

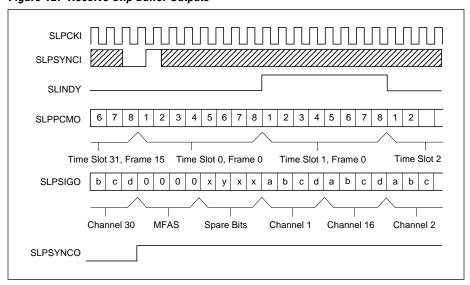

| Figure 12.  | Receive Slip Buffer Outputs                         | . 24 |

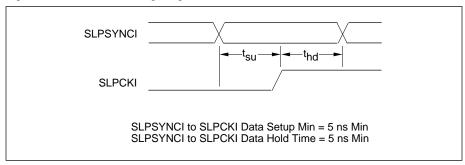

| Figure 13.  | SLPSYNCI Timing Diagram                             | . 25 |

| Figure 14.  | Local Loopback                                      | 36   |

| Figure 15.  | Line Loopback                                       | 37   |

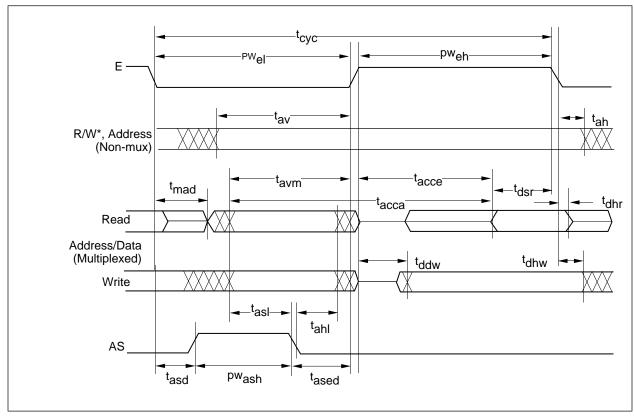

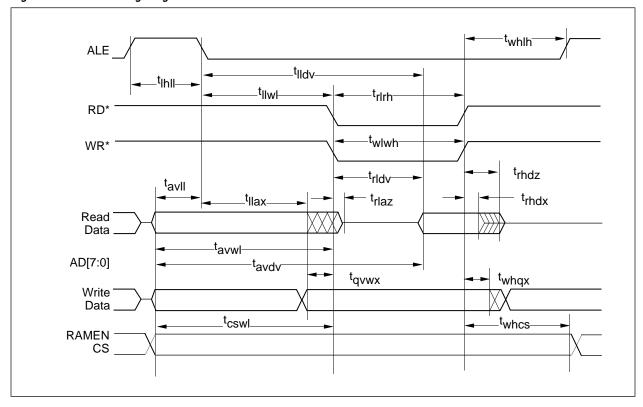

| Figure 16.  | 68HC11 Timing Diagram                               | 61   |

| Figure 17.  | 80C51 Timing Diagram                                | . 63 |

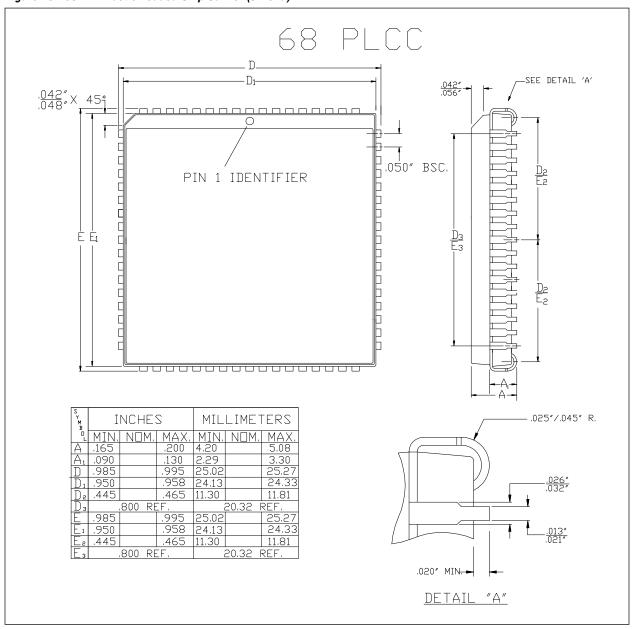

| Figure 18.  | 68-Pin Plastic Leaded Chip Carrier (J-Bend)         | 65   |

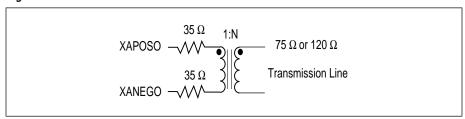

| Figure A-1. | Transmitter Transformer                             | . 67 |

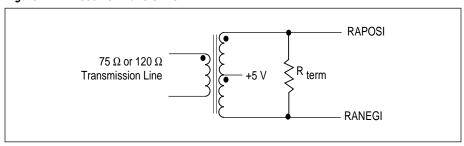

| Figure A–2. | Receiver Transformer                                | . 67 |

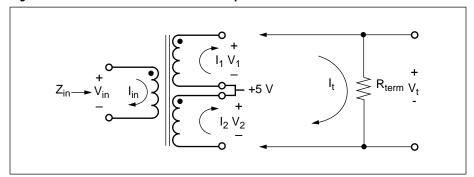

| Figure C-1. | Bt8510 Receive Termination Equivalent Circuit       | . 73 |

| Figure C–2. | Bt8510 Receiver Jitter Tolerance Graph              | 74   |

| Figure D-1. | Receiver Sensitivity Test Set-Up                    | 75   |

| Figure D–2. | Signal Reflection Immunity Test Set-Up              | 76   |

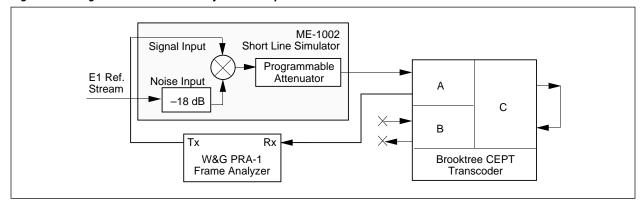

| Figure E–1. | System Clock Dejittering                            | . 77 |

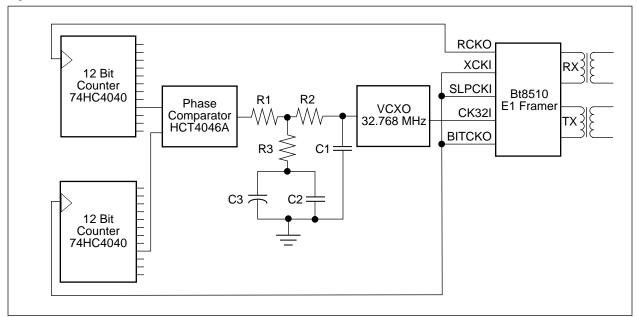

| Figure E–2. | 32.768 MHz VCXO                                     | 78   |

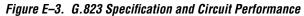

| Figure E–3. | G.823 Specification and Circuit Performance         | 79   |

|             |                                                     |      |

Brooktree\* vii

List of Tables Bt8510

## **List of Tables**

| Table 1.  | Bt8510 Pin Assignments                   | 4   |

|-----------|------------------------------------------|-----|

| Table 2.  | Hardware Signal Definitions              | . 6 |

| Table 3.  | Time Slot 0 Control                      | 32  |

| Table 4.  | Control Registers                        | 51  |

| Table 5.  | Status Registers                         | 52  |

| Table 6.  | Receive Per-Channel Control Registers    | 52  |

| Table 7.  | Transmit Per-Channel Control Registers   | 53  |

| Table 8.  | Receive Idle Code                        | 53  |

| Table 9.  | Receive PCM Buffer Low and High          | 53  |

| Table 10. | Receive TS16 Buffer                      | 54  |

| Table 11. | Transmit Idle Code                       | 54  |

| Table 12. | Transmit PCM Buffer                      | 54  |

| Table 13. | Receive TS16 Signaling Insertion Buffer  | 55  |

| Table 14. | Transmit TS16 Buffer                     | 55  |

| Table 15. | Delay Characteristics                    | .57 |

| Table 16. | Analog Interface Characteristics         | .58 |

| Table 17. | DC Characteristics                       | 59  |

| Table 18. | 68HC11 MPU Bus Interface Characteristics | .60 |

| Table 19. | 80C51 MPU Bus Interface Characteristics  | 62  |

| Table 20. | Absolute Maximum Ratings                 | 64  |

viii Brooktree\*

# **Product Description**

## Features and Modes of Operation

This specification describes the Bt8510 E1 (often called CEPT or DS1A) frame synchronization, signal generation, and recovery circuit for application in digital terminal interfaces operating at 2.048 Mb/s. Applications for this device include digital cross-connect systems, digital loop concentrators, DCME equipment, customer premise multiplexers, network managers, and PBXs. The circuit operates with Integrated Services Digital Network (ISDN) primary rate digital streams operating at a data rate of 2.048 Mb/s according to ITU-T Recommendation G.703.

The E1 framer is designed to meet the basic requirements of ITU-T Recommendation G.704. It can be used in the development of equipment to conform with ITU-T G.703 (§ 6), G.704 (§ 2.3 and § 3.3), G.705 (§ 3), G.706, G.732, G.735, G.736, G.737, G.761, and G.823 (jitter tolerance).

The physical line interface is included on-chip, accommodating both 75 ohm and 120 ohm cables. Data and clock can be recovered from received signals with up to -12 dB (120 ohm cables) and -15 dB (75 ohm cables) of attenuation. The analog circuits in the physical line interface may be powered-down if unused. Digital logic-level inputs and outputs are also provided for this case.

For ISDN applications, additional functions are provided to meet the requirements of ITU-T I.431, I.604 and G.962. These functions include LAPD formatting in Time Slot 16 (TS16), full access to the Sa bits on a multiframe basis, line loopback, per-DS0 loopbacks, idle code word insertion, and comprehensive CRC-4 functions.

An off-line framer is provided in the receiver. The framer has an average reframe time to the Frame Alignment Signal (FAS) of about 1 ms. Separate multiframe synchronization circuits are provided in the receiver for recovery of received Channel Associated Signaling (CAS) and the CRC-4 multiframe signals. CRC-4 error checking is performed and Far-End Block Error (FEBE) bits are transmitted in accordance with G.706 if these modes are enabled.

Through an 8-bit parallel interface, an external microprocessor or microcontroller can monitor all status conditions, provide configuration control, and access signaling and PCM data. The processor interface uses a multiplexed address/data bus, and can be directly connected to Intel 8051 and Motorola 68HC11 microcontrollers, without glue logic.

Individual 16-byte buffers are provided for both transmit and receive data in Time Slot 16 (one 16-byte buffer per direction). In CAS mode, this corresponds to a full multiframe. In LAPD mode, this may only be a partial message (multiframe synchronization is irrelevant). LAPD flag generation and detection (idle and abort bytes), FCS generation and checking, and zero stuffing and removal are provided. General-purpose unformatted data may be processed through the TS16 buffers including Common Channel Signaling (CCS).

The Bt8510 provides for both transmit and receive synchronization to a multi-frame reference. To enable received signal synchronization to a single clock reference, the receive circuitry provides slip buffers and signaling reinsertion. The slip buffer removes all input jitter because slip buffer outputs are synchronized to the local system clock. Signaling freeze is provided during an out-of-frame or -multiframe synchronization condition. This prevents updating of the received signaling bit register from TS16, unless framing is valid. An optional short-delay mode allows specialized use of the slip buffer for delay-sensitive applications such as wireless communication systems.

Fixed PCM idle codes can be optionally inserted in the transmitted PCM data stream from a buffer that is loaded by the host processor. Each of the 32 time slots in the E1 signal has a corresponding control word that allows the transmitted PCM to be set on a DS0 basis. This feature may also be used to insert errors in the transmitted framing pattern. CAS or CCS can be inserted via a 16-byte register that is optionally inserted into TS16, passed through from the Transmit PCM In pin (XPCMI), or inserted serially onto an external pin (XSIGI). This per-channel control word is also used to control the transmit time slot indication signal (XINDY).

Received CAS is recovered from TS16 and loaded into the receive TS16 signaling buffer. This buffer has two multiframes of memory that allow the old signaling information to be retained in the event of an out-of-frame or multiframe synchronization condition. Signaling data is provided on an external pin (SLPSIGO) and also multiplexed in the full rate stream as it is received (it may also be read via the microprocessor port).

PCM insertion of a fixed data pattern is also provided in the receive PCM stream on a DS0 basis. Receive data and signaling insertion can be similarly provided on a per-channel basis.

The Alarm Indication Signal (AIS) consisting of all-ones may be inserted on the full E1 signal or in TS16 only.

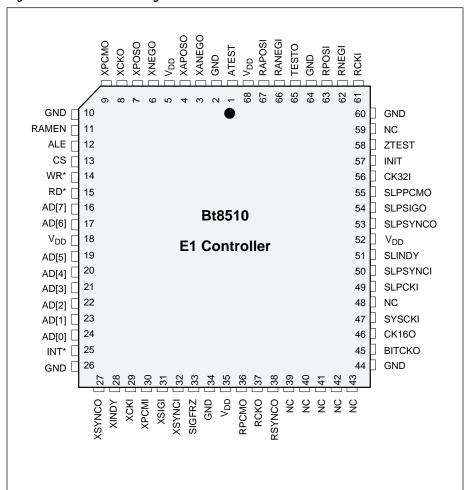

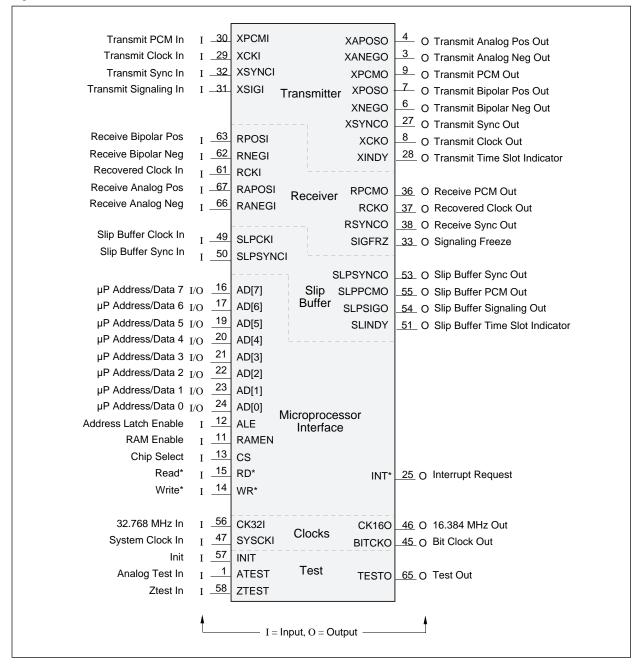

## Pin Descriptions

The Bt8510 is packaged in a 68-pin Plastic Leaded Chip Carrier (PLCC). Figure 1 illustrates the pinout. Pin assignments are listed in numerical order in Table 1. Figure 2 illustrates a functionally partitioned diagram of the Bt8510. Pin descriptions, labels, and I/O assignments are listed in Table 2. Unused inputs should be tied high or low to avoid floating inputs. No Connect (NC) pins should be left unconnected unless they are connected to signals to provide socket compatibility with the Bt8360 T1 Controller.

Figure 1. Bt8510 Pinout Diagram

Brooktree\*

Table 1. Bt8510 Pin Assignments

| Pin | Pin Label       | I/O | Pin | Pin Label       | I/O      |

|-----|-----------------|-----|-----|-----------------|----------|

| 1   | ATEST           | ı   | 35  | V <sub>DD</sub> | I        |

| 2   | GND             | I   | 36  | RPCMO           | 0        |

| 3   | XANEGO          | 0   | 37  | RCK0            | 0        |

| 4   | XAPOSO          | 0   | 38  | RSYNCO          | 0        |

| 5   | V <sub>DD</sub> | ı   | 39  | NC              | <b> </b> |

| 6   | XNEGO           | 0   | 40  | NC              | _        |

| 7   | XP0S0           | 0   | 41  | NC              | _        |

| 8   | XCKO            | 0   | 42  | NC              | _        |

| 9   | XPCMO           | 0   | 43  | NC              | _        |

| 10  | GND             | ı   | 44  | GND             | 1        |

| 11  | RAMEN           | I   | 45  | BITCKO          | 0        |

| 12  | ALE             | I   | 46  | CK160           | 0        |

| 13  | CS              | I   | 47  | SYSCKI          | 1        |

| 14  | WR*             | I   | 48  | NC              | _        |

| 15  | RD*             | I   | 49  | SLPCKI          | 1        |

| 16  | AD[7]           | 1/0 | 50  | SLPSYNCI        | I        |

| 17  | AD[6]           | I/O | 51  | SLINDY          | 0        |

| 18  | V <sub>DD</sub> | I   | 52  | V <sub>DD</sub> | I        |

| 19  | AD[5]           | 1/0 | 53  | SLPSYNCO        | 0        |

| 20  | AD[4]           | 1/0 | 54  | SLPSIG0         | 0        |

| 21  | AD[3]           | 1/0 | 55  | SLPPCM0         | 0        |

| 22  | AD[2]           | 1/0 | 56  | CK32I           | 1        |

| 23  | AD[1]           | 1/0 | 57  | INIT            | 1        |

| 24  | AD[0]           | 1/0 | 58  | ZTEST           | I        |

| 25  | INT*            | 0   | 59  | NC              | _        |

| 26  | GND             | I   | 60  | GND             | I        |

| 27  | XSYNCO          | 0   | 61  | RCKI            | 1        |

| 28  | XINDY           | 0   | 62  | RNEGI           | I/O      |

| 29  | XCKI            | I   | 63  | RPOSI           | I/O      |

| 30  | XPCMI           | I   | 64  | GND             | I        |

| 31  | XSIGI           | I   | 65  | TESTO           | 0        |

| 32  | XSYNCI          | I   | 66  | RANEGI          | I        |

| 33  | SIGFRZ          | 0   | 67  | RAPOSI          | I        |

| 34  | GND             | I   | 68  | V <sub>DD</sub> | I        |

|     |                 |     |     |                 |          |

Brooktree\*

Figure 2. Bt8510 Functional Pinout

**Table 2. Hardware Signal Definitions** (1 of 4)

|             | Pin Label | Signal Name                      | 1/0 | Definition                                                                                                                                                                                                                                                                                                              |

|-------------|-----------|----------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | XPCMI     | Transmit PCM In                  | I   | An input for unipolar transmit data. This data is sampled on the falling edge of the transmit clock, XCKI.                                                                                                                                                                                                              |

|             | XCKI      | Transmit Clock In                | I   | The framer transmit clock, nominally 2.048 MHz. The Configuration Register [CR00;0x00] can substitute the receive clock for loopback operation.                                                                                                                                                                         |

|             | XSYNCI    | Transmit Sync In                 | I   | The rising edge establishes the transmit multiframe timing for CAS and the TS0 timing. The falling edge is not relevant, except that the period high and low must be at least one cycle of the transmit clock. This signal may be connected to ground, and the resulting multiframe timing will be indicated by XSYNCO. |

|             | XSIGI     | Transmit Signaling In            | I   | Can be used to insert CAS or CCS mode signaling into the transmit bit stream, rather than from XPCMI or from the internal time slot 16 signaling buffer (TXTS16;0xF0–0xFF).                                                                                                                                             |

| er          | XPCM0     | Transmit PCM Out                 | 0   | Output for the unipolar NRZ data. Data changes on falling edges of XCKO.                                                                                                                                                                                                                                                |

| Transmitter | XP0S0     | Transmit Bipolar<br>Positive Out | 0   | Positive NRZ bipolar output. This pin is usually connected to the positive bipolar data input of an external line interface circuit.                                                                                                                                                                                    |

| <b>F</b>    | XNEGO     | Transmit Bipolar<br>Negative Out | 0   | Negative NRZ bipolar output. This pin is usually connected to the negative bipolar data input of an external line interface circuit.                                                                                                                                                                                    |

|             | XAPOSO    | Transmit Analog<br>Positive Out  | 0   | Analog line driver output for positive pulses on the E1 line. This pin drives a transformer through a series resistor.                                                                                                                                                                                                  |

|             | XANEGO    | Transmit Analog<br>Negative Out  | 0   | Analog line driver output for negative pulses on the E1 line. This pin drives a transformer through a series resistor.                                                                                                                                                                                                  |

|             | XSYNCO    | Transmit Sync Out                | 0   | Provides a transmit multiframe sync output. This signal will be derived from the frame sync input, XSYNCI. If XSYNCI is grounded, XSYNCO will free-run at a multiframe rate.                                                                                                                                            |

|             | хско      | Transmit Clock Out               | 0   | Repeats the transmit clock for timing the transmit outputs. If the receive timing is selected by the control register, that clock will be repeated here.                                                                                                                                                                |

|             | XINDY     | Transmit Time Slot<br>Indicator  | 0   | Indicates the input timing of those time slots programmed in the Transmit Per-Channel Control Registers [TXCR;0x10–0x1F].                                                                                                                                                                                               |

Brooktree\*

**Table 2. Hardware Signal Definitions** (2 of 4)

|          | Pin Label | Signal Name              | I/O | Definition                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-----------|--------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | RPCM0     | Receive PCM Out          | 0   | Recovered receive data output that is clocked out on the rising edges of RCKO. No insertion or buffering options are available.                                                                                                                                                                                                                                                       |

|          | RCKO      | Recovered Clock Out      | 0   | The recovered clock from the internal digital phase-locked loop (DPLL). If internal clock recovery is not enabled, then the receive input clock (RCKI) is repeated.                                                                                                                                                                                                                   |

|          | RSYNCO    | Receive Sync Out         | 0   | Receiver frame sync output. This output transitions high at the beginning of each 256-bit frame.                                                                                                                                                                                                                                                                                      |

|          | RPOSI     | Receive Bipolar Positive | 1/0 | Used as the positive pulse digital input from an external line interface circuit (TTL or CMOS logic-levels) if the internal analog interface is disabled. This input can also be used for unipolar data by grounding the RNEGI pin (or vice-versa). If the internal analog interface is enabled, this pin becomes an output for the positive bipolar pulses detected by the receiver. |

| Receiver | RNEGI     | Receive Bipolar Negative | 1/0 | Used as the negative pulse digital input from an external line interface circuit (TTL or CMOS levels) if the internal analog interface is disabled. This input can also be used for unipolar data by grounding the RPOSI pin (or vice-versa). If the internal analog interface is enabled, this pin becomes an output for the negative bipolar pulses detected by the receiver.       |

|          | RAPOSI    | Receive Analog Positive  | I   | Positive pulse from the line interface transformer. If the internal analog interface is disabled, this input should be tied to V <sub>DD</sub> .                                                                                                                                                                                                                                      |

|          | RANEGI    | Receive Analog Negative  | I   | Negative pulse from the line interface transformer. If the internal analog interface is disabled, this input should be tied to $V_{DD}$ .                                                                                                                                                                                                                                             |

|          | RCKI      | Recovered Clock In       | I   | Sourced by a line interface chip or local system. Optionally, internal timing recovery may be selected by setting the Enable Clock Recovery bit [EnClkRcv;CR00.0] in the Configuration Control Register [CR00;0x00], and supplying a 32.768 MHz clock to the CK32l pin.                                                                                                               |

|          | SIGFRZ    | Signaling Freeze Active  | 0   | When high, this output indicates the signaling freeze function is active. This signal is real-time and unlatched.                                                                                                                                                                                                                                                                     |

**Table 2. Hardware Signal Definitions** (3 of 4)

|                        | Pin Label | Signal Name                        | I/O | Definition                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|-----------|------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | SLPPCM0   | Slip Buffer PCM Out                | 0   | Recovered receive data with slip buffer timing. Idle code, loop-back, and signaling extraction options are available. Synchronization is established by SLPSYNCI and SLPCKI. PCM-controlled frame slips will occur if there is a long-term variation between the slip buffer clock and the receive clock. A short delay mode is also available for delay-sensitive applications. |

| 9                      | SLPCKI    | Slip Buffer Clock In               | I   | Used to read PCM data from the receive buffer memory, and to provide timing for SLPPCMO.                                                                                                                                                                                                                                                                                         |

| Slip Buffer Interface  | SLPSYNCI  | Slip Buffer Sync In                | I   | The rising edge on this pin establishes the multiframe sync reference by identifying the position of TSO, frame 0 for the slip buffer output. This input may be connected to ground, and the resulting multiframe timing will be indicated by SLPSYNCO.                                                                                                                          |

| Slip                   | SLPSYNCO  | Slip Buffer Sync Out               | 0   | The rising edge indicates the position of TS0 in frame 0 of the multiframe in the slip buffer PCM output, SLPPCMO.                                                                                                                                                                                                                                                               |

|                        | SLPSIG0   | Slip Buffer Signaling Out          | 0   | CAS or CCS mode signaling information is repeated here twice per frame in serial fashion. The TS16 information is always output here in any signaling mode. If there is not a 16-frame signaling multiframe, this output can be ignored.                                                                                                                                         |

|                        | SLINDY    | Slip Buffer Time Slot<br>Indicator | 0   | Indicates the output timing of those time slots programmed in the Receive Per-Channel Control Register [RXCR;0x00–0x0F].                                                                                                                                                                                                                                                         |

|                        | AD[7:0]   | Address/Data Bus                   | I/O | Multiplexed address and data bus to and from the host microprocessor or microcontroller.                                                                                                                                                                                                                                                                                         |

|                        | ALE       | Address Latch Enable               | I   | Timing signal from the microprocessor that latches the address onto the multiplexed address/data bus.                                                                                                                                                                                                                                                                            |

| croprocessor Interface | RD*, WR*  | Read, Write                        | I   | Active-low signals from the microprocessor that determine if the cycle is a read or write. If the RAMEN input is low, the control registers can be written or read and the status registers can only be read.                                                                                                                                                                    |

| cessor                 | RAMEN     | RAM Enable                         | I   | Directs read or write operations to the buffer memory if high. If low, only the control and status registers can be accessed.                                                                                                                                                                                                                                                    |

| Micropro               | CS        | Chip Select                        | I   | Active-high signal from the microprocessor that selects the Bt8510 on a shared bus. If this signal is low, the framer will ignore any activity on the microprocessor bus.                                                                                                                                                                                                        |

|                        | INT*      | Interrupt Request                  | 0   | Active-low, open-drain output that interrupts the processor according to the selections made in the Interrupt Control Register [CR09;0x0F] and the Enable LAPD Formatting bit (EnLAPD-Fmt;CR01.7). The interrupt is cleared when the appropriate action has been taken.                                                                                                          |

Brooktree\*

9

**Table 2. Hardware Signal Definitions** (4 of 4)

|                     | Pin Label       | Signal Name          | I/O | Definition                                                                                                                                                                                                                                                                          |

|---------------------|-----------------|----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | CK32I           | 32.768 MHz Clock In  | Ī   | Drives the internal timing recovery circuit for the receive framer. If external clock recovery is provided, this input can be tied to ground or $V_{DD}$ , or used to generate a system clock (CK160) for connection to the SYSCKI input.                                           |

| Clocks              | SYSCKI          | System Clock In      | I   | System clock for the integrated circuit that is required for any operation. The duty cycle must be 45% to 55%. The frequency must be in the range of 8.0 MHz to 20.0 MHz.                                                                                                           |

|                     | CK160           | 16.384 MHz Clock Out | 0   | 32.768 MHz clock input (CK32I) divided by 2. This signal is present whenever the 32 MHz input is present. It can be connected to SYSCKI, if desired.                                                                                                                                |

|                     | BITCKO          | Bit Clock Out        | 0   | System clock (SYSCKI) divided by 8 that can be used as an input clock for the transmitter or slip buffer, as desired.                                                                                                                                                               |

|                     | ATEST           | Analog Test In       | I   | Enables analog test mode. Used for device test only and should be tied to ground.                                                                                                                                                                                                   |

|                     | ZTEST           | ZTest In             | I   | Active-high input that turns off the AD[7:0] bus three-state outputs. It is used for device and automated board testing. It should be tied low for normal operation.                                                                                                                |

| Test                | INIT            | Initialization       | I   | Active-high input that initializes the internal circuitry to a known state for device testing. It can also be used to synchronize multiple devices for use with a single microprocessor. If XSYNCI or SLPSYNCI are grounded, they will take their timing from the INIT reset pulse. |

|                     | TESTO           | Test Out             | 0   | Verifies correct operation of the analog interface circuitry during device testing. It is normally three-stated unless ATEST is high.                                                                                                                                               |

| g g                 | V <sub>DD</sub> | Power                |     | Five pins are provided for power.                                                                                                                                                                                                                                                   |

| Power and<br>Ground | GND             | Ground               |     | Seven pins are provided for ground.                                                                                                                                                                                                                                                 |

# Functional Description

## **Overview**

A block diagram of the Bt8510 E1 transceiver is shown in Figure 3 and consists of three major sections: receiver, slip buffer and transmitter. The receiver is comprised of the analog receiver, the timing recovery circuit, the HDB3 decoder and the framer which recovers synchronization and detects alarms and errors. The receive bipolar input data can be obtained from either an external Line Interface Unit (LIU) chip, or by using the internal analog receiver and the timing recovery circuit which consists chiefly of a Digital Phase Locked Loop (DPLL). The analog receiver uses adaptive decision levels to allow for up to 15 dB of cable loss. After clock and data have been recovered, HDB3 decoding is performed to remove zero-code suppression and to convert the bipolar data into a single unipolar data stream. The resulting serial data is then checked by the framer for the G.704 Frame Alignment Signal (FAS), the G.732 Channel Associated Signaling (CAS) multiframe, and the G.706 CRC-4 multiframe, if present.

Errors and alarm status are reported in registers accessible by the microprocessor. Data in time slot 16 (TS16) is routed to the receive TS16 buffer (RXTS16;0x80-0x9F) for microprocessor access to CAS/CCS signaling bits or for processing of message-oriented signaling by the internal LAPD receiver. The recovered serial data stream is made available as unipolar NRZ data on the RPCMO output pin; the receiver sync output (RSYNCO) transitions low-to-high at the beginning of each frame. Data in each received time slot is also written to the internal buffer memory (RXLBUF, RXHBUF;0x40-0x7F) where it is read by either the slip buffer, the transmitter (for payload or per-channel loopbacks), or the microprocessor. Two complete frames of receive data, including TS0 and TS16, are kept in the buffer memory.

The slip buffer reads the appropriate data from buffer memory and assembles the serial output stream at SLPPCMO. Idle code insertion and loopback functions can be performed only on the slip buffer output. (The receive per-channel controls actually refer to the slip buffer.) Controlled frame slips are performed when the slip buffer skips or repeats a frame (256 bits) of the receive buffer memory. Signaling freeze is also performed here, again by redirecting buffer read operations (and disabling receive data write operations). The slip buffer sync output (SLPSYNCO) is a multiframe sync, and transitions low-to-high at the beginning of TS0, frame 0 of the 16-frame multiframe. This sync output is compatible with the transmit sync input, which allows the direct connection of the slip buffer output to transmit input. The slip buffer time slot indication signal (SLINDY) can be

programmed to indicate any number of time slots for each frame, a feature useful in drop-and-insert applications.

The transmitter section comprises of the DS0, loopback and idle word insertion block; the framing and CRC-4 coding insertion block; the HDB3 encoder; and the differential transmit line driver. Transmit serial data and clock from the host are applied to XPCMI and XCKI, respectively. PCM idle codes, payload loopback, and TS16 insertions are performed under microprocessor control. TS0 insertion data includes the FAS frame sync pattern, CRC-4 information and various reserved bits. TS16 insertion functions include the CAS signaling multiframe alignment pattern and transmit signaling bits. These signaling bits can be sourced from the transmit signaling input (XSIGI), from the buffer memory as microprocessor-supplied data, or embedded in the PCM input data stream at the XPCMI pin. Alternatively, TS16 can be used for transmitting LAPD messages using the internal LAPD transmitter; message data is supplied by the microprocessor via the Transmit TS16 Buffer (TXTS16;0xF0–0xFF). All framing and internal data insertion can be disabled to transparently transmit data. The transmit time slot indication signal (XINDY) can be programmed to indicate any number of time slots for each frame, a feature useful in drop-and-insert applications.

The composite serial data is then routed to the HDB3 encoder which performs zero-code suppression (can be disabled for sending AMI data) as well as conversion to a bipolar data stream. The transmit line driver then interfaces this signal to the physical E1 line via an external transformer and resistors. Compatible with 75  $\Omega$  and 120  $\Omega$  cables, the line driver performs the necessary pulse template shaping specified in ITU-T G.703. Transmit bipolar (XPOSO, XNEGO) and unipolar NRZ (XPCMO) outputs are also provided for use with an external line interface device.

Figure 3. Functional Block Diagram

## Clock Interface and Synchronization

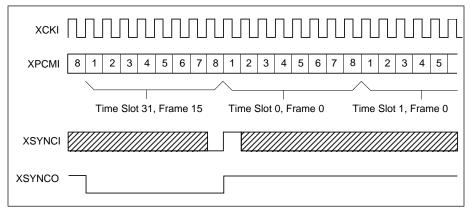

The Bt8510 has both a 32.768 MHz timing recovery clock input (CK32I) and an 8 MHz to 20 MHz System Clock Input (SYSCKI). The 32.768 MHz clock must have a duty cycle between 25% and 75%, and be accurate to within 0.01%. SYSCKI must have a duty cycle between 45% and 55% and can be in the range of 8.0 MHz to 20.0 MHz. A faster system clock increases the maximum data rate between the microprocessor and the internal RAM memory but at the expense of increased power dissipation. CK32I is used internally only by the internal DPLL for receive clock recovery; if the receive clock recovery is not being used, CK32I is not required. This clock is also divided by 2 and is provided at the CK16O output pin. If present this clock may be connected to SYSCKI when receive clock recovery is enabled.

SYSCKI is further divided by 8 to obtain a 2.048 MHz clock that can be used for the transmit clock, if desired. This signal is provided at the BITCKO output and can be used for other clock inputs such as SLPCKI or XCKI. If a system clock frequency other than 16.384 MHz is used, then the BITCKO output is then SYSCKI divided by 8.

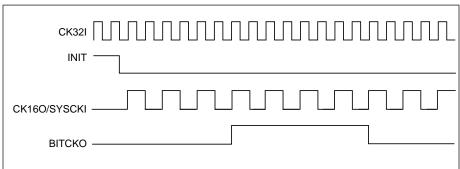

A timing diagram for the clock signals is shown in Figure 4. The initialization signal (INIT) is active-high, and can be used to synchronize the 16.384 MHz outputs for multiple Bt8510 devices on power-up.

Figure 4. Clock Signals

If several integrated circuits are to be synchronized, then the INIT and XSYNCI pins should be tied together. A common 32.768 MHz clock input (or 16.384 MHz clock input if the internal clock recovery is not used) can also be used. Such synchronization can make the collection of status information from a large number of Bt8510s faster and more convenient.

Brooktree\*

## Microprocessor Interface

The framer is managed by an external microprocessor or microcontroller. An integral interface to an Intel 8051-type controller, a Motorola 68HC11-type controller, or equivalent, is provided. A circuit within senses which type of processor (Intel or Motorola) is being used and adjusts itself automatically.

The Bt8510 is connected to a microprocessor exactly like static RAM. Two different kinds of registers can be read or written. *Direct* read and write operations access control and status registers. *Indirect* read and write operations access the 256 bytes of buffer memory when RAMEN is high. These bytes contain information associated with each channel or timeslot of the E1 signal.

#### **Control Interface**

The control interface to the Bt8510 consists of 14 pins: Address Latch Enable (ALE), Read Enable (RD\*), Write Enable (WR\*), Chip Select (CS), RAM Enable (RAMEN), eight multiplexed address/data bits (AD[7:0]), and Interrupt (INT\*).

The control interface is designed to allow the direct connection of an Intel 8051-type controller or equivalent, or a Motorola 68HC11-type controller or equivalent. The CS input to the Bt8510 allows the control of multiple devices from a single microprocessor or controller. INT\* is used for signaling and monitoring operations. It is active-low, and stays low until the interrupt condition is cleared.

The type of processor used is automatically sensed by looking at the state of the RD\* input when ALE is active (high). To use the Bt8510 with an 8051-type controller, connect ALE, WR\*, and RD\* of the 8051 to the corresponding inputs of the Bt8510. To use the Bt8510 with an HC11-type controller, connect AS of the HC11 to the ALE input of the Bt8510, Enable to RD\*, and Read/Write to WR\*. In both cases, the CS and RAMEN inputs can be driven by address lines or proper decodes of the address lines.

Detailed timing information is contained in the Electrical and Mechanical Specifications chapter.

## **Address Map**

The register address map for the Bt8510 is given in the Register Summary section of the Registers chapter. There are three types of registers: Control Registers, Status Registers, and Buffer Memory Registers. Control and Status Registers are located at addresses 0x00-0x1F when RAM Enable (RAMEN) is low. Buffer Memory Registers are located at addresses 0x00-0xFF, and require RAMEN to be high. CS must be high to address any registers within the Bt8510.

14 Brooktree®

#### **Microprocessor Interrupts**

One explicit interrupt signal (INT\*) is provided and can be triggered by one or more sources: an LAPD interrupt, an end-of-multiframe signal, an out-of-frame (OOF) event or a saturation of one of the error counters. The Interrupt Status Register [SR13;0x1F] is provided to aid in determining the source of the interrupt. The Interrupt Control Register [CR09;0x0F] controls the masking of these interrupt sources.

The microprocessor can be interrupted by either the Transmit Multiframe Sync Output signal (XSYNCO) or the Slip Multiframe Sync Output (SLPSYNCO) connected to the interrupt input of the microprocessor. These interrupts can be used to synchronize read and write operations to properly inject and extract TS16 signaling data to and from TS16 buffer memory. If the LAPD formatting operation is enabled, it can interrupt the microprocessor via the INT\* pin as well.

Depending on the options selected, an interrupt signal may have several different sources. In this case, the Interrupt Status Register must first be read to determine the source of the interrupt. The processor should be optioned for level-triggered interrupt operation.

To process status interrupts, read the Interrupt Status Register at each interrupt. If the counter interrupts are enabled in the Interrupt Control Register, read the Framing Pattern Status Register [SR03;0x13] for overflow indications for the LCV, CRC, or FAS error counters. The interrupt condition will clear once this register has been read.

## Line Interface

The receive analog interface allows direct connection to the physical E1 line via coupling transformers and two external terminating resistors. Line and local loop-backs are provided for maintenance purposes.

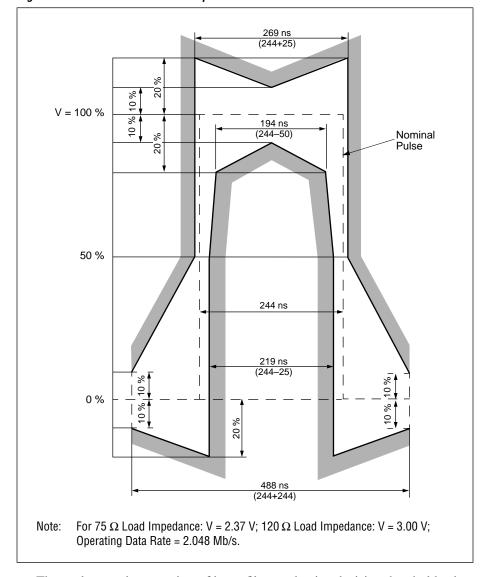

A pulse shaping, differential line driver is provided in the transmitter. This driver is always enabled; however, power drain will be negligible if the outputs are left open. Pulse shaping is performed internally so that with the recommended transformers and resistors, a transmitted signal will meet the pulse template requirements of ITU-T G.703 shown in Figure 5 (measured at the secondary side of the transformer with either a 75  $\Omega$  or 120  $\Omega$  termination). Refer to Appendices A, C and D of this document for more details about the transmit analog interface.

Figure 5. G.703 Isolated Pulse Template

The analog receiver consists of input filters, adaptive decision thresholds, data slicers, and Loss of Signal (LOS) detection. The maximum sensitivity is -18 dB, although cable characteristics may require a receive equalizer to operate reliably at that level. In general, -12 dB is possible on  $120~\Omega$  ABAM cable, and -15 dB on  $75~\Omega$  coax, without external equalization. Note that the use of the analog receiver also requires the use of internal clock recovery. A power-down mode reduces power drain from 20~mA (typical) to 0.5~mA (max).

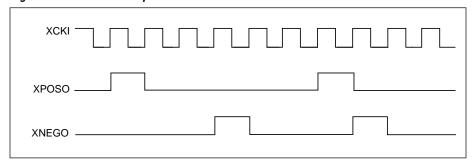

The transmit and receive *digital* interfaces allow connection of +5 V logic-level signals to and from other integrated circuits. The transmit digital interface includes the following logic-level signals: XPCMO (an output for transmit unipolar data), XCKO (the corresponding 2.048 MHz clock), and XPOSO/XNEGO (positive and negative full-width data outputs that may be connected to other physical line interface devices).

The receive digital interface includes the following logic-level signals: RPOSI/RNEGI (inputs for either full-width, clocked data or unclocked variable-width data) and RCKI (the corresponding clock for full-width data). A single unipolar data stream can be fed to either RPOSI or RNEGI as long as one of these two inputs is grounded. Two timing options are provided for the received E1 signals. The analog receiver may be configured via the Enable Clock Recovery bit (EnClkRcv;CR00.0) in the Configuration Register (CR00;0x00) for either clocked (external clock recovery) or unclocked (internal clock recovery) operation. In internal clock recovery mode, a high-performance DPLL adaptively divides the CK32I signal to match the phase and frequency of the incoming E1 signal. The resulting recovered clock samples the E1 signal for data recovery and is also used as write clock signal to the slip buffer and routed to the RCKO pin for use by the system.

#### **Transmit Digital Line Interface**

The transmit digital line interface signals are shown in Figure 6, illustrating a portion of a random data sequence (...01001001100...). Separate signal pins provide the appropriate output signal for positive and negative pulses. The outputs change on rising clock transitions of XCKI.

Figure 6. Transmitter Output

## **Receive Digital Line Interface**

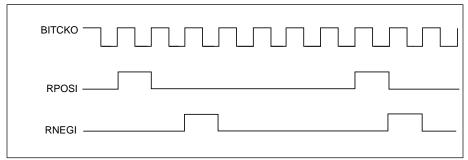

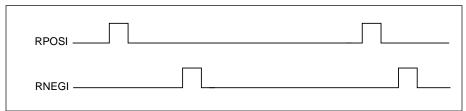

The receive digital line interface can be programmed for either clocked or unclocked operation. In clocked mode, an externally derived 2.048 MHz clock must be connected to RCKI. The input logic-level signal at RPOSI and RNEGI is internally sampled on the negative edges of RCKI as shown in Figure 7.

Figure 7. Clocked Receiver Input

If internal clock recovery is enabled (unclocked mode), the RCKI input is ignored, and the bipolar logic-level signals at RPOSI and RNEGI are sampled internally to recover clock and data. Each input pulse at RPOSI and RNEGI must have a duty cycle between 35% and 65%, as shown in Figure 8.

If desired, the receive input may be supplied as a unipolar data stream. In this configuration, the receive data must be clocked, and either the positive or negative input may be used (the unused input must be tied to ground). HDB3 decoding must also be turned off (EnAMI =1 in CR00.5) and the Line Code Violation Counter (SR10;0x1C) should be ignored.

Figure 8. Unclocked Receiver Input

## Transmitter Operation

Each transmitter circuit is synchronized to the transmit input data by an external synchronization signal (XSYNCI). This external synchronization signal sets the multiframe reference for transmitted signals.

## **Input and Synchronization**

The transmit inputs for the system PCM bus interface consists of the unipolar transmit input signal (XPCMI), clock (XCKI), and synchronization (XSYNCI). A multiframe synchronization output is provided at XSYNCO. The timing for these signals is shown in Figure 9.

Figure 9. Transmitter Input Timing and Synchronization Output

The system-side data input at XPCMI is synchronized to both the input clock at XCKI and the multiframe synchronization signal at XSYNCI, which can be either externally provided or taken from the multiframe synchronization signal output by the Bt8510 at XSYNCO. The timing of the transmit signals relative to the multiframe is shown in Figure 9. The clock frequency is 2.048 MHz. All transmit system-side inputs are internally sampled on the falling edge of XCKI while the outputs are clocked out on the rising edge.

The transmit synchronization input (XSYNCI) should have a low-to-high transition from the last bit of the multiframe's last frame to the first bit of the multiframe's first frame. If a 2-frame versus 16-frame multiframe is used, the synchronization input can cycle every other frame; however, this will disable the XSYNCO output, and will also continuously reset the CRC-4 multiframe count sequence prematurely. The XSYNCI signal should not transition at a rate faster than every other frame since framing generation errors will result if the Insert Framing bit [InsFrm;CR00.2] of the Configuration Register is enabled.

An alternative method of synchronization is provided when XSYNCI is tied to ground and XSYNCO is used by the system to synchronize the transmit data supplied to XPCMI. XSYNCO then runs at an internally determined 16-frame multiframe rate (a divide-by-4096 of the XCKI clock).

Either of the multiframe synchronization outputs (XSYNCO) or SLPSYNCO) can be used as an interrupt to indicate when the receiver status bits are updated. The multiframe synchronization signals transition low-to-high at the beginning of TSO, Frame 0 of the 16-frame multiframe.

#### Frame Alignment Signal and CRC Generation

The E1 framing insertion circuit includes three types of framing as specified in ITU-T G.704: basic frame alignment (FAS), CRC-4 multiframe alignment, and signaling multiframe alignment. While basic FAS framing is a requirement, the other types of multiframe alignment are optional and could be independent of each other. Signaling multiframe alignment is used only with Channel Associated Signaling (CAS) which employs time slot 16 to carry the signaling information for the 30 channels of PCM data. All automatic framing functions can be disabled in the following sections.

The G.704 E1 frame alignment signal (FAS) is automatically generated if the Insert Framing bit (InsertFrm;CR00.2) is set to a 1. The Sa-bits and the A-bit in TS0 of the Not-FAS frame may be programmed as desired in various control registers. If CRC-4 error checking and framing is desired, it must be enabled by setting the Insert CRC bit (InsertCRC;CR00.1) in the Configuration Register [CR00;0x00]. Automatic CRC-4 performance reporting (FEBE), using the two E-bits in the CRC-4 16-frame multiframe, may be enabled as well. Alternatively, TS0 patterns may be sourced directly from the XPCMI pin or read from the Transmit Idle Codes registers. In the latter case, the host processor would supply the desired TS0 data.

#### Transmit Per-Channel Idle Code Insertion

The Transmit Idle Code Registers (addresses 0xA0–0xB8) in buffer memory are used to transmit specific idle code ("idle code" refers to any user-specified, fixed data pattern) for each individual channel or time slot. The most significant bit of the register will be transmitted first. Setting the Insert Idle Code bit (InsertIdleTSn) for a specific time slot in the one of the appropriate Transmit Per-Channel Control Registers (addresses 0x10–0x1F) enables transmission in the E1 signal of the byte in the corresponding Transmit Idle Code Register. Therefore, each transmitted channel can contain a unique idle code pattern programmed by the host in lieu of normal PCM data traffic.

To insert user-specified framing patterns into TS0 from the Transmit Idle Code registers, the Insert Framing bit [InsFrm;CR00.2] of the Configuration Register must be cleared to 0 to disable internal framing bit generation.

#### **External Signaling Insertion**

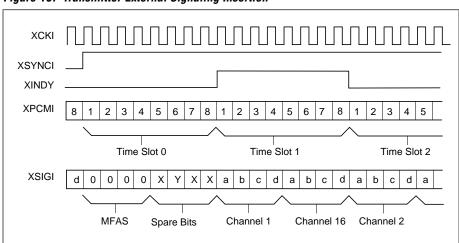

Figure 10 illustrates the required timing for external transmit signaling insertion using the external signaling input (XSIGI). Signaling bits for each channel are grouped as 4-bit nibbles. Two signaling nibbles for a pair of PCM channels are required to be input in the same byte as shown. The first 16 time slots of the frame are used for all the signaling information. The bits to be transmitted in TS16 frame 0 are coincident with the TS0 time window, and so on until the signaling channels 15 and 30 are input coincident with the data for TS15. The signaling data *must* be repeated each frame, even though signaling only changes on a multiframe rate. XSIGI is ignored during the remaining 16 time slots of each frame (TS16-TS31).

To insert user-specified framing patterns into TS16 of frame 0 directly from the XSIGI pin, the Insert CAS Framing bit [InsCASFrm;CR02.0] must be disabled in the Time Slot 16 Control Register [CR02;0x02]. If InsCASFrm is enabled, both the CAS multiframe alignment signal and the Transmit X1 [TxX1;CR02.4], Transmit X3 [TxX3;CR02.6], Transmit X4 [TxX4;CR02.7] and Send Multiframe Remote Alarm Indication [Tx16RemAlm;CR02.5] bits will be internally generated for insertion into TS16, frame 0, as programmed in the Time Slot 16 Control Register.

Figure 10. Transmitter External Signaling Insertion

#### Transmit Time Slot Indication

The transmitter time slot indicator output (XINDY) is a programmable signal that is high or low for selected channels or timeslots. Programming of each time slot is determined by the Transmit Per-Channel Control Registers [TXCR;0x10–0x1F].

**NOTE:** For the transmitter, the bit must be set in the register two time slots ahead of the one to be actually indicated. For example, to indicate TS1 the bit for TS31 (Indicate Time Slot [IndTS31;TXCR.7 at address 0x1F]) must be set (see Figure 10). Any number of time slots up to 32 may be indicated.

## Receiver Operation

The receiver features an off-line framer. Internal timing and data recovery is optionally provided. Both the recovered serial data and frame synchronization, and the slip buffer data and slip multiframe synchronization signals are provided to the user via output pins.

#### **Timing Recovery**

The receive E1 analog signal is converted by an internal adaptive-level comparator into a logic-level data stream which is fed to the timing recovery circuit. Timing recovery is accomplished through a Digital Phased Locked Loop (DPLL) using an up-down counter circuit, which operates at the 32.768 MHz (16 x 2.048 MHz) clock rate supplied at CK32I. The timing recovery circuit is designed to center the derived clock edge on each incoming E1 pulse. The phase of the recovered clock signal can be adjusted by  $\pm$  30 ns for each pulse received. The output of the timing circuit is the recovered clock signal at RCKO and the serial data output at RPCMO.

The recovered clock signal at RCKO will have jitter of  $\pm$  30 ns (.062 UI) at a frequency that corresponds to the difference between the receive E1 signal timing and CK32I. Typically, this amount of jitter is small compared to that introduced by the network E1 facility. The total of the network and Bt8510 jitter may make RCKO unsuitable for loop-timed applications without some amount of jitter attenuation via an external narrow-bandwidth Phase Lock Loop (PLL).

In the event of a loss of incoming signal, the recovered clock will continue to free-run at a rate exactly 1/16 of the clock frequency present at CK32I.

## **Bipolar-to-Unipolar Conversion**

The bipolar-to-unipolar conversion circuit includes the High-Density Binary 3 (HDB3) decoding circuit. Optionally, Alternate Mark Inversion (AMI) coded signals without HDB3 zero suppression may be received and transmitted by setting the Enable AMI bit (EnAMI;CR00.5) to a 1 in the Configuration Register (CR00; 0x00). In AMI mode, no zero code suppression is provided.

#### **Receiver Output Timing**

The received unipolar signal is recovered and provided with clock at RPCMO and RCKO respectively. A frame synchronization signal is also provided at RSYNCO. Figure 10 illustrates a timing diagram for the receiver output signals. The RSYNCO signal is low for the 8 bits of the channel output corresponding to TS31 of each frame and then transitions high at the beginning of TS0. Both RPCMO and RSYNCO transition on rising edges of RCKO.

Figure 11. Receiver Output Timing

### Framing Operation

The receiver employs an off-line framing algorithm. This means that upon detection of an Out-of-Frame (OOF) condition, the receiver will not change its timeslot, frame, or multiframe alignment until a new frame alignment is found. Data will continue to be written to the same buffer locations as before. Framing is initiated either by an OOF condition (detection of three consecutive FAS errors) or by the setting of the Force Reframing Operation control bit (FrcRefrm;CR01.2) in the Framer/Timing Control Register [CR01;0x01].

The FrcRefrm bit must be written each time a new operation is desired. It is not possible to read back this control bit, as it immediately cleared internally (the process of setting this bit to a 1 sends a momentary pulse to the receive framer which triggers the reframe sequence). The operation of this feature is timed to cause the search for the new frame position to begin immediately after the present frame alignment position. This assures an exhaustive search when CRC-4 errors are excessive, or when a false framing pattern is present.

The receiver can be set to inhibit reframing via the Abort Reframe (AbortRefrm;CR01.1) bit, which prevents an out-of-frame condition from automatically triggering reframing. Setting the AbortRefrm bit also stops a reframing operation already in progress.

Three status indicators that monitor framing functions are provided. If the reframing operation continues for more than 1 ms without identifying a unique framing pattern, the Frame Search Active Longer than 1 ms bit [FrmSch1ms;SR01.1] of the Framer/Timing Status Register [SR01;0x11] will be set. If no framing pattern is present, the FrmSch1ms indicator will be set indefinitely.

22 Brooktree®

When a new frame alignment is found that is different than the old frame alignment, the Change of Frame Alignment bit [COFADet;SR01.4] will be set. This bit is latched at the end of each successful reframe operation. It can be cleared by forcing a reframe which results in no COFA. The Loss of Frame Alignment indicator [LOFAlign;SR01.3] is set and held for one transmit multiframe period if receive FAS frame alignment was lost during the previous transmit multiframe period (as measured by the XSYNCO signal).

#### **Alarm Detection**

Alarm and error indicators are provided for E1 link maintenance. These indicators are accessible in various status registers starting at address 0x10.

#### **AIS Signal Detection**

AIS Signal Detect [AISDet;SR00.2] is updated each frame interval. It is set to a 1 if all bits in three of the last four frames are a one, and there is an OOF condition present as well. This signal can be integrated by the host processor to declare a received AIS to the system, which normally requires a response on the order of three to four seconds. This bit is located in the Maintenance Status Register [SR00;0x10]

#### Remote Frame Alarm Detection

Remote Frame Alarm (RemFrmAlm;SR03.5) is updated every other frame interval and is set if bit 3 of the not-FAS word in TS0 is set to a 1. This bit is located in the Framing Pattern Status Register [SR03; 0x13].

#### **Status Data**

Loss-of-Signal

Loss-of-Signal Detect [LOSDet;SR00.0] is set when 32 consecutive zeros are received before HDB3 decoding. This bit is set to a 1 as soon as the condition is detected. Receiving a single 1 clears the indication. This bit is located in the Maintenance Status Register.

#### **Out-Of-Frame Alignment**