# INTEGRATED CIRCUITS

# DATA SHEET

# MAX6400/MAX6401/MAX6402/ MAX6403/MAX6404/MAX6405

Ultra-low-power microprocessor reset circuit in 4-bump Chip-Scale package

Product data 2003 May 27

# Ultra-low-power microprocessor reset circuit in 4-bump Chip-Scale package

# MAX6400/MAX6401/MAX6402/ MAX6403/MAX6404/MAX6405

#### **DESCRIPTION**

The MAX6400/MAX6401//MAX6402/MAX6403/MAX6404/MAX6405 microprocessor ( $\mu P)$  reset circuits monitor power supplies in  $\mu P$  and digital systems. These devices eliminate external components and adjustments while providing excellent circuit reliability and low cost solution. They are used to monitor 2.5 V, 3 V, 3.3 V and 5 V power supplies. A manual reset input is also available.

MAX6400-MAX6405 assert a reset signal when the V<sub>DD</sub> supply voltage falls below a preset reset threshold voltage. The reset signal remains asserted for at least 100 ms after the V<sub>DD</sub> rises above the reset threshold. The reset threshold are factory trimmable from 2.2 V to 4.63 V in approximately 100 mV increments. All these parts are guaranteed to assert a reset for V<sub>DD</sub> down to 1 V. They have excellent immunity to fast transients on V<sub>DD</sub>.

The devices vary in their output configuration. The MAX6400/MAX6403 have push-pull, active-LOW reset output; while the MAX6402/MAX6405 have open drain, active-LOW reset output. The MAX6401/MAX6404 have push-pull, active-HIGH reset output.

The lower threshold MAX6400/MAX6401/MAX6402 have ultra-low supply current of typically 500 nA, making them ideal for battery powered applications. All six devices are available in the 4-bump Chip-Scale (WL-CSP4) package.

#### **FEATURES**

- Ultra-Low 1 μA (max) supply current

- Precision monitoring of 2.5 V, 3 V, 3.3 V, and 5 V power supply voltages

- Reset thresholds available from 2.2 V to 4.63 V

- ±2.5% threshold accuracy from −40 °C to +85 °C

- 100 ms (min) Power-on-Reset delay time

- Manual Reset input

- Power transient immunity

- Available in three versions: push-pull RESET, push-pull RESET, and open-drain RESET

- Guaranteed reset valid to V<sub>DD</sub> = 1.0 V

- Ultra-small 4-bump Chip-Scale packages

#### **APPLICATIONS**

- PDAs and pagers

- MP3 players

- Portable/battery-powered equipment

- Cellular phones

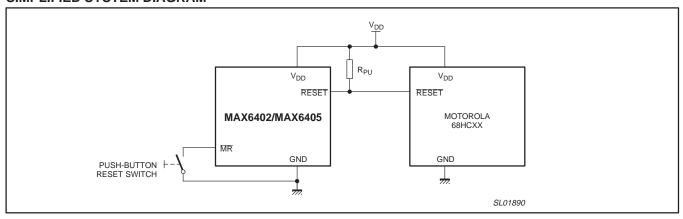

#### SIMPLIFIED SYSTEM DIAGRAM

Figure 1. Simplified system diagram.

Ultra-low-power microprocessor reset circuit in 4-bump Chip-Scale package

MAX6400/MAX6401/MAX6402/ MAX6403/MAX6404/MAX6405

#### **ORDERING INFORMATION**

# MAX6400/MAX6401/MAX6402

| TYPE NUMBER           | PACKAGE | TEMPERATURE                                             |                  |  |

|-----------------------|---------|---------------------------------------------------------|------------------|--|

| I THE NUMBER          | NAME    | DESCRIPTION                                             | RANGE            |  |

| MAX6400- <b>XX</b> UK | WL-CSP4 | Wafer-level, chip-scale package; 4 bumps; surface mount | -40 °C to +85 °C |  |

| MAX6401- <b>XX</b> UK | WL-CSP4 | Wafer-level, chip-scale package; 4 bumps; surface mount | –40 °C to +85 °C |  |

| MAX6402- <b>XX</b> UK | WL-CSP4 | Wafer-level, chip-scale package; 4 bumps; surface mount | -40 °C to +85 °C |  |

#### NOTE:

Each device has 5 standard voltage options, indicated by ' $\boldsymbol{XX'}$ ' on the 'Type number'.

Additional voltage options may be available (see Table 1 for details).

| XX<br>(type number suffix) | Reset threshold voltage (V) (Typical) |

|----------------------------|---------------------------------------|

| 22                         | 2.200                                 |

| 23                         | 2.320                                 |

| 26                         | 2.630                                 |

| 29                         | 2.930                                 |

| 31                         | 3.080                                 |

# MAX6403/MAX6404/MAX6405

| TYPE NUMBER           | PACKAGE | TEMPERATURE                                             |                  |  |

|-----------------------|---------|---------------------------------------------------------|------------------|--|

| I TPE NOWIBER         | NAME    | DESCRIPTION                                             | RANGE            |  |

| MAX6403- <b>XX</b> UK | WL-CSP4 | Wafer-level, chip-scale package; 4 bumps; surface mount | -40 °C to +85 °C |  |

| MAX6404- <b>XX</b> UK | WL-CSP4 | Wafer-level, chip-scale package; 4 bumps; surface mount | -40 °C to +85 °C |  |

| MAX6405- <b>XX</b> UK | WL-CSP4 | Wafer-level, chip-scale package; 4 bumps; surface mount | –40 °C to +85 °C |  |

#### NOTE:

Each device has 2 standard voltage options, indicated by 'XX' on the 'Type number'. Additional voltage options may be available (see Table 1 for details).

|    | Reset threshold voltage (V) (Typical) |

|----|---------------------------------------|

| 44 | 4.380                                 |

| 46 | 4.630                                 |

Ultra-low-power microprocessor reset circuit in 4-bump Chip-Scale package

MAX6400/MAX6401/MAX6402/ MAX6403/MAX6404/MAX6405

Table 1. Factory-trimmed reset thresholds (note 1)

|                                                |             | Reset Threshold Voltage, V <sub>th</sub> (V) |                           |       |        |              |  |

|------------------------------------------------|-------------|----------------------------------------------|---------------------------|-------|--------|--------------|--|

| Part number                                    | Suffix (XX) | $T_{amb} = +25$                              | T <sub>amb</sub> = +25 °C |       |        | °C to +85 °C |  |

|                                                |             | Min                                          | Тур                       | Max   | Min    | Max          |  |

|                                                | 22          | 2.167                                        | 2.200                     | 2.233 | 2.145  | 2.250        |  |

|                                                | 23          | 2.285                                        | 2.320                     | 2.355 | 2.262  | 2.375        |  |

|                                                | 24 (Note 2) | 2.364                                        | 2.400                     | 2.436 | 2.340  | 2.460        |  |

| 144 VO 400 WW U                                | 25 (Note 2) | 2.462                                        | 2.500                     | 2.537 | 2.437  | 2.562        |  |

| MAX6400-XXUK                                   | 26          | 2.591                                        | 2.630                     | 2.669 | 2.564  | 2.696        |  |

| MAX6401-XXUK                                   | 27 (Note 2) | 2.660                                        | 2.700                     | 2.741 | 2.633  | 2.768        |  |

| MAX6402- <b>XX</b> UK                          | 28 (Note 2) | 2.758                                        | 2.800                     | 2.842 | 2.730  | 2.870        |  |

|                                                | 29          | 2.886                                        | 2.930                     | 2.974 | 2.857  | 3.000        |  |

|                                                | 30 (Note 2) | 2.955                                        | 3.000                     | 3.045 | 2.925  | 3.075        |  |

|                                                | 31          | 3.034                                        | 3.080                     | 3.126 | 3.003  | 3.150        |  |

|                                                | 33 (Note 2) | 3.250                                        | 3.300                     | 3.350 | 3.217  | 3.383        |  |

|                                                | 34 (Note 2) | 3.349                                        | 3.400                     | 3.451 | 3.315  | 3.485        |  |

|                                                | 35 (Note 2) | 3.447                                        | 3.500                     | 3.552 | 3.412  | 3.587        |  |

|                                                | 36 (Note 2) | 3.546                                        | 3.600                     | 3.654 | 3.510  | 3.690        |  |

|                                                | 37 (Note 2) | 3.644                                        | 3.700                     | 3.755 | 3.607  | 3.792        |  |

|                                                | 38 (Note 2) | 3.743                                        | 3.800                     | 3.857 | 3.705  | 3.895        |  |

| MAX6403-XXUK                                   | 39 (Note 2) | 3.841                                        | 3.900                     | 3.958 | 3.802  | 3.997        |  |

| MAX6404- <b>XX</b> UK<br>MAX6405- <b>XX</b> UK | 40 (Note 2) | 3.940                                        | 4.000                     | 4.060 | 3.900  | 4.100        |  |

| AUVY-COROVVINI                                 | 41 (Note 2) | 4.038                                        | 4.100                     | 4.161 | 3.997  | 4.202        |  |

|                                                | 42 (Note 2) | 4.137                                        | 4.200                     | 4.263 | 4.095  | 4.305        |  |

|                                                | 43 (Note 2) | 4.235                                        | 4.300                     | 4.364 | 4.192  | 4.407        |  |

|                                                | 44          | 4.314                                        | 4.380                     | 4.446 | 4.270  | 4.489        |  |

|                                                | 45 (Note 2) | 4.432                                        | 4.500                     | 4.567 | 4.387  | 4.612        |  |

|                                                | 46          | 4.560                                        | 4.630                     | 4.699 | 4.3514 | 4.746        |  |

# NOTES:

<sup>1.</sup> Factory-trimmed reset thresholds are available in 100 mV increments with  $\pm 1.5\%$  tolerance at room temperature.

<sup>2.</sup> Consult factory for availability.

Ultra-low-power microprocessor reset circuit in 4-bump Chip-Scale package

MAX6400/MAX6401/MAX6402/ MAX6403/MAX6404/MAX6405

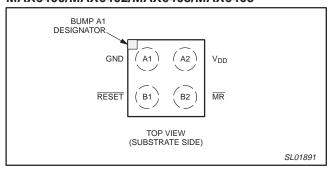

#### **PINNING**

# MAX6400/MAX6402/MAX6403/MAX6405

Figure 2. MAX6400/MAX6402/MAX6403/MAX6405 pin configuration.

# MAX6400/MAX6402/MAX6403/MAX6405 Pin description

| BUMP | SYMBOL   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | GND      | Device ground.                                                                                                                                                                                                                                                                                                                                                                                   |

| A2   | $V_{DD}$ | Positive supply voltage.                                                                                                                                                                                                                                                                                                                                                                         |

| B1   | RESET    | Active-LOW Reset output. RESET remains LOW while V <sub>DD</sub> is below the reset threshold and for a reset delay time of at least 100 ms after V <sub>DD</sub> rises above the reset threshold. MAX6402/MAX6405 have open-drain output and the MAX6400/MAX6403 are push-pull output.                                                                                                          |

| B2   | MR       | Active-LOW Manual Reset. Internal 50 k $\Omega$ pull-up resistor to V <sub>DD</sub> . Pull LOW to assert a reset condition. As long as $\overline{\text{MR}}$ is LOW, the reset remains asserted. Reset is released in typically 185 ms (reset delay time) after $\overline{\text{MR}}$ goes HIGH. When unused, the $\overline{\text{MR}}$ pin is connected to V <sub>DD</sub> or left floating. |

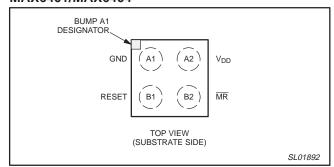

# MAX6401/MAX6404

Figure 3. MAX6401/MAX6404 pin configuration.

# MAX6401/MAX6404 Pin description

| BUMP | SYMBOL   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | GND      | Device ground.                                                                                                                                                                                                                                                                                                                                                                                   |

| A2   | $V_{DD}$ | Positive supply voltage.                                                                                                                                                                                                                                                                                                                                                                         |

| B1   | RESET    | Active-HIGH Reset Output. RESET remains HIGH while $V_{DD}$ is below the reset threshold and remains HIGH for at least 100 ms after $V_{DD}$ rises above the reset threshold.                                                                                                                                                                                                                    |

| B2   | MR       | Active-LOW Manual Reset. Internal 50 k $\Omega$ pull-up resistor to V <sub>DD</sub> . Pull LOW to assert a reset condition. As long as $\overline{\text{MR}}$ is LOW, the reset remains asserted. Reset is released in typically 185 ms (reset delay time) after $\overline{\text{MR}}$ goes HIGH. When unused, the $\overline{\text{MR}}$ pin is connected to V <sub>DD</sub> or left floating. |

# **MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                                                                     | CONDITIONS | MIN. | MAX.                  | UNIT |  |

|------------------|-------------------------------------------------------------------------------|------------|------|-----------------------|------|--|

| $V_{DD}$         | Supply voltage                                                                |            | -0.3 | +6                    | V    |  |

|                  | Voltage RESET, RESET (push-pull)                                              |            | -0.3 | V <sub>DD</sub> + 0.3 | V    |  |

|                  | Voltage RESET (open drain)                                                    |            | -0.3 | +6                    | V    |  |

|                  | Voltage manual reset, MR                                                      |            | -0.3 | V <sub>CC</sub> + 0.3 | V    |  |

| I <sub>IN</sub>  | Input current (any pin)                                                       |            | -    | 20                    | mA   |  |

| I <sub>OUT</sub> | Output current (any pin)                                                      |            | -    | 20                    | mA   |  |

| T <sub>amb</sub> | Ambient temperature range                                                     |            | -40  | +85                   | °C   |  |

| T <sub>stg</sub> | Storage temperature range                                                     |            | -65  | +150                  | °C   |  |

| P <sub>D</sub>   | Power dissipation, 4-bump WL–CSP Derate 3.8 mW/°C above T <sub>amb</sub> = 70 |            | -    | 303                   | mW   |  |

# Ultra-low-power microprocessor reset circuit in 4-bump Chip-Scale package

MAX6400/MAX6401/MAX6402/ MAX6403/MAX6404/MAX6405

#### **ELECTRICAL CHARACTERISTICS**

$V_{DD}$  = full range ( $T_{amb}$  = -40 °C to +85 °C) unless otherwise specified. Typical values are at  $T_{amb}$  = +25 °C and  $V_{DD}$  = 3 V (Note 1).

| SYMBOL                    | PARAMETER                                        | CONDITIONS                                                                                                                                                    | MIN.                   | TYP.     | MAX.                   | UNIT   |

|---------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|------------------------|--------|

| V <sub>DD</sub>           | Supply voltage range                             | T <sub>amb</sub> = 0 °C to +70 °C                                                                                                                             | 1.0                    | -        | 5.5                    | V      |

|                           |                                                  | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$                                                                                           | 1.2                    | -        | 5.5                    | V      |

| I <sub>DD</sub>           | Supply current                                   | $V_{DD} = 3.0 \text{ V for } V_{th} \le 2.93 \text{ V};$<br>$V_{DD} = 3.2 \text{ V for } V_{th} \ge 2.93 \text{ V, no load}$                                  | -                      | 0.5      | 1.0                    | μΑ     |

|                           |                                                  | V <sub>DD</sub> = 5.5 V, no load                                                                                                                              | -                      | 1.0      | 1.75                   | μΑ     |

| V <sub>th</sub>           | Reset threshold (see Table 1)                    | T <sub>amb</sub> = +25 °C                                                                                                                                     | V <sub>th</sub> – 1.5% | $V_{th}$ | V <sub>th</sub> + 1.5% | V      |

|                           |                                                  | $T_{amb} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}$                                                                                             | V <sub>th</sub> - 2.5% | $V_{th}$ | V <sub>th</sub> + 2.5% | V      |

| $\Delta V_{th}/^{\circ}C$ | Reset threshold temperature coefficient          |                                                                                                                                                               | -                      | 40       | -                      | ppm/°C |

| V <sub>hys</sub>          | Reset threshold hysteresis                       | MAX6400/MAX6401/MAX6402                                                                                                                                       | _                      | 6.3      | _                      | mV     |

| •                         |                                                  | MAX6403/MAX6404/MAX6405                                                                                                                                       | _                      | 9.5      | -                      | mV     |

| t <sub>RD</sub>           | V <sub>DD</sub> to Reset release delay           | $V_{DD} = (V_{th} + 100 \text{ mV}) \text{ to } (V_{th} - 100 \text{ mV})$                                                                                    | _                      | 20       | _                      | μs     |

| t <sub>RP</sub>           | Reset active time-out period                     |                                                                                                                                                               | 100                    | 185      | 280                    | ms     |

| V <sub>IL</sub>           | LOW-level input voltage on MR pin                | $V_{th} > 4.0 \text{ V}$                                                                                                                                      | -                      | -        | 0.8                    | V      |

|                           |                                                  | $V_{th} \le 4.0 \text{ V}$                                                                                                                                    | -                      | -        | $0.2 \times V_{DD}$    | V      |

| V <sub>IH</sub>           | HIGH-level input voltage on MR pin               | $V_{th} > 4.0 \text{ V}$                                                                                                                                      | 2.0                    | -        | -                      | V      |

|                           |                                                  | V <sub>th</sub> ≤ 4.0 V                                                                                                                                       | $0.7 \times V_{DD}$    | -        | -                      | V      |

| t <sub>MD</sub>           | MR minimum input pulse width                     |                                                                                                                                                               | 1                      | -        | -                      | μs     |

|                           | MR glitch rejection                              |                                                                                                                                                               | -                      | 100      | -                      | ns     |

| t <sub>MR</sub>           | MR to Reset time delay                           |                                                                                                                                                               | -                      | 200      | -                      | ns     |

|                           | MR pull-up resistance                            |                                                                                                                                                               | 25                     | 50       | 75                     | kΩ     |

| V <sub>OL(RESET)</sub>    | LOW-level output voltage on RESET pin            | I <sub>SINK</sub> = 1.6 mA; V <sub>DD</sub> > 2.1 V;<br>RESET asserted                                                                                        | -                      | -        | 0.3                    | V      |

|                           | (MAX6400/MAX6402/<br>MAX6403/MAX6405)            | I <sub>SINK</sub> = 100 μA; V <sub>DD</sub> > 2.1 V;<br>RESET asserted                                                                                        | -                      | -        | 0.4                    | V      |

| V <sub>OH(RESET)</sub>    | HIGH-level output voltage on RESET pin           | I <sub>SOURCE</sub> = 500 μA; V <sub>DD</sub> = 3.2 V;<br>MAX6400 only; RESET released                                                                        | $0.8 \times V_{DD}$    | _        | -                      | V      |

|                           | (MAX6400/MAX6403)                                | $I_{SOURCE}$ = 800 μA; $V_{DD}$ = 4.5 V; $V_{th}$ ≤ 4.38 V; RESET released                                                                                    | $0.8 \times V_{DD}$    | -        | _                      | V      |

|                           |                                                  | $\begin{aligned} &I_{SOURCE} = 800 \ \mu\text{A}; \ V_{DD} = V_{th(max)}; \\ &V_{th} \geq 4.5 \ V; \ \overline{\text{RESET}} \ \text{released} \end{aligned}$ | $0.8 \times V_{DD}$    | -        | _                      | V      |

| V <sub>OH(RESET)</sub>    | HIGH-level output voltage on RESET pin           | I <sub>SOURCE</sub> = 500 μA; V <sub>DD</sub> ≥ 2.1 V;<br>RESET asserted                                                                                      | $0.8 \times V_{DD}$    | _        | _                      | V      |

|                           | (MAX6401/MAX6404)                                | I <sub>SOURCE</sub> = 50 μA; V <sub>DD</sub> ≥ 1.2 V;<br>RESET asserted                                                                                       | $0.8 \times V_{DD}$    | -        | -                      | V      |

| V <sub>OL(RESET)</sub>    | LOW-level output voltage on RESET pin            | I <sub>SINK</sub> = 1.2 mA, V <sub>DD</sub> ≥ 3.2 V;<br>RESET released; MAX6401 only                                                                          | -                      | -        | 0.3                    | V      |

|                           | (MAX6401/MAX6404)                                | $I_{SINK}$ = 3.2 mA, $V_{DD} \ge 4.5 \text{ V}$ ;<br>$V_{th} \le 4.38 \text{ V}$ ; RESET released                                                             | -                      | -        | 0.4                    | V      |

|                           |                                                  | I <sub>SINK</sub> = 3.2 mA, V <sub>DD</sub> = V <sub>th(max)</sub> ;<br>Vth ≥ 4.5 V; RESET released                                                           | -                      | -        | 0.4                    | V      |

|                           | Open drain RESET output leakage current (Note 2) | RESET released                                                                                                                                                | -                      | -        | 0.1                    | μА     |

#### NOTES:

- 1. Over-temperature limits are guaranteed by design and are not production tested.

- 2. Guaranteed by design; not production tested.

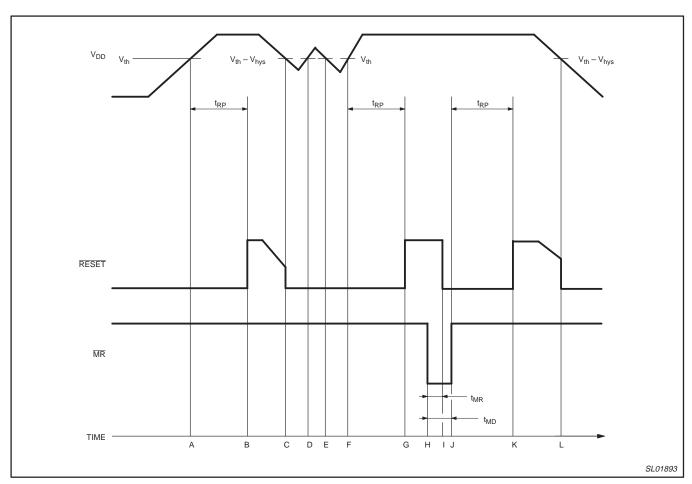

#### **TIMING DIAGRAM**

The timing diagram in Figure 4 depicts the operation of the device. Letters indicate events on the TIME axis.

On power-up, when  $V_{\mbox{\scriptsize DD}}$  reaches 1 V,  $\overline{\mbox{\scriptsize RESET}}$  is guaranteed to be a logic LOW.

At Event A, V<sub>DD</sub> rises to reset threshold voltage, V<sub>th</sub>. At this time, the internal reset delay timer is initiated. RESET and remains asserted for a reset delay time, t<sub>RP</sub> of typically 180 ms after the supply voltage rises above the reset threshold, V<sub>th</sub>.

Event B: At this time, the reset is released. RESET goes HIGH. The reset delay time helps to ensure valid reset signals with erratic changes in supply voltage.

Events C–E: At Event C, under brown-out conditions,  $V_{DD}$  falls below the reset threshold minus the hysteresis voltage,  $V_{hys}$ , the reset signal is asserted. When power recovers and  $V_{DD}$  rises above the reset threshold, it once again initiates the reset delay timer

(Event D). At Event E,  $V_{DD}$  falls below the reset threshold before the reset delay time is reached, and reset remains asserted.

At F, the  $V_{DD}$  rises above the reset threshold and remains above the reset threshold for typically 185 ms. At G, the reset is once again released.

At H, the  $\overline{MR}$  is externally pulled LOW for greater than 1  $\mu$ s (minimum  $\overline{MR}$  pulse width,  $t_{MD}$  for  $V_{DD}$  = +5 V).

At I, the manual reset is asserted in 200 ns (typical  $\overline{MR}$  to reset out delay time,  $t_{MR}$  for  $V_{CC}$  = +5 V).

At J, the  $\overline{\text{MR}}$  pin returns HIGH. At this point, reset delay timer is initiated and in typically 180 ms (at K), the reset condition is released.

Event L: On power-down, when  $V_{DD}$  falls below  $V_{th} - V_{hys}$ , RESET is guaranteed to be asserted until  $V_{DD}$  falls below 1 V.

Figure 4. Timing diagram.

Ultra-low-power microprocessor reset circuit in 4-bump Chip-Scale package

MAX6400/MAX6401/MAX6402/ MAX6403/MAX6404/MAX6405

#### TECHNICAL DISCUSSION

#### General discussion

MAX6400–MAX6405 microprocessor ( $\mu P$ ) supervisory ICs provide system protection by monitoring power supply voltage and asserting a reset signal if the supply falls below the specified threshold. The MAX6402/MAX6405 have an active-LOW open drain output. The MAX6400/MAX6403 have an active-LOW, push-pull output; while the MAX6401/MAX6404 have an active-HIGH, push-pull output. The reset state is guaranteed to remain valid as long as VDD is above +1 V.

#### Threshold levels

The reset threshold voltages are factory trimmable from 2.2 V to 4.63 V in approximately 100 mV increments. Sample stock is available for all standard threshold voltages shown in Table 1, "Factory-trimmed reset thresholds". Guaranteed threshold voltage tolerance is  $\pm 1.5\%$  at  $T_{amb}=25~^{\circ}\text{C}$  and  $\pm 2.5\%$  over the operating ambient temperature,  $T_{amb}=-40~^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ .

#### **Manual Reset**

The manual reset input,  $\overline{MR}$  is active-LOW logic. It allows the RESET to be asserted by a pushbutton switch. A mechanical pushbutton switch is effectively debounced by the glitch filter. The typical glitch rejection is 100 ns.  $\overline{MR}$  may be driven from an external logic circuit since it is TTL/CMOS compatible. The minimum  $\overline{MR}$  input pulse is 1  $\mu$ s for V<sub>DD</sub> = +1.2 V to +5.5 V. When not in use, the pin is left floating or tied to V<sub>DD</sub>.

Ultra-low-power microprocessor reset circuit in 4-bump Chip-Scale package

#### **APPLICATION INFORMATION**

#### Interfacing to µPs with bi-directional reset pins

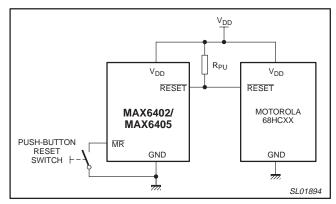

The MAX6402/MAX6405 RESET outputs are open drain and are easily interfaced with microprocessors which have bi-directional reset pins, such as the Motorola 68HC11. Directly connecting the MAX6402/MAX6405 RESET output to the  $\mu P$ 's reset input and providing a pull-up resistor to  $V_{DD}$  allows either device to independently assert reset (Figure 5).

Figure 5. Interfacing to μPs with bi-directional reset pins.

# Negative-going V<sub>DD</sub> transients

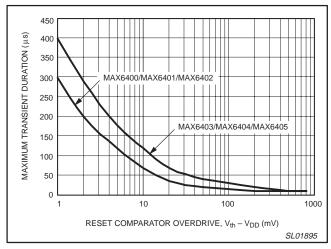

The MAX6400–MAX6405 Series resets are relatively immune to short duration, negative-going  $V_{DD}$  transients or power glitches. This capability greatly reduces false resets with short -duration pulses.

Figure 6, "Maximum transient duration versus reset comparator overdrive" shows the maximum transient condition for which reset signals are not generated. The graph shows the maximum pulse width that a negative-going transient may have before it will generate a reset signal. **Note:** as the amplitude of the transient increases, the maximum allowable transient pulse width decreases.

Figure 6. Maximum transient duration versus reset comparator overdrive.

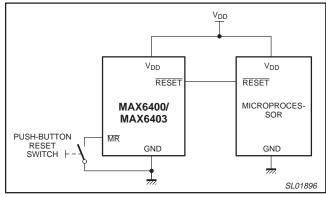

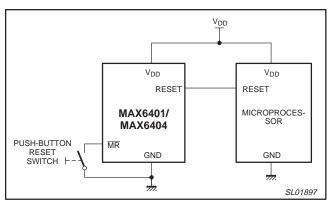

# System configurations with various µPs

The MAX6400–MAX6405 Series resets provide a system solution for various  $\mu Ps.\;$  Figures 7 and 8, respectively, reference the Philips  $\mu Ps$  which are compatible with the MAX6400/MAX6403 and MAX6401/MAX6404 system resets.

#### NOTE:

Philips microprocessors with active-LOW resets:

All 16-bit devices from the XA family (XA-Cxx, XA-Gxx, XA-Sxx, XA-Hxx), all LPC7xx devices (P87LPC760/761/762/767/768/769, P80C591/P87C591 (with on-chip CAN controller).

Figure 7.  $\mu P$  system diagram using MAX6400/MAX6403 push-pull, active-LOW resets.

#### NOTE:

1. Philips microprocessors with active-HIGH resets: 8xC5x, 8xC3x, 8xC5xX2, 8xC3xX2, 8xC51Fx, 8xC51Rx+, 89C51Rx2, 89C66x, 8xC554, 8xC552, etc.

Figure 8.  $\mu P$  system diagram using MAX6401/MAX6404 push-pull, active-HIGH resets.

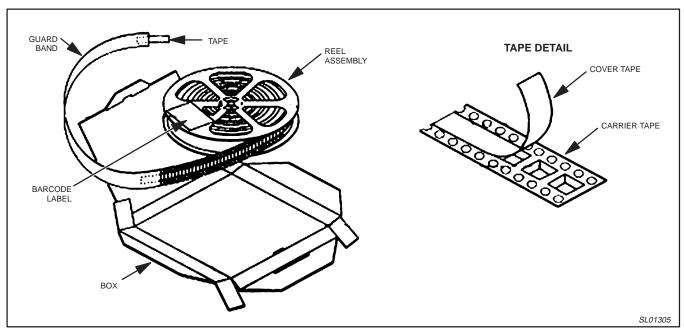

#### **PACKING METHOD**

The MAX6401-MAX6405 Series are packed in reels, as shown in Figure 9.

Figure 9. Tape and reel packing method.

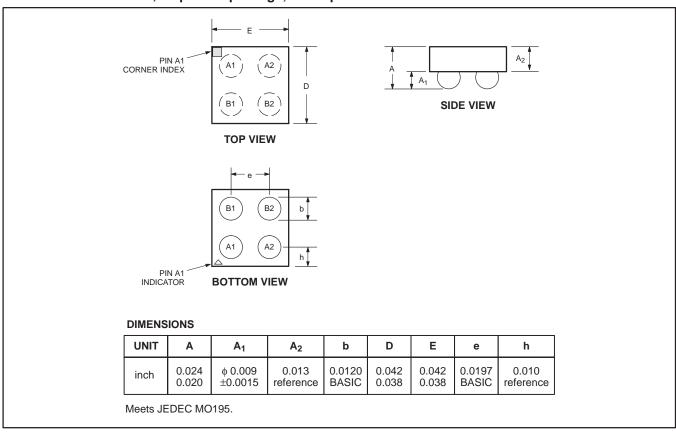

# WL-CSP4: wafer level, chip-scale package; 4 bumps

Ultra-low-power microprocessor reset circuit in 4-bump Chip-Scale package

MAX6400/MAX6401/MAX6402/ MAX6403/MAX6404/MAX6405

#### **REVISION HISTORY**

| Rev | Date     | Description                                                      |

|-----|----------|------------------------------------------------------------------|

| _1  | 20030527 | Product data (9397 750 10644); ECN 853-2428 29962 of 27 May 2003 |

#### Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                   |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

- [1] Please consult the most recently issued data sheet before initiating or completing a design.

- [2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

- [3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

# **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com

Koninklijke Philips Electronics N.V. 2003

All rights reserved. Printed in U.S.A.

Date of release: 05-03

Document order number: 9397 750 10644

Let's make things better.

Philips Semiconductors