82C235

System Controller

Single CHIP 286 AT

Datasheet

August 1991 Revision 2.0

PRELIMINARY

CHIP5°

#### Copyright Notice

Manual Copyright © 1991, CHIPS and Technologies, Inc.

All Rights Reserved.

Printed in U.S.A.

#### **Trademarks**

SCATTM is a trademark of CHIPS and Technologies, Incorporated.

IBM®, IBM PC®, and IBM PC/AT® are registered trademarks of International Business Machines Corporation.

PS2<sup>TM</sup>, Microchannel<sup>TM</sup>, and Personal System/2<sup>TM</sup> are trademarks of International Business Machines Corporation.

Intel® is a registered trademark of Intel Corporation.

Lonis® is a registered trademark of Lotus Development Corporation.

MS-DOS® is a registered trademark of Microsoft Corporation.

Motorola@ is a registered trademark of Motorola.

#### Disclaimer

This manual is copyrighted by CHIPS and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of CHIPS and Technologies, Inc.

Every possible effort was made to ensure the accuracy of this manual. However, CHIPS Systems Logic Division cannot accept responsibility for any errors in the manual or consequences resulting therefrom.

The information contained in this document is being issued in advance of the production cycle for the device(s). The parameters for the device(s) may change before final production.

CHIPS and Technologies, Inc. makes no representations or warranties regarding the contents of this manual. We reserve the right to revise the manual or make changes in the specifications of the product described within it at any time without notice and without obligation to notify any person of such revision or change.

The information contained in this manual is provided for general use by our customers. Our customers should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. It is the policy of CHIPS and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

#### Restricted Rights and Limitations

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252,277-7013.

Chips and Technologies, Inc. 3050 Zanker Road San Jose, California 95134 Phone: 408-434-0600

The 82C235 is a VLSI device that incorporates most of the motherboard logic required to build a low-cost, highly-integrated, IBM PC AT-compatible computer. It is designed to be used in conjunction with other Chips and Technologies controllers such as the 82C45X VGA Controller, the 82C601 Multifunction Controller, the 82C765 Floppy Disk Controller, and the 82C710 Integrated Floppy Disk and Multifunction Controller. When used with these devices, the 82C235 acts as the heart of a highly integrated system that significantly reduces motherboard size, component count, and the need for many I/O channel slots. This manual covers the 82C235 only. Consult the following list of related documentation for information regarding other Chips and Technologies devices.

#### Related Documentation

The following related documentation is also available:

- The 82C45X VGA Controller Data Sheet

- The 82C601 Multifunction Controller Data Sheet

- The 82C765 Floppy Disk Controller Data Sheet

- The 82C710 Integrated Floppy Disk and Multifunction Controller Data Sheet

The Development Kit Package for each chip which includes:

- The Development Kit User's Guide

- The Development Kit System Board

- The Development Kit Schematics

If you would like to review any of the above noted documentation, contact the Chips and Technologies Sales Office near you.

#### What You Need to Know

This manual is written with the assumption that you have a basic comprehension of computer concepts, operations, and terminology. Understanding of system organization and operation as well as memory functioning is essential. Finally, familiarity with the Industry Standard Architecture (ISA) is highly recommended.

The scope of the information presented in this manual is limited to this CHIPSet and does not include operation of external components. It is assumed you have a working knowledge of these components. With such knowledge, combined with the information presented here, you can utilize this CHIPSet to enhance the performance and excellence of the final product.

## Manual Organization

Here's what you'll find in this manual:

- Section 1: Introduction identifies the features of the 82C235.

- Section 2: Bus Control explains the Bus control functionality of the 82C235.

- Section 3: DMA Controller explains the DMA controller as well as the registers used during DMA functions.

- Section 4: The Interrupt Controller explains the two programmable interrupt controllers incorporated in the 82C235.

- Section 5: Programmable Interval Timer describes the Programmable Timer Control in the 82C235.

- Section 6: System Interface discusses the keyboard, memory, DRAM, and other system interfaces used by the 82C235.

- Section 7: Configuration Registers details the registers within the 82C235.

- Section 8: Pin Description provides tables describing the details of each pin.

- Section 9: System Characteristics reports the range of absolute maximum ratings, operating conditions, capacitive characteristics, and the DC and AC characteristics.

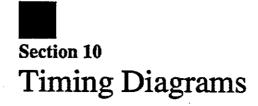

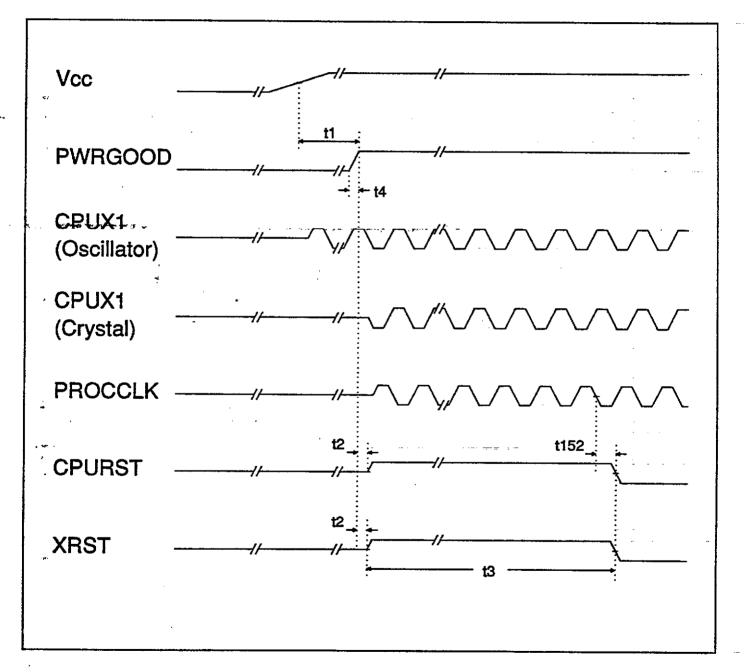

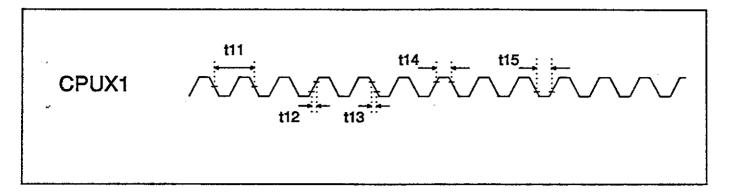

- Section 10: Timing Diagrams details the timings of the 82C235 signals.

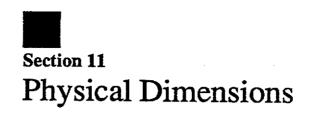

- Section 11: Physical Dimensions provides the dimensions of the 82C235.

- Appendix A: Address Mapping provides table of the I/O address and Memory maps..

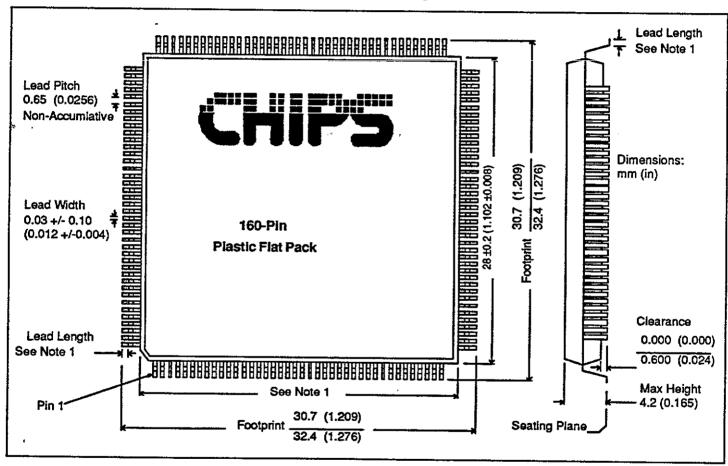

- Appendix B: 82C235 Revision A Silicon discusses the functionality of the 82C235 Revision A.

- U.S. Sales Representatives and Distributors gives a listing of the current distributors of CHIPS products.

## Manual Typography

The following typographical conventions are used throughout this manual:

- REGnH identifies the internal register of index n (hexadecimal notation).

- REGnH <x:y> indicates the bit field from bit x to bit y with index n.

- (xxx) signifies the default value after power-On Reset (xxx are register bits).

- Signal names are identified in UPPER CASE, for example, RAS3.

- A dash before the signal name indicates an active low signal; -RAS3.

- A hyphenated signal name specifies a set of signals. For example, -RAS0-3 indicates four signals: -RAS0, -RAS1, -RAS2, and -RAS3.

The following abbreviations are used throughout this manual:

- ICR = Internal Configuration Register

- Kb = kilobit

- KB = kilobyte

- Mb = megabit

- MB = megabyte

- MHz = megahertz

- ns = nanoseconds

- pF = pico farad

## Contents

| Section  | on 1: Introduction          | . 1  |

|----------|-----------------------------|------|

| 1.1      | Features                    | 1    |

| <b>~</b> |                             | _    |

|          | on 2: Bus Control           |      |

| 2.1      | Clock Generation            |      |

|          | Reset Strap Option          | 4    |

| 2.2      | Bus Control                 | 6    |

|          | Bus Controller              | 6    |

|          | Local Bus Arbitration       | 6    |

| Section  | on 3: DMA Controller        | . 7  |

| 3.1      | DMA Operation               | -    |

|          | Idle Condition              |      |

|          | Program Condition           |      |

|          | Active Condition            |      |

|          | Single Transfer Mode        |      |

|          | Block Transfer Mode         |      |

|          | Demand Transfer Mode        |      |

|          | Cascade Mode                |      |

| 3.2      | DMA Transfers               |      |

|          | Read Transfer               | _    |

|          | Write Transfer              |      |

|          | Verify Transfer             | . 12 |

| 3.3      | Auto-Initialization         | -    |

| 3.4      | DREQ Priority               |      |

| 3.5      | Address Generation          | . 13 |

| 3.6      | Current Address Register    | . 16 |

| 3.7      | Current Word Count Register | . 16 |

| 3.8      | Base Word Count Register    | . 16 |

| 3.9      | Command Register            | . 16 |

| 3.10     | Mode Register               | . 17 |

| 3.11     | Request Register            | 18   |

| 3.12    | Request Mask Register                                                                                                 | . 20                         |

|---------|-----------------------------------------------------------------------------------------------------------------------|------------------------------|

| 3.13    | Status Register                                                                                                       | . 21                         |

| 3.14    | Special Commands  Clear Byte Pointer Flip-Flop  Set Byte Pointer Flip-Flop  Master Clear  Clear Request Mask Register | . 21<br>. 22<br>. 22<br>. 22 |

| Sectio  | on 4: The Interrupt Controller                                                                                        | .23                          |

| 4.1     | Controller Operation                                                                                                  | . 24                         |

| 4.2     | Interrupt Sequence                                                                                                    |                              |

| 4.3     | End of Interrupt                                                                                                      |                              |

| 4.4     | Priority Assignment                                                                                                   | . 27                         |

|         | Fixed Priority Mode                                                                                                   | . 27                         |

|         | Specific Rotation Mode                                                                                                |                              |

|         | Automatic Rotation Mode                                                                                               |                              |

| 4.5     | Programming the Interrupt Controller                                                                                  | . 29                         |

|         | Initialization Command Words                                                                                          |                              |

|         | Operational Command Words                                                                                             | . 33                         |

| Section | on 5: Programmable Interval Timer                                                                                     | .37                          |

| 5.1     | Counter Description                                                                                                   | . 38                         |

| 5.2     | Programming the CTC                                                                                                   |                              |

| مده ل   | Read/Write Counter Command                                                                                            | . 40                         |

|         | Latch Counter Command                                                                                                 |                              |

|         | Read-Back Command                                                                                                     |                              |

| 5.3     | Counter Operation                                                                                                     | . 42                         |

| J.J     | Mode 0 - Interrupt on Terminal Count                                                                                  |                              |

|         | Mode 1 - Hardware Re-Triggerable One-Shot                                                                             | 43                           |

|         | Mode 2 - Rate Generator                                                                                               |                              |

|         | Mode 3 - Square Wave Generator                                                                                        | 43                           |

|         | Mode 4 - Software Triggered Strobe                                                                                    | 43                           |

|         | Mode 5 - Hardware Triggered Strobe                                                                                    |                              |

|         | GATE2                                                                                                                 | 44                           |

| Secti   | on 6: System Interface                                                                                                | 45                           |

| 6.1     | Keyboard Controller Interface                                                                                         | . 4:                         |

|         | FAST CPURESET and FAST GATEA20                                                                                        | 4                            |

| 6.2     | Memory Interface                                                                                                      |                              |

|         | ROM/Shadow RAM Interface                                                                                              | 46                           |

|         |                                                                                                                       | 47                           |

|             | Mixed Size DRAM Support  Expanded/Extended Memory |            |

|-------------|---------------------------------------------------|------------|

| 6.3         | Numeric Processor Interface                       |            |

| 6.4         | Real Time Clock Interface                         | 53         |

|             | Register Access                                   |            |

|             | Address Map                                       | 54         |

|             | Time Calendar and Alarm Bytes                     |            |

|             | Static RAM                                        |            |

|             | Control and Status Registers                      |            |

|             | Power-Up/Down                                     |            |

| 6.5         | I/O Channel Interface                             |            |

| 6.6         | Power Management                                  | 66         |

| Secti       | ion 7: Configuration Registers                    | <b>6</b> 9 |

| 7.1         | Internal Configuration Registers                  | 69         |

| 7.2         | IBM PC AT-Compatible Registers                    | 80         |

| Section     | ion 8: Pin Description                            | 83         |

| 8.1         | The Input and Output Pin Assignments              | 83         |

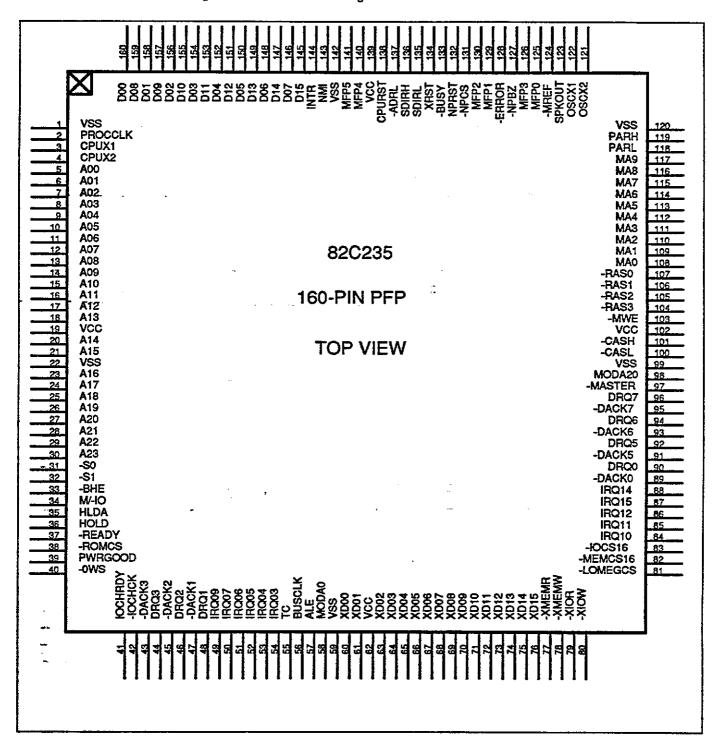

| 8.2         | Pinouts                                           | 90         |

| 8.3         | Pin Diagram                                       |            |

| Section     | ion 9: System Characteristics                     | 93         |

| 9.1         | Physical Characteristics                          | 93         |

| 9.2         | DC Characteristics                                | 94         |

| 9.3         | AC Characteristics (16 MHz 82C235)                | 95         |

| 9.4         | Tracking Parameters                               | 96         |

| 9.5         | AC Characteristics (12 MHz 82C235)                | 99         |

| Section     | ion 10: Timing Diagrams                           | 103        |

| Section     | on 11: Physical Dimensions                        | 115        |

| Appe        | endix A: Address Mapping                          | 117        |

| <b>A.</b> 1 | I/O Address Maps                                  | 117        |

| A 2         | Mamour Address Man                                | 100        |

### Contents

| A           | endix B: 82C235 Revision A Silicon   | 121 |

|-------------|--------------------------------------|-----|

| Арре<br>В 1 | Features                             | 121 |

| B.1         | AC Characteristics                   |     |

|             |                                      |     |

| B.3         | Timing Diagrams - Revision A Silicon |     |

| U.S.        | . Sales Representatives              | 129 |

|             | ributors                             |     |

# List of Figures

| Section 1:  | Introduction                                | 1  |

|-------------|---------------------------------------------|----|

| Figure 1-1  | 82C235 System Block Diagram                 |    |

|             |                                             |    |

| Section 2:  | Bus Control                                 |    |

| Figure 2-1  | Clock Generation                            | 3  |

| Figure 2-2  | Ezample of Circuit to Drive DACK Lines      | 5  |

| Section 3:  | DMA Controller                              | 7  |

| Figure 3-1  | Cascaded DMA Controllers                    | 7  |

| Figure 3-2  | Command Register                            | 17 |

| Figure 3-3  | Mode Register                               | 18 |

| Figure 3-4  | Request Register - Write Operations         | 19 |

| Figure 3-5  | Request Register - Read Operations          | 19 |

| Figure 3-6  | Request Mask Register - Set/Reset Operation | 20 |

| Figure 3-7  | Request Mask Register- Read Operations      | 20 |

| Figure 3-8  | Status Register - Read Only                 | 21 |

| Section 4:  | The Interrupt Controller                    | 23 |

| Figure 4-1  | Cascaded Interrupt Controllers              |    |

| Figure 4-2  | Interrupt Controller Block Diagram          |    |

| Figure 4-3  | Interrupt Sequence                          |    |

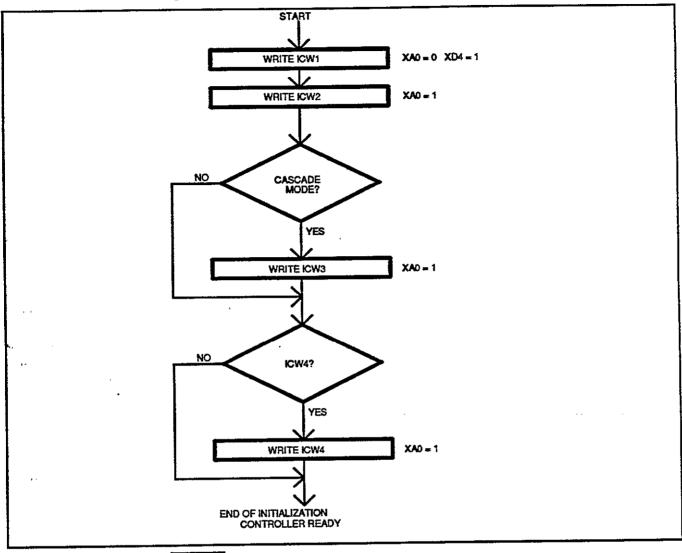

| Figure 4-4  | Initialization Sequence                     | 30 |

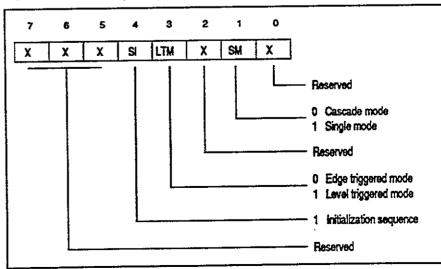

| Figure 4-5  | ICW1 Address 020H (0A0H) - Write Only       | 30 |

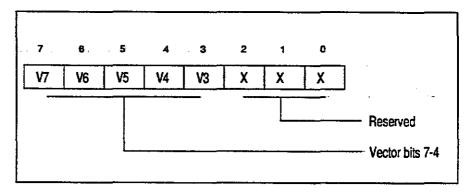

| Figure 4-6  | ICW2 Address 021H (0A1H) - Write Only       | 31 |

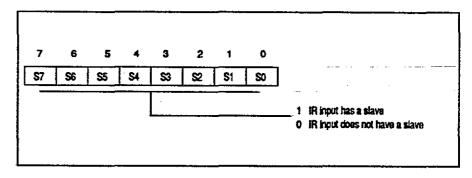

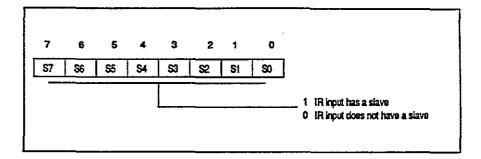

| Figure 4-7  | ICW3 Format for INTC1                       |    |

|             | Address 021H - Write Only                   | 31 |

| Figure 4-8  | ICW3 Format for INTC2                       |    |

|             | Address 0A1H - Write Only                   |    |

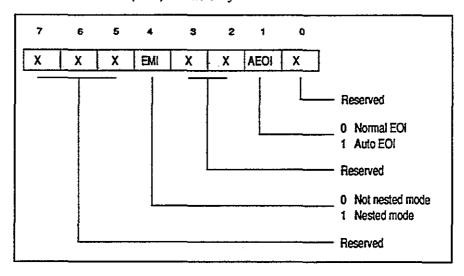

| Figure 4-9  | ICW4 Address 021H (A1H) - Write Only        |    |

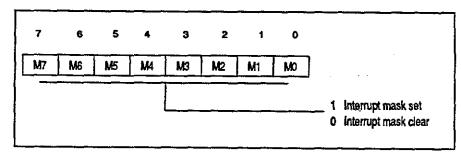

| Figure 4-10 | OCW1 Address 021H (0A1H) - Read/Write       |    |

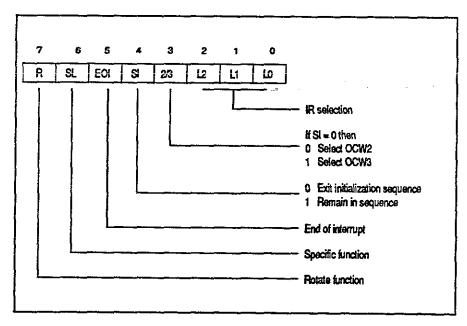

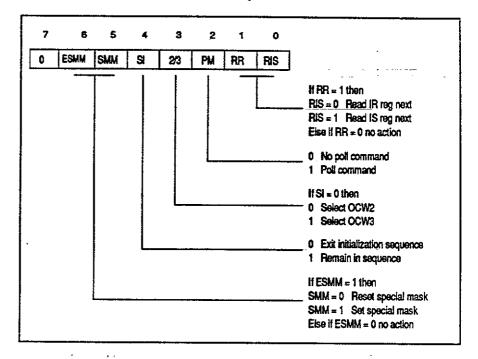

| Figure 4-11 | OCW2 Address 020H (0A0H) - Write Only       |    |

| Figure 4-12 | OCW3 Address 020H (0A0H) - Write Only       | 35 |

| Section 5:   | Programmable Interval Timer                                                  | 37  |

|--------------|------------------------------------------------------------------------------|-----|

| Figure 5-1   | Programmable Timer Control                                                   |     |

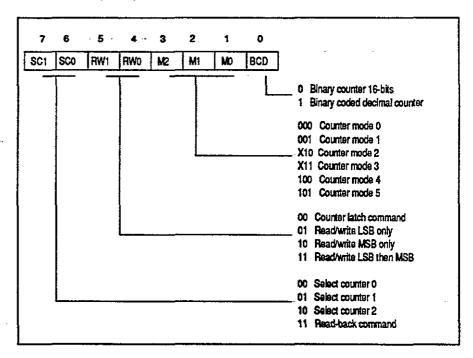

| Figure 5-2   | Control Word (043H)                                                          |     |

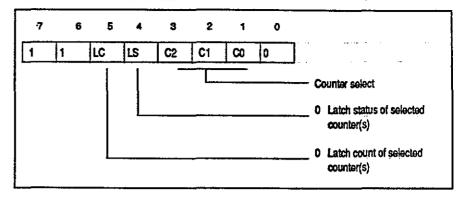

| Figure 5-3   | Read-Back Command Format                                                     |     |

| Figure 5-4   | Status Byte                                                                  | 41  |

| Section 6:   | System Interface                                                             | 45  |

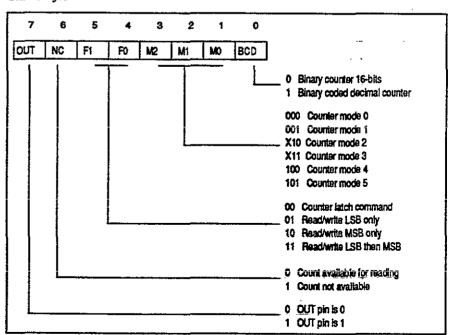

| Figure 6-1   | Keyboard Controller                                                          |     |

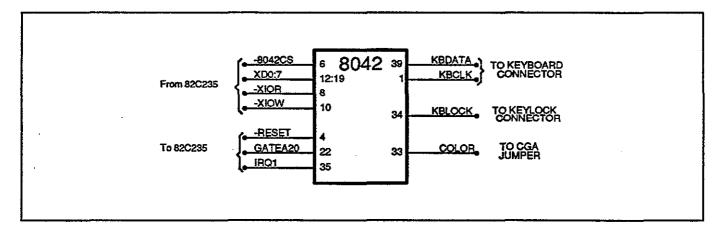

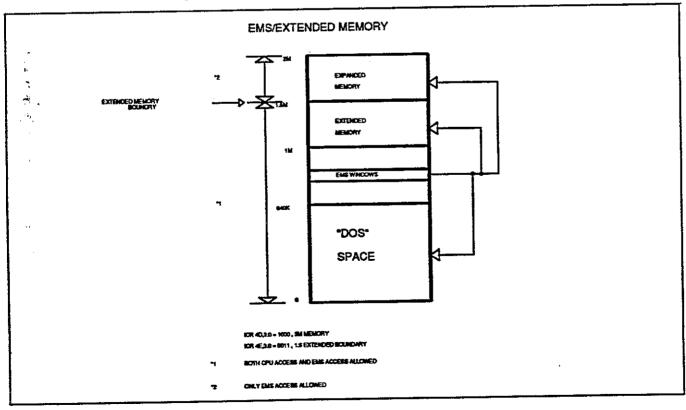

| Figure 6-2   | Expanded Memory Subsystem                                                    |     |

| Figure 6-3   | EMS/Extended Memory                                                          |     |

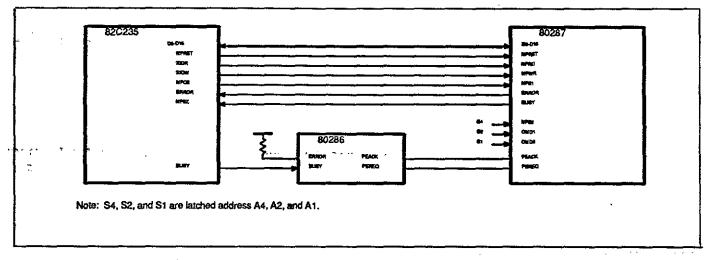

| Figure 6-4   | Numeric Coprocessor Interface                                                |     |

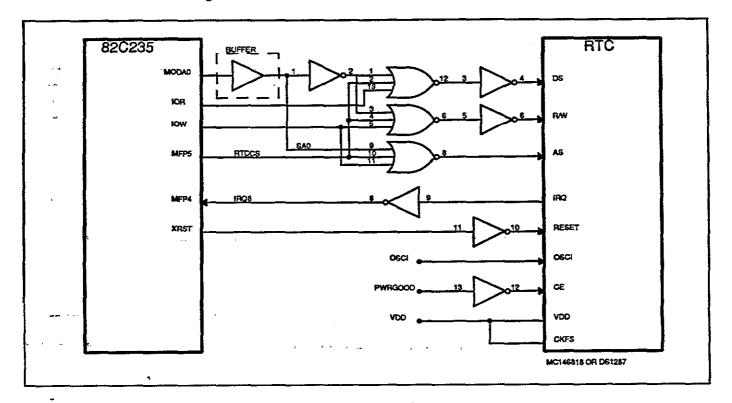

| Figure 6-5   | External Real Time Clock                                                     | 54  |

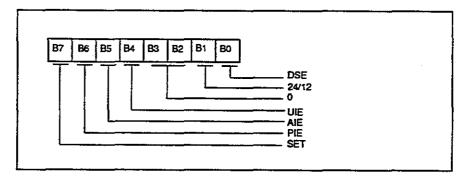

| Figure 6-6   | Register A (0AH) - Read/Write Except for Update-in-Progress                  | 57  |

| Figure 6-7   | Register B (0BH) - Read Only                                                 | 58  |

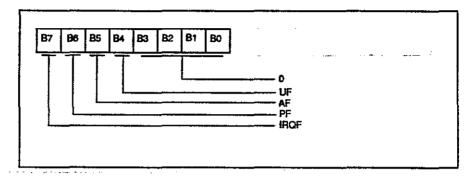

| Figure 6-8   | Register C (0CH) - Read Only                                                 |     |

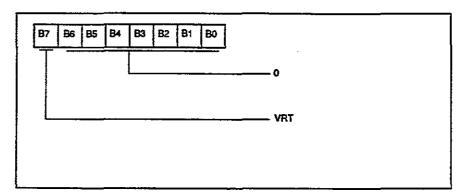

| Figure 6-9   | Register D (0DH) - Read Only                                                 | 60  |

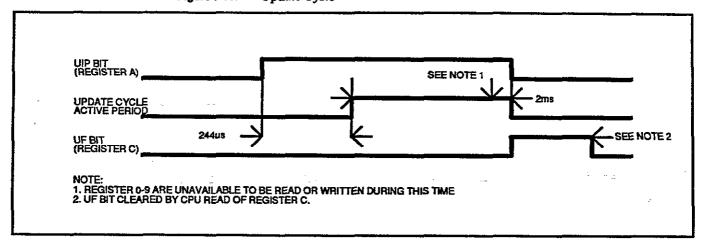

| Figure 6-10  | Update Cycle                                                                 | 61  |

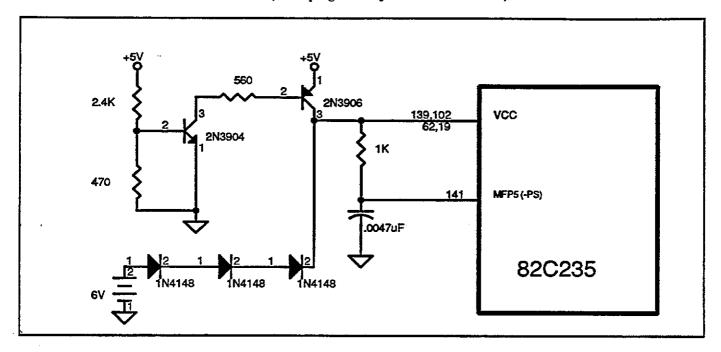

| Figure 6-11  | Power Conversion and Reset Circuitry (SCAT Programmed for Internal RTC Mode) | 62  |

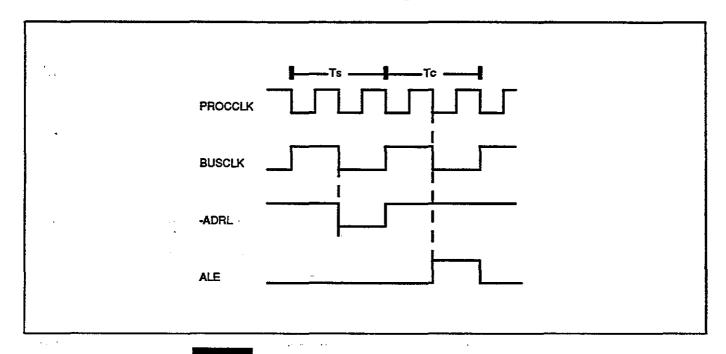

| Figure 6-12  | I/O Channel Relationships BUSCCLK = PROCCLK + 2                              |     |

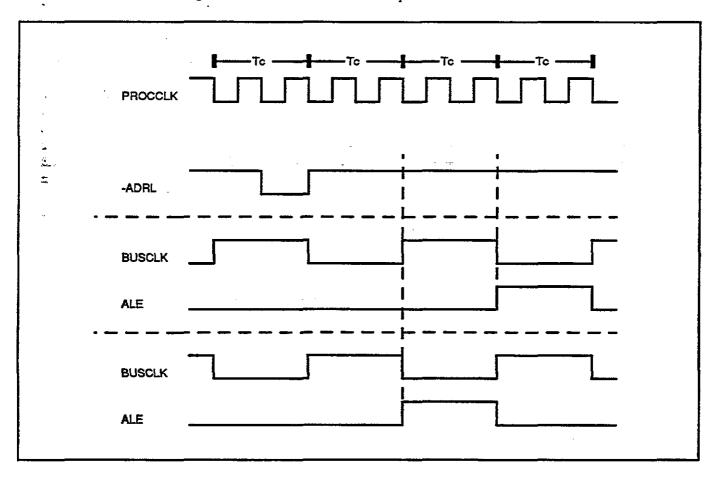

| Figure 6-13  | I/O Channel Relationships BUSCCLK = PROCCLK +4                               | 64  |

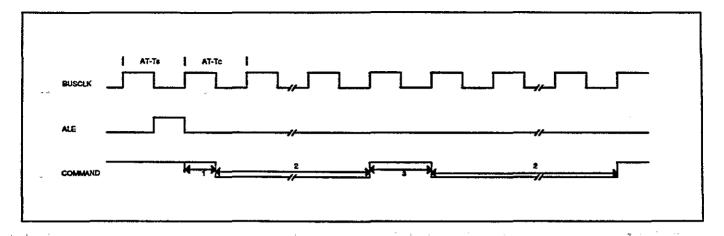

| Figure 6-14  | I/O Channel Default Cycle                                                    | 65  |

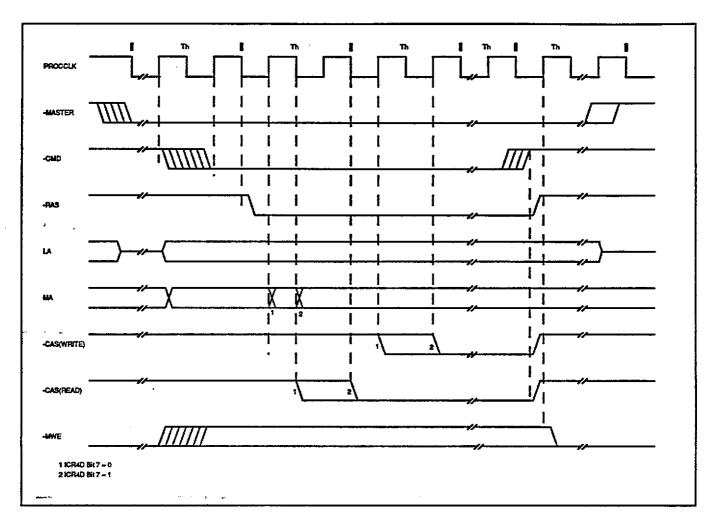

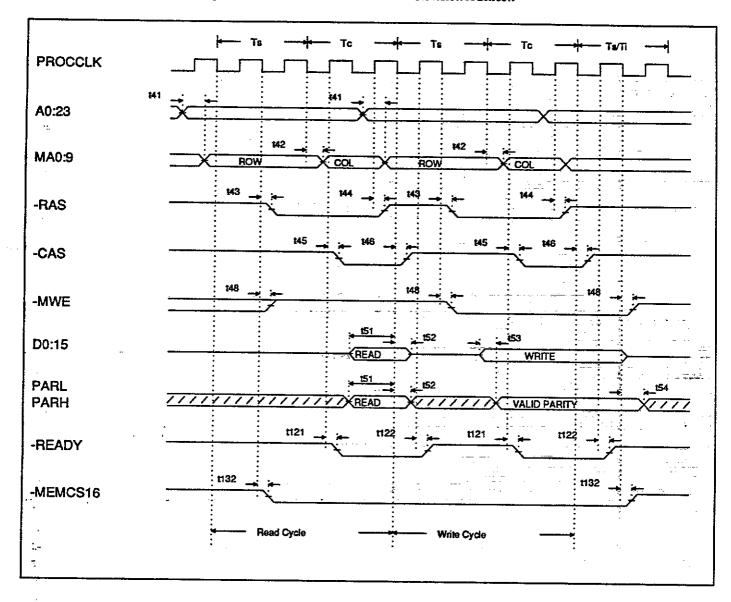

| Figure 6-15  | Master Mode DRAM Timing                                                      |     |

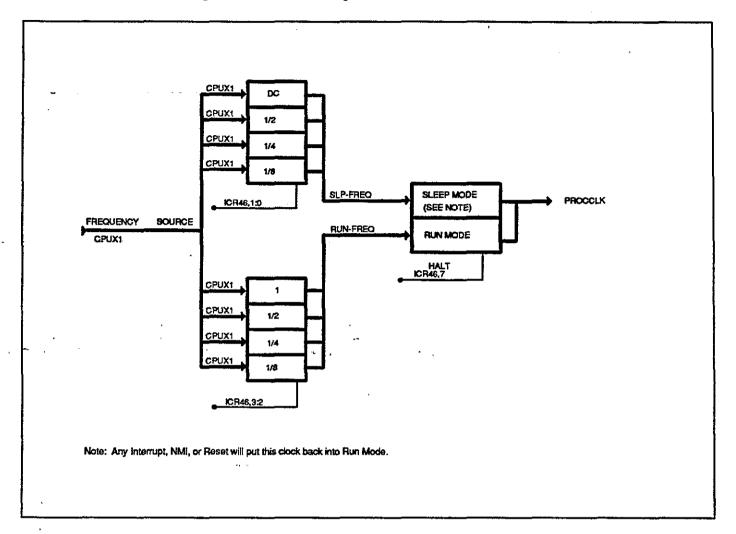

| Figure 6-16  | Clock Management                                                             | 67  |

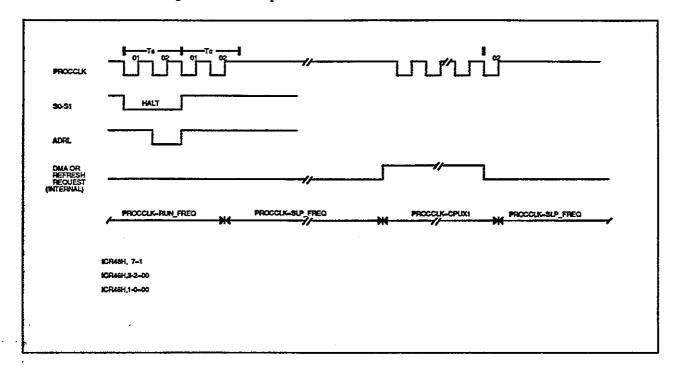

| Figure 6-17  | Sleep Mode                                                                   | 68  |

| Section 8:   | Pin Description                                                              | 83  |

| Figure 8-1   | 82C235 Pin Diagram                                                           | 92  |

| Section 10:  | Timing Diagrams                                                              | 103 |

| Figure 10-1  | Hardware Reset                                                               | 103 |

| Figure 10-2  | Clock Input                                                                  |     |

| Figure 10-3  | Clock Output                                                                 |     |

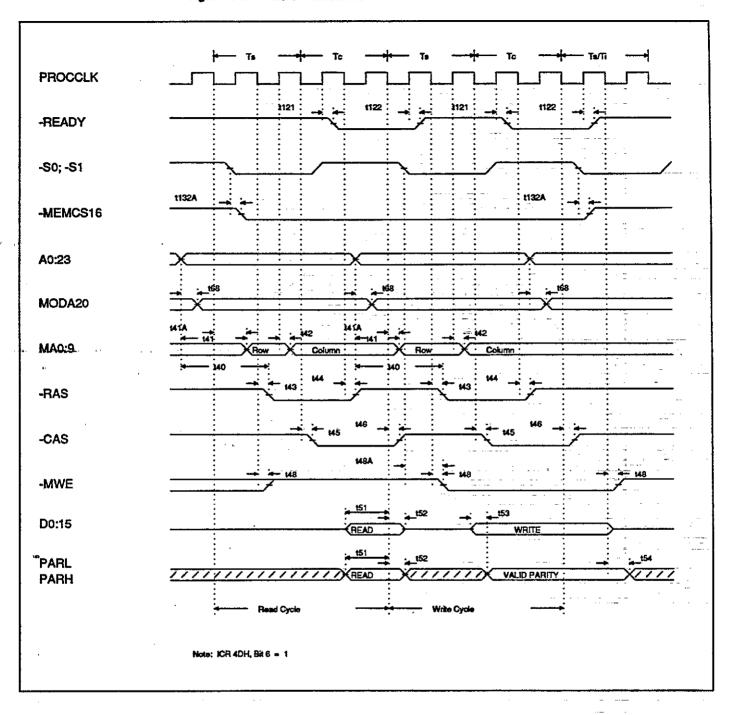

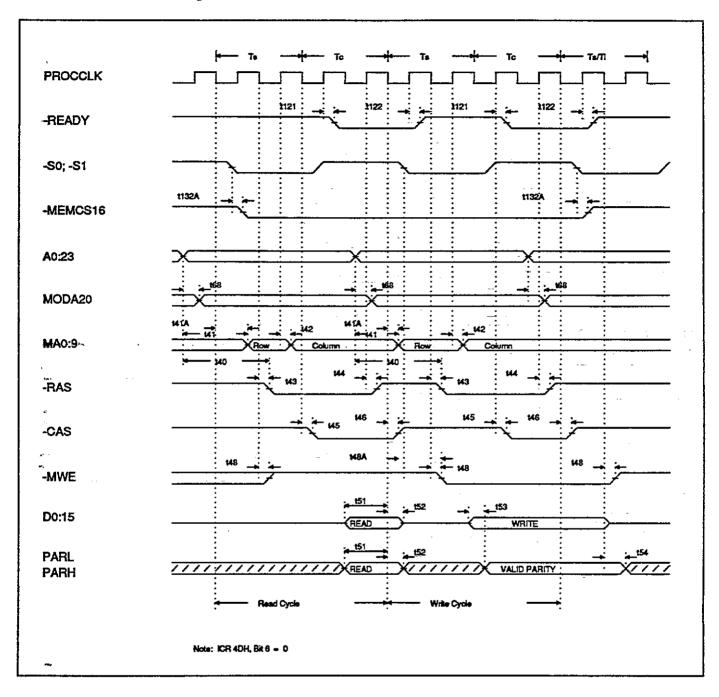

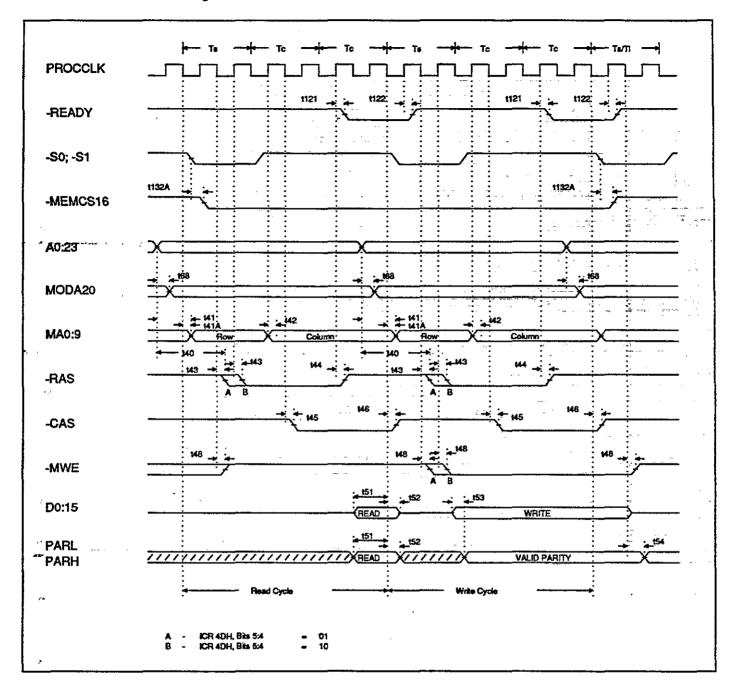

| Figure 10-4  | Zero Wait State DRAM                                                         |     |

| Figure 10-5  | Zero Wait State with Extended RAS DRAM                                       |     |

| Figure 10-6  | One Wait State DRAM                                                          |     |

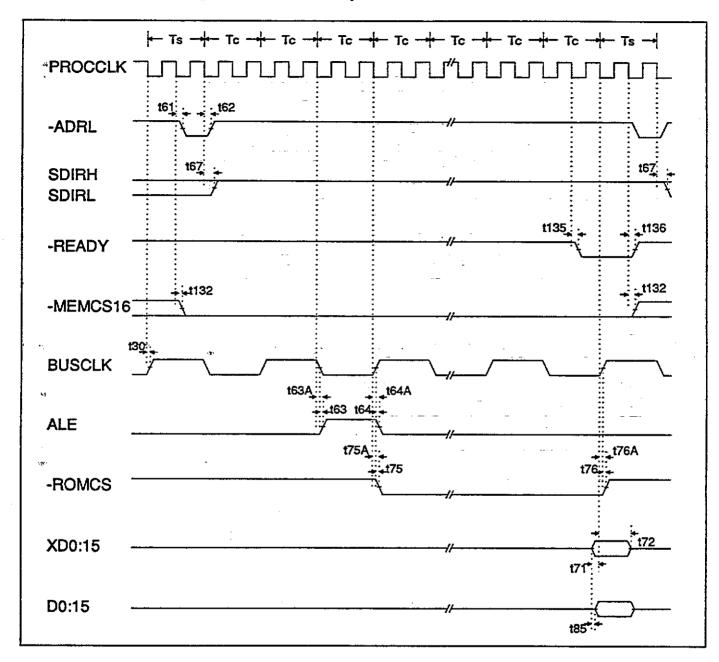

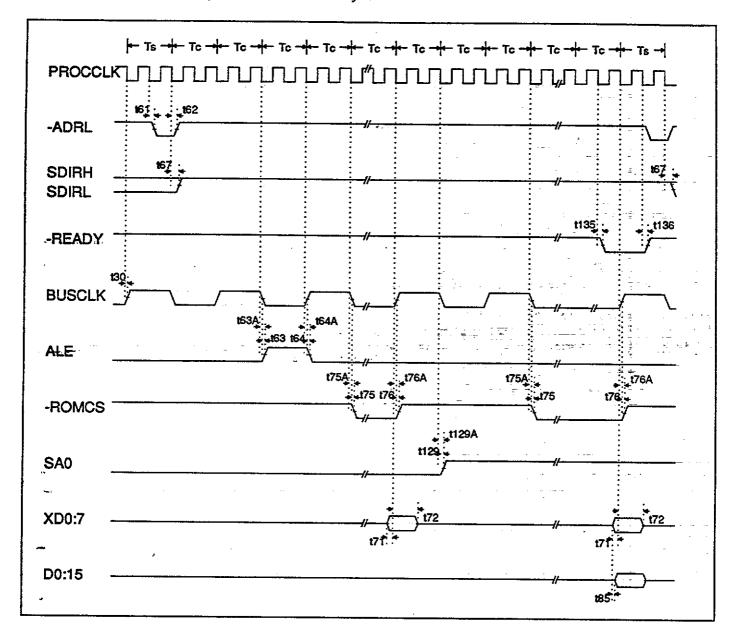

| Figure 10-7  | 16-Bit ROM Cycle                                                             |     |

| Figure 10-8  | 8-Bit ROM Cycle                                                              |     |

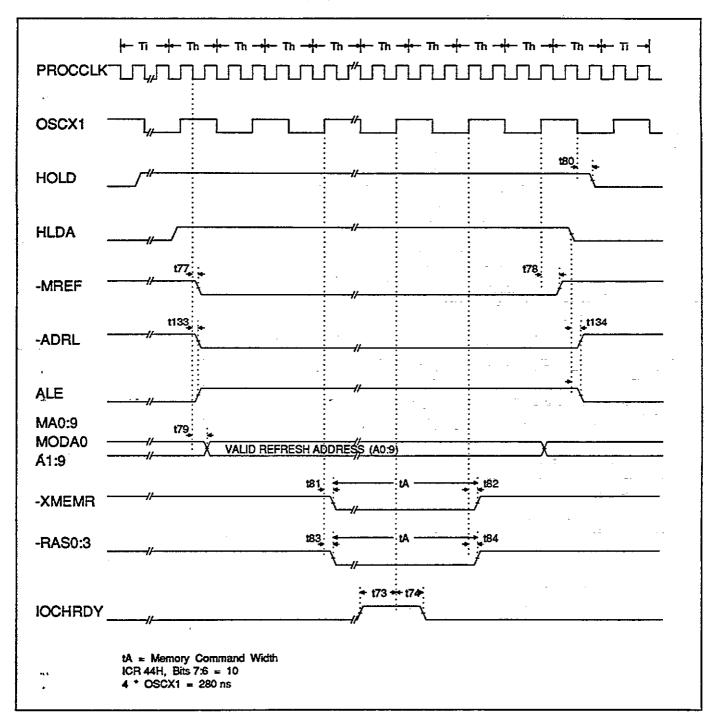

| Figure 10-9  | Memory Refresh Cycle                                                         |     |

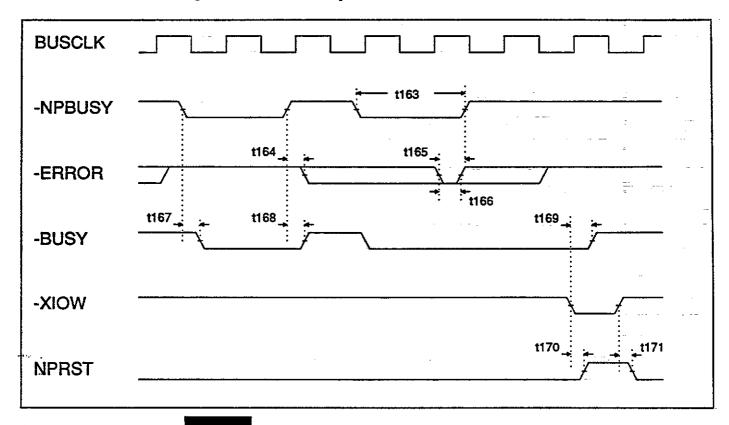

| Figure 10-10 | Numeric Coprocessor                                                          |     |

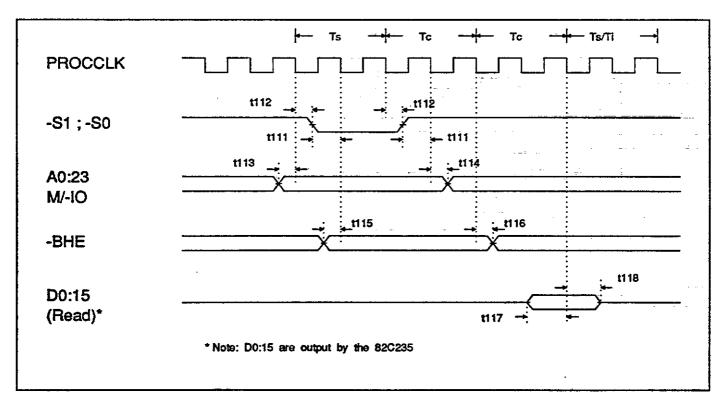

| Figure 10-11 | CPU Interface                                                                |     |

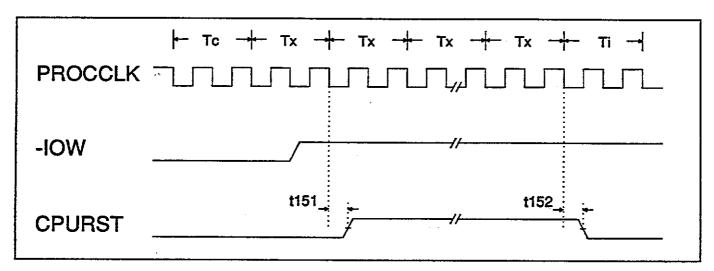

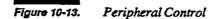

| Figure 10-12 | Software Reset                                                               | 112 |

| Figure 10-13 | Peripheral Control                          | 12 |

|--------------|---------------------------------------------|----|

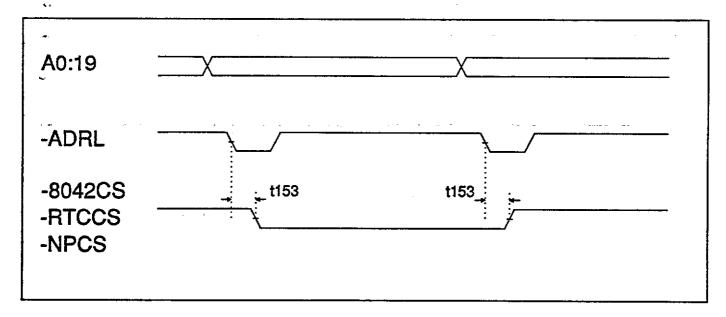

| Figure 10-14 | I/O Channel                                 | 13 |

| Section 11:  | Physical Dimensions 1                       | 15 |

| Figure 11-1  | 160-Pin Plastic Flat Package                | 15 |

| Appendix B:  | 82C235 Revision A Silicon                   | 21 |

| Figure B-1   | Memory Refresh Cycle - Revision A Silicon 1 | 26 |

| Figure B-2   | Zero Wait State DRAM - Revision A Silicon1  | 27 |

■ List of Figures

# List of Registers

| Section 7:   | Configuration Registers                 | . 69  |

|--------------|-----------------------------------------|-------|

| Index 01H    | DMA Wait-State Control Register         |       |

| Index 40H    | Version Register                        | 70    |

| Index 41H    | Clock Control Register                  | 70    |

| Index 42H    | Reserved Register                       | 70    |

| Index 43H    | Reserved Register                       |       |

| Index 44H    | Peripheral Control Register             | 71    |

| Index 45H    | Miscellaneous Status Register           | 72    |

| Index 46H    | Power Management Register               | 72    |

| Index 47H    | Reserved Register                       | 73    |

| Index 48H    | ROM Enable Register                     | 73    |

| Index 49H    | RAM Write Protect Register              | 74    |

| Index 4AH    | Shadow RAM Enable 1 Register            | 75    |

| Index 4BH    | Shadow RAM Enable 2 Register            |       |

| Index 4CH    | Shadow RAM Enable 3 Register            | 77    |

| Index 4DH    | DRAM Configuration Register             | 78    |

| Index 4EH    | Extended Boundary Register              |       |

| Index 4FH    | EMS Control Register                    | 80    |

| Port 61H     | Control Port/Status Register            | 80    |

| Port 70H     | RTC/CMOS Index and NMI Mask Register    | 81    |

| Port 71H     | RTC Data Register                       |       |

| Port 92H     | System Control Register                 | 81    |

| Appendix A:  | Address Mapping                         | 117   |

| Port OH-OFH  | DMA Controller I                        |       |

| Port 20H-21H | Interrupt Controller I                  |       |

| Port 22H-23H | Internal Configuration Registers (ICRs) |       |

| Port 40H-43H | Timer/Counter Registers                 |       |

| Port 61H-92H | Miscellaneous I/O Registers             |       |

| Port 81H-8BH | DMA Page Registers                      |       |

| Port A0H-A1H |                                         |       |

| Port COH-DEH | DMA Controller 2                        | . 119 |

| Port 0H-1H   | Coprocessor Registers                   | . 120 |

| Dow OTT ATT  | EMC Dana Danistana                      |       |

## List of Tables

| Section 2: | Bus Control                                                   |      |

|------------|---------------------------------------------------------------|------|

| Table 2-1  | Reset Strap Options                                           | 5    |

| Table 2-2  | Bus Control                                                   | 6    |

| Section 3: | DMA Controller                                                | 7    |

| Table 3-1  | DMA on the I/O Channel                                        | 8    |

| Table 3-2  | Rotating Priority Scheme                                      | 13   |

| Table 3-3  | DMA Address Extension Map                                     | 14   |

| Table 3-4  | DMA Registers                                                 | 15   |

| Section 4: | The Interrupt Controller                                      |      |

| Table 4-1  | Interrupts on the I/O Channel                                 |      |

| Table 4-2  | Format of Interrupt Vector                                    |      |

| Table 4-3  | Fixed Priority Mode Interrupt Assignments                     | 27   |

| Table 4-4  | Specific Rotation Mode Interrupt Assignments Before Rotation  | 28   |

| Table 4-5  | Specific Rotation Mode Interrupt Assignments After Rotation   | 28   |

| Table 4-6  | Automatic Rotation Mode Interrupt Assignments Before Rotation |      |

| Table 4-7  | Automatic Rotation Mode Interrupt Assignments After Rotation  |      |

| Table 4-8  | End of Interrupt Bit at Unity                                 |      |

| Table 4-9  | Specific Bit at Unity                                         |      |

| Table 4-10 | Rotate Function Bit at Unity                                  |      |

| Section 5: | Programmable Interval Timer                                   | . 37 |

| Table 5-1  | Programming the CTC                                           |      |

| Table 5-2  | Read/Write Counter Commands                                   |      |

| Table 5-3  | GATE2 Mode                                                    | 44   |

| Section 6: | System Interface                                              |      |

| Table 6-1  | I/O Port 92H                                                  |      |

| Table 6-2  | Multiplexing the <a20:1> Address Lines</a20:1>                |      |

| Table 6-3  | RAS Decode                                                    |      |

| Table 6-4  | Internal Configuration Register 4FH                           | 40   |

| Table 6-5  | Internal Configuration Register 4DH    | 49  |

|------------|----------------------------------------|-----|

| Table 6-6  | DRAM Memory Organization               | 50  |

| Table 6-7  | I/O Page Registers Defined             | 51  |

| Table 6-8  | Internal/External Real Time Clock Mode | 53  |

| Table 6-9  | Address Map for the Real Time Clock    | 55  |

| Table 6-10 | Time, Calendar, and Alarm Byte Format  | 56  |

| Table 6-11 | Periodic Interrupt Rate                |     |

| Table 6-12 | Divider/Prescaler Control Bits         |     |

| Table 6-13 | I/O Channel BUSCLK Periods             | 65  |

| Section 7: | Configuration Registers                |     |

| Table 7-1  | DRAM Configuration                     | 78  |

| Section 8: | Pin Description                        | 83  |

| Table 8-1  | Clock Input and Output Signals         |     |

| Table 8-2  | Local Bus Interface Signals            |     |

| Table 8-3  | Numeric Processor Interface Signals    |     |

| Table 8-4  | Memory Interface Signals               |     |

| Table 8-5  | I/O Channel Interface Signals          |     |

| Table 8-6  | Miscellaneous Signals                  |     |

| Table 8-7  | Alphabetical Pin Definitions           |     |

| Table 8-9  | Numerical Pin Definitions              | 91  |

| Section 9: | System Characteristics                 | .93 |

| Table 9-1  | Absolute Maximum Ratings               |     |

| Table 9-2  | Operating Conditions                   |     |

| Table 9-3  | Capacitive Characteristics             |     |

| Table 9-4  | DC Characteristics of the 82C235       |     |

| Table 9-5  | Reset Timings (16 MHz)                 |     |

| Table 9-6  | Clock Timings (16 MHz)                 |     |

| Table 9-7  | DRAM Control (16 MHz)                  |     |

| Table 9-8  | Tracking Parameters (16 MHz)           |     |

| Table 9-9  | 8-Bit Bus and ROM Cycle (16 MHz)       | 97  |

| Table 9-10 | CPU Interface (16 MHz)                 | 98  |

| Table 9-11 | Miscellaneous (16 MHz)                 |     |

| Table 9-12 | Reset Timings (12 MHz)                 |     |

| Table 9-13 | Clock Timings (12 MHz)                 | 99  |

| Table 9-14 | DRAM Control (12 MHz)                  | 100 |

| Table 9-15 | Tracking Parameters (12 MHz)           |     |

| Table 9-16 | 8-Bit Bus and ROM Cycle (12 MHz)       | 101 |

| Table 9-17 | CPU Interface (12 MHz)                 | 102 |

| Table 9-18 | Miscellaneous (12 MHz)                 | 102 |

|           | Address Mapping  Memory Address Map |     |

|-----------|-------------------------------------|-----|

| •         | 82C235 Revision A Silicon           |     |

| Table B-1 | Feature Differences Between         | 121 |

| Tanic D-1 | 82C235 A and 82C235 D               | 122 |

| Table B-2 | Reset Timing (12 MHz)               |     |

| Table B-3 | Clock Timing (12 MHz)               |     |

| Table B-4 | DRAM Control                        |     |

| Table B-5 | 8-Bit and ROM Cycle                 |     |

| Table B-6 | DMA Timing                          | 125 |

| Table B-7 | CPU Interface                       |     |

| Table B-8 | Miscellaneous Timing                |     |

List of Tables

## 1.1 Features

The 82C235 provides the following features:

- 80286 control logic and clocks that support CPU speeds of up to 16 MHz with zero (or one) wait-states

- A 146818-compatible real time clock with 114 bytes of CMOS RAM

- Two 8237-compatible DMA controllers

- Two 8259-compatible interrupt controllers

- An 8254-compatible programmable interval timer

- An 82284-compatible clock generation and READY interface

- An 82288-compatible bus controller

- A DRAM controller that supports up to 8 MB of DRAM

- A memory controller that provides shadow RAM and support for either 8-bit or 16-bit BIOS ROM

- A DRAM refresh controller

- 32 EMS page registers (LIM EMS 4.0-compatible)

- Interface logic for an 80287 numeric coprocessor

- Interface logic for an 8042 keyboard controller

- Fast Gate A20 and Fast CPU Reset logic

- Power management features

- Compact packaging in a single 160-pin plastic flat pack (160 PFP)

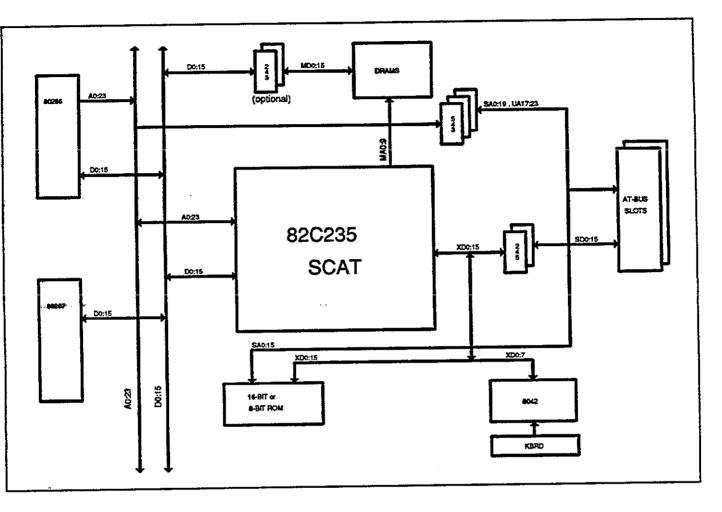

Figure 1-1 shows a block diagram of the 82C235.

Figure 1-1. 82C235 System Block Diagram

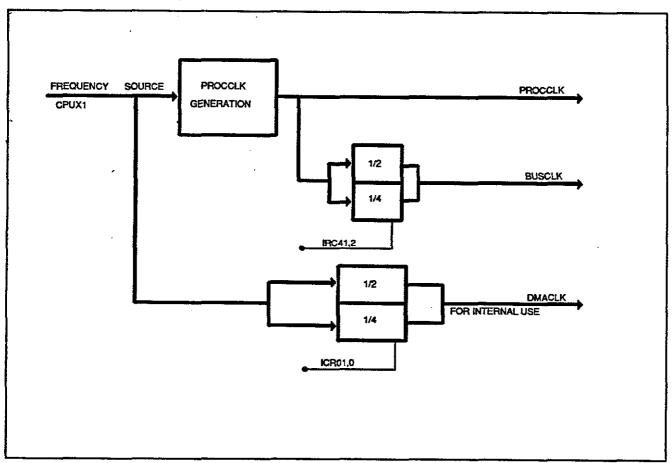

## 2.1 Clock Generation

An 82C235 clock generator produces the following signals:

Figure 2-1.

Clock Generation

- PROCCLK (processor clock) is an output clock for the 80286 processor.

PROCCLK can be set (with internal configuration register 46H, bits 3-2) for the following values:

- PROCCLK = CPUX1 (DMA or Refresh PROCCLK = CPUX1)

- o PROCCLK = CPUX1/2

- o PROCCLK = CPUX1/4

- o PROCCLK = CPUX1/8

During a DMA ore Refresh cycle, PROCCLK switches to PROCCLK = CPUX1 for the duration of HLDA active, it switches back to the set value when normal operation is resumed.

PROCCLK can also be halted in order to implement power management techniques (refer to Section 6.6 Power Management for further information). The frequency chosen for PROCCLK must be twice the frequency of the 80286 processor; e.g., for an 80286 with a speed of 16 MHz, PROCCLK must equal 32 MHz. PROCCLK is derived in one of two ways:

- From an external oscillator connected to CPUX1 (in which case CPUX2

is left unconnected), or

- 2. From an external crystal connected across CPUX1 and CPUX2.

- BUSCLK (bus clock) is an output clock for the I/O channel. BUSCLK

can be set (with internal configuration register 41H, bit 2) for the following

values:

- o BUSCLK≈PROCCLK/2

- BUSCLK ≈ PROCCLK/4

If PROCCLK is set to CPUX1/2, CPUX1/4, or CPUX1/8, a DMA or Refresh cycle switches to PROCCLK = CPUX1 and the resulting BUSCLK changes as well.

- OSC (oscillator) is a 14.31818 MHz output signal used by the I/O channel. The oscillator can be derived either from an external crystal connected to pins OSCX1 and OSCX2, or from an external oscillator connected to OSCX1 (OSCX2 is left unconnected).

- DMACLK (DMA clock) is an internal clock used by DMA controllers to time DMA operations. DMACLK can be set (with internal configuration register 01H, bit 0) to the following values:

- o DMACLK = CPUX1/2

- o DMACLK = CPUX1/4

## **Reset Strap Option**

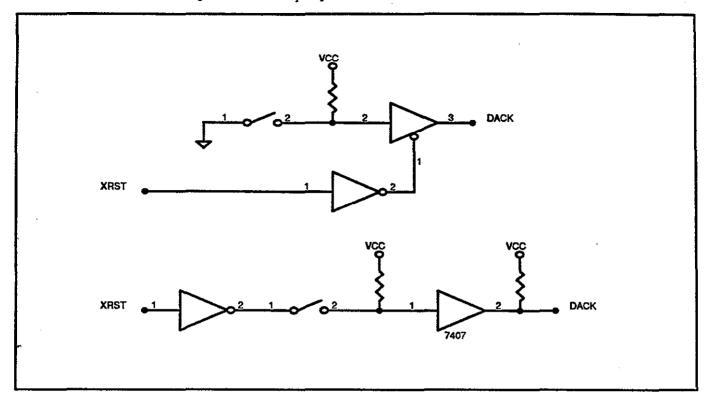

The 82C235 features a reset strap option. This option is employed to provide strap options without having to use dedicated input pins. The 82C235 uses -DACK lines to implement this feature. The -DACK lines are normally outputs, but during power-on situations they are used as input signals. Later, they convert to outputs for normal functions. A TTL device drives the signals low for strap option sampling, while a TTL device drives the signal levels high for the same purpose (see Figure 2-2). DACK5 and DACK7 must be driven to their respective strapping options. DACK6 is designated as reserved and should be pulled up with a 10K resistor. Table 2-1 describes the pins that are used in the reset strap option.

Table 2-1. Reset Strap Options

| Pin# | Normal Pin | Strap Pin | Comments                                |

|------|------------|-----------|-----------------------------------------|

| 89   | -DACK0     | SENSE0    | Reflects at ICR 45-0                    |

| 47   | -DACK1     | SENSE1    | Reflects at ICR 45-1                    |

| 45   | -DACK2     | SENSE2    | Reflects at ICR 45-2                    |

| 43   | -DACK3     | Reserved  | Must be pulled up to Vcc w/10K resistor |

| 91   | -DACK5     | -EXRTC    | Internal RTC (H) or external RTC (L)    |

| 93   | -DACK6     | Reserved  | Must be pulled up to Vcc w/10K resistor |

| 95   | -DACK7     | -16BITROM | 8-bit ROM (H) or 16-bit ROM (L)         |

The sense lines (0-2) are general purpose and can be used as per the specific system requirements.

## 2.2 Bus Control

Table 2-2 describes the data and address buses as shown in Figure 1-1 displayed earlier.

#### Table 2-2.

#### Bus Control

| 82C235 Pins           | Bus Name            | Description                                                                                                                             |  |  |

|-----------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D15-D0                | Local Data          | A 16-bit bidirectional bus connecting the 82C235, the 80286, and the optional 80287 to local memory or to the memory data (MD) buffers. |  |  |

| MD15-MD0              | Memory Data         | A 16-bit bidirectional bus connecting local DRAM and the memory data (MD) buffers.                                                      |  |  |

| XD15-XD0 X-Data       |                     | A 16-bit bidirectional bus connecting the 82C235 ROM, XD-bus peripherals, and S-Data (SD) buffers.                                      |  |  |

| SD15-SD0              | S-Data              | A 16-bit bidirectional bus connecting the I/O channel and the S-Data (SD) buffers.                                                      |  |  |

| A23-A00 Local Address |                     | A 24-bit address bus, driven by either the 80286 or the 82C235.                                                                         |  |  |

| SA19-SA0 S-Address    |                     | A latched, local address bus connecting the I/O channel to the XD-bus peripherals.                                                      |  |  |

| UA23-UA17             | Unlatched Address   | An unlatched address bus connected to the I/O channel. This bus must be latched except during quick mode.                               |  |  |

| MA9-MA0               | Multiplexed Address | A multiplexed address bus that is driven by the 82C235 to address DRAM.                                                                 |  |  |

#### **Bus Controller**

The internal bus controller, which is functionally similar to an 82288 bus controller, provides command generation and timing control for the AT-compatible I/O channel. To allow the processor to run faster than the I/O channel, DMA commands, timing, and accesses to the I/O channel can be programmed to run slower than local bus cycles.

### Local Bus Arbitration

Although the local bus is normally controlled by the 80286, the 82C235's internal DMA controller or refresh controller can request control by issuing a HOLD request to the 80286. When this occurs, the 80286 relinquishes control and issues HLDA (hold acknowledgement) to the 82C235.

Memory refresh and DMA functions are implemented within the 82C235 as independent bus masters. The 82C235 arbitrates these functions with internal logic and gains control of the local bus via the HOLD/HLDA protocol of the 80286. The 82C235 contains two DMA controllers that are compatible with the Intel 8237. Each controller is a four-channel DMA device that can generate the memory addresses and control signals necessary to transfer information between a peripheral device and memory directly. This allows high-speed information transfer with little CPU intervention.

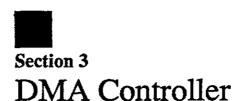

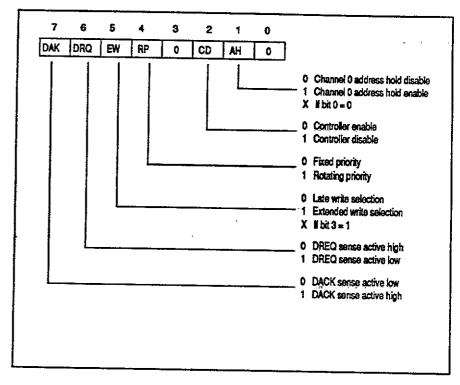

The two DMA controllers are internally cascaded to provide four DMA channels for transfers to 8-bit peripherals (DMA1) and three channels for transfers to 16-bit peripherals (DMA2). DMA2 Channel 0 provides the cascade interconnection for the two DMA devices, thereby maintaining IBM PC AT-compatibility. Figure 3-1 shows how the two controllers are cascaded.

Figure 3-1. Cascaded DMA Controllers

DMA channels 0-3 are used for 8-bit transfers, while channels 5-7 are used for 16-bit transfers. DMA operations are allowed within the full range of 16 MB memory through the use of DMA page registers.

The DMA clock, which controls DMA transfer rate and timing, is programmable. Its frequency is selectable for a rate equal to CPUX1/2 or CPUX1/4. (This is under control of internal configuration register 01H, bit 0). Wait-states during DMA operations are programmed with internal configuration Register 01H, bits 5-2.

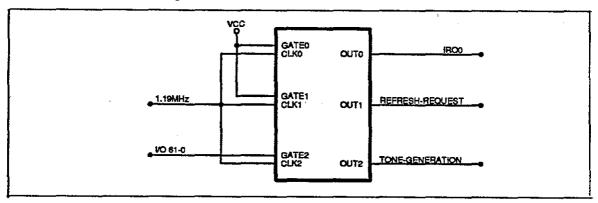

Refresh, which occurs at 15us intervals (nominally), is determined by counting down on the 1.19 MHz (OSCX1/12) clock. The refresh period is set by programming timer channel 1 of the 8254 timer/counter. Table 2-3 shows the use of DMA levels on the I/O channel. The DMA requests are shown by priority, starting with the highest level.

Table 3-1. DMA on the I/O Channel

| DMA Levei | System Board | I/O Channel    |  |

|-----------|--------------|----------------|--|

| DRQ0      | Not Used     | Available      |  |

| DRQ1      | Not Used     | Available      |  |

| DRQ2      | Not Used     | Diskette Drive |  |

| DRQ3      | Not Used     | Available      |  |

| DRQ5      | Not Used     | Available      |  |

| DRQ6      | Not Used     | Available      |  |

| DRQ7      | Not Used     | Available      |  |

DMA cycle length control is provided internally in the 82C235 allowing independent control for both 8-bit and 16-bit cycles. This is done through the programmable registers, which can extend command signals or insert wait states.

Each DMA channel has a pair of 16-bit counters and a reload register for each counter. The 16-bit counters allow the DMA to transfer blocks as large as 65,536 words. The register associated with each counter allows the channel to re-initialize without reprogramming. The following description of the DMA subsystem pertains to both DMA1 and DMA2 unless otherwise noted.

## 3.1 DMA Operation

During normal operation of the 82C235, the DMA subsystem is in either an Idle condition, a Program condition, or an Active condition. In the Idle condition, the DMA controller executes cycles consisting of only one state. The Idle state, SI, is the default condition, and the DMA remains in this condition unless the device has been initialized and one of the DMA requests is active; or the CPU attempts to access one of the internal registers.

When a DMA request becomes active, the device enters the Active condition and issues a hold request to the system. Once in the Active condition, the 82C235 generates the necessary memory addresses and command signals to accomplish a memory-to-I/O or an I/O-to-memory. Memory-to-I/O and I/O-to-memory transfers take place in one cycle. During transfers between

memory and I/O, data is presented on the system bus by either memory or the requesting device, and the transfer is completed in one cycle.

During transfers between memory and I/O, two commands are activated during the same cycle. In the case of a memory-to-I/O transfer, the 82C235 asserts both -MEMR and -IOW allowing data to be transferred directly to the requesting device from memory. Note that the 82C235 neither latches data from or drives data out on this type of cycle. The number of clock cycles required to transfer a word of data may be varied by programming the DMA, or optionally extended by the peripheral device. During an Active cycle, the DMA sequences through a series of states. Each state is one DMA clock cycle length, the number of states in a cycle varies depending on how the device is programmed and the type of cycle being performed. The states are labeled S0-S4. They are explained in detail in the section titled Active Condition.

#### Idle Condition

When no device is requesting service, the DMA is in an Idle condition that maintains the state machine in the SI state. During this time, the 82C235 samples the DREQ input pins every clock cycle. The internal select from the top level decoder and HLDA are also sampled at the same time to determine if the CPU is attempting to access the internal registers. When either of these situations occurs, the DMA exits the Idle condition. Note that the Program condition has priority over the Active condition since a CPU cycle has already started.

## **Program Condition**

The Program condition is entered whenever HLDA is inactive and internal select is active. During this time, address lines A0-A3 become inputs if DMA1 is selected, or A1-A4 become inputs if DMA2 is selected.

Note When DMA2 is selected, A0 is ignored.

These address inputs are used to select the DMA controller registers that are to be read or written to. Due to the large number of internal registers in the DMA subsystem, an internal flip-flop is used to supplement the addressing of the count and address registers. This bit is used to select between the high and low bytes of these registers. The flop-flop toggles each time a read or write occurs to any of the word count or address registers in the DMA. The internal flop-flop is cleared by a hardware RESET or a Master Clear command and may be set or cleared by the CPU issuing the appropriate command.

Special commands are supported by the DMA subsystem in the Program condition to control the device. These commands do not make use of the data bus but are derived from a set of addresses, the internal select, and -IOW or -IOR. These commands are Master Clear, Clear Register, Clear Mode Register Counter, Set, and Clear Byte Pointer Flip-Flop.

The 82C235 enables programming whenever HLDA has been inactive for one DMA clock cycle. It is the responsibility of the system to ensure that programming and HLDA are mutually exclusive. Erratic operation of the 82C235 can occur if a request for service occurs on an unmasked channel that is being programmed. The channel should be masked or the DMA disabled to prevent the 82C235 attempting to service a device with a channel which is partially programmed.

### **Active Condition**

The 82C235 DMA subsystem enters the Active condition whenever a software request occurs or a DMA request on an unmasked channel occurs and the device is not in the Program condition. The 82C235 then begins a DMA transfer cycle. In a Read cycle for example, after receiving a DREQ, the 82C235 issues an HOLD to the system. Until an HLDA is returned, the DMA remains in an Idle condition. On the next clock cycle, the DMA exits Idle and enters state S0. During S0, the device resolves priority and issues DACK on the highest priority channel requesting service. The DMA then proceeds to state S1, where the multiplexed addresses are output and latched. State S2 is then entered, at which time the 82C235 asserts -MEMR. The device then transitions into S3, where the -IOW command is asserted. The 82C235 remains in \$3 until the wait-state counter has decremented to zero and IOCHRDY is true. Note that at least one additional S3 occurs. Once a Ready condition is detected, the DMA enters S4, where both commands are de-asserted. In Burst Mode and Demand Mode, subsequent cycles begin in S2 unless the intermediate addresses require updating. In these subsequent cycles, the lower addresses are changed in S2. The DMA can be programmed on a channel-by-channel basis to operate in one of four modes. The four modes are described as follows.

#### Single Transfer Mode

This mode directs the DMA to execute only one transfer cycle at a time. DREQ must be held active until DACK becomes active. If DREQ is held active throughout the cycle, the 82C235 de-asserts HOLD and releases the bus after the transfer is complete. After HLDA is inactive, the 82C235 again asserts HOLD and executes another cycle on the same channel unless a request from a higher priority channel is received. In this mode, the CPU is allowed to execute at least one bus cycle between transfers.

Following each transfer, the word count is decremented and the address is incremented or decremented. When the word count decrements from 0000H to FFFFH, the terminal count bit in the status register is set and a TC pulse is generated. If the auto-initialization option is enabled, the channel re-initializes itself. If auto-initialize is not selected, the DMA sets the DMA request bit mask and suspends transferring on the channel.

#### Block Transfer Mode

When Block Transfer Mode is selected, the 82C235 begins transfers in response to either a DREQ or a software request. This continues until a terminal count (FFFFH) is reached, at which time TC is pulsed and the status register terminal count bit is set. In this mode DREQ need only be held active until -DACK is asserted. Auto-initialization is operational in this mode also.

#### **Demand Transfer Mode**

In Demand Transfer Mode, the DMA begins transfers in response to the assertion of DREQ and continues until either terminal count is reached or DREQ becomes inactive. This mode is normally used for peripherals that have limited buffering availability. The peripheral can initiate a transfer and continue until its buffer capacity is exhausted. The peripheral may re-establish service by again asserting DREQ. During idle periods between transfers, the CPU is released to operate and can monitor the operation by reading intermediate values from the address and word count registers. Once DREQ is de-asserted, higher priority channels are allowed to intervene. Reaching terminal count results in the generation of a TC pulse, the setting of the terminal count bit in the status register, and auto-initialization (if enabled).

#### Cascade Mode

This mode is used to interconnect more than one DMA controller, to extend the number of DMA channels while preserving the priority chain. In Cascade mode, the master DMA controller does not generate address or control signals. The DREQ and DACK signals of the master are used to interface the HOLD and HLDA signals of the slave DMA devices. Once the master has received an HLDA from the CPU in response to a DREQ caused by the HOLD from a slave DMA Controller, the master DMA controller ignores all inputs except HLDA from the CPU and DREQ on the active channel. This prevents conflicts between the DMA devices.

Figure 2-2 (shown earlier) displays the cascade interconnection between the two levels of DMA devices. Note that Channel 0 of DMA2 is internally connected for Cascade mode to DMA1. Additional devices can be cascaded to the available channels in either DMA1 or DMA2 since cascade is not limited to two levels for DMA controllers.

When programming cascaded controllers, begin with the device which is actually generating HOLD to the system (first level device) and then proceed to the second level devices. RESET causes the -DACK outputs to become active low and are placed into an inactive state. To allow the internal cascade between DMA1 and DMA2 to function correctly, the active low state of -DACK0 should not be modified. This is because the 82C235 has an inverter between -DACK0 of DMA2 and HLDA of DMA1. The first level device's DMA request mask bit

## 3.2 DMA Transfers

Three types of transfer modes are provided in the 82C235 DMA subsystem. These transfer types are as follows:

#### Read Transfer

Read transfers move data from memory to an I/O device by generating the memory address and asserting -MEMR and -IOW during the same cycle.

#### Write Transfer

Write transfers move data from an I/O device to memory by generating the memory address and asserting -IOR and MEMW.

## Verify Transfer

The verify transfer is a pseudo-transfer that is useful for diagnostics. In this type of transfer, the DMA operates as if it is performing a Read or Write Transfer by generating HOLD, addresses, and -DACK, but does so without asserting a command signal. Since no transfer actually takes place, IOCHRDY is ignored during Verify transfer cycles.

## 3.3 Auto-Initialization

Each of the four DMA channel Mode Registers contain a bit that causes the channel to re-initialize after reaching terminal count. During this process, referred to as Auto-Initialization, the Base Address and Base Word Count Registers, which were originally written by the CPU, are reloaded into the Current Address and Current Word Count Registers (both the base and current registers are loaded during a CPU write cycle). The base register remains unchanged during DMA Active cycles and can only be changed by the CPU. If the channel is programmed to auto-initialize, the request mask bit is not set upon reaching terminal count. This allows the DMA to continue operation without CPU intervention.

## 3.4 DREQ Priority

The 82C235 supports two schemes for establishing DREQ priority. The first is fixed priority, which assigns priority based on channel position. In this method, Channel 0 is assigned the highest priority. Priority assignment then progresses in order down through the channels, with Channel 3 receiving the lowest priority.

The second type of priority assignment is rotating priority (see Table 2-4). In this scheme the ordering of priority from Channel 0 to Channel 3 is maintained but the actual assignment of priority changes. The channel most recently serviced is assigned the lowest priority and, since the order of priority assignment remains fixed, the remaining three channels rotate accordingly.

Table 3-2. Rotating Priority Scheme

| First Arbitration |             | Second<br>Arbitration |             | Third Arbitration | Priority |

|-------------------|-------------|-----------------------|-------------|-------------------|----------|

| Channel 0         | Cycle Grant | Channel 2             | Cycle Grant | Channel 3         | Highest  |

| Channel 1         | Cycle Grant | Channel 3             | ]           | Channel 0         |          |

| Channel 2         |             | Channel 0             |             | Channel 1         |          |

| Channel 3         |             | Channel 1             |             | Channel 2         | Lowest   |

Note A box around a channel number indicates a requested channel.

In instances where multiple requests occur at the same time, the 82C235 issues an HOLD but does not freeze the priority logic until HLDA is returned. Once HLDA becomes active, the priority logic is frozen and DACK is asserted on the highest requesting channel. Priority is not reevaluated until HLDA is deactivated.

## 3.5 Address Generation

The DMA Page Register is a set of 16 8-bit registers in the 82C235 that are used to generate the high order addresses during DMA cycles. Only eight of the registers are actually used, but all 16 are included to maintain IBM PC/AT compatibility. Each DMA channel has a register associated with it with the exception of Channel 0 of DMA2, which is used for internal cascading to DMA1. Assignment of each of these registers is shown in Table 2-5 along with its Read/Write address.

During Demand and Block Transfers, the 82C235 generates multiple sequential transfers. For most of these transfers the information in the external address latches remains the same, eliminating the need to be re-latched. Since the need to update the latches occurs only when a carry or borrow from the lower 8-bits of the Address Counter exists, the 82C235 updates the latch contents only when necessary. The 82C235 therefore executes S1 cycles only when necessary, resulting in an overall through-put improvement.

Table 3-3. DMA Address Extension Map

| Address | Register Function Unused      |  |

|---------|-------------------------------|--|

| 080H    |                               |  |

| 081H    | 8-bit DMA Channel 2 (-DACK2)  |  |

| 082H    | 8-bit DMA Channel 3 (-DACK3)  |  |

| 083H    | 8-bit DMA Channel 1 (-DACK1)  |  |

| 084H    | Unused                        |  |

| 085H    | Unused                        |  |

| 086Н    | Unused                        |  |

| 087H    | 8-bit DMA Channel 0 (-DACK0)  |  |

| 088H    | Unused                        |  |

| 089H    | 16-bit DMA Channel 2 (-DACK6) |  |

| C8AH    | 16-bit DMA Channel 3 (-DACK7) |  |

| 08BH    | 16-bit DMA Channel 1 (-DACK5) |  |

| 08CH    | Unused                        |  |

| 08DH    | Unused                        |  |

| 08EH    | Unused                        |  |

| 08FH    | Refresh Cycle                 |  |

| DMA1         | DMA2 | -XIOR    | -XIOW | Flip-Flop | Register Function                                     |

|--------------|------|----------|-------|-----------|-------------------------------------------------------|

| 000H         | 0C0H | 0        | 1     | 0 .       | Read Channel 0 Current Address Low Byte               |

|              |      | 0        | 1     | 1         | Read Channel 0 Current Address High Byte              |

| <u>.</u> ~   |      | 1        | 0     | 0         | Write Channel 0 Base and Current Address Low Byte     |

|              |      | 1        | 0     | 1         | Write Channel 0 Base and Current Address High Byte    |

| <b>0</b> 01H | OC2H | 0        | 1     | 0         | Read Channel 0 Current Word Count Low Byte            |

|              |      | 0        | 1     | 1         | Read Channel 0 Current Word Count High Byte           |

|              |      | 1        | 0     | 0         | Write Channel 0 Base and Current Word Count Low Byte  |

|              |      | 1        | 0     | 1         | Write Channel 0 Base and Current Word Count High Byte |

| 002H         | OC4H | 0        | 1     | 0         | Read Channel 1 Current Address Low Byte               |

|              |      | 0        | 1     | 1         | Read Channel 1 Current Address High Byte              |

|              |      | 1        | 0     | 0         | Write Channel 1 Base and Current Address Low Byte     |

|              |      | <u> </u> | 0     | 1         | Write Channel I Base and Current Address High Byte    |

| 003H         | 0C6H | Ó        | 1     | 0         | Read Channel 1 Current Word Count Low Byte            |

|              |      | 0        | 1     | 1         | Read Channel 1 Current Word Count High Byte           |

|              |      | 1        | 0     | 0         | Write Channel 1 Base and Current Word Count Low Byte  |

|              |      | 1        | 0     | 1         | Write Channel I Base and Current Word Count High Byte |

| 004H         | 0C8H | 0        | 1     | 0         | Read Channel 2 Current Address Low Byte               |

|              |      | 0        | 1     | 1         | Read Channel 2 Current Address High Byte              |

|              |      | 1        | 0     | 0         | Write Channel 2 Base and Current Address Low Byte     |

|              |      | 1        | 0     | 1         | Write Channel 2 Base and Current Address High Byte    |

| 005H         | 0CAH | 0        | 1     | 0         | Read Channel 2 Current Word Count Low Byte            |

|              |      | 0        | 1     | 1         | Read Channel 2 Current Word Count High Byte           |

|              |      | 1        | Ō     | Ō         | Write Channel 2 Base and Current Word Count Low Byte  |

|              |      | 1        | o '   | 1         | Write Channel 2 Base and Current Word Count High Byte |

| 006H         | 0CCH | 0        | 1     | 0         | Read Channel 3 Current Address Low Byte               |

| • •          |      | 0        | 1     | 1         | Read Channel 3 Current Address High Byte              |

|              |      | 1        | . 0   | Ö         | Write Channel 3 Base and Current Address Low Byte     |

|              |      | 1        | 0     | 1         | Write Channel 3 Base and Current Address High Byte    |

| 007H         | 0CEH | 0        | 1     | 0         | Read Channel 3 Current Word Count Low Byte            |

|              |      | 0        | 1     | 1         | Read Channel 3 Current Word Count High Byte           |

|              |      | 1        | 0     | 0         | Write Channel 3 Base and Current Word Count Low Byte  |

|              |      | 1        | 0     | 1         | Write Channel 3 Base and Current Word Count High Byte |

| 008H         | 0D0H | 0        | 1     | X         | Read Status Register                                  |

|              |      | 1        | O     | X         | Write Command Register                                |

| 009H         | 0D2H | 0        | 1     | Х         | Read DMA Request Register                             |

|              |      | 1        | 0     | x         | Write DMA Request Register                            |

| 00AH         | 0D4H | 0        | 1     | X         | Read Command Register                                 |

| ₹            |      | 1        | 0     | x         | Write Single Bit DMA Request Mask Register            |

| 00BH         | 0D6H | 0        | 1     | X         | Read Mode Register                                    |

|              |      | 1        | 0     |           | Write Mode Register                                   |

| 00CH         | 0D8H | 0        | 1     | X         | Set Byte Pointer Flip-Flop                            |

|              |      | . 1      | 0     |           | Clear Byte Pointer Flip-Flop                          |

| 00DH         | 0DAH | 0        | 1     |           | Read Temporary Register                               |

|              |      | 1.       | 0     |           | Master Clear                                          |

| DOEH         | 0DCH | 0        | 1     |           | Clear Mode Register Counter                           |

|              |      | 1        | 0     |           | Clear All DMA Request Mask Register Bits              |

| 00FH         | 0DEH | 0        | 1     |           | Read All DMA Request Mask Register Bits               |

|              |      | _        | 0     |           | Write All DMA Request Mask Register Bits              |

## 3.6 Current Address Register

Each DMA channel has a 16-bit Current Address Register that holds the address used during transfers. Each channel can be programmed to increment or decrement this register whenever a transfer is completed. This register can be read or written by the CPU in consecutive 8-bit. If Auto-Initialization is selected, this register is reloaded from the Base Address Register upon reaching terminal count in the Current Word Count Register. Channel 0 can be prevented from incrementing or decrementing by setting the Address Hold Bit in the Command Register.

## 3.7 Current Word Count Register

Each channel has a Current Word Count Register that determines the number of transfers to perform. The actual number of transfers performed is one greater than the value programmed into the register. The register is decremented after each transfer until it goes from zero to FFFFH. When this roll-over occurs, the 82C235 generates TC, suspends operation on that channel, sets the appropriate Request Mask Bit or Auto-Initialize, and continues.

## 3.8 Base Word Count Register

This register preserves the initial value of the Current Word Count Register. It is also a write-only register that is loaded by writing to the Current Word Count Register. This register is loaded in the Current Word Count Register during Auto-Initialization.

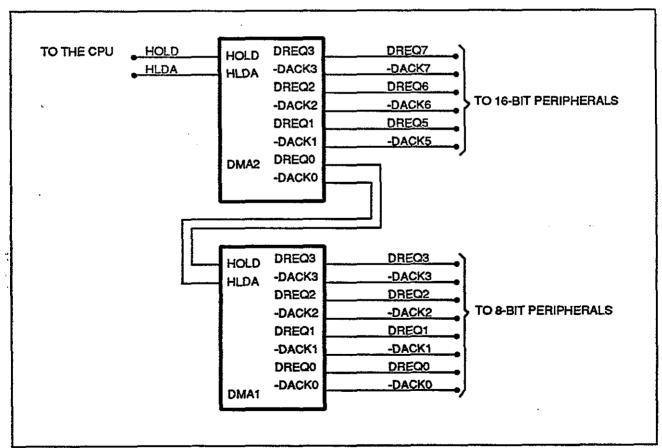

## 3.9 Command Register

This register controls the overall operation of a DMA subsystem. The register can be read or written to by the CPU and is cleared by either a system RESET or a Master Clear command.

- AH: Writing a one to bit I enables the address hold feature in Channel 0 when performing memory-to-memory transfers.

- CD: Bit 2 is the master disable for the DMA controller. Writing a one to this location disables the DMA subsystem (DMA1 or DMA2). This function is normally used whenever the CPU needs to reprogram one of the channels to prevent DMA cycles from occurring.

- RP: Writing a one to bit 4 causes the 82C235 to utilize a rotating priority scheme for honoring DMA requests. The default condition is fixed priority.

- EW: Extended Write is enabled by writing a one to bit 5, causing the write commands to be asserted one DMA cycle earlier during a transfer. The read and write commands both begin in state S2 when enabled.

- DRQ: DREQ active level is determined by bit 6. Writing a one in this bit position causes DREQ to become active low.

- DAK: DACK active level is determined by bit 7. Programming a one in this bit position makes DACK an active high signal.

## 3.10 Mode Register

Each DMA channel has a Mode Register associated with it. All four Mode Registers reside at the same I/O address. Bits 0 and 1 of the Write Mode Register command determine which Mode Register is written to the channel. The remaining six bits control the mode of the selected channel. Each channel's Mode Register can be read by sequentially reading the Mode Register location.

A Clear Mode Register Counter command is provided to allow the CPU to restart the mode read process at a known point. During mode read operation, bits 0 and 1 are one.

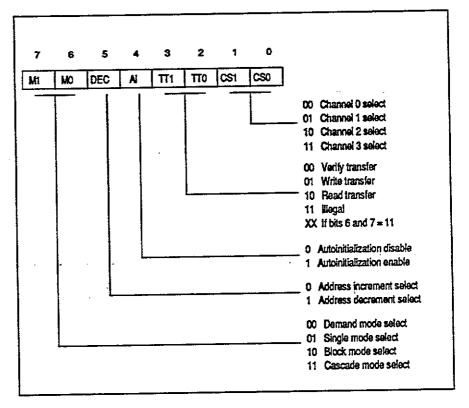

Figure 3-3.

#### Mode Register

CS<0:1>: Channel Select bits 0 and 1 determine which channel's Mode Register is written to. Read back of a mode register results in bits 0 and 1 both being ones.

TT: Bits 2 and 3 control the type of transfer that is to be performed.

Al: The Auto-Initialization function is enabled by writing a one in bit 4 of the Mode Register.

DEC: Determines direction of the address counter. A one in bit 5 decrements the address after each transfer.

M0: Mode selection for each channel is accomplished by bits 6 and 7.

## 3.11 Request Register

This is a four bit register used to generate software requests (DMA service can be requested either externally or under software control). Request Register bits can be set or reset independently by the CPU. The Request Mask has no effect on software generated requests. All four bits are read in one operation and appear in the lower four bits of the byte. Bits 4 through 7 are read as ones. All

four request bits are cleared to zero by a system RESET. The format for Request Register Write Operations is shown as follows:

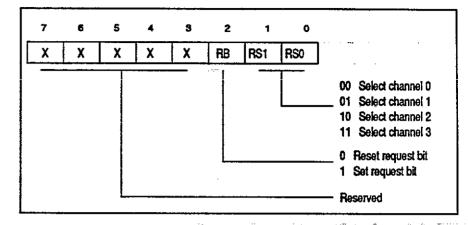

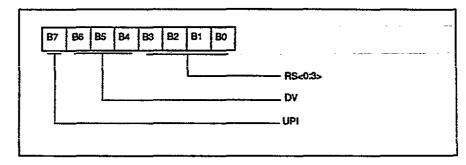

Figure 3-4. Request Register - Write Operations

RS<0:1>: Channel Select 0 and 1 determine which channel's Mode Register is written to. Read back for the mode register results in bits zero and one both being ones.

RB: The request bit is set by writing a one to bit 2. RS<0:1> select which bit (channel) is to be manipulated.

The format for Request Register Read Operations is shown as follows.

Figure 3-5. Request Register - Read Operations

RC<0:3>: During a Request Register read, the state of the request bit associated with each channel is returned in bits 0 through 3 of the byte. The bit position corresponds to the channel number.

## 3.12 Request Mask Register

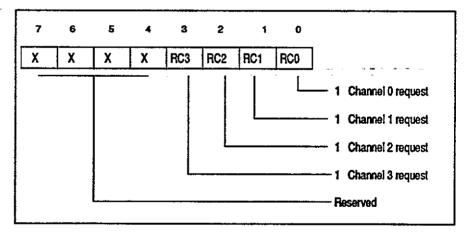

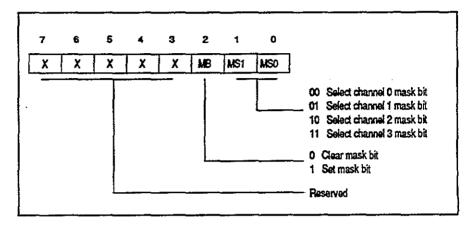

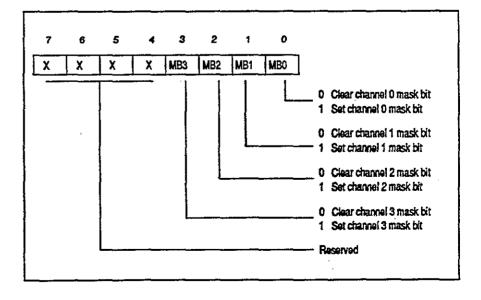

The Request Mask Register is a set of four bits that are used to inhibit external DMA requests from generating transfer cycles. This register can be programmed in two ways. Each channel can be independently masked by writing to the Write Single Mask Bit location. The data format for this operation is shown as follows.

Figure 3-6.

Request Mask Register - Set/Reset Operation

MS<0:1>: These two bits select the specific mask bit that is to be set or reset.

MB:

Bit 2 sets or resets the request mask bit for the channel selected by MS1 and MS0. Writing a one in this bit position sets the mask, inhibiting external requests.

Alternatively, all four mask bits can be programmed in one operation by writing to the Write All Mask Bits address. The data format for this function and the Read All Mask Bits function is shown as follows.

Figure 3-7.

Request Mask Register - Read Operations

MB<0:3>: Each bit position in the field represents the mask bit of a channel. The mask bit number corresponds to the channel number associated with the mask bit. All four mask bits are set following a system RESET or a Master Clear command. Individual channel mask bits are set as a result of terminal count being reached, if Auto-Initialize is disabled. The entire register can be cleared, enabling all four channels, by performing a Clear Mask Register operation.

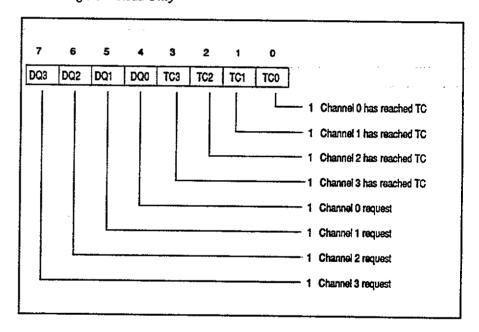

## 3.13 Status Register

The status of all four channels can be determined by reading the Status Register. Information is available to determine if a channel has reached terminal count and whether an external service request is pending. Bit 0-3 of this register are cleared by a system RESET, a Master Clear, or each time a Status Read takes place. Bits 4-7 are cleared by a systemRESET, a Master Clear, or the pending request being de-asserted. Bits 4-7 are not affected by the state of the Mask Register Bits. The channel number corresponds to the bit position.

Figure 3-8.

Status Register - Read Only

## 3.14 Special Commands

Five special commands are provided to make the task of programming the device easier. These commands are activated as a result of a specific address and assertion of either an -IOR or -IOW. Information on the data lines is ignored by the 82C235 whenever an -IOW activated command is issued. Also, data returned on -IOR activated commands is invalid. Descriptions of the five special commands follow:

## Clear Byte Pointer Flip-Flop

This command is normally executed prior to reading or writing to the address or word count register. This initializes the flop-flop to point to the low byte of the register and allows the CPU to read or write the register bytes in correct sequence.

## Set Byte Pointer Flip-Flop

Setting the Byte Pointer Flip-Flop allows the CPU to adjust the pointer to the high byte of an address or word count register.

#### Master Clear

This command has the same effect as a hardware RESET. The Command Register, Status Register, Request Register, Temporary Register, Mode Register Counter, and Byte Pointer Flip-Flop are cleared and the Request Mask Register is set. Immediately following Master Clear or RESET, the DMA is in the Idle Condition.

## Clear Request Mask Register

This command enables all four DMA channels to accept requests by clearing the mask bits in the register.

#### Section 4

# The Interrupt Controller

The 82C235 incorporates two programmable interrupt controllers that are compatible with the Intel 8259A. The controllers accept requests from peripherals, resolve priority on pending interrupts and interrupts in service, issue an interrupt request to the CPU, and provide a vector that is used as an index by the CPU to determine which interrupt service routine to execute.

A variety of priority assignment modes are provided, which can be reconfigured at any time during system operation, allowing the complete interrupt subsystem to be restructured, based on the system requirements.

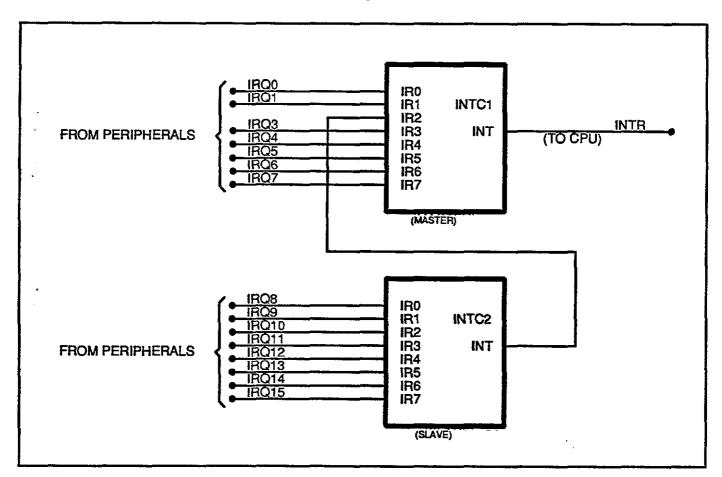

The controllers are cascaded in a fashion compatible with the IBM PC AT (refer to Figure 4-1).

Figure 4-1. Cascaded Interrupt Controllers

Table 4-1. Interrupts on the I/O Channel

| Interrupt | System Board                  | VO Channel    |

|-----------|-------------------------------|---------------|

| NMI       | Parity Check                  | -IOCHCK       |

| IRQ0      | Timer                         | Not Available |

| IRQ1      | Keyboard                      | Not Available |

| IRQ8†     | Real-Time Clock               | Not Available |

| IRQ9      | Not Used                      | Available     |

| IRQ10     | Not Used                      | Available     |

| IRQ11     | Not Used                      | Available     |

| IRQ12     | Not Used                      | Available     |

| IRQ13     | Coprocessor                   | Not Avzilable |

| IRQ14     | Not Used                      | Available     |

| IRQ15     | Not Used                      | Available     |

| IRQ3      | Serial Port 2                 | Available     |

| IRQ4      | Serial Port 1                 | Available     |

| IRQ5      | Parallel Port 2               | Available     |

| IRQ6      | Hard Disk and Diskette Drives | Available     |

| IRQ7      | Parrel Port 1                 | Available     |

†In internal RTC mode, IRQ8 is an internal signal.

The two devices are interconnected and must be programmed to operate in Cascade Mode (see Figure 4-1) for proper operation of all 16 interrupt channels. INTC1 is located at I/O Ports 020H-021H and is configured for Master operation in Cascade Mode. INTC2 is a slave device, and is located at I/O Addresses 0A0H-0A1H. The Interrupt Request output signal from INTC2 (INT) is internally connected to the interrupt request input Channel 2 IR2 of INTC1. The address decoding and Cascade interconnection matches that of the IBM PC AT.

Two additional interconnections are made to the interrupt request inputs of the interrupt controllers. The output of Timer 0 in the Counter/Timer subsystem is connected to Channel 0 (IR0) of INTC1. An Interrupt request from the Real Time Clock is connected to Channel 0 (IR0) of INTC2. Table 4-1 lists the 16 interrupt channels and their interrupt request sources.

The following description of the Interrupt Subsystem pertains to both INTC1 and INTC2 unless otherwise noted. Wherever register addresses are used, the address for the INTC1 register is listed first, and the address for the INTC2 register follows in parenthesis, e.g., 020H (0A0H).

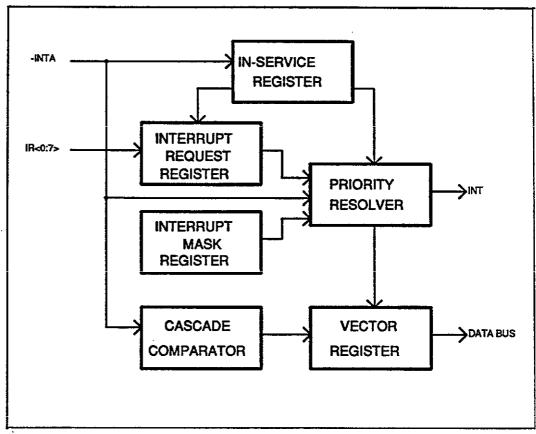

## 4.1 Controller Operation

Figure 4-2 shows a block diagram of the major elements in the interrupt controller:

The Interrupt Request Register (IRR) is used to store requests from all the channels that are requesting service. Interrupt Request Register bits are labeled using the Channel Name IR<0:7>.

- The In-Service register (ISR) contains all the channels that are currently being serviced (more than one channel can be in service at a time).

In-Service Register bits are labeled IS<0:7>.

- The Interrupt Mask Register (IMR) allows the CPU to disable any or all of the interrupt channels.

- The Priority Resolver evaluates inputs from the above three registers, issues an interrupt request, and latches the corresponding bit into the In-Service Register.

During interrupt acknowledge cycles, a master controller outputs a code to the slave device that is compared in the Cascade Buffer/Comparator with a three bit ID code previously written. If a match occurs in the slave controller, it generates an interrupt vector. The contents of the Vector Register are used to provide the CPU with an interrupt vector during Interrupt Acknowledge (INTA) cycles.

## 4.2 Interrupt Sequence

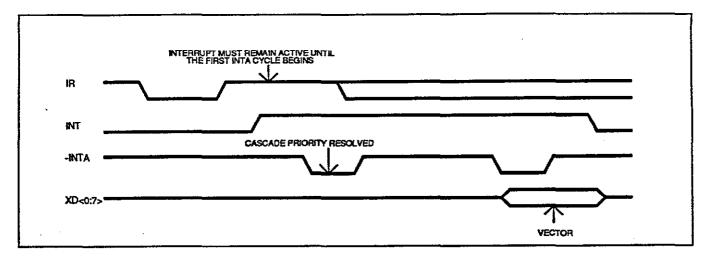

The 82C235 allows the CPU to perform an indirect jump to a service routine in response to a request for service from a peripheral device (see Figure 4-3). The indirect jump is based on a vector provided by the 82C235 on the second of two CPU generated INTA cycles (the first INTA cycle is used for resolving priority; the second cycle is used for transferring the vector to the CPU).

Figure 4-3. Interrupt Sequence

The events occurring during an interrupt sequence are as follows:

- 1. One or more of the interrupt requests (IR7-IR0) becomes active, setting the corresponding IRR bit(s).

- 2. The interrupt controller resolves priority based on the state of IRR, IMR, and ISR and asserts the INTR output if appropriate.

- 3. The CPU accepts the interrupt and responds with an INTA cycle.

- During the first INTA cycle, the highest priority ISR bit is set and the corresponding IRR bit is reset. The internal Cascade address is generated and LD<0:7> outputs remain tri-stated.

- 5. The CPU executes a second INTA cycle, during which the 82C235 drives an 8-bit vector onto the data pins LD<0:7>, which is in turn latched by the CPU. The format of this vector is shown in Table 4-2. Note that V<3:7> in the table are programmable by writing to Initialization Control Word 2 (see Section 4.5 Programming the Interrupt Controller and Figure 4-4).

Table 4-2. Format of Interrupt Vector