## Microcontrollers

**Edition 2001-03**

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2001.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# 82C900

## Standalone TwinCAN Controller

## Microcontrollers

Never stop thinking.

| 82C900<br>Prelimin<br>Revisior | ary<br>n History: | 2001-03                             | V 1.0D3 |

|--------------------------------|-------------------|-------------------------------------|---------|

| Previous                       | Version:          | -                                   |         |

| Page                           | Subjects          | (major changes since last revision) |         |

|                                |                   |                                     |         |

#### **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

#### Standalone TwinCAN Controller

82C900

#### 82C900

#### **Architectural Overview**

The Standalone TwinCAN device provides several submodules to control the data flow and to configure the peripheral function:

#### Features:

- Two interface channels are implemented for the communication with a host device:

- the Multiplexed Data/Address Bus can be used by an external CPU to read and write the TwinCAN's internal registers for initial configuration and control during normal operation. The standard Infineon Bus Mode and the Motorola Bus Mode can be handled.

- alternatively, a Synchronous Serial Channel (SSC) may be selected to read out the initial TwinCAN's register configuration from a serial EEPROM. The SSC can be also used by an external control device (microcontroller, CPU, etc.) in order to exchange control and status information.

- Both communication channels are based on byte transfers. In order to minimize the communication overhead, all internal 16 bit and 32 bit wide registers can be accessed in Page Mode requiring only one address byte.

- Powerful initialization mechanism for all registers, the device can be configured via EEPROM, based on CAN messages or by an external host device.

- Additional input/output functionality controlled by CAN messages. The transmission of CAN messages can be triggered by input pins if the SSC is used for communication.

- The clock control unit can be supplied with an external clock. Alternatively, an on-chip oscillator may be used to generate a clock driving also an external device via an output pin.

- Power Saving features have been implemented. A Sleep Mode and a Power-Down Mode can be activated in order to minimize the power consumption. The clock control of the device can be controlled by CAN messages.

- The internal power saving status can be monitored at output pins. This allows flexible and powerful system partitioning.

- The Device Controller unit generates the internal target address by concatenating the contents of the PAGE register with the address delivered by the appropriate host read/ write access.

- The Interrupt Control unit passes the interrupt requests generated by the TwinCAN controller to the external host via selectable output pins.

- The Port Control unit can be used to select the required functionality of the port pins operating as communication channel, CAN node function monitor, interrupt request line or general purpose I/O. Furthermore, the slew rate of pins configured for output operation can be adjusted via this module.

Data Sheet 5 V 1.0D3, 2001-03

The TwinCAN module permits the connection and autonomous handling of two independent CAN buses.

- Full-CAN module with 32 message objects, which can be independently assigned to one of the two buses.

- The CAN protocol version 2.0B active with standard and extended identifiers can be handled.

- The full CAN baud rate range is supported.

- Scalable FIFO mechanism for reception and transmission in order to improve the realtime behavior of the system.

- Built-in automatic gateway functionality for data exchange between both CAN buses.

The gateway feature can also be used for automatic reply to received messages (lifesign: "I got it!").

- Powerful interrupt structure, permitting application-specific interrupt generation.

- · Remote frames can be monitored.

- Enhanced acceptance filtering (an acceptance mask for each message object).

- A 16 bit frame count / timestamp is implemented for each message object.

- Analyzing mode (no dominant level will be sent) supported.

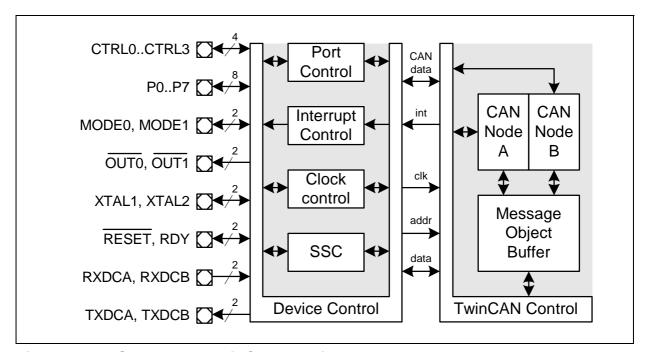

**Figure 1** shows a block diagram of the 82C900 device architecture.

Figure 1 Standalone TwinCAN Architecture

Note: The CAN bus transceivers are not integrated and have to be connected externally.

Data Sheet 6 V 1.0D3, 2001-03

#### **Application Fields**

The Standalone TwinCAN device 82C900 can be used in application requiring one or two independent CAN nodes. The built-in FIFO and gateway features minimize the CPU load for the message handling and lead to an improved real-time behavior. The access to the internal registers can be handled via a parallel or a serial interface, adapted to a large variety of applications. The interface selection is done via the two MODE pins, which can be directly connected to the supply voltage or via pull-up/down resistors (of about 10-47 kOhm). In all modes, the clock generation can be controlled either by the 82C900 device or by the system it is connected to.

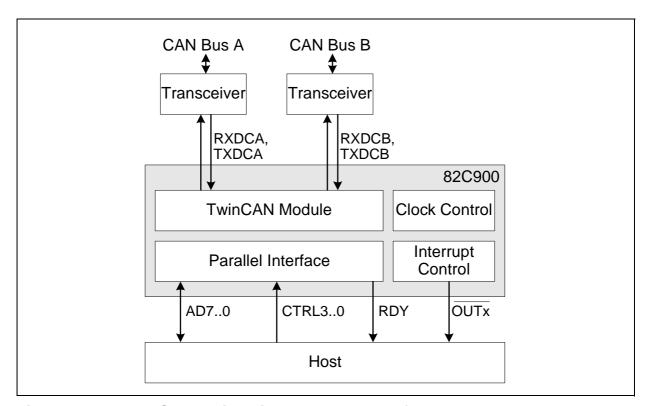

#### Connection to a Host Device via the Parallel Interface

The 82C900 can be connected to a host device via a parallel 8 bit multiplexed interface. Therefore, pin MODE0 has to be 0, whereas pin MODE1 selects, whether an Infineon-(Intel-) compatible or an Motorola-compatible protocol is handled. In this mode, the device can be easily used to extend the CAN capability of a system. The internal registers can be accessed in pages of 256 bytes per page. An additional RDY output indicates when the device is ready to be accessed. This signal can be used to detect an overload situation of the CAN device (too many host accesses to the TwinCAN module). One interrupt output line (OUT1) is always available, a second one (OUT0) can be used as clockout pin or as another interrupt output.

Figure 2 Host Connection via the Parallel Interface

Data Sheet 7 V 1.0D3, 2001-03

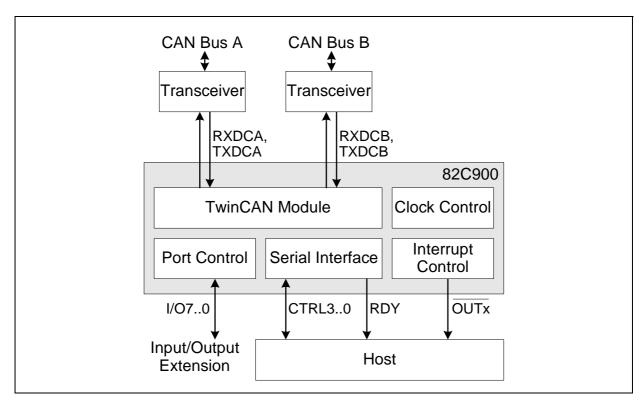

#### Connection to a Host Device via the Serial Interface

The second possibility to connect the 82C900 to a host device is via the serial interface. This mode is selected if the pin MODE0=1 and MODE1=0.

The standard four-line SPI-compatible interface has been extended by a RDY signal, which indicates that the serial interface is ready for the next access by the host.

The page size is reduced to 128 bytes per page, because the MSB of the address byte contains a read/write indication. A special incremental access mode has been implemented in order to reduce significantly the number of transferred bytes for consecutive register accesses.

The 8 remaining I/O pins from the unused parallel interface are controlled by a port control logic and can be used as I/O extension. These lines can be read or written by the serial channel or by CAN messages. Furthermore, these lines can be programmed as additional interrupt output lines in order to increase the number of independent interrupts.

The output lines OUT0 and OUT1 have the same functionality in the case a parallel interface or a serial interface connects the 82C900 to a host device.

Figure 3 Host Connection via the Serial Interface

Data Sheet 8 V 1.0D3, 2001-03

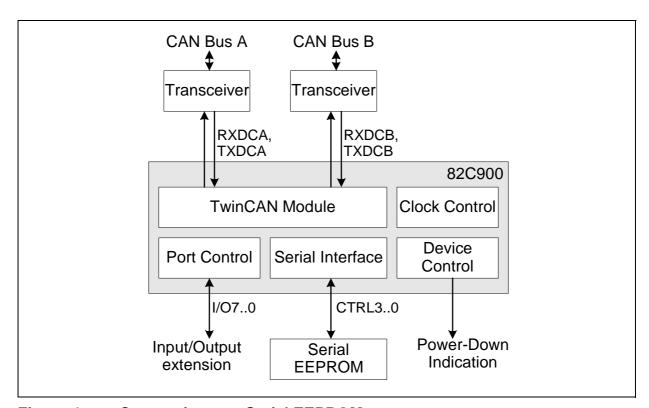

#### **Operation without Host Device**

The standalone functionality comprises an additional mode, leading to a low-cost system, which does not require any external host device. This mode can be selected by setting the input pins MODE0 and MODE1 to 1. The best solution are pull-up resistors (about 10 to 47 kOhm). After the reset phase, the MODE pins can be enabled to control the power-down functionality of the entire connected system by indicating the internal status of two clock control bits. The power-down functionality can run completely via CAN messages (sleep and wake-up by CAN messages).

The initialization sequence is automatically started from an external non-volatile memory, a serial (SPI-compatible) EEPROM. The data, which is read out from the EEPROM permits the user to initialize the registers with the desired values in a freely programmable order. Changes in the application only lead to modified data stored in the non-volatile memory.

For example, the bit timing, one message object and some control registers are set up via the data read from the EEPROM. Then, the initialization can continue via CAN messages.

The 8 remaining I/O pins from the unused parallel interface are controlled by a port control logic and can be used as I/O extension. These lines can be read or written by CAN messages.

Figure 4 Connection to a Serial EEPROM

Data Sheet 9 V 1.0D3, 2001-03

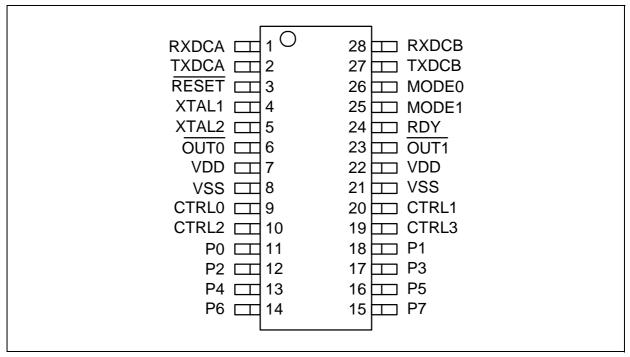

#### **Pin Configuration**

Figure 5 82C900 Pin Configuration

#### **Pin Definition**

Table 1 Pin Definitions and Functions

| Symbol | Pin<br>Number | I/O <sup>1)</sup> | Function                                                                                                                                                                            |

|--------|---------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXDCA  | 1             | I                 | Receiver Input of CAN Node A Receiver input of CAN node A, connected to the associated CAN bus via a transceiver device.                                                            |

| TXDCA  | 2             | 0                 | Transmitter Output of CAN Node A  TXDCA delivers the output signal of CAN node A. The signal level has to be adapted to the physical layer of the CAN bus via a transceiver device. |

| RXDCB  | 28            | I                 | Receiver Input of CAN Node B Receiver input of CAN node B, connected to the associated CAN bus via a transceiver device.                                                            |

Data Sheet 10 V 1.0D3, 2001-03

**Table 1 Pin Definitions and Functions** (cont'd)

| Symbol | Pin<br>Number | I/O <sup>1)</sup> | Function                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|--------|---------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TXDCB  | 27            | 0                 | Transmitter Output of CAN Node B  TXDCB delivers the output signal of CAN node B. The signal level has to be adapted to the physical layer of the CAN bus via a transceiver device.                                                                                                               |  |  |  |  |  |

| RESET  | 3             | I                 | Reset A low level on this pin resets the device.                                                                                                                                                                                                                                                  |  |  |  |  |  |

| RDY    | 24            | 0                 | Ready Signal Output signal indicating that the standalone device is ready for data transfer.                                                                                                                                                                                                      |  |  |  |  |  |

| CTRL0  | 9             | I/O               | Control 0  MODE0=0: Chip Select CS Input used as Chip Select for the device.  MODE0=1: Select Slave SLS  MODE1=0: Input used to enable SSC action when active.  MODE1=1: Output used to select a slave when active.                                                                               |  |  |  |  |  |

| CTRL1  | 20            | I/O               | Control 1  MODE0=0: Address Latch Enable or Address Strobe, ALE or AS  Input used for latching the address from the multiplexed address/data bus.  MODE0=1: Serial Channel Clock SCLK  Input/output of the SSC clock.  MODE1=0: Clock input MODE1=1: Clock output                                 |  |  |  |  |  |

| CTRL2  | 10            | I/O               | Control 2  MODE0=0: Write or Read/Write, WR or R/W  MODE1=0: Input used as write signal WR  MODE1=1: R/W=0: Data transfer direction = write  MODE1=1: R/W=1: Data transfer direction = read  MODE0=1: Master Transmit Slave Receive MTSR  MODE1=0: Serial data input  MODE1=1: Serial data output |  |  |  |  |  |

Table 1

Pin Definitions and Functions (cont'd)

| Symbol                                 | Pin<br>Number                                | I/O <sup>1)</sup>     | Function                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|----------------------------------------|----------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CTRL3                                  | 19                                           | I/O                   | Control 3  MODE0=0: Read or Read/Write Enable, RD or E  MODE1=0: Input used as read signal RD  MODE1=0: Read/write enable  MODE0=1: Master Receive Slave Transmit MRST  MODE1=0: Serial data output  MODE1=1: Serial data input                                                                                                                             |  |  |  |  |

| P7<br>P6<br>P5<br>P4<br>P3<br>P2<br>P1 | 15<br>14<br>16<br>13<br>17<br>12<br>18<br>11 | I/O                   | Parallel Bus MODE0=0: 8-bit Address/ Data Bus AD[7:0] Address and data bus AD7AD0 in 8-bit multiplexed modes. MODE0=1: 8-bit parallel I/O Port IO[7:0] Programmable 8-bit general purpose I/O-port IO7IO0.                                                                                                                                                  |  |  |  |  |

| OUT0 <sup>2)</sup>                     | 6                                            | 0                     | Output Line 0  The logic 0 level at this pin indicates an interrupt request to the external host device if selected as interrupt output. The interrupt line will be active if there is a new pending interrupt request for interrupt node 0 (according to register GLOBCTR).  If selected as clock output, the functionality is defined by register CLKCTR. |  |  |  |  |

| OUT1                                   | 23                                           | O,<br>open<br>drain   | Output Line 1 The logic 0 level at this pin indicates an interrupt request to the external host device. The interrupt line will be active if there is a new pending interrupt request for interrupt node 1 (according to register GLOBCTR).                                                                                                                 |  |  |  |  |

| MODE0 3)                               | 26                                           | I/O,<br>open<br>drain | Interface Selection Pin MODE0 selects whether the on-chip SSC or an 8                                                                                                                                                                                                                                                                                       |  |  |  |  |

Table 1

Pin Definitions and Functions (cont'd)

| Symbol              | Pin<br>Number | I/O <sup>1)</sup>     | Function                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|---------------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MODE1               | 25            | I/O,<br>open<br>drain | Interface Mode Selection Pin MODE1 determines the access mode of the host device.  MODE0=0: 8-bit multiplexed bus                                                                                                                                                                                                                                   |  |  |  |

| XTAL1               | 4             | I                     | Input of the inverting oscillator amplifier and input to the internal clock generation circuit.  When the 82C900 device is provided with an external clock, XTAL1 should be driven while XTAL2 is left unconnected.  Minimum and maximum high and low pulse width as well as rise/fall times specified in the AC characteristics must be respected. |  |  |  |

| XTAL2               | 5             | 0                     | XTAL2 Output of the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                 |  |  |  |

| $\overline{V_{SS}}$ | 21, 8         | 0V                    | Ground, both pins must be connected.                                                                                                                                                                                                                                                                                                                |  |  |  |

| $\overline{V_{DD}}$ | 22, 7         | +5V                   | Power Supply, both pins must be connected.                                                                                                                                                                                                                                                                                                          |  |  |  |

<sup>1)</sup> The slew rate of the output pins OUT0, OUT1, CTRL1..3, P0..P7, TXDCA and TXDCB can be defined by the bit fields SLR0..3 in register GLOBCTR.

Data Sheet 13 V 1.0D3, 2001-03

<sup>&</sup>lt;sup>2)</sup> After reset, this pin is configured as clock output, see register CLKCTR.

<sup>3)</sup> The initial logic state on pins MODE0 and MODE1 is registered with the rising edge of the RESET input. Afterwards, both pins can be used as additional I/O lines, according to functionality specified in register IOMODE4.

## **Register Address Map**

All Shell and Kernel registers, implemented for controlling the 82C900 device, are summarized in **Table 0-1**; detailed information about each register is provided in the respective module description chapter.

Note: Accesses to addresses which are not specified as registers in the following register address map are forbidden.

Table 0-1 Summary of Registers

| Register Name                                  | Register<br>Symbol | Address           | Reset Value            |

|------------------------------------------------|--------------------|-------------------|------------------------|

| Standalone Shell Registers                     |                    | +                 | <u> </u>               |

| Global Device Control Register                 | GLOBCTR            | 0010 <sub>H</sub> | A0 00 <sub>H</sub>     |

| Interrupt Control Register                     | INTCTR             | 0012 <sub>H</sub> | 00 00 <sub>H</sub>     |

| CAN Clock Control Register                     | CLKCTR             | 0014 <sub>H</sub> | 00 24 <sub>H</sub>     |

| Input/Output Mode Register 0                   | IOMODE0            | 0020 <sub>H</sub> | 00 00 <sub>H</sub>     |

| Input/Output Mode Register 2                   | IOMODE2            | 0022 <sub>H</sub> | 00 00 <sub>H</sub>     |

| Input/Output Mode Register 4                   | IOMODE4            | 0024 <sub>H</sub> | 00 00 <sub>H</sub>     |

| Input Value Register (8-bit port)              | INREG              | 0026 <sub>H</sub> | 00 00 <sub>H</sub>     |

| Output Value Register (8-bit port)             | OUTREG             | 0028 <sub>H</sub> | 00 00 <sub>H</sub>     |

| CAN Power-Down Control Register                | CANPWD             | 0040 <sub>H</sub> | 00 00 <sub>H</sub>     |

| CAN Input/Output Control Register              | CANIO              | 0042 <sub>H</sub> | 00 00 <sub>H</sub>     |

| CAN Initialization Control Register            | CANINIT            | 0044 <sub>H</sub> | 00 00 <sub>H</sub>     |

| Paging Mode Register (accessible in all pages) | PAGE               | XX7C <sub>H</sub> | 00 00 <sub>H</sub>     |

| CAN RAM Address Buffer Register                | CAB                | 007E <sub>H</sub> | 00 00 <sub>H</sub>     |

| Initialization Control Register                | INITCTR            | 02F0 <sub>H</sub> | 0103 0000 <sub>H</sub> |

| TwinCAN Kernel, Common Registers               |                    |                   |                        |

| CAN Receive Interrupt Pending Register         | RXIPND             | 0284 <sub>H</sub> | 0000 0000 <sub>H</sub> |

| CAN Transmit Interrupt Pending Register        | TXIPND             | 0288 <sub>H</sub> | 0000 0000 <sub>H</sub> |

| TwinCAN Kernel, Node A Registers               |                    |                   |                        |

| CAN Node A Control Register                    | ACR                | 0200 <sub>H</sub> | 0000 0001 <sub>H</sub> |

| CAN Node A Status Register                     | ASR                | 0204 <sub>H</sub> | 0000 0000 <sub>H</sub> |

| CAN Node A Interrupt Pending Register          | AIR                | 0208 <sub>H</sub> | 0000 0000 <sub>H</sub> |

| CAN Node A Bit Timing Register                 | ABTR               | 020C <sub>H</sub> | 0000 0000 <sub>H</sub> |

Data Sheet 14 V 1.0D3, 2001-03

Table 0-1 Summary of Registers (cont'd)

| Register Name                                          | Register<br>Symbol | Address                                  | Reset Value            |

|--------------------------------------------------------|--------------------|------------------------------------------|------------------------|

| CAN Node A Global Int. Node Pointer Reg.               | AGINP              | 0210 <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node A Frame Counter Register                      | AFCR               | 0214 <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node A INTID Mask Register 0                       | AIMR0              | 0218 <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node A INTID Mask Register 4                       | AIMR4              | 021C <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node A Error Counter Register                      | AECNT              | 0220 <sub>H</sub>                        | 0060 0000 <sub>H</sub> |

| TwinCAN Kernel, Node B Registers                       |                    |                                          | 1                      |

| CAN Node B Control Register                            | BCR                | 0240 <sub>H</sub>                        | 0000 0001 <sub>H</sub> |

| CAN Node B Status Register                             | BSR                | 0244 <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node B Interrupt Pending Register                  | BIR                | 0248 <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node B Bit Timing Register                         | BBTR               | 024C <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node B Global Int. Node Pointer Reg.               | BGINP              | 0250 <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node B Frame Counter Register                      | BFCR               | 0254 <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node B INTID Mask Register 0                       | BIMR0              | 0258 <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node B INTID Mask Register 4                       | BIMR4              | 025C <sub>H</sub>                        | 0000 0000 <sub>H</sub> |

| CAN Node B Error Counter Register                      | BECNT              | 0260 <sub>H</sub>                        | 0060 0000 <sub>H</sub> |

| TwinCAN Kernel, Message Object Registe                 | ers                |                                          |                        |

| CAN Message Object n Data Register 0                   | MSGDRn0            | 0300 <sub>H</sub><br>+ n*20 <sub>H</sub> | 0000 0000 <sub>H</sub> |

| CAN Message Object n Data Register 4                   | MSGDRn4            | 0304 <sub>H</sub><br>+ n*20 <sub>H</sub> | 0000 0000 <sub>H</sub> |

| CAN Message Object n Arbitration Register              | MSGARn             | 0308 <sub>H</sub><br>+ n*20 <sub>H</sub> | 0000 0000 <sub>H</sub> |

| CAN Message Object n Acceptance Mask<br>Register       | MSGAMRn            | 030C <sub>H</sub><br>+ n*20 <sub>H</sub> | FFFF FFFF <sub>H</sub> |

| CAN Message Object n Message Control<br>Register       | MSGCTRn            | 0310 <sub>H</sub><br>+ n*20 <sub>H</sub> | 0000 5555 <sub>H</sub> |

| CAN Message Object n Message<br>Configuration Register | MSGCFGn            | 0314 <sub>H</sub><br>+ n*20 <sub>H</sub> | 0000 0000 <sub>H</sub> |

| CAN Message Object n Gateway / FIFO Control Register   | MSGFGCRn           | 0318 <sub>H</sub><br>+ n*20 <sub>H</sub> | 0000 0000 <sub>H</sub> |

<sup>1)</sup> Registers with 32-bit reset values are located in the CAN RAM and have to be accessed accordingly. The other registers are standard SFRs, which have 16-bit reset values.

Data Sheet 15 V 1.0D3, 2001-03

## **Absolute Maximum Ratings**

Table 2

Absolute Maximum Rating Parameters

| Parameter                                                            | Symbol     | Limit Values |                      | Unit | Notes |

|----------------------------------------------------------------------|------------|--------------|----------------------|------|-------|

|                                                                      |            | min.         | max.                 |      |       |

| Storage temperature                                                  | $T_{ST}$   | -65          | 150                  | °C   |       |

| Voltage on $V_{\rm DD}$ pins with respect to ground ( $V_{\rm SS}$ ) | $V_{DD}$   | -0.5         | 6.5                  | V    |       |

| Voltage on any pin with respect to ground $(V_{SS})$                 | $V_{IN}$   | -0.5         | V <sub>DD</sub> +0.5 | V    |       |

| Input current on any pin during overload condition                   |            | -10          | 10                   | mA   |       |

| Absolute sum of all input currents during overload condition         |            |              | [100]                | mA   |       |

| Power dissipation                                                    | $P_{DISS}$ |              | 480                  | mW   |       |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions  $(V_{IN} > V_{DD})$  or  $V_{IN} < V_{SS}$  the voltage on  $V_{DD}$  pins with respect to ground  $(V_{SS})$  must not exceed the values defined by the absolute maximum ratings.

Data Sheet 16 V 1.0D3, 2001-03

#### **Operating Conditions**

The following operating conditions must not be exceeded in order to ensure correct operation of the device. All parameters, specified in the following sections, refer to the normal operating conditions, unless otherwise noticed. The timings refer to the fast edge mode.

**Table 3** Operating Condition Parameters

| Parameter                         | Symbol                   | Limit Values      |      | Unit | Notes                                          |

|-----------------------------------|--------------------------|-------------------|------|------|------------------------------------------------|

|                                   |                          | min.              | max. |      |                                                |

| Standard digital supply voltage   | $V_{DD}$                 | 4.5               | 5.5  | V    | Active mode, $f_{\text{max}} = 25 \text{ MHz}$ |

|                                   |                          | 2.5 <sup>1)</sup> | 5.5  | V    | Power-Down mode                                |

| Digital ground voltage            | $V_{SS}$                 | 0                 |      | V    | Reference voltage                              |

| Overload current                  | $I_{OV}$                 | -                 | ±5   | mA   | Per pin <sup>2) 3)</sup>                       |

| Absolute sum of overload currents | $\Sigma  I_{\text{OV}} $ | -                 | 50   | mA   | 4)                                             |

| External Load Capacitance         | $C_{L}$                  | -                 | 100  | pF   |                                                |

| Ambient temperature               | $T_{A}$                  | -40               | 125  | °C   | SAK 82C900                                     |

Output voltages and output currents will be reduced when  $V_{\rm DD}$  leaves the range defined for active mode. The clock frequency has to be reduced to operate with a voltage supply below 4.5V.

Data Sheet 17 V 1.0D3, 2001-03

Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range (i.e.  $V_{\text{OV}} > V_{\text{DD}} + 0.5 \text{V}$  or  $V_{\text{OV}} < V_{\text{SS}} - 0.5 \text{V}$ ). The absolute sum of input overload currents on all port pins may not exceed **50 mA**. The supply voltage must remain within the specified limits.

<sup>3)</sup> Not 100% tested, guaranteed by design characterization

<sup>4)</sup> Not 100% tested, guaranteed by design characterization.

#### **DC Characteristics**

Operating Conditions apply.

Table 4 DC Characteristics under Normal Operation Conditions

| Parameter                                              | Symbol               | Limit Va                     | lues                         | Unit | <b>Test Condition</b>                           |  |

|--------------------------------------------------------|----------------------|------------------------------|------------------------------|------|-------------------------------------------------|--|

|                                                        |                      | min.                         | max.                         | -    |                                                 |  |

| Input low voltage (XTAL1)                              | $V_{IL}$             | - 0.5                        | 0.3 V <sub>DD</sub>          | V    | -                                               |  |

| Input high voltage (XTAL1)                             | $V_{IH}$             | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | _                                               |  |

| Input low voltage (other pins)                         | $V_{IL}$             | - 0.5                        | 0.2 V <sub>DD</sub><br>- 0.1 | V    | _                                               |  |

| Input high voltage (other pins)                        | $V_{IH}$             | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> + 0.5        | V    | _                                               |  |

| Output low voltage <sup>1)</sup> (P0P7)                | $V_{OLP}$            | _                            | 0.45                         | V    | $I_{\text{OLP}} = 5 \text{ mA}$                 |  |

| Output high voltage 1)                                 | $V_{OHP}$            | 2.4                          | _                            | V    | $I_{\text{OHP}}$ = -5 mA                        |  |

| (P0P7)                                                 |                      | 0.9 V <sub>DD</sub>          | _                            | V    | $I_{\rm OHP}$ = -0.5 mA                         |  |

| Output low voltage (other pins)                        | $V_{OL}$             | _                            | 0.45                         | V    | $I_{\rm OL}$ = 2.4 mA                           |  |

| Output high voltage <sup>2)</sup>                      | $V_{OH}$             | 2.4                          | _                            | V    | $I_{OH}$ = -2.4 mA                              |  |

| (other pins)                                           |                      | 0.9 V <sub>DD</sub>          | _                            | V    | $I_{OH} = -0.5 \text{ mA}$                      |  |

| Input leakage current                                  | I <sub>OZ</sub>      | _                            | ±500                         | nA   | $0.45 \text{V} < V_{\text{IN}} < V_{\text{DD}}$ |  |

| RESET inactive current 3)                              | I <sub>RSTH</sub> 4) | _                            | -10                          | μΑ   | $V_{IN} = V_{IH}$                               |  |

| RESET active current                                   | I <sub>RSTL</sub> 5) | -100                         | _                            | μΑ   | $V_{IN} = V_{IL}$                               |  |

| XTAL1 input current                                    | $I_{IL}$             | _                            | ±20                          | μΑ   | $0 \ V < V_{IN} < V_{DD}$                       |  |

| Pin capacitance <sup>6)</sup> (digital inputs/outputs) | $C_{IO}$             | _                            | 10                           | pF   | f = 1 MHz<br>$T_{\rm A}$ = 25 °C                |  |

<sup>1)</sup> The sum of  $|I_{OHP}|$ ,  $I_{OIP}$  must not exceed 20mA.

Data Sheet 18 V 1.0D3, 2001-03

<sup>&</sup>lt;sup>2)</sup> This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

These parameters describe the  $\overline{RESET}$  pull-up, which equals a resistance of ca. 50 to 250 K $\Omega$ .

<sup>4)</sup> The maximum current may be drawn while the respective signal line remains inactive.

<sup>&</sup>lt;sup>5)</sup> The minimum current must be drawn in order to drive the respective signal line active.

<sup>6)</sup> Not 100% tested, guaranteed by design characterization.

#### **Power Consumption**

Operating Conditions apply.

Table 5 Power Consumption

| Parameter                                                            | Symbol                          | Limit Values |      | Unit | <b>Test Condition</b>                                                            |

|----------------------------------------------------------------------|---------------------------------|--------------|------|------|----------------------------------------------------------------------------------|

|                                                                      |                                 | min.         | max. |      |                                                                                  |

| Power supply current (5V active) with all elements active            | $I_{DD5}$                       | _            | 80   | mA   | $\overline{\text{RESET}} = V_{\text{IH}}$ $f_{\text{CAN}} = 25 \text{ MHz}^{1)}$ |

| Sleep mode supply current (5V) (oscillator running, clock gated off) | I <sub>IDX5</sub> <sup>2)</sup> | _            | 1.5  | mA   | $\overline{RESET} = V_{IH} \\ f_{CAN} = 25 \; MHz$                               |

| Power-down mode supply current (5V) (oscillator stopped)             | $I_{IDO5}$                      | _            | 10   | μΑ   | RESET = V <sub>IH</sub>                                                          |

The supply current is a function of the operating frequency. These parameters are tested at  $V_{\rm DDmax}$  and maximum CPU clock with all outputs disconnected and all inputs at  $V_{\rm IL}$  or  $V_{\rm IH}$ .

The oscillator also contributes to the total supply current. The given values refer to the worst case. For lower oscillator frequencies the respective supply current can be reduced accordingly.

Data Sheet 19 V 1.0D3, 2001-03

<sup>&</sup>lt;sup>2)</sup> This parameter is determined mainly by the current consumed by the oscillator. This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The values given refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

#### **AC Characteristics**

Operating Conditions apply.

Table 6 External Clock Drive XTAL1

| Parameter            | Symbol           | Direct Drive (1:1) | Unit |    |

|----------------------|------------------|--------------------|------|----|

|                      |                  | min.               | max. |    |

| Oscillator period 1) | T <sub>CAN</sub> | 40                 | _    | ns |

| High time            |                  | 10                 | _    | ns |

| Low time             |                  | 15                 | _    | ns |

<sup>1)</sup> The clock input signal must reach the defined levels  $V_{\rm II}$  and  $V_{\rm IH}$ .

Assuming a maximum access rate from an external host to the CAN RAM via the communication interface (worst case, parallel interface), the CAN protocol can still be handled on both nodes with 1 Mbps if the clock frequency  $f_{CAN}$  is 24 MHz. For additional data handling features (FIFO, gateway, etc.), a higher frequency should be used, the access rate to the device has to be reduced or a lower baud rate has to be selected. Under worst case access conditions and CAN traffic, a baud rate of 500 kbps for each node can be achieved with full data handling functionality with  $f_{CAN}$ =24 MHz.

CAN input delay, output delay: typ. 15 ns

Data Sheet 20 V 1.0D3, 2001-03

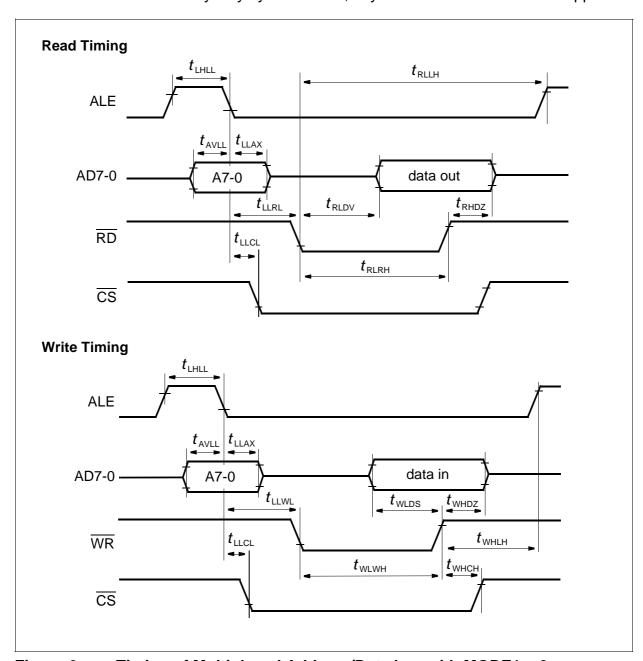

## 8-Bit Multiplexed Bus Infineon/ Intel Compatibility Mode

The bus access is internally fully synchronized, asynchronous accesses are supported.

Figure 6 Timing of Multiplexed Address/Data bus with MODE1 = 0

Data Sheet 21 V 1.0D3, 2001-03

Operating Conditions apply.

| Parameter                                                               | Symbol            | Limit Values            |                         | Unit |

|-------------------------------------------------------------------------|-------------------|-------------------------|-------------------------|------|

|                                                                         |                   | min.                    | max.                    | 1    |

| Address valid to ALE low                                                | t AVLL            | 5                       | _                       | ns   |

| Address hold after ALE low                                              | t <sub>LLAX</sub> | 10                      | _                       | ns   |

| ALE high time                                                           | t <sub>LHLL</sub> | 10                      | _                       | ns   |

| ALE low to RD low                                                       | t <sub>LLRL</sub> | 10                      | _                       | ns   |

| ALE low to WR low                                                       | t <sub>LLWL</sub> | 10                      | _                       | ns   |

| ALE low to CS low                                                       | t <sub>LLCL</sub> | 10                      | _                       | ns   |

| Data setup to WR high                                                   | t <sub>WLDS</sub> | 10                      | _                       | ns   |

| Input data hold after WR high                                           | t <sub>WHDZ</sub> | 10                      | _                       | ns   |

| WR pulse width                                                          | t <sub>WLWH</sub> | 1.5 T <sub>CAN</sub>    | _                       | ns   |

| WR high to next ALE high (if the next access targets the device)        | t <sub>WHLH</sub> | 10 T <sub>CAN</sub>     | _                       | ns   |

| WR high to next ALE high (if the next access doesn't target the device) | t <sub>WHLH</sub> | 4 T <sub>CAN</sub> +15  | _                       | ns   |

| WR high to CS high                                                      | t <sub>WHCH</sub> | 0                       | _                       | ns   |

| RD pulse width (short read)                                             | t <sub>RLRH</sub> | 1.5 T <sub>CAN</sub>    | _                       | ns   |

| RD pulse width (long read)                                              | t <sub>RLRH</sub> | 8 T <sub>CAN</sub> + 25 | _                       | ns   |

| RD low to data valid (short read)                                       | t <sub>RLDV</sub> | _                       | 25                      | ns   |

| RD low to data valid (long read)                                        | t <sub>RLDV</sub> | _                       | 25 + 8 T <sub>CAN</sub> | ns   |

| RD low to next ALE high (short read)                                    | t <sub>RLLH</sub> | 8 T <sub>CAN</sub>      | _                       | ns   |

| RD low to next ALE high (long read)                                     | t <sub>RLLH</sub> | 25                      | _                       | ns   |

| Data float after RD high                                                | t <sub>RHDZ</sub> | _                       | 25                      | ns   |

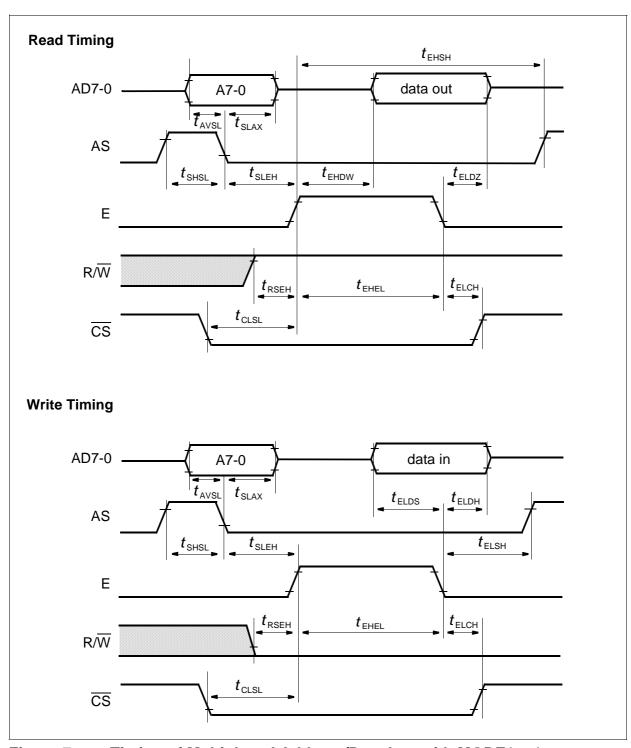

## 8-Bit Multiplexed Bus Motorola Compatibility Mode

The bus access is internally fully synchronized, asynchronous accesses are supported.

Figure 7 Timing of Multiplexed Address/Data bus with MODE1 = 1

Data Sheet 23 V 1.0D3, 2001-03

Operating Conditions apply.

| Parameter                                                                        | Symbol            | Limit Values            |      | Unit |

|----------------------------------------------------------------------------------|-------------------|-------------------------|------|------|

|                                                                                  |                   | min.                    | max. |      |

| Address valid to AS low                                                          | t AVSL            | 5                       | _    | ns   |

| Address hold after AS low                                                        | t <sub>SLAX</sub> | 10                      | _    | ns   |

| Data float after E low                                                           | t <sub>ELDZ</sub> | _                       | 25   | ns   |

| E high to data valid output                                                      | t <sub>EHDV</sub> | _                       | 25   | ns   |

| Input data setup to E low                                                        | t <sub>ELDS</sub> | 10                      | _    | ns   |

| Input data hold after E low                                                      | t <sub>ELDH</sub> | 10                      | _    | ns   |

| E high time                                                                      | t <sub>EHEL</sub> | 1.5 T <sub>CAN</sub>    | _    | ns   |

| AS high time                                                                     | t <sub>SHSL</sub> | 10                      | _    | ns   |

| Setup time of R/W to E high                                                      | t <sub>RSEH</sub> | 0                       | _    | ns   |

| AS low to E high                                                                 | t <sub>SLEH</sub> | 10                      | _    | ns   |

| CS low to E high                                                                 | t <sub>CLSL</sub> | 0                       | _    | ns   |

| E low to CS high                                                                 | t <sub>ELCH</sub> | 0                       | _    | ns   |

| E low to next AS high (for write) (if the next access targets the device)        | t <sub>ELSH</sub> | 10 T <sub>CAN</sub>     | _    | ns   |

| E low to next AS high (for write) (if the next access doesn't target the device) | t <sub>ELSH</sub> | 4 T <sub>CAN</sub> + 15 | _    | ns   |

| E high to next AS high (for read)                                                | t <sub>EHSH</sub> | 8 T <sub>CAN</sub>      | _    | ns   |

#### Timings of the SSC

In the case that the SSC is used in slave mode without the RDY signal, the following timings have to be respected:

| Parameter                                                           | Min. Time<br>(access to<br>TwinCAN<br>registers) | Min. Time (access to standalone registers) | Units            |

|---------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------|------------------|

| First activation of SLS after end of reset                          | 1100                                             | 1100                                       | T <sub>CAN</sub> |

| SLS active after SLS inactive (to start a new communication cycle)  | 4                                                | 4                                          | T <sub>CAN</sub> |

| SLS active before SCLK active in order to transfer the address byte | 2                                                | 2                                          | T <sub>CAN</sub> |

| SLS inactive after SLS active without transfer of data              | 2                                                | 2                                          | T <sub>CAN</sub> |

| Time after the address transfer to the first data byte transfer     | 5 (write)<br>14 (read)                           | 5 (write)<br>11 (read)                     | T <sub>CAN</sub> |

| Time between two byte transfers (SCLK active to SCLK active)        | 5 (write)<br>14 (read)                           | 5 (write)<br>11 (read)                     | T <sub>CAN</sub> |

| Time to SLS inactive after last byte transfer                       | 11 (write)<br>1 (read)                           | 6 (write)<br>1 (read)                      | T <sub>CAN</sub> |

Note: The RDY signal can be used for a handshake to access to the device. Furthermore, this signal indicates SSC error conditions (see baud rate error detection). Accesses to the device during an SSC error condition can not be correctly taken into account and might lead to errors.

Data Sheet 25 V 1.0D3, 2001-03

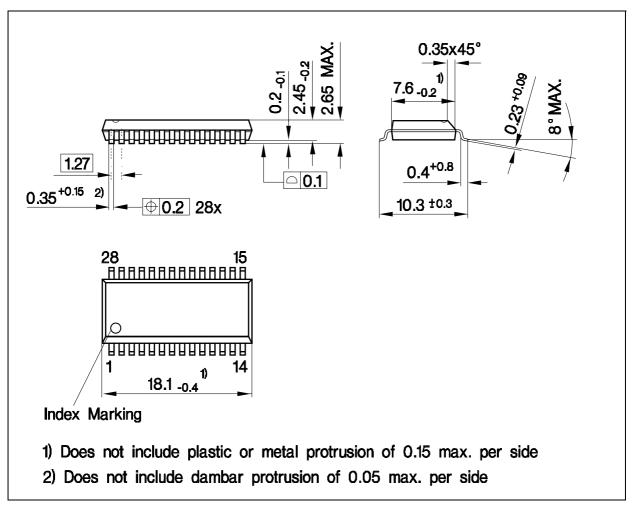

## **Package**

The 82C900 device is available in a 28-pin P-DSO package. **Table 1** contains a functional description of each pin.

Figure 8 P-DSO-28-1 Package

Data Sheet 26 V 1.0D3, 2001-03

## Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com