Fast Ethernet Transceiver

MARVELL

# FAST ETHERNET INFRASTRUCTURES

**WITH NEW 88E3080**

**OCTAL PHY TRANSCEIVER**

#### 88E3080 Star Performance

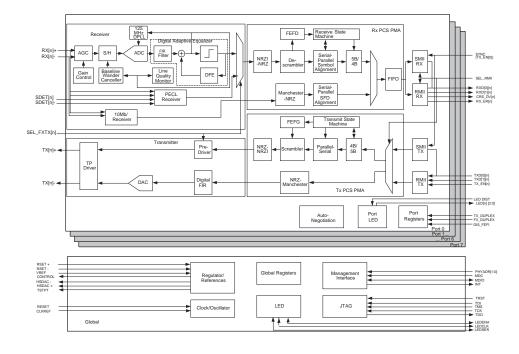

Marvell strengthens 100BASE-TX/FX and 10BASE-T Ethernet infrastructures by offering a highly integrated eight port Fast Ethernet Transceiver to the LAN market. The 88E3080 performs the physical layer functions to convert data streams to and from eight MACs and the IEEE 802.3 100BASE-TX/FX and 10BASE-T twisted pair cable in full or half duplex mode.

Marvell's 88E3080 transceiver is a low pin-count solution for customers connecting directly to Fast Ethernet MACs through either the RMII or SMII interfaces. It is fully IEEE 802.3 compliant and provides a seamless solution from Media Independent Interface (MII) to magnetics.

The 88E1000 applies Marvell's advanced mixed-signal DSP architectures and digital design technology to implement digital adaptive equalization, digital timing recovery, line driver support, encoders and decoders. An advanced high speed ADC is also incorporated on each receive channel.

The digital adaptive equalizer uses a combination of feedforward equalizer (FFE) and decision feedback equalizer (DFE) for the best optimized signal-to-noise (SNR) ratio. Marvell's equalizer is designed to achieve an error rate of less than 10E-12 at a distance of 150 meters.

The all-digital clock recovery and generator circuit used to create all the needed receive and transmit clocks makes the 88E3080 receiver path tolerant to the presence of variations in process, temperature, on-chip noise, and supply voltage.

Marvell's patented architectures and field proven design techniques result in high differential and integral linearity, high power supply noise rejection, and lower error rates.

The 88E3080 leverages technology developed through four generations of PRML read channels designed for the data storage market. The 88E3080 is the ideal solution for networking systems where outstanding performance and low power dissipation are vital.

#### The Marvell Advantage

As with all Marvell products, the 88E3080 comes with a complete set of hardware and software tools to assist network hardware engineers with product evaluation. Marvell's worldwide field applications engineers collaborate closely with network equipment vendors to develop and deliver new competitive products to market on time.

Marvell utilizes recognized world-leading semiconductor foundry and packaging services to reliably deliver high volume and low-cost solutions.

www marvell com

Copyright 2000 Marvell Technology Group, Ltd. All rights reserved. Marvell and the Marvell logo are trademarks of Marvell Tehnology Goup, Ltd. Marvell reserves the right to make changes to specifications and product descriptions at any time without notice.

For more information, visit www.marvell.com or contact one of our regional sales offices:

#### Marvell USA

645 Alamanor Avenue Sunnyvale, CA 94086 p 408.222.2500 f 408.328.0120

# Marvell Asia Pte, Ltd.

Block 20, Woodlands Link, #08-38 Woodlands East Industrial Estate Singpore 738733 p 65.756.1600 f 65.756.7600

# Marvell Japan

AsahiSeimei Fuchu Bldg. 12F 1-14-1 Fuchu-cho, Fuchu-shi Tokyo 183-0055 p 011.042.369.0487 f 011.042.369.6201

# 88E3080

### Fast Ethernet Transceiver

#### Features

- Eight independent IEEE 802.3 compliant 100BASE-TX and 10BASE-T ports

- Eight independent IEEE 802.3 compliant

- 100BASE-FX ports for fiber optics apps

- RMII and SMII interfaces compatible

- Programmable interrupt to minimize polling

Automatic polarity correction

- IEEE 802.3u Auto-Negotiation with next page support for auto speed and duplex selection

- IEEE 1149.1 (JTAG) boundary scan support

- Flexible serial and direct drive LED support

- Advanced mixed-signal and DSP techniques

Advanced high speed, high resolution ADC

- Digital adaptive equalizers

- Advanced baseline wander correction

- On-chip transmit wave-shaping to reduce EMI

- \* All digital clock recovery and generator circuit

- \*0.25micron standard digital CMOS process

- Low power dissipation ~300mW per port

- 3.3V single supply with built-in internal regulator

- Standard 208-pin PQFP package

# Benefits

- True plug-and-play for Fast Ethernet networks

- Makes existing Fast Ethernet infrastructures (lower cost cabling) more robust

- Seamless Ethernet solution from standard

- RMII and SMII interfaces to magnetics

- Reduced pin count support to high port

- count switches

- Increased reliability for board level testing and manufacturability

- Allows operation over all existing Category 5

- Provides robust performance over a wide range of operating conditions

- Efficient power consumption control

- Eliminates the need for fans and heat sinks

- Lowest power for long-term reliability

- Simplifies board level design

- Increased number of ports per rack to reduce backbone expenditures