# 8101/8104 Gigabit Ethernet Controller

# LSI LOGIC

Datasheet

The 8101/8104 Gigabit Ethernet Controller is a complete media access controller (MAC sublayer) with integrated coding logic for fiber and short haul copper media (8-bit/10-bit Physical Coding Sublayer) (8B/10B PCS) for 1000 Mbit/s Gigabit Ethernet systems.

The 8104 is functionally the same as the 8101 except that the 8104 is in a 208-pin Ball Grid Array (BGA) package and the 8101 is in a 208-pin Plastic Quad Flat Pack (PQFP) package.

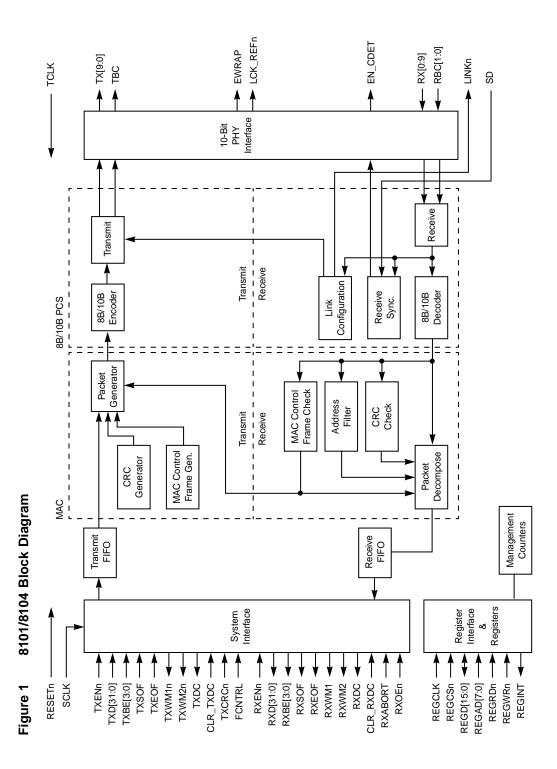

The Controller consists of a 32-bit system interface, receive/transmit First In First Out (FIFO) buffers, a full-duplex Ethernet Media Access Controller (MAC), an 8B/10B PCS, a 10-bit Physical Layer Device (PHY) interface, and a 16-bit register interface. The controller also contains all the necessary circuitry to implement the IEEE 802.3x Flow Control Algorithm. Flow control messages can be sent automatically without host intervention. Figure 1 is a block diagram of the controller.

The controller contains 53 counters which satisfy the management objectives of the Remote Monitoring (RMON) Statistics Group MIB, (RFC 1757), Simple Network Management Protocol (SNMP) Interfaces Group (RFC 1213 and 1573), Ethernet-like Group MIB (RFC 1643), and Ethernet MIB (IEEE 802.3z Clause 30). The controller also contains 136 internal 16-bit registers that can be accessed through the register interface. These registers contain configuration inputs, status outputs, and management counter results.

The 8101/8104 is ideal as an Ethernet controller for Gigabit Ethernet switch ports, uplinks, backbones, and adapter cards.

2

## Features

The 8101/8104 provides the following features.

- Combined Ethernet MAC and 8B/10B PCS

- 1000 Mbits/s data rate

- 64-bit, 66 MHz external bus interface (4 Gbits/s bandwidth)

- 10-bit interface to external SERDES chip

- 16-bit interface to internal registers and management counters

- Full RMON, SNMP, and Ethernet management counter support

- Independent receive and transmit FIFOs with programmable watermarks

- 16 Kbyte receive FIFO size

- 4 Kbyte Transmit FIFO size

- AutoNegotiation algorithm on chip

- Full duplex only

- Flow control per IEEE 802.3x

- Automatic CRC generation and checking

- Automatic packet error discarding

- Programmable transmit start threshold

- Interrupt capability

- Supports fiber and short haul copper media

- 3.3 V power supply, 5 V tolerant inputs

- Meets all applicable IEEE 802.3 and 802.3z specifications

## **Transmit Data Path**

Data is input to the system from an external bus. The data is then sent to the transmit FIFO. The transmit FIFO provides temporary storage of the data until it is sent to the MAC transmit section. The transmit MAC formats the data into an Ethernet packet according to IEEE 802.3 specification. The transmit MAC also generates MAC control frames and includes logic for AutoNegotiation. The Ethernet frame packet is then sent to the 8B/10B PCS.

The 8B/10B PCS encodes the data and adds appropriate framing delimiters to create 10-bit symbols as specified in IEEE 802.3. The 10-bit symbols are then sent to the 10-bit PHY interface for transmission to an external PHY device.

## **Receive Data Path**

The 10-bit PHY interface receives incoming encoded data from an external PHY device. The incoming encoded data must be encoded in the 10-bit PHY format specified in IEEE 802.3z. The incoming encoded data is then sent to the receive 8B/10B PCS, which strips off the framing delimiters, decodes the data, and converts the encoded data into an Ethernet packet according to the IEEE 802.3 specifications. The Ethernet packet data is then sent to the receive MAC section.

The receive MAC section disassembles the packet, checks the validity of the packet against certain error criteria and address filters, and checks for MAC control frames. The receive MAC then sends valid packets to the receive FIFO. The receive FIFO provides temporary storage of data until it is demanded by the system interface. The system interface outputs the data to an external bus.

## **Register Structure**

The controller has 136 internal 16-bit registers. Twenty-two registers are available for setting configuration inputs and reading status outputs. The remaining 114 registers are associated with the management counters.

The register interface is a separate internal register bidirectional 16-bit data bus to set configuration inputs, read status outputs, and access management counters.

## **Ethernet Frame Format**

Information in an Ethernet network is transmitted and received in packets or frames. The basic function of the controller is to process Ethernet frames. An Ethernet frame is defined in IEEE 802.3 and consists of a preamble, start of frame delimiter (SFD), destination address (DA), source address (SA), length/type field (L/T), data, frame check sequence (FCS), and interpacket gap (IPG).

An Ethernet frame is specified by IEEE 802.3 to have a minimum length of 64 bytes and a maximum length of 1518 bytes, exclusive of the preamble and SFD. Packets that are less than 64 bytes or greater than 1518 bytes are referred to as undersize and oversize packets, respectively.

## **System Interface**

The system interface is a 64-bit wide data interface consisting of separate 32-bit data buses for transmit and receive.

## Data Format and Bit Order

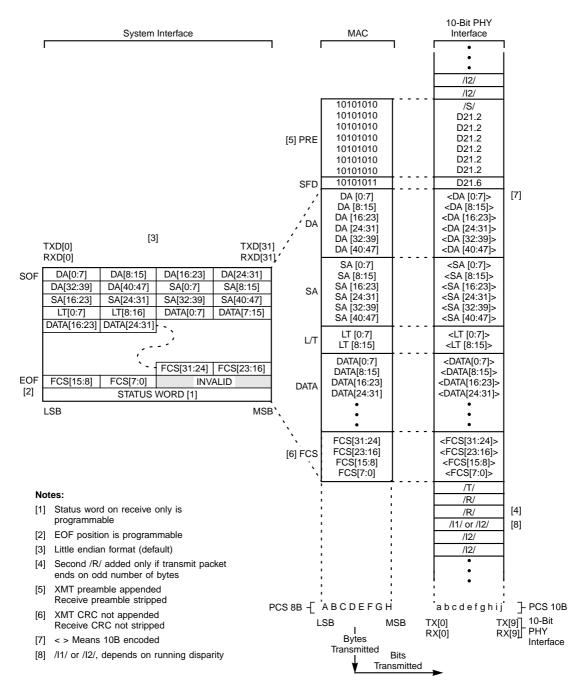

The format of the data word on TXD[31:0] and RXD[31:0] and its relationship to the MAC frame format and 10-bit PHY interface format is shown in Figure 2. Note that the controller can be programmed to append an additional 32-bit status word to the end of the receive packet.

## Figure 2 Frame Formats and Bit Ordering

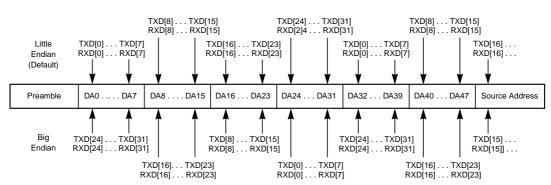

The byte order is little endian format mode (default). If the controller is placed in big endian format, the byte order shown in Figure 3 is reversed, DA[0:7] occurs on pins RXD[24:31], DA[24:31] occurs on pins RXD[0:7]and so on. The endian bit affects all bytes in the frame including the receive status word (if appended). The difference between little endian and big endian format is illustrated in Figure 3.

## Figure 3 Little Endian vs. Big Endian Format

## Transmit

The transmit portion of the system interface consists of 45 signals:

- 32 transmit data input bits (TXD[31:0])

- One transmit enable (TXENn)

- Four transmit byte enable inputs (TXBE[3:0])

- Two transmit start of frame and end of frame inputs (TXSOFn and TXEOFn)

- Two transmit FIFO watermark outputs (TXWM1n and TXWM2n)

- One transmit discard output (TXDC)

- One transmit discard clear input (CLR\_TXDC)

- One transmit CRC enable input (TXCRCn)

- One flow control enable input (FCNTRL)

All receive and transmit data is clocked in and out on the rising edge of the system clock, SCLK. SCLK must operate between 33–66 MHz.

## Receive

The receive portion of the system interface consists of 45 signals:

- 32 receive output data bits (RXD[31:0])

- One receive enable input (RXENn)

- Four receive byte enable outputs (RXBE[3:0])

- Two receive start of frame and end of frame outputs (RXSOF and RXEOF)

- Two receive FIFO watermark outputs (RXWM1 and RXWM2)

- One receive discard output (RXDC)

- One receive discard clear input (CLR\_RXDC)

- One receive packet abort input (RXABORT)

- One receive output enable (RXOEn)

All receive and transmit data is clocked in and out with the system clock, SCLK, which must operate between 33–66 MHz.

## **Transmit MAC**

To generate an Ethernet MAC frame from the transmit FIFO packet, the transmit MAC section:

- generates preamble and SFD

- pads undersize packets with zeros to meet minimum packet size requirements

- calculates and appends a CRC value to the packet

- maintains a minimum interpacket gap

Each of the above four operations can be individually disabled and altered if desired. The transmit MAC then sends the fully formed Ethernet packet to the 8B/10B PCS block for encoding. The transmit MAC section also generates MAC control frames.

## **Receive MAC**

The receive MAC section performs the following operations to disassemble Ethernet packets received from the receive 8B/10B PCS section:

- strips off the preamble and SFD

- strips off the CRC

- checks the destination address against the address filters to determine packet validity

- checks frame validity against the discard conditions

- checks the length/type field for MAC control frames

Each of the above operations can be individually disabled and altered, if desired. The receive MAC then sends valid packets to the receive FIFO for storage.

## **Transmit FIFO**

The transmit FIFO acts as a temporary buffer between the system interface and transmit MAC section. The transmit FIFO size is 4 Kbytes. Data is clocked into the transmit FIFO with the 33–66 MHz system interface clock, SCLK. Data is automatically clocked out of the transmit FIFO with the 125 MHz 8B/10B PCS clock whenever a full packet has been loaded into the FIFO (an EOF is written into the FIFO on the system interface), or the FIFO data exceeds the transmit FIFO AutoSend threshold. There are two programmable watermark outputs, TXWM1n and TXWM2n, which aid in managing the data flow into the transmit FIFO.

## **Receive FIFO**

The receive FIFO acts as a temporary buffer between the receive MAC section and system interface. The receive FIFO size is 16 kbytes. Data is clocked into the receive FIFO with the 125 MHz 8B/10B PCS clock. Data is clocked out of the receive FIFO with the 33–66 MHz system

interface clock, SCLK. There are two programmable watermark outputs, RXWM1 and RXWM2, which aid in managing the data flow out of the receive FIFO.

## 8B/10B PCS

The 8B/10B PCS encodes the data and adds approiate framing delimiters to create 10-bit symbols as specified in IEEE 802.3.

## Transmit

The transmit 8B/10B PCS section accepts Ethernet formatted packet data from the transmit MAC and:

- Encodes the data with the 8B/10B encoder

- Adds the start of packet delimiter

- Adds the end of packet delimiter

- Adds the idle code stream

- Formats the packet according to the 10-bit PHY format defined in IEEE 802.3z

The 8B/10B encoded data stream is then sent to the transmit 10-bit PHY interface for transmission.

The transmit 8B/10B PCS section also generates the AutoNegotation code stream when the controller is in the AutoNegotation process.

## Receive

The receive 8B/10B PCS section takes the 8B/10B encoded packet data from the incoming 10-bit PHY interface and:

- Acquires and maintains word synchronization

- Strips off the start of packet delimiter

- Strips off the end of packet delimiter

- Strips off the idle code stream

- Decodes the data with the 8B/10B decoder

- Converts the packet to the Ethernet packet format

The Ethernet packet is then sent to the receive MAC for processing.

The receive 8B/10B PCS section also decodes the AutoNegotation code stream when the controller is in the AutoNegotation process.

## 8B/10B Encoder

The 8B/10B encoder converts each data byte of a packet into a unique 10-bit word as defined in IEEE 802.3z

The encoder also converts the start of packet delimiter, end of packet delimiter, idle code streams, and AutoNegotation code streams into unique 10B code words. These unique 10B code words are referred to as ordered sets.

The 8B/10B encoder also keeps the running disparity of the outgoing 10B word as close as possible to zero. Running disparity is the difference between the number of ones and zeros transmitted on the outgoing bitstream. The algorithm for calculating running disparity is defined in IEEE 802.3z.

## **10-Bit PHY Interface**

The 10-bit PHY interface is a standardized interface between the 8B/10B PCS section and an external physical layer device. The 10-bit PHY interface meets all the requirements outlined in IEEE 802.3z. The controller can directly connect, without any external logic, to any physical layer device that also complies with the IEEE 802.3z 10-bit interface specifications.

The 10-bit PHY interface consists of 26 signals as follows:

- 10-bit transmit data output bits (TX[9:0])

- Transmit clock output (TBC)

- 10-bit receive data input bits (RX[9:0])

- Two receive clock inputs (RBC0 and RBC1)

- Comma detect enable output (EN\_CDET)

- Loopback output (EWRAP)

- Receiver lock output (LCK\_REFn)

## **Packet Discard**

The controller can be programmed to discard receive and transmit packets when certain error conditions are detected. The detection of these error conditions can occur in the MAC, FIFO, or 8B/10B PCS sections.

## **Transmit Discards**

Transmit packets are automatically discarded if certain error conditions are detected. These error conditions are described in Table 1. When a discard error is detected for a transmit packet, any remaining data for that packet being input from the system interface is ignored, a /V/ code is appended to the end of the packet to indicate an error to a remote station, and TXDC is asserted if the packet was being input from the system interface when the discard occurred.

| Discard Condition       | Description                                                                                                                                              |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit FIFO Underflow | TX FIFO empty. Packet transmission to 8B/10B PCS halted. Partially transmitted packet is terminated with a /V/ code, followed by normal /I/ codes.       |

| Transmit FIFO Overflow  | TX FIFO full. No more data accepted from the system interface. Partially transmitted packet is terminated with a /V/ code, followed by normal /I/ codes. |

## Table 1 Transmit Discard Conditions

## **Receive Discards**

Receive packets can be discarded if the error conditions listed in Table 2 are detected. The discard behavior is dependent on whether or not the packet is being output on the system interface when the discard condition is detected. If the packet containing the error is not being output on the system interface when the discard condition is detected (an internal discard) the packet is discarded, (all data from the packet containing the error is flushed from the receive FIFO). If the packet containing the error is being output on the system interface when the discard condition is detected (an external discard) the packet is automatically discarded. For both internal and external discarded packets, the appended status word is updated to reflect the discard error condition.

| Discard Condition     | Description                                                                        |

|-----------------------|------------------------------------------------------------------------------------|

| Receive FIFO overflow | Receive FIFO full. No more data accepted from the 8B/10B PCS.                      |

| CRC error             | Receive packet has a CRC error.                                                    |

| Undersize packet      | Receive packet is less than 64 bytes, exclusive of preamble and SFD.               |

| Oversize packet       | Receive packet is greater than maximum packet size, exclusive of preamble and SFD. |

| PCS codeword error    | Receive packet contains at least one word with an 8B/10BPCS coding error.          |

Table 2

Receive Discard Conditions

## Counters

The controller has a set of 53 management counters. Each counter tabulates the number of times a specific event occurs. These counters provide the necessary statistics to completely support the following specifications:

- RMON Statistics Group (IETF RFC 1757)

- SNMP Interfaces Group (IETF RFC 1213 and 1573)

- Ethernet-Like MIB (IETF RFC 1643)

- Ethernet MIB (IEEE 802.3z, clause 30)

## **Signal Descriptions**

This section describes the controller interfaces and the signals used in each interface. Figure 4 is a diagram of the 8101/8104 signals.

## Figure 4 8101/8104 Interface Diagram

## System Interface Signals

This section describes the 8101/8104 system interface signals.

#### CLR RXDC Clear RXDC

When CLR RXDC is asserted, the RXDC pin is cleared. When CLR RXDC is LOW, the RXDC pin is not cleared. CLR RXDC is clocked in on the rising edge of the system clock, SCLK.

This pin only clears RXDC when AutoClear mode is disabled. When AutoClear mode is enabled, this pin is ignored and RXDC is automatically cleared two clock cycles after RXEOF is asserted.

#### **Clear TXDC** CLR\_TXDC

When CLR\_TXDC is HIGH, the TXDC pin is cleared. When CLR TXDC is LOW, the TXDC pin is not cleared. TXDC is clocked in on the rising edge of the system clock, SCLK.

This pin only clears TXDC when AutoClear mode is disabled. When AutoClear mode is enabled, this pin is ignored and TXDC is automatically cleared two clock cycles after TXEOF is asserted.

#### FCNTRL **Flow Control Enable** Input When FCNTRL is HIGH, transmitter automatically transmits a MAC control pause frame. When FCNTRL is LOW, the controller resumes normal operation. FCNTRL is clocked in on the rising edge of the system clock, SCLK.

RXABORT Receive FIFO Data Abort Input When RXABORT is asserted, the packet being read out on RXD[31:0] is aborted and discarded. When LOW, the packet is not aborted and discarded. RXABORT is clocked in on the rising edge of the system clock, SCLK. **RXBE[3:0]** Receive Byte Enable Output

## These outputs determine which bytes of the current data on RXD[31:0] contain valid data. RXBE[3:0] is clocked out of the device on the rising edge of the system interface clock, SCLK.

### Input

## Input

RXD[31:0] **Receive Data** Output This output bus contains the 32-bit received data word that is clocked out on the rising edge of the system interface clock. SCLK.

RXDC

#### **Receive Packet Discard** Output When HIGH, device detects that current packet being output on the system interface has an error and should be discarded. When LOW, no discard.

Asserting the RXABORT pin or setting the AUTORXAB bit in register 9 (Configuration 3 Register) automatically discards the packet being output. RXDC is clocked out on the rising edge of the system clock, SCLK.

If AutoClear mode is not enabled, this output is latched HIGH and stays latched until cleared with the assertion of the CLR\_RXDC pin. If AutoClear mode is enabled, this output is latched HIGH and automatically clears itself two clock cycles after RXEOF is asserted. RXDC can also be cleared with RXABORT if programmed to do so.

#### **RXENn Receive Enable** Input This input must be asserted active LOW to enable the

current data word to be clocked out of the receive FIFO on RXD[31:0]. RXENn is clocked in on the rising edge of the system interface clock, SCLK.

on the rising edge of the system interface clock, SCLK.

#### RXEOF **Receive End Of Frame** Output This output is asserted on the same clock cycle when the last word of the packet is being read out of the receive FIFO on RXD[31:0]. RXEOF is clocked out of the device

#### **RXOEn Receive Output Enable** Input When LOW, all receive outputs are active. When HIGH, receive outputs (RXD[31:0], RXBE[3:0], RXSOF, RXEOF) are high-impedence.

#### RXSOF Receive Start Of Frame Output This output is asserted on the same clock cycle when the first word of the packet is being read out of the receive FIFO on RXD[31:0]. RXSOF is clocked out of the device on the rising edge of the system interface clock, SCLK.

#### 16

|           | either RXWM1 or RXWM2 is asserted, independent of RXENn.                                                                                                                                                                                                                                                                                                                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXWM2     | Receive FIFO Watermark 2 Output<br>When RXWM2 is LOW, the receive FIFO data is less<br>than or equal to the receive FIFO watermark 2 threshold<br>and no EOF in FIFO. When HIGH, the receive FIFO data<br>is greater than the watermark. RXWM2n is clocked out<br>on the rising edge of the system clock, SCLK. Data is<br>valid on RXD[31:0] when either RXWM1 or RXWM2 is<br>asserted, independent of RXENn. |

| SCLK      | System Interface ClockInputThis input clocks data in and out of the transmit and<br>receive FIFOs on TXD[31:0] and RXD[31:0], respectively.All system interface inputs and outputs are also clocked<br>in and out on the rising edge of SCLK, with the exception<br>of RXOEn. SCLK clock frequency must be between<br>33–66 MHz.                                                                               |

| TXBE[3:0] | Transmit Byte EnableInputThese inputs determine which bytes of the current 32-bitword on TXD[31:0] contain valid data. TXBE[3:0] isclocked into the device on the rising edge of the systeminterface clock, SCLK.                                                                                                                                                                                              |

| TXCRCn    | Transmit CRC EnableInputWhen TXCRC is LOW, CRC is calculated and appended<br>to the current packet being input on the system interface.When TXCRC is HIGH, CRC is not calculated. TXCRCn<br>is clocked in on the rising edge of the system clock,<br>SCLK, and must be asserted on the same SCLK clock<br>cycle as TXSOF.                                                                                      |

| TXD[31:0] | Transmit Data Input                                                                                                                                                                                                                                                                                                                                                                                            |

**Receive FIFO Watermark 1**

When RXWM1 is LOW, the receive FIFO data is less than or equal to the receive FIFO watermark 1 threshold. When HIGH, the receive FIFO data is greater than the watermark. RXWM1 is clocked out on the rising edge of the system clock, SCLK. Data is valid on RXD[31:0] when

## [31:0] Transmit Data Input This input bus contains the 32-bit data word that is clocked into the transmit FIFO on the rising edge of the system interface clock, SCLK.

RXWM1

Output

| TXDC   | Transmit Packet DiscardOutputWhen TXDC is HIGH, the controller detects that the<br>current packet being input on the system interface has an<br>error, the rest of packet is ignored. When LOW, The<br>packet is not discarded. TXDC is clocked out on thr rising<br>edge of the system clock. |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | If AutoClear mode is not enabled, this output is latched<br>HIGH and stays latched until cleared with the assertion<br>of the CLR_TXDC pin. If the AutoClear mode is enabled,<br>this output is latched HIGH and automatically clears itself<br>two clock cycles after TXEOF is asserted.      |

| TXENn  | Transmit EnableInputThis input must be low to enable the current data word<br>on TXD[31:0] to be clocked into the transmit FIFO.TXENn is clocked in on the rising edge of the system<br>interface clock, SCLK.                                                                                 |

| TXEOF  | Transmit End Of FrameInputThis input must be asserted on the same clock cyclewhen the last word of the packet is being clocked in onTXD[31:0]. TXEOF is clocked into the device on the risingedge of the system interface clock, SCLK.                                                         |

| TXSOF  | Transmit Start Of FrameInputThis input must be asserted in the same clock cycle that<br>the first word of the packet is being clocked in on<br>TXD[31:0]. TXSOF is clocked into the device on the rising<br>edge of the system interface clock, SCLK.                                          |

| TXWM1n | Transmit FIFO Watermark 1OutputWhen TXWM1n is HIGH, the transmit FIFO data is less<br>than or equal to the transmit FIFO watermark 1. When<br>LOW, the transmit FIFO data is above the watermark.<br>TXWM1n is clocked out on the rising edge of the system<br>clock, SCLK.                    |

| TXWM2n | Transmit FIFO Watermark 2OutputWhen TXWM2n is HIGH, the transmit FIFO data is less<br>than or equal to the transmit FIFO watermark 2. When<br>LOW, the transmit FIFO data is above the watermark.<br>TXWM2n is clocked out on the rising edge of the system<br>clock, SCLK.                    |

# **10-Bit PHY Interface Signals**

This section describes the 8101/8104 10-Bit PHY interface signals.

| EN_CDET  | Comma Detect EnableOutputThis output is asserted when either the receive 8B/10BPCS state machine is in the loss of synchronization stateor the CDET bit is set in Register 9 (Configuration 3register. This output is typically used to enable thecomma detect function in an external physical layerdevice. |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EWRAP    | Loopback Output Enable Output<br>This output is asserted whenever the EWRAP bit is set<br>in Register 9 (Configuration 3 register). This output is<br>typically used to enable loopback in an external physical<br>layer device.                                                                             |

| LCK_REFn | Receiver LockOutputThis output is asserted whenever the LCK_REFn bit is<br>set in Register 9 (Configuration 3 register). This output is<br>typically used to enable the receive lock-to-reference<br>mechanism in an external physical layer                                                                 |

| RBC[1:0] | Receive ClockInputThe RBC[1:0] signals clock receive data into the<br>controller on the clock rising edge. RBC[1:0] are<br>62.5 MHz clocks, 180° out of phase, that clock data into<br>the controller on RX[9:0] at an effective rate of 125 MHz.<br>                                                        |

| RX[9:0]  | Dessive Deta                                                                                                                                                                                                                                                                                                 |

|          | Receive DataInputThese inputs contain receive data that are clocked in on<br>the rising edges of RBC[1:0]                                                                                                                                                                                                    |

| ТВС      | These inputs contain receive data that are clocked in on                                                                                                                                                                                                                                                     |

## **Register Interface Signals**

This section describes the 8101/8104 register interface signals.

- **REGA[7:0]** Register Interface Address Input These inputs provide the address for the specific internal register to be accessed, and are clocked into the device on the rising edge of REGCLK.

- REGCLKRegister Interface ClockInputThis input clocks data in and out on REGD[15:0],<br/>REGA[7:0], REGRDn, and REGWRn on its rising edge.<br/>REGCLK frequency must be between 5–40 MHz.

- REGCSnRegister Interface Chip SelectInputThis input must be asserted to enable reading and writing<br/>data on REGD[15:0] and REGA[7:0]. This input is<br/>clocked in on the rising edge of REGCLK.

- **REGD[15:0]** Register Interface Data Bus Bidirectional This bus is a bidirectional 16-bit data path to and from the internal registers. Data is read and written from and to the internal registers on the rising edge of the register clock, REGCLK.

- **REGINT Register Interface Interrupt Output** This output is asserted when certain interrupt bits in the registers are set, and it remains latched HIGH until all interrupt bits are read and cleared.

- REGRDnRegister Interface ReadInputWhen this input is asserted, the accessed internal<br/>register is read (data is output from the register). This<br/>input is clocked into the device on the rising edge of<br/>REGCLK.

- **REGWRN Register Interface Write Input** When this input is asserted, the accessed internal register is written (data is input to the register). This input is clocked into the device on the rising edge of REGCLK.

## **Micellaneous Signals**

This section describes the 8101/8104 micellaneous signals.

- LINKn Receive Link Output When this signal is HIGH, there is no link. When this signal is asserted, the receive link is synchronized and configured.

- **RESERVED** Reserved These pins are reserved and must be left floating.

- RESETnResetInputWhen this signal is HIGH, controller is in normal<br/>operation. When this signal is asserted, controller resets,<br/>FIFOs are cleared, counters are cleared, and register bits<br/>are set to default values.

- SDSignal DetectInputWhen this signal is asserted, data detected on receive<br/>10-bit PHY is valid. When SD is LOW, data is not valid<br/>and the 8B/10B PCS receiver is forced to a loss of sync<br/>state. This signal is ignored (assumed high) unless the<br/>SD\_EN bit in Register 9 (Configuration 3) register is<br/>cleared.

- TAP3-State All PinsInputThis pin is used for testing purposes only. When<br/>asserted, all output and bidirectional pins are placed in a<br/>high-impedence state.

- TESTTest ModeInputThis pin is used for factory test and must be tied LOW for<br/>proper operation.InputTCLKTransmit ClockInput

- **CLK** Transmit Clock Input This 125 MHz input clock is used by the 8B/10B PCS section and generates the 125 MHz transmit output clock, TBC is used to output data on the 10-bit PHY interface.

# **Power Supply Signals**

This section describes the 8101/8104 power supply signals.

| VCC | Positive Supply $3.3 \text{ V} \pm 5\%$ | - |

|-----|-----------------------------------------|---|

| GND | Ground<br>0 Volts                       | - |

## **Specifications**

This section describes the specifications of the 8101/8104 Gigabit Ethernet Controller.

## **Absolute Maximum Ratings**

Absolute maximum ratings are limits, which when exceeded may cause permanent damage to the device or affect device reliability. All voltages are specified with respect to GND, unless otherwise specified.

| VCC supply voltage                 | –0.3 V to +4.0 V  |

|------------------------------------|-------------------|

| All inputs and outputs             | -0.3 V to +5.5 V  |

| Package power dissipation          | 2.2 Watt @ 70 °C  |

| Storage temperature                | –65 °C to +150 °C |

| Temperature under bias             | –10 °C to +85 °C  |

| Lead temperature (soldering, 10 s) | 260 °C            |

| Body temperature (soldering, 30 s) | 220 °C            |

## **DC Electrical Characteristics**

Table 3 lists and describes the DC electrical characteristics of the8101/8104. Unless otherwise noted, all test conditions are as follows:

- TA = 0 to +70  $^{\circ}$ C

- VCC = 3.3 V ± 5%

- SCLK = 66 MHz  $\pm$  0.01%

- TCLK = 125 MHz ± 0.01%

### Table 3 DC Electrical Characteristics

|        |                     | Limit       |     |     |      |                                 |

|--------|---------------------|-------------|-----|-----|------|---------------------------------|

| Symbol | Parameter           | Min         | Тур | Max | Unit | Conditions                      |

| VIL    | Input LOW voltage   | _           | _   | 0.8 | Volt |                                 |

| VIH    | Input HIGH voltage  | 2           | -   | 5.5 | Volt |                                 |

| IIL    | Input LOW current   | -           | -   | -1  | μA   | VIN = GND                       |

| ΙΗ     | Input HIGH current  | _           | _   | 1   | μA   | VIN = VCC                       |

| VOL    | Output LOW voltage  | GND         | _   | 0.4 | Volt | IOL = -4 mA<br>All except LINKn |

|        |                     | GND         | -   | 1   | Volt | IOL = -20 mA LINKn              |

| VOH    | Output HIGH voltage | 2.4         | -   | VCC | Volt | IOL = 4 mA<br>All except LINKn  |

|        |                     | VCC<br>-1.0 | -   | VCC | Volt | IOL = 20 mA LINKn               |

| CIN    | Input capacitance   | -           | -   | 5   | pF   |                                 |

| ICC    | VCC supply current  | _           | -   | 300 | mA   | No output load                  |

## **AC Electrical Characteristics**

The following tables list and describe the the AC electrical characteristics of the 8101/8104. Unless otherwise noted, all test conditions are as follows:

- TA = 0 to +70 °C

- VCC = 3.3 V ± 5%

- SCLK = 66 MHz ± 0.01%

- TCLK = 125 MHz  $\pm$  0.01%

- Input conditions:

- All Inputs: tr, tf  $\leq$  4 ns, 0.8 V to 2.0 V

- Output loading

- TBC, TX[9:0]: 10 pF

- LINK: 50 pF

- All other digital outputs: 30 pF

- Measurement points:

- Data active to 3-state: 200 mV change

- Data 3-state to active: 200 mV change

- All inputs and outputs: 1.5 Volts

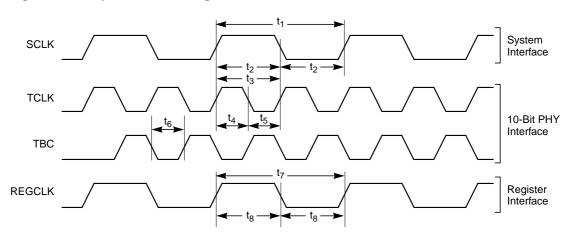

|        |                   | Limit  |     |        |       |            |

|--------|-------------------|--------|-----|--------|-------|------------|

| Symbol | Parameter         | Min    | Тур | Max    | Unit  | Conditions |

| t1     | SCLK cycle time   | 1/33   |     | 1/66   | 1 MHz |            |

| t2     | SCLK duty cycle   | 40     |     | 60     | %     |            |

| t3     | TCLK period       | 7.9992 | 8   | 8.0008 | ns    |            |

| t4     | TCLK HIGH time    | 3.6    |     | 4.4    | ns    |            |

| t5     | TCLK LOW time     | 3.6    |     | 4.4    | ns    |            |

| t6     | TCLK to TBC delay | 0      |     | 8      | ns    |            |

| t7     | REGCLK cycle time | 1/5    |     | 1/40   | 1 MHz |            |

| t8     | REGCLK duty cycle | 40     |     | 60     | %     |            |

## Table 4 Input Clock Timing Characteristics

Note: Refer to Figure 5 for timing diagram.

## Figure 5 Input Clock Timing

|        |                                                      | Limit           |     |     |      |            |

|--------|------------------------------------------------------|-----------------|-----|-----|------|------------|

| Symbol | Parameter                                            | Min             | Тур | Max | Unit | Conditions |

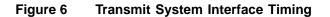

| t11    | TXENn setup time                                     | 5               |     |     | ns   |            |

| t12    | TXENn hold time                                      | 0               |     |     | ns   |            |

| t13    | TXENn deassert time                                  | 1 SCLK<br>cycle |     |     | ns   |            |

| t14    | TXD, TXBE, TXSOFn,<br>TXEOF, and TXCRC<br>setup time | 5               |     |     | ns   |            |

| t15    | TXD, TXBE, TXSOFn,<br>TXEOF, and TXCRC<br>hold time  | 0               |     |     | ns   |            |

| t16    | TXWMn[2:1] delay time                                | 0               |     | 8   | ns   |            |

| t17    | TXWMn[2:1] rise/fall time                            |                 |     | 4   | ns   |            |

## Table 5 Transmit System Interface Timing Characteristics

Note: Refer to Figure 6 for timing diagram.

[1] Back-to-back packet transmission allowed without TXENn deassertion.

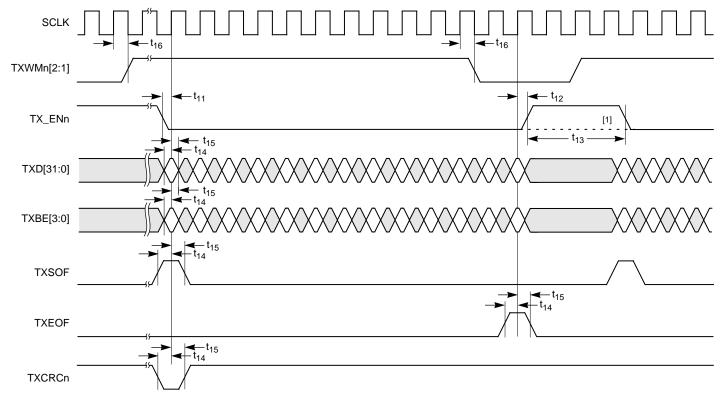

| Table 6 | Receive System I | nterface Timing | Characteristics |

|---------|------------------|-----------------|-----------------|

|---------|------------------|-----------------|-----------------|

|        |                                                        | Limit            |     |                          |      |            |

|--------|--------------------------------------------------------|------------------|-----|--------------------------|------|------------|

| Symbol | Parameter                                              | Min              | Тур | Max                      | Unit | Conditions |

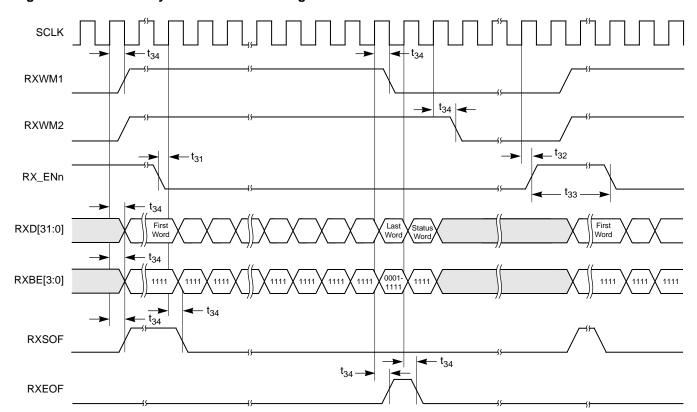

| t31    | RXENn setup time                                       | 5                |     |                          | ns   |            |

| t32    | RXENn hold time                                        | 1                |     |                          | ns   |            |

| t33    | RXENn deassert time                                    | 3 SCLK<br>cycles |     |                          | ns   |            |

| t34    | RXD, RXBE, RXSOF,<br>RXEOF, and RXWM<br>delay time     | 0                |     | 8                        | ns   |            |

| t35    | RXD, RXBE, RXSOF,<br>RXEOF, and RXWM<br>rise/fall time |                  |     | 4                        | ns   |            |

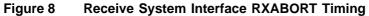

| t41    | RXABORT setup time                                     | 5                |     |                          | ns   |            |

| t42    | RXABORT hold time                                      | 0                |     |                          | ns   |            |

| t43    | RXABORT assert to<br>RXWM deassert delay               | 0                |     | 1 SCLK<br>cycle<br>+8 ns | ns   |            |

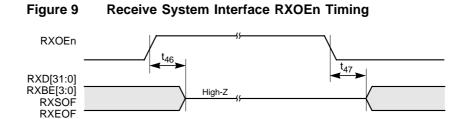

| t46    | RXOEn deassert to data<br>High-Z delay                 | 0                |     | 15                       | ns   |            |

| t47    | RXOEn assert to data active delay                      | 0                |     | 15                       | ns   |            |

Note: Refer to Figure 7 through 9 for timing diagrams.

## Figure 7 Receive System Interface Timing

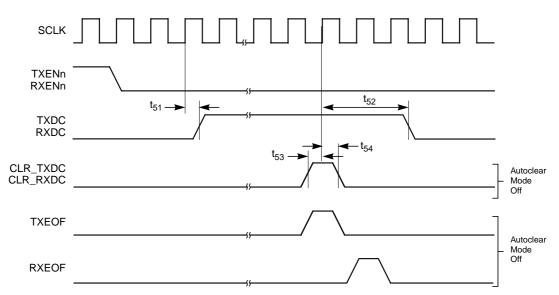

## Table 7 System Interface TXDC/RXDC Timing Characteristics

|        |                                  |     | Limit | t                         |      |                    |

|--------|----------------------------------|-----|-------|---------------------------|------|--------------------|

| Symbol | Parameter                        | Min | Тур   | Max                       | Unit | Conditions         |

| t51    | TXDC/RXDC<br>assert delay time   | 0   |       | 8                         | ns   |                    |

| t52    | TXDC/RXDC<br>deassert delay time | 0   |       | 2 SCLK<br>cycles<br>+8 ns | ns   | AutoClear mode off |

|        |                                  | 0   |       | 3 SCLK<br>cycles<br>+8 ns | ns   | AutoClear mode on  |

| t53    | CLR_TXDC/RXDC<br>setup time      | 5   |       |                           | ns   |                    |

| t54    | CLR_TXDC/RXDC<br>hold time       | 0   |       |                           | ns   |                    |

| t55    | TXDC/RXDC<br>rise and fall time  |     |       | 4                         | ns   |                    |

| Note: | Refer to | Figure | 10 for | timing | diagram. |

|-------|----------|--------|--------|--------|----------|

|-------|----------|--------|--------|--------|----------|

## Figure 10 System Interface RXDC/TXDC Timing

|        |                                              |       | Limit |       |      |                                    |

|--------|----------------------------------------------|-------|-------|-------|------|------------------------------------|

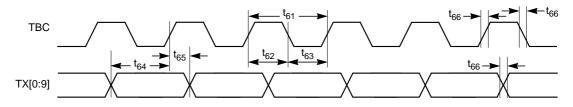

| Symbol | Parameter                                    | Min   | Тур   | Max   | Unit | Conditions                         |

| t61    | TBC period                                   | 7.992 | 8     | 8.008 | ns   |                                    |

| t62    | TBC HIGH time                                | 3.2   |       | 4.8   | ns   |                                    |

| t63    | TBC LOW time                                 | 3.2   |       | 4.8   | ns   |                                    |

| t64    | TX[9:0] data valid before<br>TBC rising edge | 2.0   |       |       | ns   | Assumes TBC duty<br>cycle = 40–60% |

| t65    | TX[9:0] data valid after<br>TBC rising edge  | 1.0   |       |       | ns   | Assumes TBC duty<br>cycle = 40–60% |

| t66    | TBC, TX[9:0]<br>rise and fall time           | 0.7   |       | 2.4   | ns   |                                    |

## Table 8 Transmit 10-Bit PHY Interface Timing Characteristics

Note: Refer to Figure 11 for timing diagram.

## Figure 11 Transmit 10-Bit PHY Interface Timing

|        |                                 |         | Limit |         |      |                           |

|--------|---------------------------------|---------|-------|---------|------|---------------------------|

| Symbol | Parameter                       | Min     | Тур   | Max     | Unit | Conditions                |

| t71    | RBC frequency                   | 62.4937 | 62.5  | 62.5063 | MHz  |                           |

| t72    | RBC HIGH time                   | 6.4     |       | 9.6     | ns   |                           |

|        |                                 | 6.4     |       | 128     | ns   | During<br>synchronization |

| t73    | RBC LOW time                    | 6.4     |       | 9.6     | ns   |                           |

|        |                                 | 6.4     |       | 128     | ns   | During<br>synchronization |

| t74    | RBC skew                        | 7.5     |       | 8.5     | ns   |                           |

| t75    | RX[9:0] setup time              | 2.5     |       |         | ns   |                           |

| t76    | RX[9:0] hold time               | 1.5     |       |         | ns   |                           |

| t77    | RBC, RX[9:0] rise and fall time | 0.7     |       | 2.4     | ns   |                           |

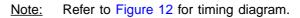

## Table 9 Receive 10-Bit PHY Interface Timing Characteristics

## Figure 12 Receive 10-Bit PHY Interface Timing

|        |                                                     |     | Limi | it                              |      |                                                                            |

|--------|-----------------------------------------------------|-----|------|---------------------------------|------|----------------------------------------------------------------------------|

| Symbol | Parameter                                           | Min | Тур  | Max                             | Unit | Conditions                                                                 |

| t81    | REGCSn, REGWRn,<br>REGRDn, REGA, REGD<br>setup time | 10  |      |                                 | ns   |                                                                            |

| t82    | REGCSn, REGWRn,<br>REGRDn, REGA, REGD<br>hold time  | 1   |      |                                 | ns   |                                                                            |

| t83    | REGCLK to REGD active delay                         |     |      | 10                              | ns   | Read cycle.<br>All registers except<br>Counter Registers 1–53              |

|        |                                                     |     |      | 6<br>REGCLK<br>cycles<br>+10 ns | ns   | Read cycle. Counter<br>Registers 1–53, first<br>16 bits of counter result  |

|        |                                                     |     |      | 3<br>REGCLK<br>cycles<br>+10 ns | ns   | Read cycle. Counter<br>Registers 1–53, second<br>16 bits of counter result |

| t84    | REGCLK to REGD<br>3-state delay                     | 0   |      | 10                              | ns   |                                                                            |

| t85    | REGCLK to REGINT assert delay                       | 0   |      | 20                              | ns   |                                                                            |

| t86    | REGCLK to REGINT deassert delay                     | 0   |      | 20                              | ns   |                                                                            |

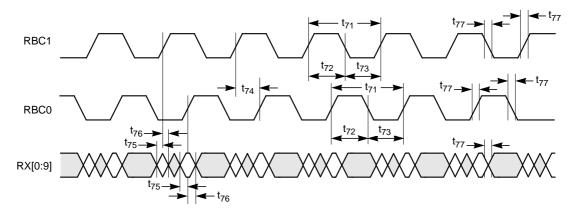

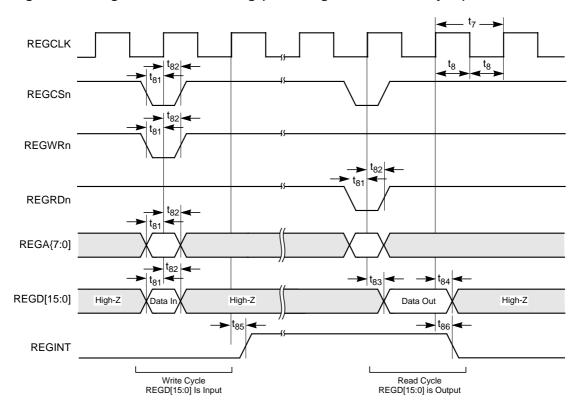

## Table 10 Register Interface Timing Characteristics

Note: Refer to Figure 13 and Figure 14 for timing diagrams.

Figure 13 Register Interface Timing (Excluding Counter Read Cycle)

Figure 14 Register Interface Timing, Counter Read Cycle

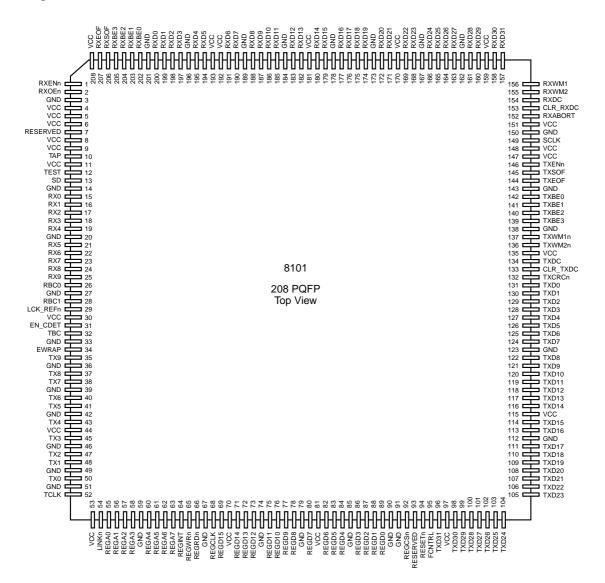

## 8101/8104 Pinouts and Pin Listings

Figure 15 shows the pinout and Table 11 lists the pins for the 8101 and Figure 16 shows the pinout and Table 12 lists the pins for the 8104.

## Table 11 8101 208-Pin PQFP Pin List (Alphabetical Listing)

| Signal   | Pin | Signal   | Pin | Signal      | Pin | Signal | Pin | Signal | Pin |

|----------|-----|----------|-----|-------------|-----|--------|-----|--------|-----|

| CLR_RXDC | 153 | REGA2    | 57  | RXBE1       | 203 | SCLK   | 149 | TXD21  | 107 |

| CLR_TXDC | 133 | REGA3    | 58  | RXBE2       | 204 | SD     | 13  | TXD22  | 106 |

| EN_CDET  | 31  | REGA4    | 60  | RXBE3       | 205 | TAP    | 10  | TXD23  | 105 |

| EWRAP    | 34  | REGA5    | 61  | RXD0        | 200 | TBC    | 32  | TXD24  | 104 |

| FCNTRL   | 95  | REGA6    | 62  | RXD1        | 199 | TCLK   | 52  | TXD25  | 103 |

| GND      | 3   | REGA7    | 63  | RXD2        | 198 | TEST   | 12  | TXD26  | 102 |

| GND      | 14  | REGCLK   | 68  | RXD3        | 197 | TX0    | 50  | TXD27  | 101 |

| GND      | 20  | REGCSn   | 92  | RXD4        | 195 | TX1    | 48  | TXD28  | 100 |

| GND      | 27  | REGD0    | 89  | RXD5        | 194 | TX2    | 47  | TXD29  | 99  |

| GND      | 33  | REGD1    | 88  | RXD6        | 191 | TX3    | 45  | TXD30  | 98  |

| GND      | 36  | REGD2    | 87  | RXD7        | 190 | TX4    | 43  | TXD31  | 96  |

| GND      | 39  | REGD3    | 86  | RXD8        | 188 | TX5    | 41  | TXDC   | 134 |

| GND      | 42  | REGD4    | 84  | RXD9        | 187 | TX6    | 40  | TXENn  | 146 |

| GND      | 46  | REGD5    | 83  | RXD10       | 186 | TX7    | 38  | TXEOF  | 144 |

| GND      | 49  | REGD6    | 82  | RXD11       | 185 | TX8    | 37  | TXSOF  | 145 |

| GND      | 51  | REGD7    | 80  | RXD12       | 183 | TX9    | 35  | TXWM1n | 137 |

| GND      | 59  | REGD8    | 78  | RXD13       | 182 | TXBE0  | 142 | TXWM2n | 136 |

| GND      | 67  | REGD9    | 77  | RXD14       | 180 | TXBE1  | 141 | VCC    | 4   |

| GND      | 74  | REGD10   | 76  | RXD15       | 179 | TXBE2  | 140 | VCC    | 5   |

| GND      | 79  | REGD11   | 75  | RXD16       | 177 | TXBE3  | 139 | VCC    | 6   |

| GND      | 85  | REGD12   | 73  | RXD17       | 176 | TXCRCn | 132 | VCC    | 8   |

| GND      | 90  | REGD13   | 72  | RXD18       | 175 | TXD0   | 131 | VCC    | 9   |

| GND      | 91  | REGD14   | 71  | RXD19       | 174 | TXD1   | 130 | VCC    | 11  |

| GND      | 112 | REGD15   | 69  | RXD20       | 172 | TXD2   | 129 | VCC    | 30  |

| GND      | 123 | REGINT   | 64  | RXD21       | 171 | TXD3   | 128 | VCC    | 44  |

| GND      | 138 | REGRDn   | 66  | RXD22       | 169 | TXD4   | 127 | VCC    | 53  |

| GND      | 143 | REGWRn   | 65  | RXD23       | 168 | TXD5   | 126 | VCC    | 70  |

| GND      | 150 | RESERVED | 7   | RXD24       | 166 | TXD6   | 125 | VCC    | 81  |

| GND      | 162 | RESERVED | 93  | RXD25       | 165 | TXD7   | 124 | VCC    | 97  |

| GND      | 167 | RESETn   | 94  | RXD26       | 164 | TXD8   | 122 | VCC    | 115 |

| GND      | 173 | RX0      | 15  | RXD27       | 163 | TXD9   | 121 | VCC    | 135 |

| GND      | 178 | RX1      | 16  | RXD28       | 161 | TXD10  | 120 | VCC    | 147 |

| GND      | 184 | RX2      | 17  | RXD29       | 160 | TXD11  | 119 | VCC    | 148 |

| GND      | 189 | RX3      | 18  | RXD30       | 158 | TXD12  | 118 | VCC    | 151 |

| GND      | 196 | RX4      | 19  | RXD31       | 157 | TXD13  | 117 | VCC    | 159 |

| GND      | 201 | RX5      | 21  | RXDC        | 154 | TXD14  | 116 | VCC    | 170 |

| LCK_REFn | 29  | RX6      | 22  | RXENn       | 1   | TXD15  | 114 | VCC    | 181 |

| LINKn    | 54  | RX7      | 23  | RXEOF       | 207 | TXD16  | 113 | VCC    | 193 |

| RBC0     | 26  | RX8      | 24  | RXOEn       | 2   | TXD17  | 111 | VCC    | 192 |

| RBC1     | 28  | RX9      | 25  | RXSOF       | 206 | TXD18  | 110 | VCC    | 208 |

| REGA0    | 55  | RXABORT  | 152 | RXWM1       | 156 | TXD19  | 109 |        | 200 |

| REGA1    | 56  | RXBE0    | 202 | RXWM2       | 155 | TXD20  | 108 |        |     |

|          | 00  | 10 OLO   | 202 | 10/00/01/02 | 100 |        | 100 |        |     |

| Pinout    |

|-----------|

| BGA       |

| 208-Pin   |

| 8104      |

| Figure 16 |

| A16<br>RXD31 | B16 | RXWM2 | C16<br>TXDC     | D16 | VCC      | E16  | TXENn | F16 | TXBE1 | G16 | TXWM1n | H16 | CLR_TXDC | J16 | TXD4     | K16 | TXD8    | L16 | TXD12 | M16 | VCC   | N16 | TXD16    | P16 | TXD20        | R16 | TXD21  | T16<br>TXD24  |

|--------------|-----|-------|-----------------|-----|----------|------|-------|-----|-------|-----|--------|-----|----------|-----|----------|-----|---------|-----|-------|-----|-------|-----|----------|-----|--------------|-----|--------|---------------|

| A15<br>RXD30 | B15 | RXWM1 | C15<br>CLR_RXDC | D15 | SLCK     | E15  | TXSOF | F15 | TXBE0 | G15 | TXWM2n | H15 | TXCRCn   | J15 | TXD5     | K15 | GND     | L15 | TXD11 | M15 | TXD15 | N15 | TXD18    | P15 | TXD22        | R15 | TXD23  | T15<br>TXD25  |

| A14<br>RXD29 | B14 | VCC   | C14<br>RXABORT  | D14 | VCC      | E 14 | TXEOF | F14 | TXBE2 | G14 | VCC    | H14 | TXD0     | J14 | TXD3     | K14 | TXD7    | L14 | TXD10 | M14 | TXD14 | N14 | TXD17    | P14 | TXD19        | R14 | TXD27  | T14<br>TXD26  |

| A13<br>RXD27 | B13 | RXD28 | C13<br>GND      | D13 | VCC      | E 13 | GND   | F13 | TXBE3 | G13 | TXDC   | H13 | TXD1     | J13 | TXD2     | K13 | TXD6    | L13 | TXD9  | M13 | TXD13 | N13 | VCC      | P13 | TXD30        | R13 | TXD28  | T13<br>TXD29  |

| A12<br>RXD23 | B12 | RXD25 | C12<br>RXD26    | D12 | RXD24    |      |       |     |       |     |        |     |          |     |          |     |         |     |       |     |       | N12 | RESERVED | P12 | RESETn       | R12 | TXD31  | T12<br>FCNTRL |

| A11<br>RXD21 | B11 | VCC   | C11<br>RXD22    | D11 | VCC      |      |       |     |       |     |        |     |          |     |          | 1   |         | 1   |       |     |       | N11 | REGD1    | P11 | REGD0        | R11 | GND    | T11<br>REGCSn |

| A10<br>RXD20 | B10 | RXD19 | C10<br>RXD18    | D10 | RXD17    |      |       |     |       | G10 | GND    | H10 | GND      | J10 | GND      | K10 | GND     |     |       |     |       | N10 | REGD5    | P10 | REGD4        | R10 | REGD2  | T10<br>REGD3  |

| A9<br>RXD16  | B9  | RXD15 | C9<br>RXD14     | 6D  | VCC      |      |       |     |       | 69  | GND    | 6H  | GND      | 96  | GND      | K9  | GND     |     |       |     |       | 6N  | REGD7    | 64  | REGD6        | R9  | VCC    | T9<br>VCC     |

| A8<br>RXD11  | BB  | RXD10 | c8<br>RXD12     | ä   | RXD13    |      |       |     |       | G8  | GND    | 8   | GND      | JB  | GND      | K8  | GND     |     |       |     |       | NB  | REGD8    | P8  | REGD9        | R8  | REGD11 | T8<br>REGD10  |

| A7<br>RXD7   | 87  | RXD8  | c7<br>RXD6      | D7  | RXD9     |      |       |     |       | G7  | GND    | H7  | GND      | 77  | GND      | K7  | GND     |     |       |     |       | NZ  | REGD12   | P7  | REGD13       | R7  | VCC    | T7<br>REGD14  |

| A6<br>VCC    | B6  | VCC   | c6<br>VCC       | D6  | RXD5     |      |       |     |       |     |        |     |          |     |          |     |         |     |       |     |       | 9N  | REGD15   | P6  | REGCLK       | R6  | REGRDn | T6<br>GND     |

| A5<br>RXD4   | B5  | RXD2  | C5<br>RXD3      | D5  | RXD1     |      |       |     |       |     |        |     |          |     |          |     |         |     |       |     |       | N5  | REGWRn   | P5  | REGINT       | R5  | REGA6  | T5<br>REGA7   |

| A4<br>RXD0   | B4  | RXBE2 | C4<br>RXBE1     | D4  | RXBE0    | E4   | TEST  | F4  | RX2   | G4  | RX6    | H4  | RBC0     | J4  | VCC      | K4  | TX9     | L4  | TX6   | M4  | VCC   | N4  | GND      | P4  | <b>REGA5</b> | R4  | REGA4  | T4<br>GND     |

| A3<br>RXBE3  | B3  | RXSOF | c3<br>VCC       | D3  | RESERVED | E3   | VCC   | F3  | RX1   | e3  | RX5    | H3  | RX9      | J3  | VCC      | K3  | EWRAP   | L3  | GND   | M3  | TX4   | N3  | GND      | 52  | REGA3        | R3  | REGA2  | T3<br>REGA1   |

| A2<br>RXEOF  | B2  | RXENn | c2<br>VCC       | D2  | VCC      | E2   | TAP   | F2  | RX0   | G2  | RX3    | H2  | RX7      | J2  | LCK_REFn | K2  | EN_CDET | 12  | TX8   | M2  | TX5   | N2  | TX2      | P2  | TCLK         | R2  | VCC    | T2<br>REGA0   |

| A1<br>VCC    | B1  | RXOEn | C1<br>GND       | 5   | VCC      | E1   | VCC   | F1  | SD    | G1  | RX4    | Ħ   | RX8      | 11  | RBC1     | K1  | TBC     | L1  | TX7   | M1  | GND   | Z1  | TX3      | P1  | TX1          | R1  | TX0    | T1<br>LINKn   |

## Table 12 8104 208-Pin BGA Pin List (Alphabetical Listing)

| Signal   | Pin | Signal   | Pin | Signal | Pin | Signal | Pin | Signal | Pin |

|----------|-----|----------|-----|--------|-----|--------|-----|--------|-----|

| CLR_RXDC | C15 | REGA4    | R04 | RXBE3  | A03 | TBC    | K01 | TXD24  | T16 |

| CLR_TXDC | H16 | REGA5    | P04 | RXD0   | A04 | TCLK   | P02 | TXD25  | T15 |

| COM_DET  | F01 | REGA6    | R05 | RXD1   | D05 | TEST   | E04 | TXD26  | T14 |

| EN_CDET  | K02 | REGA7    | T05 | RXD2   | B05 | TX0    | R01 | TXD27  | R14 |

| EWRAP    | K03 | REGCLK   | P06 | RXD3   | C05 | TX1    | P01 | TXD28  | R13 |

| FCNTRL   | T12 | REGCSn   | T11 | RXD4   | A05 | TX2    | N02 | TXD29  | T13 |

| GND      | A07 | REGD0    | P11 | RXD5   | D06 | TX3    | N01 | TXD30  | P13 |

| GND      | C01 | REGD1    | N11 | RXD6   | C07 | TX4    | M03 | TXD31  | R12 |

| GND      | C13 | REGD2    | R10 | RXD7   | A07 | TX5    | M02 | TXDC   | G13 |

| GND      | E13 | REGD3    | T10 | RXD8   | B07 | TX6    | L04 | TXENn  | E16 |

| GND      | G07 | REGD4    | P10 | RXD9   | D07 | TX7    | L01 | TXEOF  | E14 |

| GND      | G08 | REGD5    | N10 | RXD10  | B08 | TX8    | L02 | TXSOF  | E15 |

| GND      | G09 | REGD6    | P09 | RXD11  | A08 | TX9    | K04 | TXWM1n | G16 |

| GND      | G10 | REGD7    | N09 | RXD12  | C08 | TXBE0  | F15 | TXWM2n | G15 |

| GND      | H07 | REGD8    | N08 | RXD13  | D08 | TXBE1  | F16 | VCC    | A01 |

| GND      | H08 | REGD9    | P08 | RXD14  | C09 | TXBE2  | F14 | VCC    | A06 |

| GND      | H09 | REGD10   | T08 | RXD15  | B09 | TXBE3  | F13 | VCC    | B06 |

| GND      | H10 | REGD11   | R08 | RXD16  | A09 | TXCRCn | H15 | VCC    | B11 |

| GND      | J07 | REGD12   | N07 | RXD17  | D10 | TXD0   | H14 | VCC    | B14 |

| GND      | J08 | REGD13   | P07 | RXD18  | C10 | TXD1   | H13 | VCC    | C02 |

| GND      | J09 | REGD14   | T07 | RXD19  | B10 | TXD2   | J13 | VCC    | C03 |

| GND      | J10 | REGD15   | N06 | RXD20  | A10 | TXD3   | J14 | VCC    | D01 |

| GND      | K07 | REGINT   | P05 | RXD21  | A11 | TXD4   | J16 | VCC    | D02 |

| GND      | K08 | REGRDn   | R06 | RXD22  | C11 | TXD5   | J15 | VCC    | D09 |

| GND      | K09 | REGWRn   | N05 | RXD23  | A12 | TXD6   | K13 | VCC    | D11 |

| GND      | K10 | RESERVED | D03 | RXD24  | D12 | TXD7   | K14 | VCC    | D13 |

| GND      | K15 | RESERVED | N12 | RXD25  | B12 | TXD8   | K16 | VCC    | D14 |

| GND      | L03 | RESETn   | P12 | RXD26  | C12 | TXD9   | L13 | VCC    | D16 |

| GND      | M01 | RX0      | F02 | RXD27  | A13 | TXD10  | L14 | VCC    | E01 |

| GND      | N03 | RX1      | F03 | RXD28  | B13 | TXD11  | L15 | VCC    | E03 |

| GND      | N04 | RX2      | F04 | RXD29  | A14 | TXD12  | L16 | VCC    | G14 |

| GND      | R11 | RX3      | G02 | RXD30  | A15 | TXD13  | M13 | VCC    | J03 |

| GND      | T04 | RX4      | G01 | RXD31  | A16 | TXD14  | M14 | VCC    | J04 |

| GND      | T06 | RX5      | G03 | RXDC   | C16 | TXD15  | M15 | VCC    | M04 |

| LCK_REFn | J02 | RX6      | G04 | RXENn  | B02 | TXD16  | N16 | VCC    | M16 |

| LINKn    | T01 | RX7      | H02 | RXEOF  | A02 | TXD17  | N14 | VCC    | N13 |

| RBC0     | H04 | RX8      | H01 | RXOEn  | B01 | TXD18  | N15 | VCC    | R02 |

| RBC1     | J01 | RX9      | H03 | RXSOF  | B03 | TXD19  | P14 | VCC    | R07 |

| REGA0    | T02 | RXABORT  | C14 | RXWM1  | B15 | TXD20  | P16 | VCC    | R09 |

| REGA1    | T03 | RXBE0    | D04 | RXWM2  | B16 | TXD21  | R16 | VCC    | T09 |

| REGA2    | R03 | RXBE1    | C04 | SCLK   | D15 | TXD22  | P15 |        |     |

| REGA3    | P03 | RXBE2    | B04 | TAP    | E02 | TXD23  | R15 |        |     |

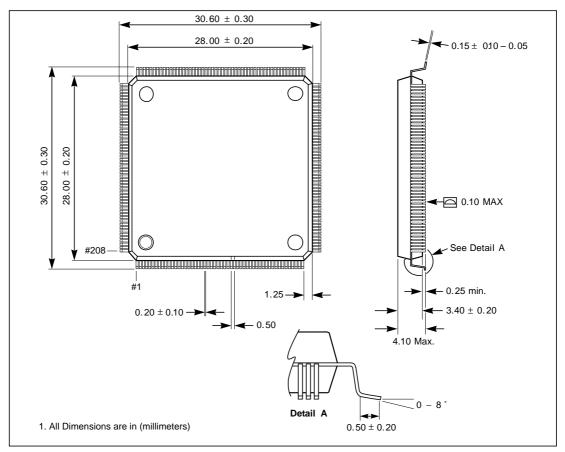

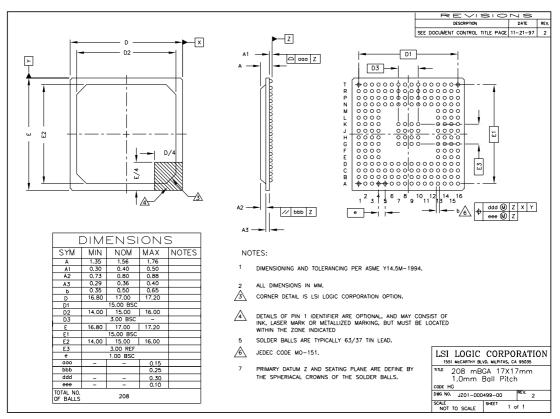

## **Package Mechanical Dimensions**

The 8101 Gigabit Ethernet Controller is available in the 208-pin Plastic Quad Flat Pack (PQFP) as shown in Figure 17. and the 8104 Ball Grid Array Package as shown in Figure 6.14

Important: This drawing may not be the latest version. For board layout and manufacturing, obtain the most recent engineering drawings from your LSI Logic marketing representative by requesting the outline drawing.

Important: This drawing may not be the latest version. For board layout and manufacturing, obtain the most recent engineering drawings from your LSI Logic marketing representative by requesting the outline drawing for package code HG.

## Notes

#### Sales Offices and Design Resource Centers

LSI Logic Corporation Corporate Headquarters Tel: 408.433.8000 Fax: 408.433.8989

#### NORTH AMERICA

California Irvine ♦ Tel: 949.809.4600 Fax: 949.809.4444

Pleasanton Design Center Tel: 925.730.8800 Fax: 925.730.8700

San Diego Tel: 858.467.6981 Fax: 858.496.0548

Silicon Valley ◆ Tel: 408.433.8000 Fax: 408.954.3353

Wireless Design Center Tel: 858.350.5560 Fax: 858.350.0171

Colorado Boulder ♦ Tel: 303.447.3800 Fax: 303.541.0641

Colorado Springs Tel: 719.533.7000 Fax: 719.533.7020

Fort Collins Tel: 970.223.5100 Fax: 970.206.5549

Florida Boca Raton Tel: 561.989.3236

Fax: 561.989.3237 Georgia

Alpharetta Tel: 770.753.6146 Fax: 770.753.6147 Illinois Oakbrook Terrace Tel: 630.954.2234 Fax: 630.954.2235

**Kentucky** Bowling Green Tel: 270.793.0010 Fax: 270.793.0040

Maryland Bethesda Tel: 301.897.5800 Fax: 301.897.8389

Massachusetts Waltham ♦ Tel: 781.890.0180 Fax: 781.890.6158

Burlington - Mint Technology Tel: 781.685.3800 Fax: 781.685.3801

Minneapolis ♦ Tel: 612.921.8300 Fax: 612.921.8399

New Jersey Red Bank Tel: 732.933.2656 Fax: 732.933.2643

Cherry Hill - Mint Technology Tel: 856.489.5530 Fax: 856.489.5531

New York Fairport Tel: 716.218.0020 Fax: 716.218.9010

North Carolina Raleigh Tel: 919.785.4520 Fax: 919.783.8909

Oregon Beaverton Tel: 503.645.0589 Fax: 503.645.6612 **Texas** Austin Tel: 512.388.7294 Fax: 512.388.4171

Plano ♦ Tel: 972.244.5000 Fax: 972.244.5001

> Houston Tel: 281.379.7800 Fax: 281.379.7818

Canada Ontario Ottawa ♦ Tel: 613.592.1263 Fax: 613.592.3253

#### INTERNATIONAL

France Paris LSI Logic S.A. Immeuble Europa ♦ Tel: 33.1.34.63.13.13

Fax: 33.1.34.63.13.19

Germany Munich LSI Logic GmbH ♦ Tel: 49.89.4.58.33.0

Fax: 49.89.4.58.33.108

Stuttgart ♦ Tel: 49.711.13.96.90 Fax: 49.711.86.61.428

Italy Milan LSI Logic S.P.A.

♦ Tel: 39.039.687371 Fax: 39.039.6057867

Japan Tokyo LSI Logic K.K. ♦ Tel: 81.3.5463.7821 Fax: 81.3.5463.7820

Osaka ♦ Tel: 81.6.947.5281 Fax: 81.6.947.5287 Korea Seoul LSI Logic Corporation of Korea Ltd Tel: 82.2.528.3400 Fax: 82.2.528.2250

The Netherlands Eindhoven LSI Logic Europe Ltd Tel: 31.40.265.3580 Fax: 31.40.296.2109

Singapore Singapore LSI Logic Pte Ltd Tel: 65.334.9061 Fax: 65.334.4749

Sweden Stockholm LSI Logic AB ♦ Tel: 46.8.444.15.00 Fax: 46.8.750.66.47

Taiwan Taipei LSI Logic Asia, Inc. Taiwan Branch Tel: 886.2.2718.7828 Fax: 886.2.2718.8869

United Kingdom Bracknell LSI Logic Europe Ltd ◆ Tel: 44.1344.426544

► Tel: 44.1344.426544 Fax: 44.1344.481039

Sales Offices with Design Resource Centers

To receive product literature, visit us at http://www.lsilogic.com

#### ISO 9000 Certified

Printed on Recycled Paper

IF Printed in USA Order No. R15011 Doc. No. DB08-000134-00

The LSI Logic logo design is a registered trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

LSI Logic Corporation reserves the right to make changes to any products and services herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase, lease, or use of a product or service from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or of third parties.