# Advance Information

# EC603e<sup>™</sup> Embedded RISC Microprocessor (PID6) Hardware Specifications

The EC603e microprocessor from Motorola is an implementation of the PowerPC<sup>TM</sup> family of reduced instruction set computing (RISC) microprocessors. The EC603e microprocessor for embedded systems is functionally equivalent to the MPC603e with the exception of the floating-point unit which is not supported on the EC603e microprocessor.

The EC603e microprocessor is implemented in both a 2.5-volt version (PID 0007t EC603e microprocessor, abbreviated as PID7t) and a 3.3-volt version (PID 0006 EC603e microprocessor, abbreviated as PID6). This document describes the pertinent physical characteristics of the PID6. For functional characteristics of the processor, refer to the MPC603e & EC603e RISC Microprocessors User's Manual.

This document contains the following topics:

| Topic                                                 | Page |

|-------------------------------------------------------|------|

| Section 1.1, "Overview"                               | 2    |

| Section 1.2, "Features"                               | 3    |

| Section 1.3, "General Parameters"                     | 4    |

| Section 1.4, "Electrical and Thermal Characteristics" | 4    |

| Section 1.5, "Pin Assignments"                        | 14   |

| Section 1.6, "Pinout Listings"                        | 16   |

| Section 1.7, "Package Description"                    | 20   |

| Section 1.8, "System Design Information"              | 24   |

| Section 1.9, "Document Revision History"              | 30   |

| Section 1.10, "Ordering Information"                  | 30   |

The PowerPC name, the PowerPC logotype, PowerPC 603, and PowerPC 603e are trademarks of International Business Machines Corporation, used by Motorola under license from International Business Machines Corporation. FLOTHERM is a registered trademark of Flomerics Ltd., UK This document contains information on a new product under development by Motorola and IBM. Motorola and IBM reserve the right to change or discontinue this product without notice.

© Motorola Inc., 1999. All rights reserved.

Portions hereof © International Business Machines Corporation, 1991–1999. All rights reserved.

To locate any published errata or updates for this document, refer to the website at http://www.mot.com/SPS/PowerPC/.

# 1.1 Overview

The PID6 implementation of the EC603e microprocessor is a low-power implementation of the PowerPC microprocessor family of reduced instruction set computer (RISC) microprocessors. The PID6 implements the 32-bit portion of the PowerPC architecture specification, which provides 32-bit effective addresses, and integer data types of 8, 16, and 32 bits. For 64-bit PowerPC microprocessors, the PowerPC architecture provides 64-bit integer data types, 64-bit addressing, and other features required to complete the 64-bit architecture.

The PID6 provides four software controllable power-saving modes. Three of the modes (the nap, doze, and sleep modes) are static in nature, and progressively reduce the amount of power consumed by the processor. The fourth is a dynamic power management mode that causes the functional units in the PID6 to automatically enter a low-power mode when the functional units are idle without affecting operational performance, software execution, or any external hardware.

The PID6 is a superscalar processor capable of issuing and retiring as many as three instructions per clock. Instructions can execute out of order for increased performance; however, the PID6 makes completion appear sequential.

The PID6 integrates four execution units—an integer unit (IU), a branch processing unit (BPU), a load/store unit (LSU), and a system register unit (SRU). The ability to execute five instructions in parallel and the use of simple instructions with rapid execution times yield high efficiency and throughput for PID6—based systems. Most integer instructions execute in one clock cycle.

The PID6 provides independent on-chip, 16-Kbyte, four-way set-associative, physically addressed caches for instructions and data, as well as on-chip instruction and data memory management units (MMUs). The MMUs contain 64-entry, two-way set-associative, data and instruction translation lookaside buffers (DTLB and ITLB) that provide support for demand-paged virtual memory address translation and variable-sized block translation. The TLBs and caches use a least-recently used (LRU) replacement algorithm. The PID6 also supports block address translation through the use of two independent instruction and data block address translation (IBAT and DBAT) arrays of four entries each. Effective addresses are compared simultaneously with all four entries in the BAT array during block translation. In accordance with the PowerPC architecture, if an effective address hits in both the TLB and BAT array, the BAT translation takes priority.

The PID6 has a selectable 32- or 64-bit data bus and a 32-bit address bus. The PID6 interface protocol allows multiple masters to compete for system resources through a central external arbiter. The PID6 provides a three-state coherency protocol that supports the exclusive, modified, and invalid cache states. This protocol is a compatible subset of the MESI (modified/exclusive/shared/invalid) four-state protocol and operates coherently in systems that contain four-state caches. The PID6 supports single-beat and burst data transfers for memory accesses, and supports memory-mapped I/O.

The PID6 uses an advanced, 3.3-V CMOS process technology and maintains full interface compatibility with TTL devices.

# 1.2 Features

This section summarizes features of the PID6's implementation of the PowerPC architecture. Major features of the PID6 are as follows:

- High-performance, superscalar microprocessor

- As many as three instructions issued and retired per clock

- As many as five instructions in execution per clock

- Single-cycle execution for most instructions

- Four independent execution units and one register file

- BPU featuring static branch prediction

- A 32-bit IU

- LSU for data transfer between data cache and GPRs

- SRU that executes condition register (CR), special-purpose register (SPR) instructions, and integer add/compare instructions

- Thirty-two GPRs for integer operands

- High instruction and data throughput

- Zero-cycle branch capability (branch folding)

- Programmable static branch prediction on unresolved conditional branches

- Instruction fetch unit capable of fetching two instructions per clock from the instruction cache

- A six-entry instruction queue that provides lookahead capability

- Independent pipelines with feed-forwarding that reduces data dependencies in hardware

- 16-Kbyte data cache—four-way set-associative, physically addressed; LRU replacement algorithm

- 16-Kbyte instruction cache—four-way set-associative, physically addressed; LRU replacement algorithm

- Cache write-back or write-through operation programmable on a per page or per block basis

- BPU that performs CR lookahead operations

- Address translation facilities for 4-Kbyte page size, variable block size, and 256-Mbyte segment size

- A 64-entry, two-way set-associative ITLB

- A 64-entry, two-way set-associative DTLB

- Four-entry data and instruction BAT arrays providing 128-Kbyte to 256-Mbyte blocks

- Software table search operations and updates supported through fast-trap mechanism

- 52-bit virtual address; 32-bit physical address

- Facilities for enhanced system performance

- A 32- or 64-bit split-transaction external data bus with burst transfers

- Support for one-level address pipelining and out-of-order bus transactions

- Integrated power management

- Low-power 3.3-volt design

- Internal processor/bus clock multiplier that provides 1/1, 1.5/1, 2/1, 2.5/1, 3/1, 3.5/1, and 4/1 ratios

- Three power saving modes: doze, nap, and sleep

- Automatic dynamic power reduction when internal functional units are idle

- In-system testability and debugging features through JTAG boundary-scan capability

# 1.3 General Parameters

The following list provides a summary of the general parameters of the PID6.

Technology  $0.5 \mu$  CMOS, four-layer metal Die size  $11.67 \text{ mm x } 8.4 \text{ mm } (98 \text{ mm}^2)$

Transistor count 2.6 million Logic design Fully-static

Package Surface mount 240-pin ceramic quad flat pack (CQFP)

or 255-pin ceramic ball grid array (CBGA)

Power supply  $3.3 \pm 5\% \text{ V dc}$

# 1.4 Electrical and Thermal Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the PID6.

### 1.4.1 DC Electrical Characteristics

The tables in this section describe the PID6 DC electrical characteristics. Table 1 provides the absolute maximum ratings.

|                           |                  | •           |      |

|---------------------------|------------------|-------------|------|

| Characteristic            | Symbol           | Value       | Unit |

| Core supply voltage       | Vdd              | -0.3 to 4.0 | V    |

| PLL supply voltage        | AVdd             | -0.3 to 4.0 | V    |

| I/O supply voltage        | OVdd             | -0.3 to 4.0 | V    |

| Input voltage             | V <sub>in</sub>  | -0.3 to 5.5 | V    |

| Storage temperature range | T <sub>stg</sub> | -55 to 150  | °C   |

**Table 1. Absolute Maximum Ratings**

- 1. Functional operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. Caution: Vin must not exceed OVdd by more than 2.5 V at any time including during power-on reset.

- 3. Caution: OVdd must not exceed Vdd/AVdd by more than 2.5 V at any time including during power-on reset

- Caution: Vdd/AVdd must not exceed OVdd by more than 0.4 V at any time including during power-on reset.

Table 2 provides the recommended operating conditions for the PID6.

**Table 2. Recommended Operating Conditions**

| Characteristic           | Symbol          | Value            | Unit |

|--------------------------|-----------------|------------------|------|

| Core supply voltage      | Vdd             | 3.3 ± 165mv      | V    |

| PLL supply voltage       | AVdd            | 3.3 ± 165mv      | V    |

| I/O supply voltage       | OVdd            | $3.3 \pm 165 mv$ | V    |

| Input voltage            | V <sub>in</sub> | -0.3 to 5.5      | V    |

| Die-junction temperature | T <sub>j</sub>  | 0 to 105         | °C   |

#### Note:

Table 3 provides the packages thermal characteristics for the PID6.

**Table 3. Package Thermal Characteristics**

| Characteristic                                                           | Symbol            | Value | Rating |

|--------------------------------------------------------------------------|-------------------|-------|--------|

| Wire-bond CQFP package die junction-to-case thermal resistance (typical) | $\theta_{JC}$     | 2.2   | °C/W   |

| Wire-bond CQFP package die junction-to-lead thermal resistance (typical) | $\theta_{JB}$     | 18.0  | °C/W   |

| CBGA package die junction-to-case thermal resistance (typical)           | $\theta_{\sf JC}$ | 0.08  | °C/W   |

| CBGA package die junction-to-ball thermal resistance (typical)           | $\theta_{JB}$     | 2.8   | °C/W   |

Note: Refer to Section 1.8, "System Design Information," for more details about thermal management.

Table 4 provides the DC electrical characteristics for the PID6.

**Table 4. DC Electrical Specifications**

At recommended operating conditions. See Table 2

| Characteristic                                              | Symbol           | Min  | Max | Unit | Notes |

|-------------------------------------------------------------|------------------|------|-----|------|-------|

| Input high voltage (all inputs except SYSCLK)               | V <sub>IH</sub>  | 2.0  | 5.5 | V    |       |

| Input low voltage (all inputs except SYSCLK)                | V <sub>IL</sub>  | -0.3 | 0.8 | V    |       |

| SYSCLK input high voltage                                   | CVIH             | 2.4  | 5.5 | V    |       |

| SYSCLK input low voltage                                    | CV <sub>IL</sub> | -0.3 | 0.4 | V    |       |

| Input leakage current, V <sub>in</sub> = 3.465 V            | I <sub>in</sub>  | _    | 10  | μΑ   | 1     |

| V <sub>in</sub> = 5.5 V                                     | I <sub>in</sub>  | _    | 245 | μA   | 1     |

| Hi-Z (off-state) leakage current, V <sub>in</sub> = 3.465 V | I <sub>TSI</sub> | _    | 10  | μΑ   | 1     |

| V <sub>in</sub> = 5.5 V                                     | I <sub>TSI</sub> |      | 245 | μA   | 1     |

| Output high voltage, I <sub>OH</sub> = -9 mA                | V <sub>OH</sub>  | 2.4  |     | V    | 1     |

<sup>1.</sup> These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

### **Table 4. DC Electrical Specifications (Continued)**

At recommended operating conditions. See Table 2

| Characteristic                                                                                                                                                                   | Symbol          | Min | Max  | Unit | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|------|------|-------|

| Output low voltage, I <sub>OL</sub> = 14 mA                                                                                                                                      | V <sub>OL</sub> | _   | 0.4  | V    |       |

| Capacitance, $V_{in} = 0 \text{ V}$ , $f = 1 \text{ MHz}$ (excludes $\overline{\text{TS}}$ , $\overline{\text{ABB}}$ , $\overline{\text{DBB}}$ , and $\overline{\text{ARTRY}}$ ) | C <sub>in</sub> | _   | 10.0 | pF   | 2     |

| Capacitance, $V_{in} = 0 \text{ V}$ , $f = 1 \text{ MHz}$ (for $\overline{TS}$ , $\overline{ABB}$ , $\overline{DBB}$ , and $\overline{ARTRY}$ )                                  | C <sub>in</sub> | _   | 15.0 | pF   | 2     |

#### Notes:

- 1. Excludes test signals (LSSD\_MODE, L1\_TSTCLK, L2\_TSTCLK) and JTAG signals.

- 2. Capacitance is periodically sampled rather than 100% tested.

Table 5 provides the power consumption for the PID6.

### **Table 5. Power Consumption**

At recommended operating conditions. See Table 2

| CPU Clock:                 | Processor | (CPU) Frequency | Unit   | Notes |

|----------------------------|-----------|-----------------|--------|-------|

| SYSCLK                     | 100 MHz   | 133.33 MHz      | - Onit | Notes |

| Full-On Mode (DPM Enabled) |           | •               | '      | •     |

| Typical                    | 3.2       | 4.2             | W      | 1, 3  |

| Max.                       | 4.0       | 5.3             | W      | 1, 2  |

| Doze Mode                  | '         | •               |        |       |

| Typical                    | 1.0       | 1.3             | W      | 1, 2  |

| Nap Mode                   |           |                 |        |       |

| Typical                    | 70        | 85              | mW     | 1, 2  |

| Sleep Mode                 | •         |                 | •      | •     |

| Typical                    | 40        | 50              | mW     | 1, 2  |

| Sleep Mode—PLL Disabled    | •         | •               | •      | •     |

| Typical                    | 5         | 6               | mW     | 1, 2  |

| Sleep Mode—PLL and SYSCLK  | Disabled  |                 |        |       |

| Typical                    | 3         | 3               | mW     | 1, 2  |

- 1. These values apply for all valid bus ratios (PLL\_CFG[0-3] settings). The values do not include I/O supply power (OVdd) or PLL supply power (AVdd). OVdd power is system dependent, but is typically <10% of Vdd power. Worst-case power consumption for AVdd = 15 mw.</p>

- 2. Maximum power is measured at Vdd = 3.465 V using a worst-case instruction mix.

- 3. Typical power is an average value measured at Vdd = AVdd = OVdd = 3.3 V in a system executing typical applications and benchmark sequences.

### 1.4.2 AC Electrical Characteristics

This section provides the AC electrical characteristics for the PID6. After fabrication, parts are sorted by maximum processor core frequency as shown in Section 1.4.2.1, "Clock AC Specifications," and tested for conformance to the AC specifications for that frequency. These specifications are for 100 and 133.33 MHz processor core frequencies. The processor core frequency is determined by the bus (SYSCLK) frequency and the settings of the PLL\_CFG[0–3] signals. Parts are sold by maximum processor core frequency; see Section 1.10, "Ordering Information."

### 1.4.2.1 Clock AC Specifications

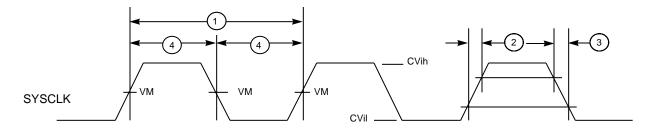

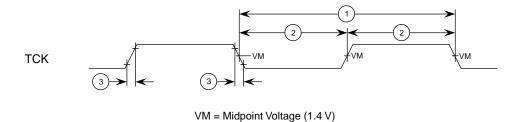

Table 6 provides the clock AC timing specifications as defined in Figure 1.

### **Table 6. Clock AC Timing Specifications**

At recommended operating conditions. See Table 2

| Num | Characteristic                      | 100 MHz  |        | 100 MHz 133.33 MH |        | z 133.33 MHz |       | 133.33 MHz |  | Unit | Notes |

|-----|-------------------------------------|----------|--------|-------------------|--------|--------------|-------|------------|--|------|-------|

|     | Gnaracteristic                      | Min      | Max    | Min               | Max    | Unit         | Notes |            |  |      |       |

|     | Processor frequency                 | 50       | 100    | 50                | 133.33 | MHz          | 1     |            |  |      |       |

|     | VCO frequency                       | 100      | 266.66 | 100               | 266.66 | MHz          | 1     |            |  |      |       |

|     | SYSCLK (bus) frequency              | 16.67    | 66.67  | 16.67             | 66.67  | MHz          |       |            |  |      |       |

| 1   | SYSCLK cycle time                   | 15.0     | 60.0   | 15.0              | 60.0   | ns           |       |            |  |      |       |

| 2,3 | SYSCLK rise and fall time           | <b> </b> | 2.0    | _                 | 2.0    | ns           | 2     |            |  |      |       |

| 4   | SYSCLK duty cycle measured at 1.4 V | 40.0     | 60.0   | 40.0              | 60.0   | %            | 3     |            |  |      |       |

|     | SYSCLK jitter                       | _        | ±150   | _                 | ±150   | ps           | 4     |            |  |      |       |

|     | Internal PLL relock time            | _        | 100    | _                 | 100    | μs           | 3, 5  |            |  |      |       |

- 1. **Caution**: The SYSCLK frequency and PLL\_CFG[0–3] settings must be chosen such that the resulting SYSCLK (bus) frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0–3] signal description in Section 1.8, "System Design Information," for valid PLL\_CFG[0–3] settings.

- 2. Rise and fall times for the SYSCLK input are measured from 0.4 V to 2.4 V.

- 3. Timing is guaranteed by design and characterization, and is not tested.

- 4. Cycle-to-cycle jitter, and is guaranteed by design.

- 5. Relock timing is guaranteed by design and characterization, and is not tested. PLL-relock time is the maximum amount of time required for PLL lock after a stable Vdd and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that HRESET must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

Figure 1 provides the SYSCLK input timing diagram.

VM = Midpoint Voltage (1.4 V)

Figure 1. SYSCLK Input Timing Diagram

### 1.4.2.2 Input AC Specifications

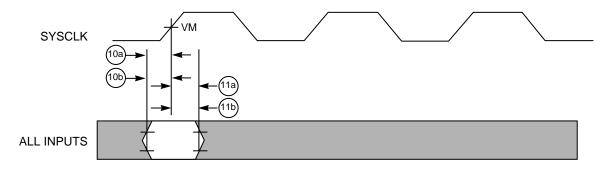

Table 7 provides the input AC timing specifications for the PID6 as defined in Figure 2 and Figure 3.

### **Table 7. Input AC Timing Specifications**

At recommended operating conditions. See Table 2

| Num | m Characteristic                                                                  |                       | 100 MHz |                       | 133.33 MHz |      | Notes       |

|-----|-----------------------------------------------------------------------------------|-----------------------|---------|-----------------------|------------|------|-------------|

| Num | Gilaracteristic                                                                   | Min                   | Max     | Min                   | Max        | Unit | Notes       |

| 10a | Address/data/transfer attribute inputs valid to SYSCLK (input setup)              | 3.0                   | _       | 3.0                   | _          | ns   | 2           |

| 10b | All other inputs valid to SYSCLK (input setup)                                    | 5.0                   | _       | 5.0                   | _          | ns   | 3           |

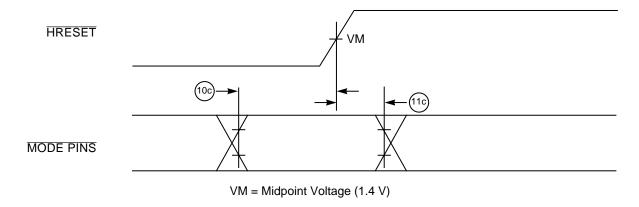

| 10c | Mode select inputs valid to HRESET (input setup) (for DRTRY, QACK and TLBISYNC)   | 8*t <sub>sysclk</sub> | _       | 8*t <sub>sysclk</sub> | _          | ns   | 4,5,<br>6,7 |

| 11a | SYSCLK to address/data/transfer attribute inputs invalid (input hold)             | 1.0                   | _       | 1.0                   | _          | ns   | 2           |

| 11b | SYSCLK to all other inputs invalid (input hold)                                   | 1.0                   | _       | 1.0                   | _          | ns   | 3           |

| 11c | HRESET to mode select inputs invalid (input hold) (for DRTRY, QACK, and TLBISYNC) | 0                     | _       | 0                     | _          | ns   | 4,6,7       |

- 1. All input specifications are measured from the TTL level (0.8 or 2.0 V) of the signal in question to the 1.4 V of the rising edge of the input SYSCLK (see Figure 2). Both input and output timings are measured at the pin.

- 2. Address/data/transfer attribute input signals are composed of the following—A[0–31], AP[0–3], TT[0–4], TC[0–1], TBST, TSIZ[0–2], GBL, DH[0–31], DL[0–31], DP[0–7].

- 3. All other input signals are composed of the following—TS, ABB, DBB, ARTRY, BG, AACK, DBG, DBWO, TA, DRTRY, TEA, DBDIS, HRESET, SRESET, INT, SMI, MCP, TBEN, QACK, TLBISYNC.

- 4. The setup and hold time is with respect to the rising edge of HRESET (see Figure 3).

- 5. t<sub>sysclk</sub> is the period of the external clock (SYSCLK) in nanoseconds.

- 6. These values are guaranteed by design, and are not tested.

- 7. This specification is for configuration mode select only. Also note that HRESET must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

Figure 2 provides the input timing diagram for the PID6.

VM = Midpoint Voltage (1.4 V)

Figure 2. Input Timing Diagram

Figure 3 provides the mode select input timing diagram for the PID6.

Figure 3. Mode Select Input Timing Diagram

### 1.4.2.3 Output AC Specifications

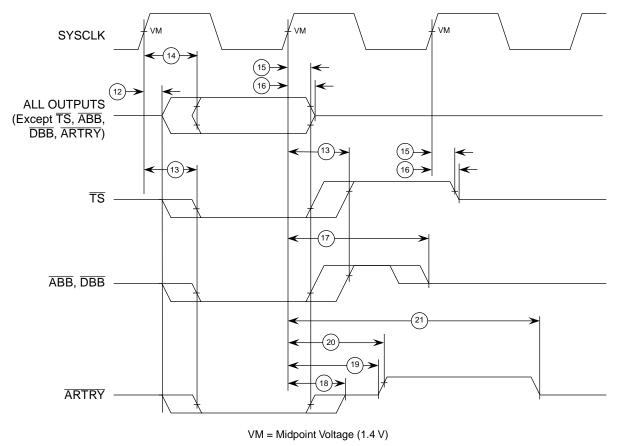

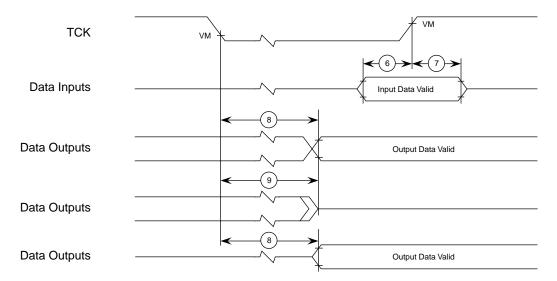

Table 8 provides the output AC timing specifications for the PID6 as defined in Figure 4.

### Table 8. Output AC Timing Specifications<sup>1</sup>

At recommended operating conditions. See Table 2.  $C_L = 50 \text{ pF}^2$

| Num | Characteristic                                                         | 100 MF                            | MHz 133.33 MHz |                                   | ИНz  | Unit        | Notes |

|-----|------------------------------------------------------------------------|-----------------------------------|----------------|-----------------------------------|------|-------------|-------|

| Num | Gilalacteristic                                                        | Min                               | Max            | Min                               | Max  | Oill        | Notes |

| 12  | SYSCLK to output driven (output enable time)                           | 1.0                               | _              | 1.0                               | _    | ns          |       |

| 13a | SYSCLK to output valid (5.5 V to 0.8 V—TS, ABB, ARTRY, DBB)            | _                                 | 11.0           | _                                 | 11.0 | ns          | 4     |

| 13b | SYSCLK to output valid (TS, ABB, ARTRY, DBB)                           | _                                 | 10.0           | _                                 | 10.0 | ns          | 6     |

| 14a | SYSCLK to output valid (5.5 V to 0.8 V—all except TS, ABB, ARTRY, DBB) | _                                 | 13.0           | _                                 | 13.0 | ns          | 4     |

| 14b | SYSCLK to output valid (all except TS, ABB, ARTRY, DBB)                | _                                 | 11.0           | _                                 | 11.0 | ns          | 6     |

| 15  | SYSCLK to output invalid (output hold)                                 | 1.5                               | _              | 1.5                               | _    | ns          | 3     |

| 16  | SYSCLK to output high impedance (all except ARTRY, ABB, DBB)           | _                                 | 9.5            | _                                 | 9.5  | ns          |       |

| 17  | SYSCLK to ABB, DBB, high impedance after precharge                     | _                                 | 1.2            | _                                 | 1.2  | t<br>sysclk | 5,7   |

| 18  | SYSCLK to ARTRY high impedance before precharge                        | _                                 | 9.0            | _                                 | 9.0  | ns          |       |

| 19  | SYSCLK to ARTRY precharge enable                                       | 0.2 *<br>t <sub>sysclk</sub> +1.0 | _              | 0.2 *<br>t <sub>sysclk</sub> +1.0 | _    | ns          | 3,5,8 |

| 20  | Maximum delay to ARTRY precharge                                       | _                                 | 1.2            | _                                 | 1.2  | t<br>sysclk | 5,8   |

| 21  | SYSCLK to ARTRY high impedance after precharge                         | _                                 | 2.25           | _                                 | 2.25 | t<br>sysclk | 5,8   |

- 1. All output specifications are measured from the 1.4 V of the rising edge of SYSCLK to the TTL level (0.8 V or 2.0 V) of the signal in question. Both input and output timings are measured at the pin (see Figure 4).

- 2. All maximum timing specifications assume  $C_L = 50$  pF.

- 3. This minimum parameter assumes  $C_L = 0$  pF.

- 4. SYSCLK to output valid (5.5 V to 0.8 V) includes the extra delay associated with discharging the external voltage from 5.5 V to 0.8 V instead of from Vdd to 0.8 V (5 V CMOS levels instead of 3.3 V CMOS levels).

- 5. t<sub>sysclk</sub> is the period of the external bus clock (SYSCLK) in nanoseconds (ns). The numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the parameter in question.

- 6. Output signal transitions from GND to 2.0 V or Vdd to 0.8 V.

- 7. Nominal precharge width for  $\overline{ABB}$  and  $\overline{DBB}$  is 0.5  $t_{sysclk}$ .

- 8. Nominal precharge width for  $\overline{ARTRY}$  is 1.0  $t_{sysclk}$ .

Figure 4 provides the output timing diagram for the PID6.

Figure 4. Output Timing Diagram

# 1.4.3 JTAG AC Timing Specifications

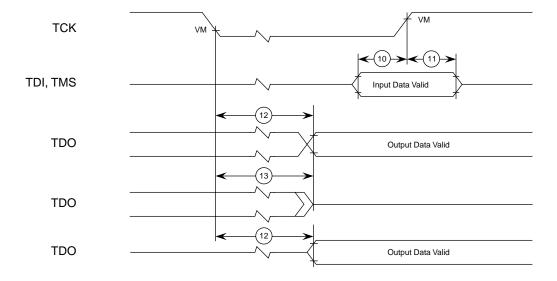

Table 9 provides the JTAG AC timing specifications as defined in Figure 5 through Figure 8.

Table 9. JTAG AC Timing Specifications (Independent of SYSCLK)

At recommended operating conditions. See Table 2.,  $C_L$  = 50 pF

| Num | Characteristic                          | Min  | Max | Unit | Notes |

|-----|-----------------------------------------|------|-----|------|-------|

|     | TCK frequency of operation              | 0    | 16  | MHz  |       |

| 1   | TCK cycle time                          | 62.5 | _   | ns   |       |

| 2   | TCK clock pulse width measured at 1.4 V | 25   | _   | ns   |       |

| 3   | TCK rise and fall times                 | 0    | 3   | ns   |       |

| 4   | TRST setup time to TCK rising edge      | 13   | _   | ns   | 1     |

| 5   | TRST assert time                        | 40   | _   | ns   |       |

| 6   | Boundary-scan input data setup time     | 6    | _   | ns   | 2     |

| 7   | Boundary-scan input data hold time      | 27   | _   | ns   | 2     |

| 8   | TCK to output data valid                | 4    | 25  | ns   | 3     |

| 9   | TCK to output high impedance            | 3    | 24  | ns   | 3     |

### Table 9. JTAG AC Timing Specifications (Independent of SYSCLK) (Continued)

At recommended operating conditions. See Table 2.,  $C_L = 50 \text{ pF}$

| Num | Characteristic            | Min | Max | Unit | Notes |

|-----|---------------------------|-----|-----|------|-------|

| 10  | TMS, TDI data setup time  | 0   | _   | ns   |       |

| 11  | TMS, TDI data hold time   | 25  | _   | ns   |       |

| 12  | TCK to TDO data valid     | 4   | 24  | ns   |       |

| 13  | TCK to TDO high impedance | 3   | 15  | ns   |       |

### Notes:

- 1. TRST is an asynchronous signal. The setup time is for test purposes only.

- 2. Non-test signal input timing with respect to TCK.

- 3. Non-test signal output timing with respect to TCK.

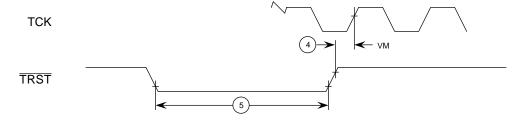

Figure 5 provides the JTAG clock input timing diagram.

Figure 5. JTAG Clock Input Timing Diagram

Figure 6 provides the  $\overline{TRST}$  timing diagram.

Figure 6. TRST Timing Diagram

Figure 7 provides the boundary-scan timing diagram.

Figure 7. Boundary-Scan Timing Diagram

Figure 8 provides the test access port timing diagram.

Figure 8. Test Access Port Timing Diagram

# 1.5 Pin Assignments

The following sections contain the pinout diagrams for the PID6. Note that the PID6 is offered in both ceramic quad flat pack (CQFP) and ceramic ball grid array (CBGA) packages.

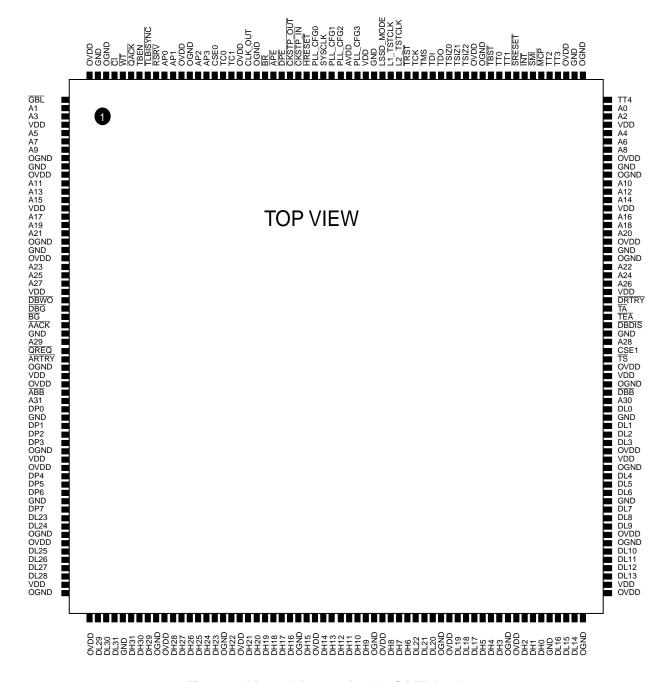

# 1.5.1 Pinout Diagram for the CQFP Package

Figure 9 contains the pinout diagram of the CQFP package for the PID6.

Figure 9. Pinout Diagram for the CQFP Package

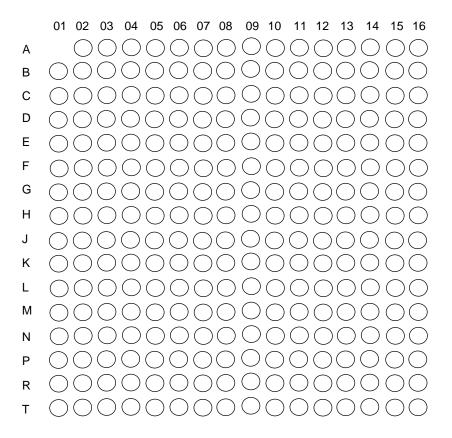

# 1.5.2 Pinout Diagram for the CBGA Package

Figure 10 (in part A) shows the pinout of the CBGA package as viewed from the top surface. Part B shows the side profile of the CBGA package to indicate the direction of the top surface view.

### Part A

Not to Scale

Figure 10. Pinout of the CBGA Package as Viewed from the Top Surface

# 1.6 Pinout Listings

The following sections contain the pinout listings for the PID6 CQFP and CBGA packages.

# 1.6.1 Pinout Listing for the CQFP Package

Table 10 provides the pinout listing for the PID6 CQFP package.

Table 10. Pinout Listing for the 240-pin CQFP Package

| Signal Name           | Pin Number                                                                                                                                            | Active | I/O    |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--|

| A[0-31]               | 179, 2, 178, 3, 176, 5, 175, 6, 174, 7, 170, 11, 169, 12, 168, 13, 166, 15, 165, 16, 164, 17, 160, 21, 159, 22, 158, 23, 151, 30, 144, 37             | High   | I/O    |  |

| AACK                  | 28                                                                                                                                                    | Low    | Input  |  |

| ABB                   | 36                                                                                                                                                    | Low    | I/O    |  |

| AP[0-3]               | 231, 230, 227, 226                                                                                                                                    | High   | I/O    |  |

| APE                   | 218                                                                                                                                                   | Low    | Output |  |

| ARTRY                 | 32                                                                                                                                                    | Low    | I/O    |  |

| AVDD                  | 209                                                                                                                                                   | High   | Input  |  |

| BG                    | 27                                                                                                                                                    | Low    | Input  |  |

| BR                    | 219                                                                                                                                                   | Low    | Output |  |

| CI                    | 237                                                                                                                                                   | Low    | Output |  |

| CLK_OUT               | 221                                                                                                                                                   | _      | Output |  |

| CKSTP_IN              | 215                                                                                                                                                   | Low    | Input  |  |

| CKSTP_OUT             | 216                                                                                                                                                   | Low    | Output |  |

| CSE[0-1] <sup>1</sup> | 225, 150                                                                                                                                              | High   | Output |  |

| DBB                   | 145                                                                                                                                                   | Low    | I/O    |  |

| DBDIS                 | 153                                                                                                                                                   | Low    | Input  |  |

| DBG                   | 26                                                                                                                                                    | Low    | Input  |  |

| DBWO                  | 25                                                                                                                                                    | Low    | Input  |  |

| DH[0-31]              | 115, 114, 113, 110, 109, 108, 99, 98, 97, 94, 93, 92, 91, 90, 89, 87, 85, 84, 83, 82, 81, 80, 78, 76, 75, 74, 73, 72, 71, 68, 67, 66                  | High   | I/O    |  |

| DL[0-31]              | 143, 141, 140, 139, 135, 134, 133, 131, 130, 129, 126, 125, 124, 123, 119, 118, 117, 107, 106, 105, 102, 101, 100, 51, 52, 55, 56, 57, 58, 62, 63, 64 | High   | I/O    |  |

| DP[0-7]               | 38, 40, 41, 42, 46, 47, 48, 50                                                                                                                        | High   | I/O    |  |

| DPE                   | 217                                                                                                                                                   | Low    | Output |  |

| DRTRY                 | 156                                                                                                                                                   | Low    | Input  |  |

| GBL                   | 1                                                                                                                                                     | Low    | I/O    |  |

| GND                   | 9, 19, 29, 39, 49, 65, 116, 132, 142, 152, 162, 172, 182, 206, 239                                                                                    | Low    | Input  |  |

| HRESET                | 214                                                                                                                                                   | Low    | Input  |  |

| ĪNT                   | 188                                                                                                                                                   | Low    | Input  |  |

Table 10. Pinout Listing for the 240-pin CQFP Package (Continued)

| Signal Name            | Pin Number                                                                                              | Active | I/O    |

|------------------------|---------------------------------------------------------------------------------------------------------|--------|--------|

| LSSD_MODE <sup>2</sup> | 205                                                                                                     | Low    | Input  |

| L1_TSTCLK <sup>2</sup> | 204                                                                                                     | _      | Input  |

| L2_TSTCLK <sup>2</sup> | 203                                                                                                     | _      | Input  |

| MCP                    | 186                                                                                                     | Low    | Input  |

| OGND                   | 8, 18, 33, 43, 53, 60, 69, 77, 86, 95, 103, 111, 120, 127, 136, 146, 161, 171, 181, 193, 220, 228, 238  | Low    | Input  |

| OVDD <sup>3</sup>      | 10, 20, 35, 45, 54, 61, 70, 79, 88, 96, 104, 112, 121, 128, 138, 148, 163, 173, 183, 194, 222, 229, 240 | High   | Input  |

| PLL_CFG[0-3]           | 213, 211, 210, 208                                                                                      | High   | Input  |

| QACK                   | 235                                                                                                     | Low    | Input  |

| QREQ                   | 31                                                                                                      | Low    | Output |

| RSRV                   | 232                                                                                                     | Low    | Output |

| SMI                    | 187                                                                                                     | Low    | Input  |

| SRESET                 | 189                                                                                                     | Low    | Input  |

| SYSCLK                 | 212                                                                                                     | _      | Input  |

| TA                     | 155                                                                                                     | Low    | Input  |

| TBEN                   | 234                                                                                                     | High   | Input  |

| TBST                   | 192                                                                                                     | Low    | I/O    |

| TC[0-1]                | 224, 223                                                                                                | High   | Output |

| TCK                    | 201                                                                                                     | _      | Input  |

| TDI                    | 199                                                                                                     | High   | Input  |

| TDO                    | 198                                                                                                     | High   | Output |

| TEA                    | 154                                                                                                     | Low    | Input  |

| TLBISYNC               | 233                                                                                                     | Low    | Input  |

| TMS                    | 200                                                                                                     | High   | Input  |

| TRST                   | 202                                                                                                     | Low    | Input  |

| TSIZ[0-2]              | 197, 196, 195                                                                                           | High   | I/O    |

| TS                     | 149                                                                                                     | Low    | I/O    |

| TT[0-4]                | 191, 190, 185, 184, 180                                                                                 | High   | I/O    |

| VDD <sup>3</sup>       | 4, 14, 24, 34, 44, 59, 122, 137, 147, 157, 167, 177, 207                                                | High   | Input  |

| WT                     | 236                                                                                                     | Low    | Output |

- 1. There are two CSE signals in the EC603e microprocessor—CSE0 and CSE1. The XATS signal in the PowerPC 603™ microprocessor is replaced by the CSE1 signal in the PID6.

- 2. These are test signals for factory use only and must be pulled up to OVdd for normal machine operation.

- 3. OVdd inputs supply power to the I/O drivers and Vdd inputs supply power to the processor core.

# 1.6.2 Pinout Listing for the CBGA Package

Table 11 provides the pinout listing for the PID6 CBGA package.

Table 11. Pinout Listing for the 255-pin CBGA Package

| Signal Name            | Pin Number                                                                                                                                                                                             | Active | I/O    |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| A[0-31]                | C16, E04, D13, F02, D14, G01, D15, E02, D16, D04, E13, GO2, E15, H01, E16, H02, F13, J01, F14, J02, F15, H03, F16, F04, G13, K01, G15, K02, H16, M01, J15, P01                                         | High   | I/O    |

| AACK                   | L02                                                                                                                                                                                                    | Low    | Input  |

| ABB                    | K04                                                                                                                                                                                                    | Low    | I/O    |

| AP[0-3]                | C01, B04, B03, B02                                                                                                                                                                                     | High   | I/O    |

| APE                    | A04                                                                                                                                                                                                    | Low    | Output |

| ARTRY                  | J04                                                                                                                                                                                                    | Low    | I/O    |

| AVDD                   | A10                                                                                                                                                                                                    | _      | 1-     |

| BG                     | L01                                                                                                                                                                                                    | Low    | Input  |

| BR                     | B06                                                                                                                                                                                                    | Low    | Output |

| CI                     | E01                                                                                                                                                                                                    | Low    | Output |

| CKSTP_IN               | D08                                                                                                                                                                                                    | Low    | Input  |

| CKSTP_OUT              | A06                                                                                                                                                                                                    | Low    | Output |

| CLK_OUT                | D07                                                                                                                                                                                                    | -      | Output |

| CSE[0-1]               | B01, B05                                                                                                                                                                                               | High   | Output |

| DBB                    | J14                                                                                                                                                                                                    | Low    | I/O    |

| DBG                    | N01                                                                                                                                                                                                    | Low    | Input  |

| DBDIS                  | H15                                                                                                                                                                                                    | Low    | Input  |

| DBWO                   | G04                                                                                                                                                                                                    | Low    | Input  |

| DH[0-31]               | P14, T16, R15, T15, R13, R12, P11, N11, R11,T12, T11, R10, P09, N09, T10, R09, T09, P08, N08, R08, T08, N07, R07, T07, P06, N06, R06, T06, R05, N05, T05, T04                                          | High   | I/O    |

| DL[0-31]               | K13, K15, K16, L16, L15, L13, L14, M16, M15, M13, N16, N15, N13, N14, P16, P15, R16, R14, T14, N10, P13, N12, T13, P03, N03, N04, R03, T01, T02, P04, T03, R04                                         | High   | I/O    |

| DP[0-7]                | M02, L03, N02, L04, R01, P02, M04, R02                                                                                                                                                                 | High   | I/O    |

| DPE                    | A05                                                                                                                                                                                                    | Low    | Output |

| DRTRY                  | G16                                                                                                                                                                                                    | Low    | Input  |

| GBL                    | F01                                                                                                                                                                                                    | Low    | I/O    |

| GND                    | C05, C12, E03, E06, E08, E09, E11, E14, F05, F07, F10, F12, G06, G08, G09, G11, H05, H07, H10, H12, J05, J07, J10, J12, K06, K08, K09, K11, L05, L07, L10, L12, M03, M06, M08, M09, M11, M14, P05, P12 | _      | _      |

| HRESET                 | A07                                                                                                                                                                                                    | Low    | Input  |

| INT                    | B15                                                                                                                                                                                                    | Low    | Input  |

| L1_TSTCLK <sup>1</sup> | D11                                                                                                                                                                                                    | -      | Input  |

Table 11. Pinout Listing for the 255-pin CBGA Package (Continued)

| Signal Name            | Pin Number                                                                                         | Active   | I/O    |

|------------------------|----------------------------------------------------------------------------------------------------|----------|--------|

| L2_TSTCLK <sup>1</sup> | D12                                                                                                | 1-       | Input  |

| LSSD_MODE 1            | B10                                                                                                | Low      | Input  |

| MCP                    | C13                                                                                                | Low      | Input  |

| NC                     | B07, B08, C03, C06, C08, D05, D06, F03, H04, J16                                                   | Low      | Input  |

| OVDD                   | C07, E05, E07, E10, E12, G03, G05, G12, G14, K03, K05, K12, K14, M05, M07, M10, M12, P07, P10      | _        | _      |

| PLL_CFG[0-3]           | A08, B09, A09, D09                                                                                 | High     | Input  |

| QACK                   | D03                                                                                                | Low      | Input  |

| QREQ                   | J03                                                                                                | Low      | Output |

| RSRV                   | D01                                                                                                | Low      | Output |

| SMI                    | A16                                                                                                | Low      | Input  |

| SRESET                 | B14                                                                                                | Low      | Input  |

| SYSCLK                 | C09                                                                                                | <u> </u> | Input  |

| TA                     | H14                                                                                                | Low      | Input  |

| TBEN                   | C02                                                                                                | High     | Input  |

| TBST                   | A14                                                                                                | Low      | I/O    |

| TC[0-1]                | A02, A03                                                                                           | High     | Output |

| TCK                    | C11                                                                                                | 1-       | Input  |

| TDI                    | A11                                                                                                | High     | Input  |

| TDO                    | A12                                                                                                | High     | Output |

| TEA                    | H13                                                                                                | Low      | Input  |

| TLBISYNC               | C04                                                                                                | Low      | Input  |

| TMS                    | B11                                                                                                | High     | Input  |

| TRST                   | C10                                                                                                | Low      | Input  |

| TS                     | J13                                                                                                | Low      | I/O    |

| TSIZ[0-2]              | A13, D10, B12                                                                                      | High     | I/O    |

| TT[0-4]                | B13, A15, B16, C14, C15                                                                            | High     | I/O    |

| WT                     | D02                                                                                                | Low      | Output |

| VDD <sup>2</sup>       | F06, F08, F09, F11, G07, G10, H06, H08, H09, H11, J06, J08, J09, J11, K07, K10, L06, L08, L09, L11 |          | _      |

- 1. These are test signals for factory use only and must be pulled up to OVdd for normal machine operation.

- 2. OVdd inputs supply power to the I/O drivers and Vdd inputs supply power to the processor core. Future members of the 603 family may use different OVdd and Vdd input levels.

# 1.7 Package Description

The following sections provide the package parameters and the mechanical dimensions for the PID6.

# 1.7.1 CQFP Package Description

The following sections provide the package parameters and mechanical dimensions for the Motorola CQFP package.

### 1.7.1.1 Package Parameters

The package parameters are as provided in the following list. The package type is 32 mm x 32 mm, 240-pin ceramic quad flat pack.

Package outline 32 mm x 32 mm

Interconnects 240

Pitch 0.5 mm

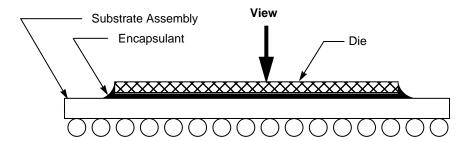

# 1.7.1.2 Mechanical Dimensions of the CQFP Package

Figure 11 shows the mechanical dimensions of the Motorola CQFP package.

Figure 11. Mechanical Dimensions of the Wire-Bond CQFP Package

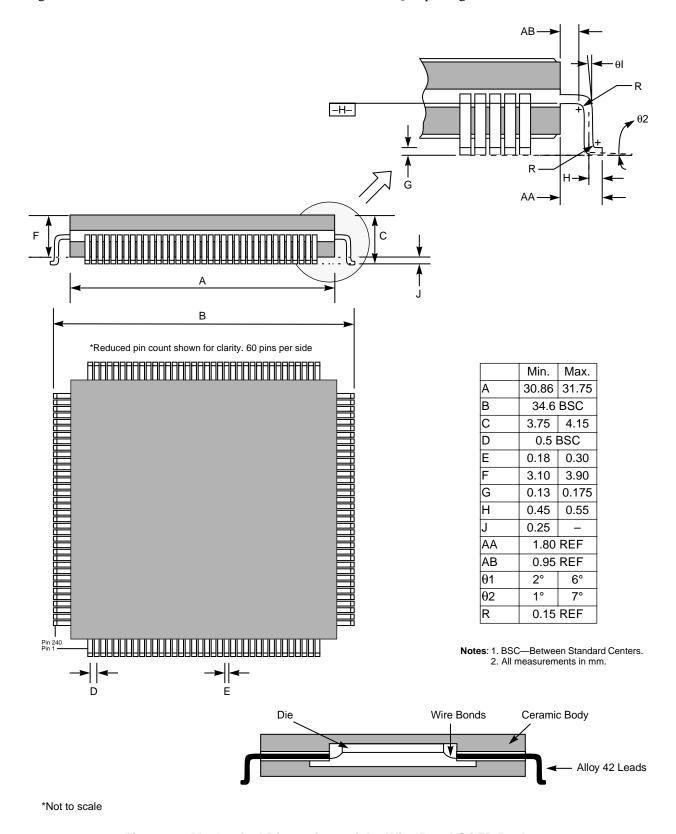

# 1.7.2 CBGA Package Description

The following sections provide the package parameters and mechanical dimensions for the CBGA package.

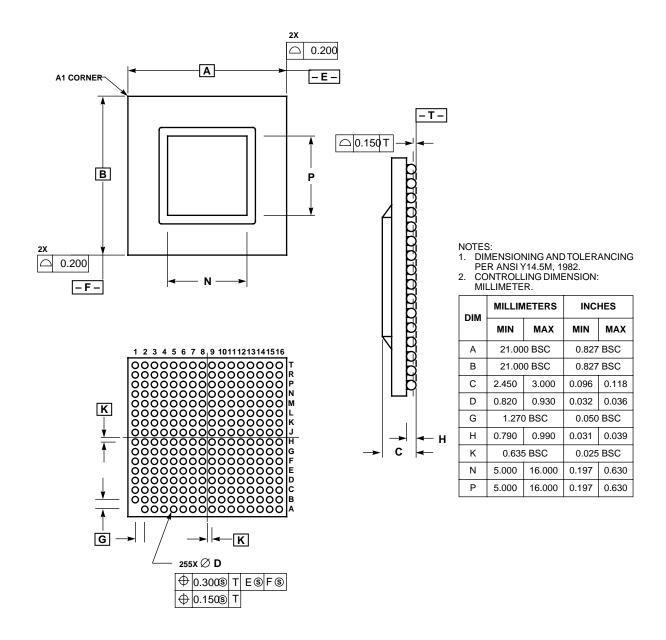

### 1.7.2.1 Package Parameters

The package parameters are as provided in the following list. The package type is 21 x 21 mm, 255-pin ceramic ball grid array (CBGA).

| Package outline       | 21 mm            |

|-----------------------|------------------|

| Interconnects         | 255              |

| Pitch                 | 1.27 mm          |

| Minimum module height | 2.45 mm          |

| Maximum module height | 3.00 mm          |

| Ball diameter         | 0.89 mm (35 mil) |

### 1.7.2.2 Mechanical Dimensions of the CBGA Package

Figure 12 provides the mechanical dimensions and bottom surface nomenclature of the CBGA package.

Figure 12. Mechanical Dimensions and Bottom Surface Nomenclature of the CBGA Package

# 1.8 System Design Information

This section provides electrical and thermal design recommendations for successful application of the PID6.

# 1.8.1 PLL Configuration

The PID6 PLL, shown in Table 12 for nominal frequencies, is configured by the PLL\_CFG[0-3] signals. For a given SYSCLK (bus) frequency, the PLL configuration signals set the internal CPU and VCO frequency of operation.

**Table 12. PLL Configuration**

|                  | CPU Frequency in MHz (VCO Frequency in MHz) |                               |                     |                  |                  |                     |                  |                  |                  |                     |

|------------------|---------------------------------------------|-------------------------------|---------------------|------------------|------------------|---------------------|------------------|------------------|------------------|---------------------|

| PLL_CFG<br>[0-3] | Bus-to-<br>Core<br>Multiplier               | Core-to-<br>VCO<br>Multiplier | Bus<br>16.67<br>MHz | Bus<br>20<br>MHz | Bus<br>25<br>MHz | Bus<br>33.33<br>MHz | Bus<br>40<br>MHz | Bus<br>50<br>MHz | Bus<br>60<br>MHz | Bus<br>66.67<br>MHz |

| 0000             | 1x                                          | 2x                            | _                   | _                | _                | _                   | _                | 50<br>(100)      | 60<br>(120)      | 66.67<br>(133)      |

| 0001             | 1x                                          | 4x                            | _                   | _                | _                | _                   | _                | 50<br>(200)      | 60<br>(240)      | 66.67<br>(266)      |

| 1100             | 1.5x                                        | 2x                            | _                   | _                | _                | 50<br>(100)         | 60<br>(120)      | 75<br>(150)      | 90<br>(180)      | 100<br>(200)        |

| 0100             | 2x                                          | 2x                            | _                   | _                | _                | 66.67<br>(133)      | 80<br>(160)      | 100<br>(200)     | 120<br>(240)     | 133.33<br>(266)     |

| 0101             | 2x                                          | 4x                            | _                   | _                | 50<br>(200)      | 66.67<br>(266)      | _                | _                | _                | _                   |

| 0110             | 2.5x                                        | 2x                            | _                   | 50<br>(100)      | 62.5<br>(125)    | 83.33<br>(166)      | 100<br>(200)     | 125<br>(250)     | _                | _                   |

| 1000             | 3x                                          | 2x                            | 50<br>(100)         | 60<br>(120)      | 75<br>(150)      | 100<br>(200)        | 120<br>(240)     | _                | _                | _                   |

| 1110             | 3.5x                                        | 2x                            | 58.4<br>(117)       | 70<br>(140)      | 87.5<br>(175)    | 116.67<br>(233)     | _                | _                | _                | _                   |

| 1010             | 4x                                          | 2x                            | 66.67<br>(133)      | 80<br>(160)      | 100<br>(200)     | 133.33<br>(266)     | _                | _                | _                | _                   |

| 0011             | PLL bypass                                  |                               |                     |                  |                  |                     |                  |                  |                  |                     |

| 1111             | Clock off                                   |                               |                     |                  |                  |                     |                  |                  |                  |                     |

- 1. PLL\_CFG[0-3] settings not listed are reserved.

- 2. The sample bus-to-core frequencies shown are for reference only. Some PLL configurations may select bus, core, or VCO frequencies which are not useful, not supported, or not tested for by the PID6; see Section 1.4.2.1, "Clock AC Specifications," for valid SYSCLK and VCO frequencies.

- 3. In PLL-bypass mode, the SYSCLK input signal clocks the internal processor directly, the PLL is disabled, and the bus mode is set for 1:1 mode operation. This mode is intended for factory use only.

Note: The AC timing specifications given in this document do not apply in PLL-bypass mode.

- 4. In clock-off mode, no clocking occurs inside the PID6 regardless of the SYSCLK input.

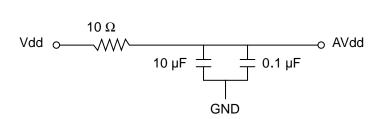

# 1.8.2 PLL Power Supply Filtering

The AVdd power signal is provided on the PID6 to provide power to the clock generation phase-locked loop. To ensure stability of the internal clock, the power supplied to the AVdd input signal should be filtered using a circuit similar to the one shown in Figure 13. The circuit should be placed as close as possible to the AVdd pin to ensure it filters out as much noise as possible.

Figure 13. PLL Power Supply Filter Circuit

## 1.8.3 Decoupling Recommendations

Due to the PID6's dynamic power management feature, large address and data buses, and high operating frequencies, the PID6 can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the PID6 system, and the PID6 itself requires a clean, tightly regulated source of power. Therefore, it is strongly recommended that the system designer place at least one decoupling capacitor at each Vdd and OVdd pin of the PID6. It is also recommended that these decoupling capacitors receive their power from separate Vdd, OVdd, and GND power planes in the PCB, utilizing short traces to minimize inductance.

These capacitors should vary in value from 220 pF to 10  $\mu$ F to provide both high- and low-frequency filtering, and should be placed as close as possible to their associated Vdd or OVdd pin. Suggested values for the Vdd pins—220 pF (ceramic), 0.01  $\mu$ F (ceramic), and 0.1  $\mu$ F (ceramic). Suggested values for the OVdd pins—0.01  $\mu$ F (ceramic), 0.1  $\mu$ F (ceramic), and 10  $\mu$ F (tantalum). Only SMT (surface mount technology) capacitors should be used to minimize lead inductance.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the Vdd and OVdd planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should also have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors— $100 \, \mu F$  (AVX TPS tantalum) or  $330 \, \mu F$  (AVX TPS tantalum).

### 1.8.4 Connection Recommendations

To ensure reliable operation, it is recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to Vdd. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

# 1.8.5 Pull-up Resistor Requirements

The PID6 requires high-resistive (weak:  $10 \text{ K}\Omega$ ) pull-up resistors on several control signals of the bus interface to maintain the control signals in the negated state after they have been actively negated and released by the PID6 or other bus master. These signals are— $\overline{TS}$ ,  $\overline{ABB}$ ,  $\overline{DBB}$ ,  $\overline{ARTRY}$ .

In addition, the PID6 has three open-drain style outputs that require pull-up resistors (weak or stronger:  $4.7 \text{ K}\Omega - 10 \text{ K}\Omega$ ) if they are used by the system. These signals are— $\overline{APE}$ ,  $\overline{DPE}$ , and  $\overline{CKSTP}$  OUT.

During inactive periods on the bus, the address and transfer attributes on the bus are not driven by any master and may float in the high-impedance state for relatively long periods of time. Since the PID6 must continually monitor these signals for snooping, this float condition may cause excessive power draw by the input receivers on the PID6. It is recommended that these signals be pulled up through weak (10 K $\Omega$ ) pull-up resistors or restored in some manner by the system. The snooped address and transfer attribute inputs are—A[0–31], AP[0–3], TT[0–4], TBST, TSIZ[0–2], and  $\overline{GBL}$ .

The data bus input receivers are normally turned off when no read operation is in progress and do not require pull-up resistors on the data bus.

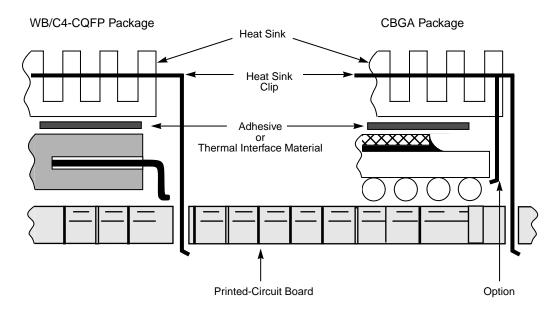

### 1.8.6 Thermal Management Information

This section provides thermal management information for the ceramic quad-flat package (CQFP) and the ceramic ball grid array (CBGA) package for air-cooled applications. Proper thermal control design is primarily dependent upon the system-level design—the heat sink, airflow and thermal interface material. To reduce the die-junction temperature, heat sinks may be attached to the package by several methods—adhesive, spring clip to holes in the printed-circuit board or package, and mounting clip and screw assembly (CBGA package); see Figure 14. This spring force should not exceed 5.5 pounds of force.

Figure 14. Package Exploded Cross-Sectional View with Several Heat Sink Options

The board designer can choose between several types of heat sinks to place on the PID6. There are several commercially-available heat sinks for the PID6 provided by the following vendors:

| Chip Coolers Inc. 333 Strawberry Field Rd. Warwick, RI 02887-6979                                  | 800-227-0254 (USA/Canada)<br>401-739-7600 |

|----------------------------------------------------------------------------------------------------|-------------------------------------------|

| International Electronic Research Corporation (IERC)<br>135 W. Magnolia Blvd.<br>Burbank, CA 91502 | 818-842-7277                              |

| Thermalloy<br>2021 W. Valley View Lane<br>P.O. Box 810839                                          | 214-243-4321                              |

Dallas, TX 75731

Wakefield Engineering 60 Audubon Rd. Wakefield, MA 01880

Aavid Engineering 603-528-3400 One Kool Path Laconia, NH 03247-0440

Ultimately, the final selection of an appropriate heat sink depends on many factors, such as thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly, and cost.

617-245-5900

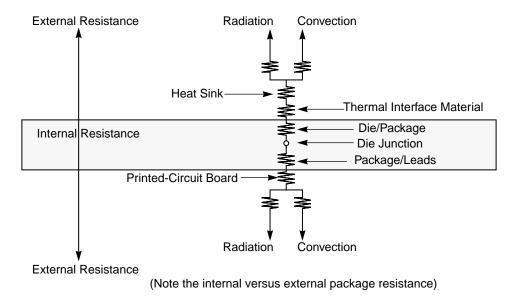

### 1.8.6.1 Internal Package Conduction Resistance

For this packaging technology the intrinsic thermal conduction resistance (shown in Table 3) versus the external thermal resistance paths are shown in Figure 15 for a package with an attached heat sink mounted to a printed-circuit board.

Figure 15. Package with Heat Sink Mounted to a Printed-Circuit Board

### 1.8.6.2 Adhesives and Thermal Interface Materials

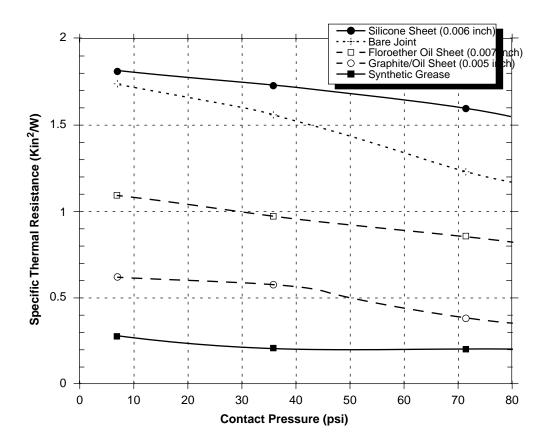

A thermal interface material is recommended at the package lid-to-heat sink interface to minimize the thermal contact resistance. For those applications where the heat sink is attached by spring clip mechanism, Figure 16 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, floroether oil), a bare joint, and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. The use of thermal grease significantly reduces the interface thermal resistance. That is, the bare joint results in a thermal resistance approximately seven times greater than the thermal grease joint.

Heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 14). This spring force should not exceed 5.5 pounds of force. Therefore, the synthetic grease offers the best thermal performance, considering the low interface pressure. Of course, the selection of any thermal interface material depends on many factors—thermal performance requirements, manufacturability, service temperature, dielectric properties, cost, etc.

Figure 16. Thermal Performance of Select Thermal Interface Material

The board designer can choose between several types of thermal interface. Heat sink adhesive materials should be selected based upon high conductivity, yet adequate mechanical strength to meet equipment shock/vibration requirements. There are several commercially-available thermal interfaces and adhesive materials provided by the following vendors:

| Dow-Corning Corporation Dow-Corning Electronic Materials PO Box 0997 Midland, MI 48686-0997 | 517-496-4000 |

|---------------------------------------------------------------------------------------------|--------------|

| Chomerics, Inc. 77 Dragon Court Woburn, MA 01888-4850                                       | 617-935-4850 |

| Thermagon Inc.<br>3256 West 25th Street<br>Cleveland, OH 44109-1668                         | 216-741-7659 |

| Loctite Corporation<br>1001 Trout Brook Crossing<br>Rocky Hill, CT 06067                    | 860-571-5100 |

| AI Technology (e.g. EG7655)<br>1425 Lower Ferry Rd<br>Trent, NJ 08618                       | 609-882-2332 |

### 1.8.6.3 Heat Sink Selection Example

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_i = T_a + T_r + (\theta_{ic} + \theta_{int} + \theta_{sa}) * P_d$$

#### Where:

T<sub>i</sub> is the die-junction temperature

T<sub>a</sub> is the inlet cabinet ambient temperature

T<sub>r</sub> is the air temperature rise within the computer cabinet

$\theta_{ic}$  is the junction-to-case thermal resistance

$\theta_{int}$  is the adhesive or interface material thermal resistance

$\theta_{sa}$  is the heat sink base-to-ambient thermal resistance

P<sub>d</sub> is the power consumed by the device

During operation the die-junction temperatures  $(T_j)$  should be maintained less than the value specified in Table 2. The temperature of the air cooling the component greatly depends upon the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_a)$  may range from 30 to 40 °C. The air temperature rise within a cabinet  $(T_r)$  may be in the range of 5 to 10 °C. The thermal resistance of the thermal interface material  $(\theta_{int})$  is typically about 1 °C/W. Assuming a  $T_a$  of 30 °C, a  $T_r$  of 5 °C, a CQFP package  $\theta_{jc} = 2.2$ , and a power consumption  $(P_d)$  of 4.5 watts, the following expression for  $T_i$  is obtained:

Die-junction temperature:

$$T_j = 30 \, ^{\circ}\text{C} + 5 \, ^{\circ}\text{C} + (2.2 \, ^{\circ}\text{C/W} + 1.0 \, ^{\circ}\text{C/W} + R_{sa}) * 4.5 \, \text{W}$$

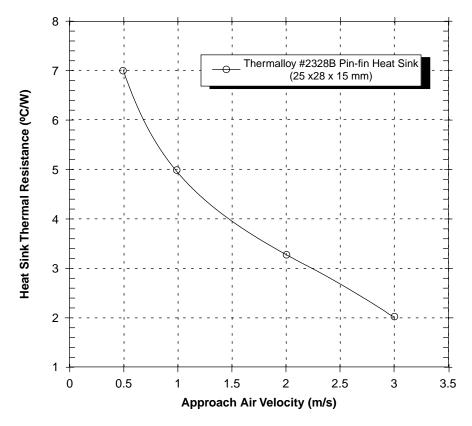

For a Thermalloy heat sink #2328B, the heat sink-to-ambient thermal resistance ( $R_{sa}$ ) versus airflow velocity is shown in Figure 17.

Figure 17. Thermalloy #2328B Heat Sink-to-Ambient Thermal Resistance Versus Airflow Velocity

Assuming an air velocity of 0.5 m/s, we have an effective R<sub>sa</sub> of 7 °C/W, thus

$$T_i = 30^{\circ}C + 5^{\circ}C + (2.2^{\circ}C/W + 1.0^{\circ}C/W + 7^{\circ}C/W) * 4.5 W,$$

resulting in a die-junction temperature of approximately 81 °C which is well within the maximum operating temperature of the component.

Other heat sinks offered by Chip Coolers, IERC, Thermalloy, Wakefield Engineering, and Aavid Engineering offer different heat sink-to-ambient thermal resistances, and may or may not need air flow.

Though the die junction-to-ambient and the heat sink-to-ambient thermal resistances are a common figure-of-merit used for comparing the thermal performance of various microelectronic packaging technologies, one should exercise caution when only using this metric in determining thermal management because no single parameter can adequately describe three-dimensional heat flow. The final die-junction operating temperature, is not only a function of the component-level thermal resistance, but the system-level design and its operating conditions. In addition to the component's power consumption, a number of factors affect the final operating die-junction temperature—airflow, board population (local heat flux of adjacent components), heat sink efficiency, heat sink attach, heat sink placement, next-level interconnect technology, system air temperature rise, altitude, etc.

Due to the complexity and the many variations of system-level boundary conditions for today's microelectronic equipment, the combined effects of the heat transfer mechanisms (radiation, convection and conduction) may vary widely. For these reasons, we recommend using conjugate heat transfer models for the board, as well as, system-level designs. To expedite system-level thermal analysis, several "compact" thermal-package models are available within FLOTHERM®. These are available upon request.

# 1.9 Document Revision History

**Table 13. Document Revision History**

# 1.10 Ordering Information

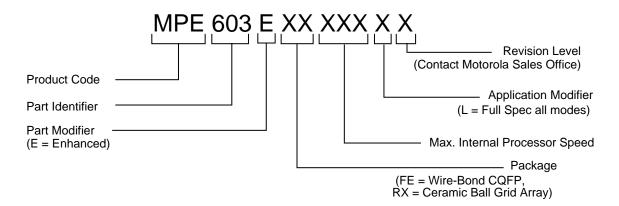

This section provides the part numbering nomenclature for the PID6. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Motorola sales office.

Figure 18 provides the Motorola part numbering nomenclature for the PID6. In addition to the processor frequency, the part numbering scheme also consists of a part modifier and application modifier. The part modifier indicates any enhancement(s) in the part from the original production design. The bus divider may specify special bus frequencies or application conditions. Each part number also contains a revision code. This refers to the die mask revision number and is specified in the part numbering scheme for identification purposes only.

Figure 18. Motorola Part Number Key

EC603e and Mfax are trademarks of Motorola, Inc.

The PowerPC name, the PowerPC logotype, and PowerPC 603e are trademarks of International Business Machines Corporation used by Motorola under license from International Business Machines Corporation.

FLOTHERM is a registered trademark of Flomerics Ltd., UK.

Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. There are no express or implied copyright licenses granted hereunder to design or fabricate PowerPC integrated circuits or integrated circuits based on the information in this

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages." Typical parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, and reasonable attorney fees arising out of, directly or indirectly. any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and (M) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Motorola Literature Distribution Centers:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 5405; Denver, Colorado 80217; Tel.: 1-800-441-2447 or 1-303-675-2140; World Wide Web Address: http://ldc.nmd.com/

JAPAN: Nippon Motorola Ltd SPD, Strategic Planning Office 4-32-1, Nishi-Gotanda Shinagawa-ku, Tokyo 141, Japan Tel.: 81-3-5487-8488

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd Silicon Harbour Centre 2, Dai King Street Tai Po Industrial Estate Tai Po, New Territories, Hong Kong

Mfax™: RMFAX0@email.sps.mot.com; TOUCHTONE 1-602-244-6609; US & Canada ONLY (800) 774-1848; World Wide Web Address: http://sps.motorola.com/mfax

INTERNET: http://motorola.com/sps

Technical Information: Motorola Inc. SPS Customer Support Center 1-800-521-6274; electronic mail address: crc@wmkmail.sps.mot.com.