#### **DATA-SHEET**

April 2004

#### DESCRIPTION

The TDK Semiconductor Corporation 73S1121F is a CMOS single chip dual ISO-7816 smart-card terminal micro-controller that implements all the functions required to build a low-cost dual smart-card terminal with a USB interface, suitable for various applications including EMVco compliant payment terminals. Its enhanced set of features supports several configurations allowing low component count and a fast design cycle. Based on an 80C52 core, it incorporates communication and man-machine interfaces. The TDK 73S1121F device is applicable to either portable or host-connected applications. Embedded Flash memory makes the TDK 73S1121F a complete system-on-chip suitable for both development and production phases.

This data-sheet presents the package and pin description, as well as the electrical features that are unique to the TDK 73S1121F. It also presents a brief description of the architecture and of its embedded functions.

Refer to the 73S11xxF Hardware User's Guide for more detailed information about the microcontroller architecture, description of the registers, description of the different blocks that are common to the TDK 73S11xxF smart card terminal controller family.

Also refer to the TDK 73S11xxF Software User's Guide for a complete description of the Application Programming Interface (API).

### **APPLICATIONS**

- PIN-pads Smart Card Readers

- Computer-connected Terminal for:

- → PATM

- → E-commerce

- → Home-Banking

- → E-purse

- → Logical Access

- Point of Sales & Transaction Terminals

- Standalone or connected Applications

- General Purpose Smart Card readers

#### **ADVANTAGES**

- True System-on-Chip solution, with built-in communication interfaces and peripherals

- Compact solution, that requires only a few external components

- Embedded 64kB Flash and 5kB RAM are the largest memory size among 8-bit smart card reader controllers in the industry

- Low-cost solution for portable and hostconnected terminals

- Software API (Application Programming Interface) includes the ready-to-use protocol layers for asynchronous cards and USB

- → Faster development time

- → Time-to-Market

#### **DATA-SHEET**

#### **FEATURES**

#### 80C52 core:

- 12 clock-cycle / instruction

- CPU clocked up to 24MHz (with a 12MHz crystal)

- 16-bit PC (64kB program linear memory address space)

#### Memory:

- 64kB internal Flash (Program Memory)

- 128 Bytes Flash Info Memory Block

- Flash memory guaranteed for 10,000 erase-write cycles

- 1kB IRAM (internal RAM for registers) + 4kB internal XRAM (User Data Memory)

- Interface for external program / data memory

- Boot-ROM loader program allows both In-System-Programming and In-Application-Programming of the embedded flash (ISP and IAP modes)

- Flash PROM-programming mode

- ISP, PROM programming modes and external memory interface can be permanently disabled by protection fuses

#### Oscillators:

- Single low-cost 12MHz crystal

- Optional low-cost 32kHz crystal (with internal counter for RTC support)

- An Internal PLL provides all the necessary clocks to each block of the system

#### Interrupts:

- Standard 80C52 2-priority level structure

- 8 different sources of interrupt

#### **Power Down Modes:**

- 2 standard 80C52 Power Down and IDLE modes

- 1 low-speed mode (CPU run at 32kHz)

#### Timers:

- (3) Standard 80C52 timers T0, T1 and T2

- (1) 16-bit timer that can generate RTC interrupts from the 32KHz oscillator

#### (2) Built-in ISO-7816 card interfaces:

- (2) Independent step-up converters generate VCC for the card (3V or 5V)

- Compliant with EMV 4.0 (EMV2000)

- Activation/Deactivation sequencers

- Auxiliary I/O lines (C4-C8 signals)

- 6kV ESD protection on all interface pins

#### Communication with smart cards:

- ISO-7816 UART 9600 to 115kbps (with 12MHz crystal) for protocols T=0, T=1

- 2-Byte FIFO for transmit and receive

- Hardware support to manage additional external card interfaces

#### Communication interfaces:

- Full-duplex serial interface (1200 to 115kbps UART)

- USB 1.1 Full Speed 12Mbps Interface (backward compatible with USB 2.0), PC/SC compliant with 4 Endpoints:

- Control (16B FIFO)

- Interrupt IN (32B FIFO)

- Bulk IN (128B FIFO)

- Bulk OUT (128B FIFO)

#### Man-Machine Interface and I/Os:

- 5x6 Keyboard (hardware scanning, debouching and scrambling)

- (7) Dedicated LCD I/Os (Control of any external HD44780 standard LCD driver) – Can be also used as standard I/Os

- (8) User I/Os

- (4) GPIOs (with separate voltage reference input)

#### **Voltage Detection:**

- (3) Analog Inputs (Voltage detection range: 0.2V to 2.5V)

- (1) 2.5V Voltage reference available on an output pin.

#### **Operating Voltage:**

2.7V to 3.6V (3V to 3.6V when USB is in use)

#### **Operating Temperature:**

0°C to 85°C

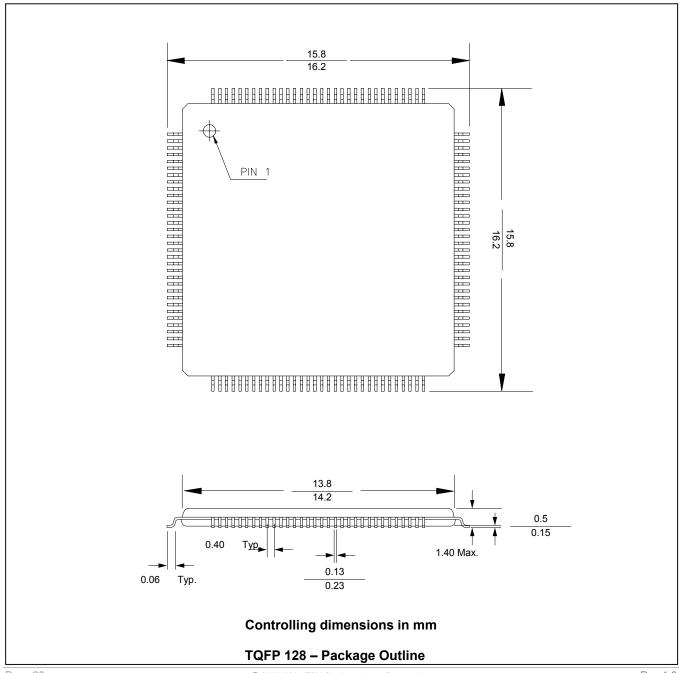

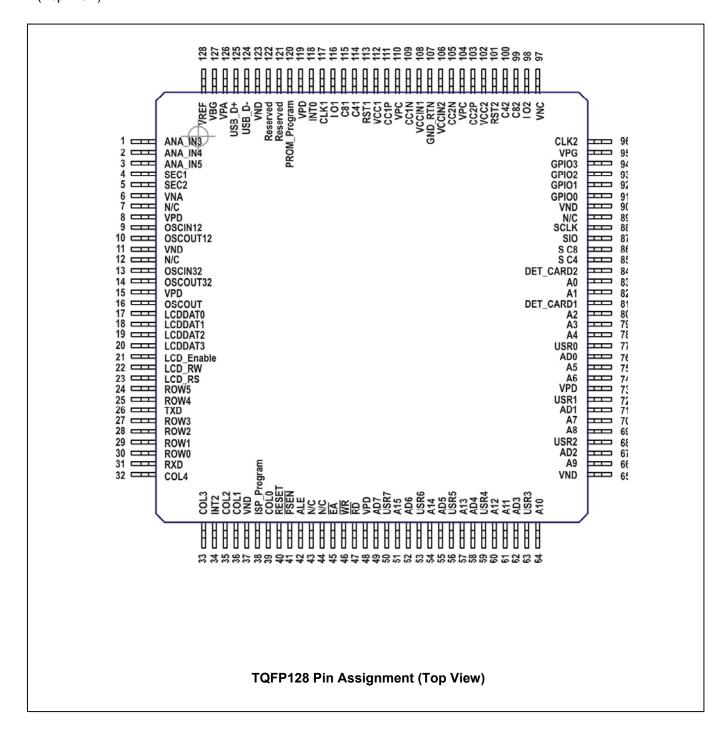

#### Package:

- 128 pin TQFP

- Bare Die

#### Software:

- Two-level Application Programming Interface (ANSI C-language libraries)

- USB and T=0 T=1 smart card protocol layers

- PIN Management functions compatible with CCID requirements

#### **DATA-SHEET**

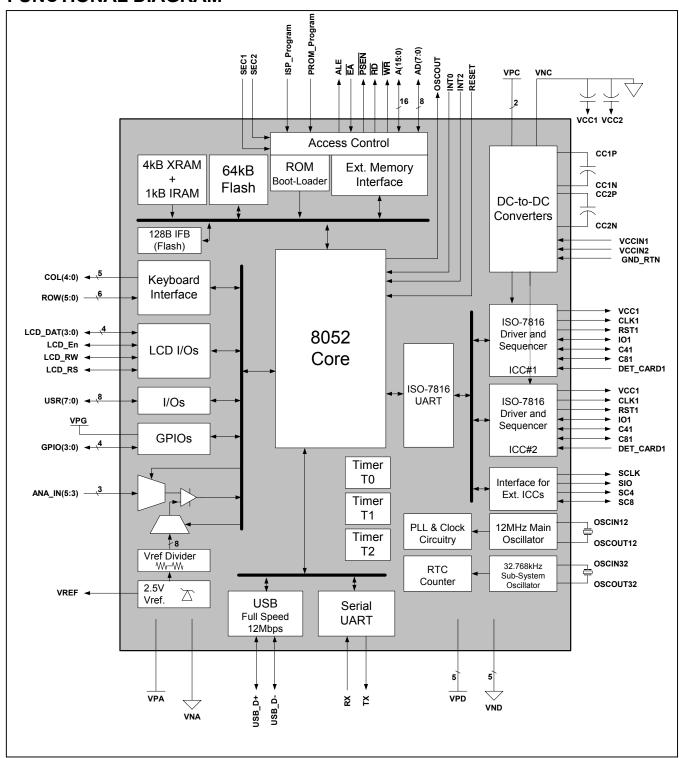

#### **FUNCTIONAL DIAGRAM**

#### **DATA-SHEET**

#### Microcontroller

The 73S1121F core is an 8-bit 80C52 micro-controller, with embedded 5kB of RAM (data memory) and 64kB of flash (program memory). An additional Information Block Flash cell (128B IFB) is available for storage of device ID, serial number, firmware version etc

An embedded ROM boot-loader allows downloading of the flash memory (either program or IFB) through the serial port. This programming mode can be forced externally (In-System-Programming = ISP mode) or also can be called by the application (In-Application-Programming = IAP mode) through the Application Programming Interface. The 73S1121F flash memory can also be programmed with a parallel PROM programmer. An interface for external memory is provided to allow extension of the RAM up to 64kB total (addition of 59kB external). Extension of the total program memory above the 64kB can be implemented by adding bank-switched external memory pages, the firmware being responsible for management of the banks. Security fuses allows the user to permanently disable, either the ISP mode, the PROM programming mode, the interface for external memory, or any combination of the 3. It allows the 73S1121F, once programmed with an application, to run independently without possibility from the external world to access the internal memory, or to re-download a non-authorized application, or to run an external program.

The 73S1121F has a main oscillator that requires a 12MHz crystal. Internal clock circuitry generates clock signals to the different blocks and to the CPU (that can be clocked at 6, 12 or 24MHz). An optional 2nd crystal (32,768Hz) can be connected to a sub-system oscillator. It is associated with a 16-bit counter that can generate real-time interrupts to the core, every 0.5s, 1s or 2s. The firmware application is then responsible to service this interrupt and to update a real time/date counter for applications that require it. This sub-system clock can also be used as a CPU clock for low-speed operation as an additional power saving mode. Keypad scanning can also operate from a 1kHz clock generated from the sub-system clock.

The 73S1121F has the standard 8052 2-priority level interrupt structure, with 8 different interrupt sources: 2 external interrupts (pins INT2 and INT0), 3 timer interrupts, 1 serial/USB interrupt, 1 smart-card interrupt and a shared interrupt (keypad, GPIO, RTC counter and analog comparator inputs).

The 73S1121F incorporates 3 timers, T0, T1 and T2 that can be clocked internally or externally by the respective input signals on the pins USR0, USR1 and USR2.

Standard 8052 Power Down mode and IDLE mode are supported for power saving modes. The clock for each block, as well as the analog circuitry (analog input, voltage reference and USB transceiver) and the DC-to-DC converters (VCC generators for the card) can be independently enabled or disabled by firmware to optimize power consumption.

Management of the embedded card interfaces, peripherals and communication capabilities are controlled by means of dedicated registers in RAM. Management of the interrupts, of the power saving modes and of the clock circuitry is also controlled through registers.

#### **DATA-SHEET**

#### ISO-7816 Interfaces and UART

The feature set of the TDK 73S1121F includes two built-in smart-card interfaces, controlled by an ISO-7816 compliant sequencer. Each built-in smart card interface has its own DC-DC converter, able to generate the card power supply, VCC=3V or 5V. The sequencer handles the activation / deactivation of the card signals. Each card interface includes an input for the card presence switch (programmable polarity) and auxiliary I/O lines for C4 / C8 signals. A hardware ISO-7816 UART with a dedicated FIFO allows easy implementation of asynchronous card protocols T=0 and T=1. This UART can be bypassed to allow a firmware UART to handle other protocols such as synchronous card protocols. Control and use of the ISO-7816 UART is widely and easily configurable with dedicated registers located in XRAM. A 4-line interface enables the 73S1121F to control additional external smart card (ICC) interfaces, typically for multiple-SAM configurations. The ISO-7816 UART can be shared between all the smart card interfaces (internal and external).

### Communication, Man-Machine Interface and I/Os

The 73S1121F has a full-speed (12Mbps) USB slave interface with 4 endpoints for implementation of computerconnected terminals. A standard 8052 serial UART allows the 73S1121F to communicate with any host or peripheral on a serial link, at a data transmission rate from 1200 to 115kbps. Communication with a computer through RS232 can be easily implemented only using an external level shifter.

Keyboard implementation is supported with a built-in 5x6 keyboard interface with hardware scanning and debouching. It also features a scrambling capability (change of the scanning order).

7 I/O lines are dedicated to control an external standard LCD driver, allowing a wide choice of LCDs to be controlled by the 73S1121F, such as 7-wire, Hitachi-type HD44780.

Additional input/outputs feature 8 user I/Os, 4 general purpose I/Os (GPIOs, that are compatible with any interfacing voltage up to 5.5V), and 3 analog inputs for voltage detection (for battery monitoring or any DC voltage comparison). Each of the analog inputs can be multiplexed to a comparator pre-set to a threshold voltage adjustable between 0.2V to 2.5V (8 possible levels).

## DATA-SHEET

## **PIN DESCRIPTION**

| Pin Name | Pin<br>Number<br>128 TQFP | Total<br>Pins | Туре | Description                                                                                               |  |  |  |

|----------|---------------------------|---------------|------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| CC1P     | 111                       | 1             | I/O  | Card interface 1 - Charge-pump capacitor positive node $(0.68\mu F \text{ Low ESR} < 100 \text{m}\Omega)$ |  |  |  |

| CC1N     | 109                       | 1             | I/O  | Charge-pump capacitor 1 Negative Node                                                                     |  |  |  |

| CC2P     | 103                       | 1             | I/O  | Card interface 2 - Charge-pump capacitor positive node $(0.68\mu F \text{ Low ESR} < 100 \text{m}\Omega)$ |  |  |  |

| CC2N     | 105                       | 1             | I/O  | Charge-pump capacitor 2 Negative Node                                                                     |  |  |  |

| COL (4)  | 32                        |               |      |                                                                                                           |  |  |  |

| COL (3)  | 33                        |               |      |                                                                                                           |  |  |  |

| COL (2)  | 35                        | 5             | 0    | Keypad column drive lines                                                                                 |  |  |  |

| COL (1)  | 36                        |               |      |                                                                                                           |  |  |  |

| COL (0)  | 39                        |               |      |                                                                                                           |  |  |  |

| ROW (5)  | 24                        |               |      |                                                                                                           |  |  |  |

| ROW (4)  | 25                        |               |      |                                                                                                           |  |  |  |

| ROW (3)  | 27                        | C             |      | Keypad row sense lines                                                                                    |  |  |  |

| ROW (2)  | 28                        | 6             | I    |                                                                                                           |  |  |  |

| ROW (1)  | 29                        |               |      | Transmit data - Serial output port from the 73S1121F serial UART                                          |  |  |  |

| ROW (0)  | 30                        |               |      |                                                                                                           |  |  |  |

| TXD      | 26                        | 1             | 0    | Transmit data - Serial output port from the 73S1121F serial UART                                          |  |  |  |

| RXD      | 31                        | 1             | I    | Receive data - Serial input port to the 73S1121F serial UART                                              |  |  |  |

| USR (7)  | 50                        |               |      |                                                                                                           |  |  |  |

| USR (6)  | 53                        |               |      |                                                                                                           |  |  |  |

| USR (5)  | 56                        |               |      |                                                                                                           |  |  |  |

| USR (4)  | 59                        | 8             | I/O  |                                                                                                           |  |  |  |

| USR (3)  | 63                        |               |      |                                                                                                           |  |  |  |

| USR (2)  | 68                        |               |      |                                                                                                           |  |  |  |

| USR (1)  | 72                        |               |      |                                                                                                           |  |  |  |

| USR (0)  | 77                        |               |      |                                                                                                           |  |  |  |

| INT2     | 34                        | 1             | I    | External interrupt input pin                                                                              |  |  |  |

| INT0     | 118                       | 1             | I    | External interrupt input pin                                                                              |  |  |  |

| USB_D-   | 124                       | 1             | I/O  | USB D-                                                                                                    |  |  |  |

| USB_D+   | 125                       | 1             | I/O  | USB D+                                                                                                    |  |  |  |

| GPIO (3) | 94                        |               |      |                                                                                                           |  |  |  |

| GPIO (2) | 93                        |               | 1/0  |                                                                                                           |  |  |  |

| GPIO (1) | 92                        | 4             | I/O  |                                                                                                           |  |  |  |

| GPIO (0) | 91                        |               |      |                                                                                                           |  |  |  |

| Pin Name                   | Pin<br>Number<br>128 TQFP | Total<br>Pins | Туре | Description                                                                                                                                                                                                                                                    |  |  |  |  |

|----------------------------|---------------------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LCDDAT (3)                 | 20                        |               |      |                                                                                                                                                                                                                                                                |  |  |  |  |

| LCDDAT (2)                 | 19                        | 4             | I/O  | LCD driver dedicated I/O lines - Data pins.                                                                                                                                                                                                                    |  |  |  |  |

| LCDDAT (1)                 | 18                        | 4             | 1/0  | Can be used as standard I/Os                                                                                                                                                                                                                                   |  |  |  |  |

| LCDDAT (0)                 | 17                        |               |      |                                                                                                                                                                                                                                                                |  |  |  |  |

| LCD_Enable<br>(LCDDAT (4)) | 21                        | 1             | I/O  | LCD driver dedicated I/O line: LCD Enable. Can be used as standard I/O                                                                                                                                                                                         |  |  |  |  |

| LCD_RW<br>(LCDDAT (5))     | 22                        | 1             | I/O  | LCD driver dedicated I/O line: LCD Read/Write. Can be used as standard I/O                                                                                                                                                                                     |  |  |  |  |

| LCD_RS<br>(LCDDAT (6))     | 23                        | 1             | I/O  | LCD driver dedicated I/O line: LCD Register Select. Can be used as standard I/O                                                                                                                                                                                |  |  |  |  |

| ANA_IN (5)                 | 3                         |               |      |                                                                                                                                                                                                                                                                |  |  |  |  |

| ANA_IN (4)                 | 2                         | 3             | I    | Analog Inputs - (Voltage detection inputs 0.2V to 2.5V $\pm 3\%$ )                                                                                                                                                                                             |  |  |  |  |

| ANA_IN (3)                 | 1                         |               |      | Voltage reference. $2.5V\pm7\%$ . Decouple with $0.1\mu F$ capacitor to VNA.                                                                                                                                                                                   |  |  |  |  |

| VREF                       | 128                       | 1             | 0    | Voltage reference. $2.5V \pm 7\%$ . Decouple with $0.1\mu F$ capacitor to VNA                                                                                                                                                                                  |  |  |  |  |

| VBG                        | 127                       | 1             | 0    | Bandgap output - internal use. To be decoupled with 0.1μF capacitor to VNA. Nothing else should be connected to VBG                                                                                                                                            |  |  |  |  |

| RESET                      | 40                        | 1             | I    | 73S1121F Reset. Active high                                                                                                                                                                                                                                    |  |  |  |  |

| ISP_Program                | 38                        | 1             | ı    | Forces internal Flash programming in ISP mode at reset. Active High. Inactive Low, suitable for normal operation. Internal pull-down allows NC for normal operation                                                                                            |  |  |  |  |

| N/C                        | 7; 12; 43;<br>44; 89;     | 5             | -    | Not Connected                                                                                                                                                                                                                                                  |  |  |  |  |

| Reserved                   | 121; 122                  | 2             | -    | To be connected to VND                                                                                                                                                                                                                                         |  |  |  |  |

| PROM_Program               | 120                       | 1             | I    | Forces internal Flash programming in PROM parallel mode at reset.  Active High. Internal pull-down allows NC for normal operation                                                                                                                              |  |  |  |  |

| SEC1                       | 4                         |               |      | Digital security inputs that control the internal protection fuses. Active High. Internal pull-down allows NC for normal operation 00 – Inactive.  01- Permanently deactivates both PROM programming mode, TDK testing modes.                                  |  |  |  |  |

| SEC2                       | 5                         | 2             | I    | 10 – Permanently deactivates the external interface of address and data signals to the processor 11- Permanently deactivates the ISP programming mode. Any combination of the 3 protection modes can be achieved by applying the proper sequence on these pins |  |  |  |  |

## 73S1121F

# EMV Smart-Card Terminal Controller with Built-in Dual ISO-7816 Interface and USB

| Pin Name | Pin<br>Number<br>128 TQFP | Total<br>Pins | Туре   | Description                                                                                                                                                                    |  |  |  |

|----------|---------------------------|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VND      | 11; 37; 65;<br>90; 123    | 5             | GND    | Digital ground                                                                                                                                                                 |  |  |  |

| VPD      | 8; 15; 48;<br>73; 119     | 5             | Supply | Digital power supply. 2.7V - 3.6V Must be at least equal to 3V when using the USB interface. Each pin to be decoupled to VND with a $0.1\mu F$ capacitor.                      |  |  |  |

| VNA      | 6                         | 1             | GND    | Analog ground                                                                                                                                                                  |  |  |  |

| VPA      | 126                       | 1             | Supply | Analog power supply. 2.7V - 3.6V To be decoupled to VNA with a 0.1μF capacitor.                                                                                                |  |  |  |

| VPG      | 95                        | 1             | Supply | GPIO power supply: 2.7V - 5.5V. Only connect if GPIO used. VPG is the reference voltage for interfacing GPIOs with external devices operating on a voltage different than VPD. |  |  |  |

| VPC      | 104; 110                  | 2             | Supply | DC/DC Step-up Converter power supply (2.7 - 3.6V). Each pin to be decoupled to VNC with one $0.1\mu F$ and one $10\mu F$ capacitor.                                            |  |  |  |

| VNC      | 97                        | 1             | GND    | DC/DC Step-up Converter ground                                                                                                                                                 |  |  |  |

| OSCIN32  | 13                        | 1             | I      | 32.768KHz crystal input. Can drive clock in and leave OSCOUT32 unconnected                                                                                                     |  |  |  |

| OSCOUT32 | 14                        | 1             | 0      | 32.768KHz crystal output. Leave unconnected if not using a crystal                                                                                                             |  |  |  |

| OSCIN12  | 9                         | 1             | I      | 12MHz crystal input. Can drive clock in and leave OSCOUT12 unconnected                                                                                                         |  |  |  |

| OSCOUT12 | 10                        | 1             | 0      | 12MHz crystal output. Leave unconnected if not using a crystal                                                                                                                 |  |  |  |

| OSCOUT   | 16                        | 1             | 0      | CPU clock output pin                                                                                                                                                           |  |  |  |

| Pin Name | Pin<br>Number<br>128 TQFP | Total<br>Pins | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|----------|---------------------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ALE      | 42                        | 1             | 0    | Address latch enable. A pulse for latching the low byte of the address on the AD pins during access to external memory. ALE is internally used to demultiplex the low address byte A(7:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PSEN     | 41                        | 1             | 0    | on the AD pins during access to external memory. ALE is internally used to demultiplex the low address byte A(7:0)  Program store enable. This output goes low during a fetch from program external memory. Active low  External Access enable. When this pin is low, the core fetches code from external program memory only  Read. A strobe, active during an external read. To be used as a read enable for external data memory devices. Active low.  Write. A strobe, active during an external write. To be used as a read enable for external data memory devices. Active low  Multiplexed Low-byte Address bus / 8-bit Data BUS. Address/Data. The low byte of the address and the data byte time multiplexed during external memory accesses. There is no need to use this bus to extract the low-address byte, since is already demultiplexed and available on the pins A7:0 |  |  |  |  |

| ĒĀ       | 45                        | 1             | I    | from external program memory only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| RD       | 47                        | 1             | I/O  | enable for external data memory devices. Active low.  Write. A strobe, active during an external write. To be used as a read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| WR       | 46                        | 1             | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| AD(7)    | 49                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| AD(6)    | 52                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| AD(5)    | 55                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| AD(4)    | 58                        | 8             | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| AD(3)    | 62                        | 0             | .,,  | There is no need to use this bus to extract the low-address byte, since it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| AD(2)    | 67                        |               |      | is already demultiplexed and available on the pins A7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| AD(1)    | 71                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| AD(0)    | 76                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(15)    | 51                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(14)    | 54                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(13)    | 57                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(12)    | 60                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(11)    | 61                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(10)    | 64                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(9)     | 66                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(8)     | 69                        | 16            | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(7)     | 70                        | 10            |      | A(7:0) are generated internally by demultiplexing of AD(7:0) with ALE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| A(6)     | 74                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(5)     | (5) 75                    |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(4)     | 78                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(3)     | 79                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(2)     | 80                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(1)     | 82                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| A(0)     | 83                        |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Pin Name  | Pin<br>Number<br>128 TQFP | Total<br>Pins | Туре | Description                                                                                                                                             |  |  |

|-----------|---------------------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLK1      | 117                       | 1             | 0    | Card interface 1 - Clock signal                                                                                                                         |  |  |

| IO1       | 116                       | 1             | I/O  | Card interface 1 - I/O signal                                                                                                                           |  |  |

| RST1      | 113                       | 1             | 0    | Card interface 1 - RST signal                                                                                                                           |  |  |

| VCC1      | 112                       | 1             | 0    | Card interface 1 - VCC signal Must be decoupled to GND with a 6.8μF low-ESR capacitor                                                                   |  |  |

| VCCIN1    | 108                       | 1             |      | Card interface 1 – voltage supply for interface circuits – take from VCC1 filter capacitor                                                              |  |  |

| C41       | 114                       | 1             | I/O  | Card interface 1 - Auxiliary I/O signal (card C4 signal)                                                                                                |  |  |

| C81       | 115                       | 1             | I/O  | Card interface 1 - Auxiliary I/O signal (card C8 signal)                                                                                                |  |  |

| CLK2      | 96                        | 1             | 0    | Card interface 2 - Clock signal                                                                                                                         |  |  |

| 102       | 98                        | 1             | I/O  | Card interface 2 - I/O signal                                                                                                                           |  |  |

| RST2      | 101                       | 1             | 0    | Card interface 2 - RST signal                                                                                                                           |  |  |

| VCC2      | 102                       | 1             | 0    | Card interface 2 - VCC signal Must be decoupled to GND with a 6.8μF low-ESR capacitor                                                                   |  |  |

| VCCIN2    | 106                       | 1             |      | Card interface 2 - voltage supply for interface circuits – take from VCC2 filter capacitor                                                              |  |  |

| GND_RTN   | 107                       | 1             |      | Ground connection for SC power converters                                                                                                               |  |  |

| C42       | 100                       | 1             | I/O  | Card interface 2 – Auxiliary I/O signal (card C4 signal)                                                                                                |  |  |

| C82       | 99                        | 1             | I/O  | Card interface 2 – Auxiliary I/O signal (card C8 signal)                                                                                                |  |  |

| DET_CARD1 | 81                        | 1             | I    | Card interface 1 - Presence contact input pin. Programmable polarity (to be connected according to the card presence switch with a pull-up / pull-down) |  |  |

| DET_CARD2 | 84                        | 1             | I    | Card interface 2 - Presence contact input pin. Programmable polarity (to be connected according to the card presence switch with a pull-up / pull-down) |  |  |

| SIO       | 87                        | 1             | I/O  | Digital I/O line for external card interfaces. Open drain with internal pull-up configuration – no external pull-up required                            |  |  |

| SCLK      | 88                        | 1             | 0    | Digital I/O line for external card interfaces.                                                                                                          |  |  |

| SC4       | 85                        | 1             | I/O  | Digital auxiliary I/O line for external card interfaces (C4 I/O). Open drain with internal pull-up configuration – no external pull-up required         |  |  |

| SC8       | 86                        | 1             | I/O  | Digital auxiliary I/O line for external card interfaces (C8 I/O). Open drain with internal pull-up configuration – no external pull-up required         |  |  |

| TOTAL     |                           | 128           |      |                                                                                                                                                         |  |  |

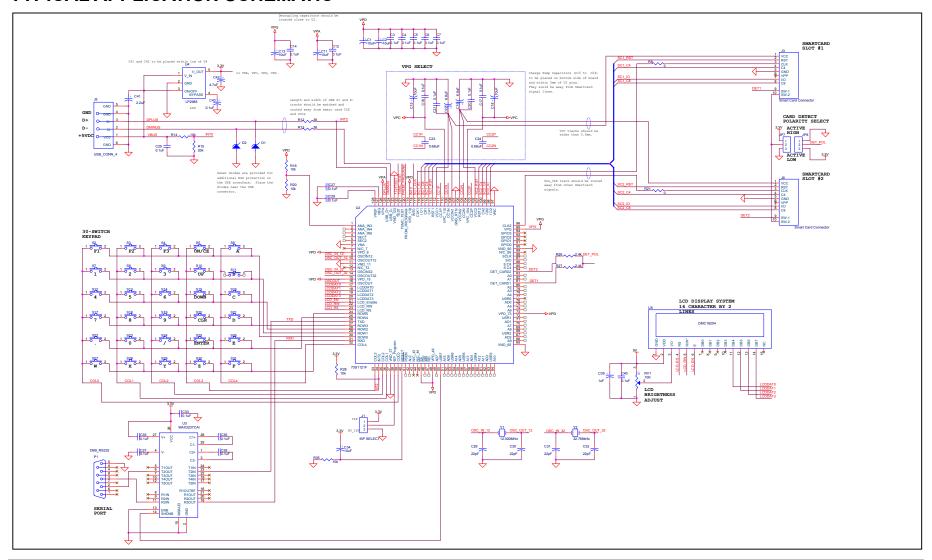

### **TYPICAL APPLICATION SCHEMATIC**

#### **ELECTRICAL SPECIFICATION**

#### **ABSOLUTE MAXIMUM RATINGS**

Operation outside these rating limits may cause permanent damage to the device.

| PARAMETER                                                                                  | RATING              |

|--------------------------------------------------------------------------------------------|---------------------|

| Supply Voltage (V <sub>PD</sub> , V <sub>PA</sub> , V <sub>PC</sub> , V <sub>PDPLL</sub> ) | -0.5V to 4.0V       |

| Supply Voltage (V <sub>PG</sub> )                                                          | -0.5V to 6.0V       |

| Pin Input Voltage (except OSCIN12, OSCIN32)                                                | -0.5V to 6.0V       |

| Pin Input Voltage (OSCIN12, OSCIN32)                                                       | -0.5V to VPD + 0.5V |

| Storage Temperature                                                                        | -60 to 150°C        |

| Pin Current                                                                                | ±75mA               |

| Maximum continuous Total Power Dissipation (at T <sub>A</sub> = 85 °C)                     | 1.2W                |

| Maximum Operating Junction Temperature                                                     | 125 °C              |

| ESD Tolerance – Card interface pins*                                                       | +/- 5kV             |

| ESD Tolerance – USB interface pins**                                                       | +/- 1.75kV          |

| ESD Tolerance – Other pins                                                                 | +/- 1kV             |

Note\*: ESD testing on Card pins is HBM condition, 3 pulses, each polarity referenced to ground.

Note\*\*: When an ESD tolerance of up to +/- 6kV is required on the USB interface pins, addition of 6.8V Zener diodes on D+ and D- are recommended. This is shown in the typical application schematic above.

#### **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                                                                                                                                                 | RATING             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Supply Voltage V <sub>PA</sub> /V <sub>PD</sub> /V <sub>PC</sub> with respect to V <sub>NA</sub> /V <sub>ND</sub> /V <sub>NC</sub> when not using USB I/F | 2.7V to 3.6V       |

| Supply Voltage $V_{PA}/V_{PD}/V_{PC}$ with respect to $V_{NA}/V_{ND}/V_{NC}$ when using USB I/F                                                           | 3.0V to 3.6V       |

| Supply Voltage V <sub>PD</sub> with respect to V <sub>ND</sub> for RAM data retention                                                                     | 2.0V to 3.6V       |

| Supply Voltage (V <sub>PG</sub> ) with respect to V <sub>NG</sub> <sup>1</sup>                                                                            | 2.7V to 5.5V       |

| 12MHz Oscillator Frequency                                                                                                                                | 12.000 MHz ±100ppm |

| 32768Hz Oscillator Frequency                                                                                                                              | 32.768 KHz ±20ppm  |

| Operating Temperature                                                                                                                                     | 0°C to +85°C       |

| Input Voltage for DP/DM                                                                                                                                   | 0V to 3.6V         |

| Input Voltage for ANA_IN(7:0)                                                                                                                             | 0V to 3.6V         |

#### THERMAL RESISTANCE

| PARAMETER                                                    | RATING  |

|--------------------------------------------------------------|---------|

| R <sub>th (J-A)</sub> Thermal Resistance Junction to Ambient | 33° C/W |

<sup>&</sup>lt;sup>1</sup> VPG can be left unconnected if GPIO are not used.

### DATA-SHEET

#### DC CHARACTERISTICS: DIGITAL I/Os

| SYMBOL           | PARAMETER                                             | Condition                                                                                | MIN                    | Тур. | MAX  | UNIT |

|------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------|------|------|------|

| Digital I/O exc  | ept for OSC12 and OSC32 I/O                           |                                                                                          |                        |      |      |      |

| V <sub>IL1</sub> | Input Low Voltage<br>(Except OSCIN32, OSCIN12)        |                                                                                          | -0.5                   |      | 0.8  | ٧    |

| V <sub>IH1</sub> | Input High Voltage<br>(Except OSCIN32, OSCIN12)       |                                                                                          | 0.7*V <sub>PD</sub>    |      | 5.5  | ٧    |

| V <sub>OL</sub>  | Output Low Voltage<br>(Except OSCOUT32,<br>OSCOUT12)  | I <sub>OL</sub> = 2mA                                                                    |                        |      | 0.45 | \ \  |

| V <sub>OH</sub>  | Output High Voltage<br>(Except OSCOUT32,<br>OSCOUT12) | I <sub>OH</sub> = -1mA                                                                   | V <sub>PD</sub> - 0.45 |      |      | \ \  |

| I <sub>IL1</sub> | Input Low Leakage Current (Except OSCIN32, OSCIN12)   | $V_{SS} < V_{in} < V_{IL1}$<br>Pull-ups Disabled <sup>2</sup>                            |                        |      | 1    | μA   |

| I <sub>IH1</sub> | Input High Leakage Current (Except OSCIN32, OSCIN12)  | V <sub>IH1</sub> < V <sub>in</sub> < V <sub>DD</sub><br>Pull-downs Disabled <sup>3</sup> |                        |      | 1    | μA   |

| I <sub>IL3</sub> | Input Low Leakage Current (Except OSCIN32, OSCIN12)   | $V_{SS} < V_{in} < V_{IL1}$<br>Pull-ups Enabled <sup>1</sup>                             |                        |      | 30   | μA   |

| I <sub>IH3</sub> | Input High Leakage Current (Except OSCIN32, OSCIN12)  | $V_{IH1} < V_{in} < 5.5V$<br>Pull-downs Enabled <sup>2</sup>                             |                        |      | 100  | μA   |

### DC CHARACTERISTICS: OSCILLATOR I/OS

| SYMBOL               | PARAMETER                                     | Condition                                                  | MIN                   | Тур. | MAX                    | UNIT |

|----------------------|-----------------------------------------------|------------------------------------------------------------|-----------------------|------|------------------------|------|

| Oscillator (OS       | SC) I/O Parameters                            |                                                            |                       |      |                        |      |

| V <sub>IL32</sub>    | Input Low Voltage -<br>OSCIN32                |                                                            | -0.5                  |      | 0.2* V <sub>PD</sub>   | V    |

| V <sub>IH32</sub>    | Input High Voltage -<br>OSCIN32               |                                                            | 0.7*V <sub>PD</sub>   |      | V <sub>PD</sub> + 0.5  | V    |

| V <sub>IL12</sub>    | Input Low Voltage -<br>OSCIN12                |                                                            | -0.5                  |      | 0.075* V <sub>PD</sub> | V    |

| V <sub>IH12</sub>    | Input High Voltage -<br>OSCIN12               |                                                            | 0.7*V <sub>PD</sub>   |      | V <sub>PD</sub> + 0.5  | V    |

| V <sub>OLOSC12</sub> | Output Low Voltage -<br>OSCOUT12              | I <sub>OL</sub> = 3.0mA                                    |                       |      | 0.7                    | V    |

| V <sub>OHOSC12</sub> | Output High Voltage - OSCOUT12                | I <sub>OH</sub> =-3.0mA                                    | V <sub>PD</sub> - 0.9 |      |                        | ٧    |

| V <sub>OLOSC32</sub> | Output Low Voltage - OSCOUT32                 | I <sub>OL</sub> = 5 μA                                     |                       |      | 0.25                   | V    |

| V <sub>OHOSC32</sub> | Output High Voltage - OSCOUT32                | I <sub>OH</sub> =-5 μA                                     | 0.5                   |      | $V_{PD}$               | V    |

| I <sub>IL2</sub>     | Input Leakage Current - OSCIN32, OSCIN12      | $V_{SS} < V_{in} < V_{IL2}$                                | 1                     |      | 30                     | μA   |

| I <sub>IH2</sub>     | Input High Leakage Current - OSCIN12, OSCIN32 | $V_{IH2} < V_{in} < V_{DD}$                                | 1                     |      | 30                     | μA   |

| tosc12MStart         | 12MHz Oscillator start up time                | Osc $V_{PP}$ = 90% stable $V_{PP}$ @ $V_{PC}$ = 3.3V, 25°C |                       | 500  |                        | μS   |

| tosc32KStart         | 32KHz Oscillator start up time                | Osc $V_{PP}$ = 90% stable $V_{PP}$ @ $V_{PC}$ = 3.3V, 25°C |                       | 300  |                        | mS   |

Pull-ups on USR1(7:0), GPIO(3:0), ROW(5:0)

Pull-downs on ISP\_Program, Prom\_Program

## 73S1121F EMV Smart-Card Terminal Controller

## with Built-in Dual ISO-7816 Interface and USB

## DATA-SHEET

#### DC CHARACTERISTICS: USB INTERFACE

| SYMBOL           | PARAMETER                              | Condition                           | MIN                   | Тур. | MAX      | UNIT |

|------------------|----------------------------------------|-------------------------------------|-----------------------|------|----------|------|

| Receiver para    | ameters                                |                                     |                       |      |          |      |

| V <sub>DI</sub>  | Differential input sensitivity         | (D+) - (D-)                         | 0.2                   |      |          | V    |

| V <sub>CM</sub>  | Differential common mode range         | Includes V <sub>DI</sub> range      | 0.8                   |      | 2.5      | V    |

| V <sub>SE</sub>  | Single ended receiver threshold        |                                     | 0.8                   |      | 2.0      | V    |

| Transmitter le   | evels                                  |                                     |                       |      |          |      |

| V <sub>OL</sub>  | Low Level Output Voltage               | USBCon = 1 (D+ pull-<br>up enabled) |                       |      | 0.3      | V    |

| V <sub>OH</sub>  | High Level Output Voltage              | 15K ohm resistor to ground          | V <sub>PD</sub> - 0.1 |      | $V_{PD}$ | V    |

| Leakage para     | ameters                                |                                     |                       |      |          |      |

| l <sub>oz</sub>  | High-Z state data line leakage current | 0V < VIN < 3.6V                     |                       |      | ±5       | nA   |

| Output resista   | ance                                   |                                     |                       |      |          |      |

| $Z_{DRV}$        | Driver output resistance               | Steady state drive                  | 28                    |      | 44       | Ω    |

| $Z_{pu}^{4}$     | Pull-up Resistor (to V <sub>PD</sub> ) | USBCon = 1                          | 1.2                   | 1.5  | 1.8      | kΩ   |

| Transceiver p    | ower requirements (not measurable      | on tester)                          |                       |      |          |      |

| I <sub>PSO</sub> | Operating supply current (output)      | Outputs enabled                     |                       |      | 5        | mA   |

| I <sub>PSI</sub> | Operating supply current (input)       | Outputs Hi-Z                        |                       |      | 1        | ma   |

| I <sub>PDN</sub> | Supply current in power down           |                                     |                       |      | 10       | nA   |

| $I_{PSS}$        | Supply current in suspend.             |                                     |                       |      | 10       | nA   |

$<sup>^4</sup>$  USB specifies that this value be 1.5k  $\Omega$  +/- 5%. An external resistor could be used instead (MIUSCTRL bit 0 set by firmware)

## DATA-SHEET

#### DC CHARACTERISTICS: ICC INTERFACE - CLK AND RST SIGNALS

| SYMBOL                                      | PARAMETER                        | Condition                                  | MIN                   | Тур. | MAX                    | UNIT |

|---------------------------------------------|----------------------------------|--------------------------------------------|-----------------------|------|------------------------|------|

| Clock Lines C                               | CLK and /CLK2 (VCC = VCC1 for CL | LK1 and VCC = VCC2 for                     | CLK2)                 |      |                        |      |

| V <sub>OHC</sub>                            | High Level Output Voltage        | $0 < I_{OH} < 50\mu A$ ,<br>$V_{CC} = Min$ | V <sub>CC</sub> - 0.5 |      | V <sub>CC</sub>        | V    |

| $V_{OLC}$                                   | Low Level Output Voltage         | $-50\mu A < I_{OL} < 0, V_{CC} = Min$      | 0                     |      | 0.4                    | V    |

| t <sub>r-clk</sub> , t <sub>f-clk</sub>     | Rise / Fall time                 | C <sub>load</sub> = 30pf max               | -                     |      | 8% of clock period     |      |

| P <sub>ERTLC</sub>                          | Signal perturbation low          | Signal low                                 | - 0.25                |      | 0.4                    | V    |

| P <sub>ERTHC</sub>                          | Signal perturbation high         | Signal high                                | V <sub>CC</sub> - 0.5 |      | $V_{CC} + 0.25$        | V    |

| δ                                           | Duty Cycle                       | Clocks in stable operation                 | 45                    |      | 55                     | %    |

| Reset Lines F                               | RST1 and RST2 (VCC = VCC1 for F  | RST1 and VCC = VCC2 fo                     | or RST2)              |      |                        |      |

| V <sub>OHR</sub>                            | High Level Output Voltage        | $0 < I_{OH} < 50\mu A, V_{CC} = Min$       | V <sub>CC</sub> - 0.5 |      | Vcc                    | V    |

| V <sub>OLR</sub>                            | Low Level Output Voltage         | $-50\mu A < I_{OL} < 0, V_{CC} = Min$      | 0                     |      | 0.4                    | V    |

| t <sub>r-RST</sub> , t <sub>f-</sub><br>RST | Rise / Fall time                 | C <sub>load</sub> = 30pf Max               | -                     |      | 0.8                    | μs   |

| $P_{ERTLR}$                                 | Signal perturbation low          | Signal low                                 | - 0.25                |      | 0.4                    | V    |