# 7902 Network Security Processor Data Sheet

Hifn supplies the Internet's most important raw materials for the creation of intelligent and secure networks: compression, encryption, and flow classification. This is central to the growth of the Internet, helping to make electronic mail, web browsing, Internet shopping and multimedia communications better, faster and more secure.

Hi/fn, Inc. 750 University Avenue Los Gatos, CA 95032 info@hifn.com http://www.hifn.com Tel: 408-399-3500 Fax: 408-399-3501

For technical support, please contact your local Hifn sales office, representative or distributor. For locations check: www.hifn.com

#### Disclaimer

Hi/fn reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

Hi/fn warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with Hi/fn's standard warranty. Testing and other quality control techniques are utilized to the extent Hi/fn deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

HI/FN SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of Hi/fn products in such critical applications is understood to be fully at the risk of the customer. Questions concerning potential risk applications should be directed to Hi/fn through a local sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

Hi/fn does not warrant that its products are free from infringement of any patents, copyrights or other proprietary rights of third parties. In no event shall Hi/fn be liable for any special, incidental or consequential damages arising from infringement or alleged infringement of any patents, copyrights or other third party intellectual property rights.

"Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals," must be validated for each customer application by customer's technical experts.

The use of this product may require a license from Motorola. A license agreement for the right to use Motorola patents may be obtained through Hi/fn or directly from Motorola.

DS-0040-00 (1/01) © 1997-2001 by Hi/fn, Inc., including one or more U.S. patents No.: 4,701,745, 5,003,307, 5,016,009, 5,126,739, 5,146,221, 5,414,425, 5,414,850, 5,463,390, 5,506,580, and 5,532,694. Other patents pending. Hi/fn and LZS are registered trademarks of Hi/fn, Inc. Hifn is a trademark of Hi/fn, Inc. All other trademarks are the property of their respective holders.

This product must be exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law prohibited.

## **Table of Contents**

| 1  | Prod | luct Description                            | 7    |

|----|------|---------------------------------------------|------|

| 2  | Perf | ormance Summary                             | 8    |

|    | 2.1  | Symmetric Key Processing Units              |      |

|    | 2.2  | Protocols                                   |      |

|    | 2.3  | Public Key                                  |      |

| 3  | Prod | luct Overview                               |      |

|    | 3.1  | Operation                                   | . 11 |

|    | 3.2  | Functional Blocks                           |      |

| 4  | Sign | al Description                              |      |

|    | 4.1  | Signal List                                 |      |

|    | 4.2  | Clocks                                      |      |

|    | 4.3  | Phase Lock Loop (PLL)                       |      |

|    | 4.4  | Reset                                       |      |

| 5  | Men  | nory Map                                    | . 16 |

|    | 5.1  | Byte and Bit Ordering                       | . 16 |

|    | 5.2  | Registers                                   | . 17 |

|    | 5.3  | Internal Memory                             | . 17 |

| 6  | Exte | rnal RAM                                    | . 19 |

| 7  | Proc | essor Bus Interface                         | . 20 |

|    | 7.1  | MPC860/8260 Bus Interface                   |      |

|    | 7.2  | Bus Transfer Overview – MPC860 Mode         |      |

|    | 7.3  | Processor Bus Interface Signal Descriptions | . 28 |

| 8  | Gen  | eral Registers                              |      |

|    | 8.1  | General Configuration Register              | . 31 |

|    | 8.2  | Chip ID Register                            |      |

| 9  | Publ | ic Key Engine & Random Number Generator     |      |

|    | 9.1  | Overview                                    |      |

|    | 9.2  | Random Number Generator                     |      |

|    | 9.3  | Public Key Data Movement                    |      |

|    | 9.4  | Operations                                  |      |

|    | 9.5  | Operands                                    |      |

|    | 9.6  | Reciprocal Calculations                     | . 38 |

|    | 9.7  | Public Base Address Register                |      |

|    | 9.8  | Public Operand Length Register              |      |

|    | 9.9  | Public Operation Register                   |      |

|    |      | Public Status Register                      |      |

|    |      | Public Interrupt Enable Register            |      |

|    |      | RNG Configuration Register                  |      |

|    |      | RNG Data Register                           |      |

| 10 | Pack | tet Engine                                  | . 44 |

|    | 10.1 | Overview                                    | . 44 |

|    |      | Data Movement                               |      |

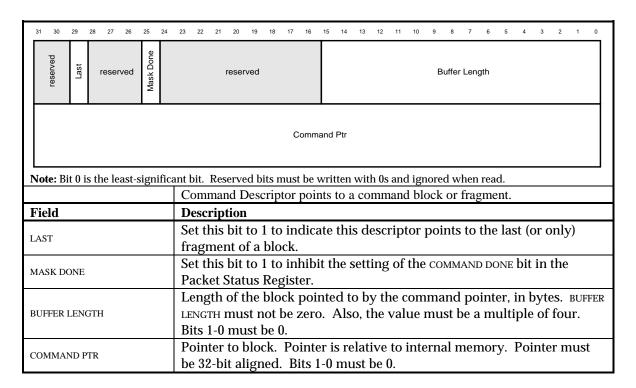

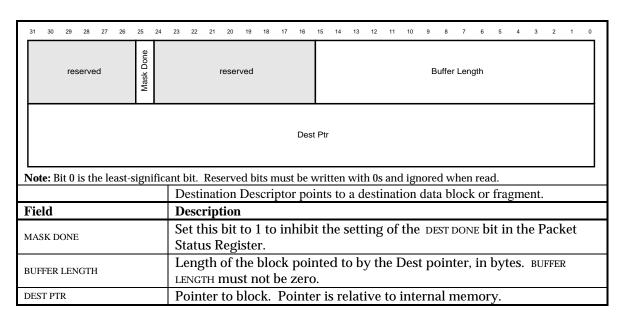

|    | 10.3 | Descriptors                                 | . 46 |

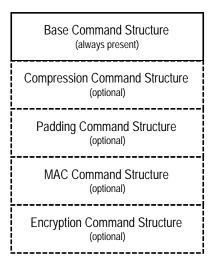

|    |      | Command Structure                           |      |

|    | 10.5 | Read RAM/Write RAM Command Structures       | . 56 |

|    |      | Source Structures                           |      |

|    | 10.7 | Dest Structures                             | . 57 |

|    |      | Result Structures                           |      |

|    |      | External RAM Usage                          |      |

|    | 10.1 | OHost Command Index Register                | . 62 |

|    | 10.1 | 1 Host Source Index Register                | . 63 |

|       | 10.12Host Result Index Register                                | 63 |

|-------|----------------------------------------------------------------|----|

|       | 10.13Host Destination Index Register                           | 64 |

|       | 10.14Packet Status Register                                    | 64 |

|       | 10.15Packet Interrupt Enable Register                          | 67 |

|       | 10.16Packet Configuration Register                             | 68 |

| 11    | DC Specifications                                              |    |

|       | 11.1 Power Sequencing                                          |    |

|       | 11.2 Recommended Operating Conditions                          |    |

|       | 11.3 DC Characteristics                                        |    |

| 12    | AC Specifications                                              |    |

| 13    | Thermal Specifications                                         |    |

| -     | Pin List.                                                      |    |

|       | Physical Specifications                                        |    |

| 13    | 1 hysical Specifications                                       | 1) |

|       |                                                                |    |

| Fig   | ures                                                           |    |

| Figu  | re 1. Typical VPN Router Example                               | 7  |

|       | re 2. Processing Unit Performance                              |    |

|       | re 3. Protocol Performance                                     |    |

|       | ire 4. IKE Performance                                         |    |

|       | re 5. Processing Unit Performance (50MHz Operation)            |    |

|       | re 6. Processing Unit Performance (66MHz Operation)            |    |

|       | re 7. 7902 Internal Block Diagram                              |    |

| _     | re 8. CPU Interface Signal List                                |    |

|       | re 9. External RAM Interface Signal List                       |    |

|       | re 10. Miscellaneous Signal List                               |    |

| _     | <u> </u>                                                       |    |

|       | ure 11. Internal Clock and PLL Circuit                         |    |

|       | re 12. 7902 Operating Frequency Range                          |    |

|       | ire 13. 7902 Memory Map                                        |    |

|       | ire 14. Byte Order in Memory                                   |    |

|       | re 15. 7902 Register Summary                                   |    |

|       | ire 16. Internal Memory Map                                    |    |

|       | re 17. MPC860 / 7902 Interface                                 |    |

| _     | re 18. Input Sample Window                                     |    |

|       | re 19. MPC860 Single-Beat Write and Read Timing                |    |

|       | re 20. MPC860 Burst Transfer Read and Write Timing             |    |

| Figu  | re 21. Transfer Error Acknowledge (TEA#) Timing                | 27 |

| Figu  | re 22. Transfer Sizes Supported (MPC860 Mode)                  | 29 |

| Figu  | re 23. Public Key Operations                                   | 33 |

| Figu  | re 24. Public Key Operand Storage in Internal Memory           | 34 |

| Figu  | re 25. Operand Pointers and Offsets                            | 34 |

|       | re 26. Field Values and Memory Locations                       |    |

|       | re 27. Operand Use for Each Operation                          |    |

|       | re 28. Public Key Memory Use General Purpose Example           |    |

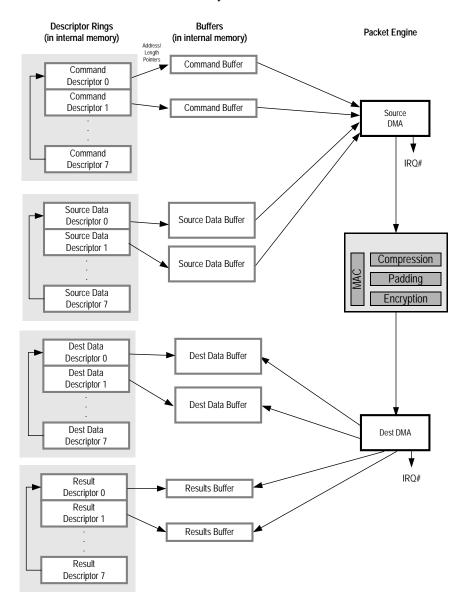

|       | re 29. Packet Engine Block Diagram                             |    |

|       | ire 30. Command Structures                                     |    |

|       | ire 31. Typical Use of Descriptors For a Command That Requires | .0 |

|       | Encryption Context                                             | 56 |

|       | re 32. Result Structures                                       |    |

|       | re 33. Context Memory Modes                                    |    |

|       |                                                                |    |

|       | ire 34. External RAM Memory Usage                              |    |

|       | are 35. Absolute Maximum Ratings                               |    |

| rıgu: | re 36. Recommended Operating Conditions                        | 69 |

| Figure 37. | DC Electrical Characteristics       | 70 |

|------------|-------------------------------------|----|

| Figure 38. | AC Specification Definition         | 71 |

| Figure 39. | AC Specification Derating           | 71 |

|            | Reset Timing                        |    |

|            | External Clock                      |    |

| Figure 42. | Read/Write CPU Timing (Single Beat) | 73 |

| Figure 43. | External SRAM Read Timing           | 74 |

|            | External SRAM Write Timing          |    |

| Figure 45. | Thermal Specifications              | 76 |

| Figure 46. | Pin List (Numeric)                  | 77 |

| Figure 47. | Pin List (Alphabetical)             | 78 |

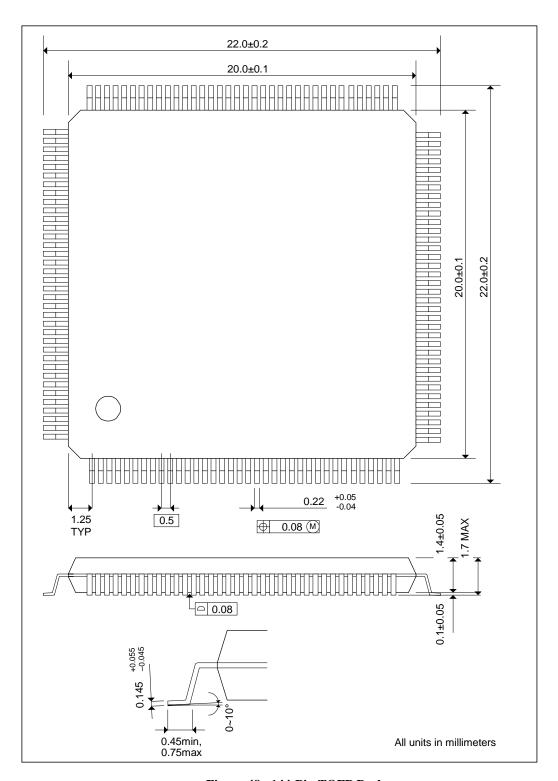

| -          | 144-Pin TOFP Package                |    |

THIS PAGE INTENTIONALLY BLANK

# **Product Description**

The 7902 Network Security Processor implements symmetric key encryption, public key encryption, authentication, and data compression in hardware. Its pipelined architecture allows many of these functions to be performed in a single pass. The integrated algorithms support standard network security protocols including IPSec, PPTP, L2TP, PPP, and others. The algorithms implemented by the processor include DES, Triple-DES, and RC4 encryption, SHA-1 and MD5 hash algorithms, HMAC functions, and LZS and MPPC data compression.

The 7902 also includes a math processor and a true hardware random number generator. These features are provided to support the public key cryptography required for key generation, exchange, and authentication such as used by X.509.

The processing speed of the 7902 supports the equivalent of two full duplex T1/E1 data communication lines. The 7902 interfaces directly with the MPC860 bus; no external interface logic is required with this bus. The 7902 also interfaces with the MPC8260 with a minimal amount of external logic.

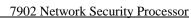

Figure 1 shows the placement of a 7902 in a typical VPN Router.

#### **Features**

- Pipelined security processor supporting major security protocols including IPSec, PPTP, L2TP, PPP, and IKE

- Symmetric key encryption (DES, Triple-DES, and RC4)

- Authentication (SHA-1 and MD5)

- Compression (LZS and MPPC)

- Public Key processing unit (2048-bit modular arithmetic and exponentiation)

- Random Number Generator

- Internal memory buffers data packets

- Direct interface to 50 MHz MPC860 bus

- Minimal external logic interface to MPC8260 bus

- Maximum frequency of 66 MHz

| Part Number | Package      |

|-------------|--------------|

| 7902PT6     | 144-Pin TQFP |

Figure 1. Typical VPN Router Example

# 2 Performance Summary

The figures in this section summarize the performance of the 7902 functional units. Performance of the 7902 when multiple engines are used (for example, the compression, MAC and encryption engines are all engaged) can be approximated by considering the 7902 throughput of the slowest engine.

The MAC and encryption engine speeds are accelerated (effectively multiplied) by the actual compression ratio achieved by the compression engine. For example, if the achieved compression ratio is 2:1, then the MAC and encryption engine speeds are effectively doubled and the compression engine would be the slowest engine. This performance data reflects the following conditions:

- 1. 1500-byte packets.

- 2. Single session or security association.

# 2.1 Symmetric Key Processing Units

| Protocol           | 50 MHz<br>Performance | 66 MHz<br>Performance |

|--------------------|-----------------------|-----------------------|

| DES                | 143 Mbps              | 188 Mbps              |

| 3DES               | 53 Mbps               | 70 Mbps               |

| RC4                | 78 Mbps               | 103 Mbps              |

| SHA-1              | 50 Mbps               | 66 Mbps               |

| MD5                | 60 Mbps               | 79 Mbps               |

| LZS Compression    | 40 Mbps               | 52 Mbps               |

| LZS Decompression  | 75 Mbps               | 99 Mbps               |

| MPPC Compression   | 33 Mbps               | 43 Mbps               |

| MPPC Decompression | 67 Mbps               | 88 Mbps               |

**Note:** The performance numbers are based on simulation results. Text from the United States Constitution was arbitrarily selected for the compression and decompression simulations. The compression ratio is approximately 2:1.

Figure 2. Processing Unit Performance

#### 2.2 Protocols

|                           | 50 N        | ИHz                | 66 M        | Hz              |

|---------------------------|-------------|--------------------|-------------|-----------------|

| Protocol                  | Performance | No.<br>Packets/sec | Performance | No. Packets/sec |

| IPSec (3-DES, SHA-1, LZS) | 37 Mbps     | 25 K               | 48 Mbps     | 33 K            |

| PPTP (RC4, MPPC)          | 32 Mbps     | 40 K               | 42 Mbps     | 52 K            |

**Note:** The performance and packets/sec numbers are based on simulation results. The performance numbers are based on the rate of the uncompressed data; the data was arbitrarily selected from the United States Constitution. The compression ratio is approximately 2:1.

Figure 3. Protocol Performance

# 2.3 Public Key

| IKE Handshake                 | No.<br>Connections/sec<br>50 MHz | No.<br>Connections/sec<br>66 MHz |

|-------------------------------|----------------------------------|----------------------------------|

| Two 1024-bit Diffie-Hellman   | 6                                | 8                                |

| operations (Quick Mode)       |                                  |                                  |

| Two 1024-bit Diffie-Hellman   | 3                                | 4                                |

| operations, 1 RSA sign, 2 RSA |                                  |                                  |

| verifies (Main Mode)          |                                  |                                  |

| Four 1024-bit Diffie-Hellman  | 2                                | 2.7                              |

| operations, 1 RSA sign, 2 RSA |                                  |                                  |

| verifies (Main Mode + Quick   |                                  |                                  |

| Mode)                         |                                  |                                  |

**Notes:** 180-bit exponent. The number of connections/sec is based on simulation results.

Figure 4. IKE Performance

| On another 50 MHz                       | Time to complete    |              |             |             |  |

|-----------------------------------------|---------------------|--------------|-------------|-------------|--|

| Operation – 50 MHz                      | <b>2048-bit key</b> | 1024-bit key | 768-bit key | 512-bit key |  |

| RSA private key                         | 873.9 ms            | 125.4 ms     | 49.5 ms     | 18.5 ms     |  |

| RSA public key<br>(3-bit exponent)      | 4.8 ms              | 1.3 ms       | 0.8 ms      | 0.4 ms      |  |

| Diffie-Hellman<br>(180-bit exponent)    | 286.5 ms            | 76.6 ms      | 50.9 ms     | 21.8 ms     |  |

| Diffie-Hellman<br>(exponent = key size) | 3260.4 ms           | 435.6 ms     | 216.5 ms    | 62.1 ms     |  |

| DSA sign                                |                     | 136.7 ms     | 82.2 ms     | 39.6 ms     |  |

| DSA verify                              |                     | 205 ms       | 123.2 ms    | 59.4 ms     |  |

**Notes:** Performance assumes a uniform distribution of ones and zeros in the exponent. The performance numbers are based on simulation results.

Figure 5. Processing Unit Performance (50MHz Operation)

| Operation 66 MHz                        | Time to complete |              |             |             |

|-----------------------------------------|------------------|--------------|-------------|-------------|

| Operation – 66 MHz                      | 2048-bit key     | 1024-bit key | 768-bit key | 512-bit key |

| RSA private key                         | 662 ms           | 95.0 ms      | 37.5 ms     | 14.0 ms     |

| RSA public key<br>(3-bit exponent)      | 3.6 ms           | 0.95 ms      | 0.58 ms     | 0.27 ms     |

| Diffie-Hellman<br>(180-bit exponent)    | 217 ms           | 58.0 ms      | 38.5 ms     | 16.5 ms     |

| Diffie-Hellman<br>(exponent = key size) | 2,470 ms         | 330 ms       | 164 ms      | 47.0 ms     |

| DSA sign                                |                  | 103.5 ms     | 62.2 ms     | 30.0 ms     |

| DSA verify                              |                  | 155.3 ms     | 93.3 ms     | 45.0 ms     |

**Note:** Performance assumes a uniform distribution of ones and zeros in the exponent. The performance numbers are based on simulation results.

Figure 6. Processing Unit Performance (66MHz Operation)

# **Product Overview**

# 3.1 Operation

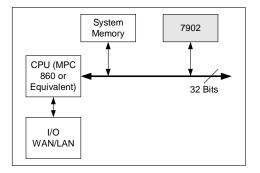

The 7902 contains several processing units—Random Number Generator, Public Key, symmetric key encryption, compression, padding, and authentication. The symmetric key encryption, compression, padding, and authentication units are combined into a single functional block labeled *Packet Engine*.

In normal operation, the host buffers data packets (or fragments) and commands into the internal memory of the 7902. Since internal memory is memory mapped, there is no need for sophisticated external DMA hardware. Simple memory-to-memory DMA transfers or CPU I/O transfers may be used. As the 7902 executes each command, the resulting data packets are stored back into internal memory. The host then transfers the resulting data out.

The 7902 internal block diagram is shown in Figure 7.

Figure 7. 7902 Internal Block Diagram

#### 3.2 Functional Blocks

#### 3.2.1 Internal Packet Memory

The internal packet memory (IPM) is 8K bytes in size and is used to buffer data packets, command structures, context information, context information, and descriptors.

The IPM is mapped into the host memory space and is accessed as host memory. See section 5 Memory Map for more information and the memory map.

#### 3.2.2 RAM Interface

The RAM interface controls an external 16-bit memory device. Up to 256Kx16 of SRAM is supported. External memory is required only if the data compression engine is used. External memory has space available for keys and Initialization Vectors (IVs) to be stored. Therefore, they don't need to be supplied for every encryption/authentication operation.

This memory is not directly accessible by the host CPU as it is dedicated for use by the compression engine.

#### 3.2.3 Registers

Programmable registers are used to store configuration information for the functional units. The registers are all memory-mapped.

#### 3.2.4 Processor Bus Interface

The synchronous Processor Bus Interface gluelessly supports the MPC860 bus. With a minimal amount of external logic, the MPC8260 bus interface is supported. Since all registers and internal memory are accessed as system memory, there is no need for DMA handshaking signals. Data transfers are performed with memory-to-memory DMA transfers or CPU I/O transfers.

#### 3.2.5 Packet Engine

The Packet Engine contains the symmetric encryption, compression, padding, and authentication processing units. The Packet Engine accesses data packets and commands directly from the IPM. The resulting data and status information are stored back into IPM.

#### 3.2.6 Random Number Generator

The Random Number Generator (RNG) is based on internal free-running oscillators whose frequencies drift relative to each other and to the 7902's internal clock. The phase relation of these signals is unpredictable, and this is used to provide a random bit stream. The host must further process this random bit stream to create cryptographic-quality random numbers.

#### 3.2.7 Public Key

The Public Key processing unit implements modular arithmetic functions. The Public Key processing unit accesses operands and commands directly from the IPM. The arithmetic results are stored back into IPM.

# Signal Description

# 4.1 Signal List

# 4.1.1 CPU Interface

| Name                | Type  | Description                                                                                                                                       |  |  |  |

|---------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                     |       | Address Bus.  Important: The address bus lines have dual names since the signal                                                                   |  |  |  |

| A[13-0]//MA[18-31]  | I     | names and signal ordering differ with different processors. MA[18-31]                                                                             |  |  |  |

|                     |       | signal names are for use with MPC860/8260 processors. A[13-0] signal                                                                              |  |  |  |

|                     |       | names are for use with other processors.                                                                                                          |  |  |  |

|                     |       | Data bus.                                                                                                                                         |  |  |  |

| D[31-0]/ MD[0-31]   | I/O8  | <b>Important:</b> The data bus lines have dual names since the signal names and signal ordering differ with different processors. MD[0-31] signal |  |  |  |

| D[01 0]/ MD[0 01]   | 17 00 | names are for use with MPC860/8260 processors. D[31-0] signal names                                                                               |  |  |  |

|                     |       | are for use with other processors.                                                                                                                |  |  |  |

|                     |       | Transfer Size.                                                                                                                                    |  |  |  |

|                     |       | <b>Important:</b> A subset of the transfer sizes available with the MPC860                                                                        |  |  |  |

|                     |       | and MPC8260 processors is supported. The transfer sizes supported                                                                                 |  |  |  |

|                     |       | are shown in the table below:                                                                                                                     |  |  |  |

|                     |       | <b>TSIZ[0-1] BURST# MPC860</b> 00 1 4 bytes                                                                                                       |  |  |  |

|                     |       | 00 1 4 bytes<br>00 0 16 bytes                                                                                                                     |  |  |  |

| TSIZ[0-3]           | I     | <b>Note:</b> Other transfer sizes are not supported. TSIZ[0-1] must be connected for proper                                                       |  |  |  |

| · •. <u>=</u> [• •] | 1     | operation of TEA#. TSIZ[2-3] should be tied low.                                                                                                  |  |  |  |

|                     |       | TSIZ[0-3] BURST# MPC8260                                                                                                                          |  |  |  |

|                     |       | 0000 1 8 bytes                                                                                                                                    |  |  |  |

|                     |       | 0010 0 32 bytes<br>0100 1 4 bytes                                                                                                                 |  |  |  |

|                     |       | 0100 1 4 bytes  Note: Other transfer sizes are not supported. TSIZ[0-3] must be connected for proper                                              |  |  |  |

|                     |       | operation of TEA#.                                                                                                                                |  |  |  |

|                     | 3S    | Interrupt Request.                                                                                                                                |  |  |  |

| IRQ#                |       | <b>Important:</b> When this signal is not being driven low by the 7902 for                                                                        |  |  |  |

|                     |       | an interrupt request, it is in a high-z state. An external pull-up resistor                                                                       |  |  |  |

| CS#                 | I     | should be tied to this signal. Chip Select.                                                                                                       |  |  |  |

| BURST#              | I     | Burst Transfer.                                                                                                                                   |  |  |  |

| TS#                 | I     | Transfer Start.                                                                                                                                   |  |  |  |

| TA#                 | 3S    | Transfer Acknowledge.                                                                                                                             |  |  |  |

| AACK#               | 3S    | Address Acknowledge. (Used with 8260 only.)                                                                                                       |  |  |  |

| DBB#                | I     | Data Bus Busy. (Used with 8260 only.)                                                                                                             |  |  |  |

| R/W#                | I     | Read/Write. R/W# is not used with the MPC8260. In the MPC8260                                                                                     |  |  |  |

| K/VV#               |       | mode, RW# functions as TT1.                                                                                                                       |  |  |  |

| TEA#                | 3S    | Transfer Error Acknowledge.                                                                                                                       |  |  |  |

| BDIP#/PSDVAL#       | I/3S  | BDIP# - 860 mode (input) - Burst data in progress.                                                                                                |  |  |  |

|                     |       | PSDVAL# - 8260 mode (tri-state) - Partial Data Valid.                                                                                             |  |  |  |

| CLK                 | I     | Bus Clock.                                                                                                                                        |  |  |  |

| BMODE               | I     | Bus Mode. Low = MPC8260 mode. High = MPC860 mode.                                                                                                 |  |  |  |

**Notes:** I-input, O-output, I/O-Input/Output, 3S-TriState. Refer to the DC Specifications for details regarding the output drive capabilities.

Figure 8. CPU Interface Signal List

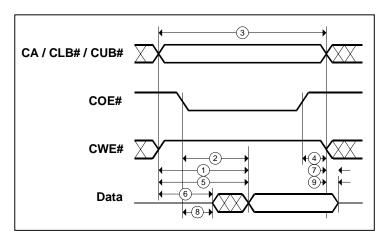

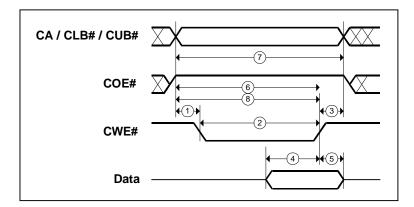

#### 4.1.2 External RAM Interface

| Name     | Type | Description                                       |

|----------|------|---------------------------------------------------|

| CA[17-0] | О8   | SRAM Address.                                     |

| CA[17-0] |      | <b>Important:</b> Bit 0 is least-significant bit. |

| COE#     | O8   | SRAM Output Enable.                               |

| CD[45 0] | I/O8 | SRAM Data.                                        |

| CD[15-0] |      | Important: Bit 0 is least-significant bit.        |

| CUB#     | O4   | SRAM Upper Byte Enable.                           |

| CLB#     | O4   | SRAM Lower Byte Enable.                           |

| CWE#     | O8   | SRAM Write Enable.                                |

$oldsymbol{Notes:}$  O-output, I/O-Input/Output. Refer to the DC Specifications for details regarding the output drive capabilities.

Figure 9. External RAM Interface Signal List

#### 4.1.3 Miscellaneous

| Name    | Type | Description                                  |

|---------|------|----------------------------------------------|

| RESET#  | I    | Reset.                                       |

| PLLE#   | ī    | PLL enable input.                            |

| PLLE#   | 1    | High=PLL disabled, low=PLL enabled.          |

|         |      | NAND Tree Test Enable input.                 |

| NDTEST# | I    | High = normal mode, low = NAND tree test     |

|         |      | mode.                                        |

| NDPI    | т .  | NAND Tree input. This input should be low in |

| NDFI    | 1    | normal mode.                                 |

| NDPO    | O4   | NAND Tree output. This pin should be left    |

| NDFO    | 04   | open in normal mode.                         |

| VDD     |      | +3.3 volts.                                  |

| VDD2    |      | +2.5 volts.                                  |

| VSS     |      | Ground.                                      |

| AVDD2   |      | PLL VDD. Connect to analog +2.5 volts.       |

| AVSS    |      | PLL VSS. Connect to analog ground.           |

|         |      | No connection.                               |

| NC      |      | Important: Pins labeled as NC must not have  |

|         |      | anything connected to them.                  |

$\label{eq:Notes:output} \textbf{Notes:} \ O\text{-output}, \ I/O\text{-Input/Output}. \ \ Refer to the DC \ Specifications for details regarding the output drive capabilities.$

Figure 10. Miscellaneous Signal List

#### 4.2 Clocks

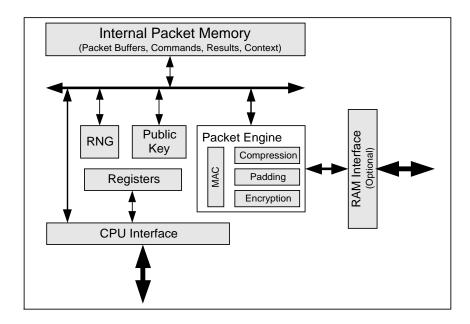

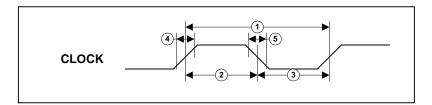

The 7902 has a single clock input signal (CLK). This clock signal drives I/O timing as well as the operation of the functional units (the Random Number Generator, Public Key processor, and Packet Engine).

Figure 11. Internal Clock and PLL Circuit

# 4.3 Phase Lock Loop (PLL)

The 7902 has an integrated PLL that does not require external components. The PLL should be enabled or disabled based on the input clock frequency (see Figure 11 and Figure 12).

| PLL      | CLK      |  |  |  |  |  |  |

|----------|----------|--|--|--|--|--|--|

| Disabled | < 40MHz  |  |  |  |  |  |  |

| Enabled  | 40-66MHz |  |  |  |  |  |  |

Figure 12. 7902 Operating Frequency Range

#### 4.4 Reset

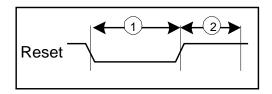

Reset halts all the internal functional blocks and resets the registers. A reset may be initiated with the RESET# signal, or the RESET bit in the Configuration Register. All registers return to their reset value as defined in each register description.

# Memory Map

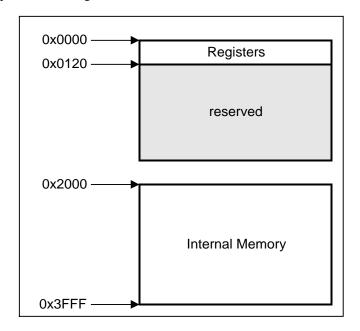

All registers and internal memory is accessed by the system with normal memory transfers. The 7902 occupies 16 Kbytes of the system memory map. The memory map is shown in Figure 13.

Figure 13. 7902 Memory Map

# 5.1 Byte and Bit Ordering

#### 5.1.1 Byte Ordering

All addresses are presented as byte addresses. Multi-byte transfers are assumed to be ordered in big-endian style. For example, the byte string 0x20, 0x21, 0x22, 0x23, 0x24, 0x25, 0x26, 0x27 would appear in memory as shown in Figure 14.

| Address  | 00   | 01   | 02   | 03   | 04   | 05   | 06   | 07   |

|----------|------|------|------|------|------|------|------|------|

| Contents | 0x20 | 0x21 | 0x22 | 0x23 | 0x24 | 0x25 | 0x26 | 0x27 |

Figure 14. Byte Order in Memory

This byte string would be transferred over the 32-bit bus as 0x20212223, 0x24252627.

#### 5.1.2 Bit Ordering

The convention used for bus signal labels with the MPC860/8260 is the opposite order from other processor buses. The MPC860/8260 convention uses bit zero as the most-significant bit while other processors use bit zero as the least-significant bit. This convention applies to address signals, data signals, and register bits.

This datasheet adopts the convention that the least-significant bit is always labeled as bit zero; however, the address and data bus pins have been given dual names to make it easier when using processors supporting the MPC860/8260 bit

ordering convention. The address bus pin names are A[13-0]/MA[18-31] and the MA[18-31] signals should be used with processors supporting the MPC860/8260 convention. Similarly, the data bus pin names are D[31-0]/MD[0-31] and the MD[0-31] signals should be used with processors supporting the MPC860/8260 convention.

# 5.2 Registers

The 32-bit programmable registers are mapped into the first 8 Kbytes of the memory address space (0x0000 to 0x1FFF), although only a small subset of this address space is actually used. A register summary is shown in Figure 15.

| Category                      | Address | Register                |  |  |  |  |

|-------------------------------|---------|-------------------------|--|--|--|--|

| General                       | 0x0004  | General Configuration   |  |  |  |  |

| General                       | 0x0008  | Chip ID                 |  |  |  |  |

|                               | 0x0080  | Host Command Index      |  |  |  |  |

|                               | 0x0084  | Host Source Index       |  |  |  |  |

| Crommotois Vary and           | 0x0088  | Host Result Index       |  |  |  |  |

| Symmetric Key and Compression | 0x008C  | Host Destination Index  |  |  |  |  |

| Compression                   | 0x0090  | Packet Status           |  |  |  |  |

|                               | 0x0094  | Packet Interrupt Enable |  |  |  |  |

|                               | 0x0098  | Packet Configuration    |  |  |  |  |

|                               | 0x0100  | Public Base Address     |  |  |  |  |

|                               | 0x0104  | Public Operand Length   |  |  |  |  |

|                               | 0x0108  | Public Operation        |  |  |  |  |

| Public Key and RNG            | 0x010C  | Public Status           |  |  |  |  |

|                               | 0x0110  | Public Interrupt Enable |  |  |  |  |

|                               | 0x0114  | RNG Configuration       |  |  |  |  |

|                               | 0x0118  | RNG Data                |  |  |  |  |

Note: Unused addresses are reserved and must not be accessed.

Figure 15. 7902 Register Summary

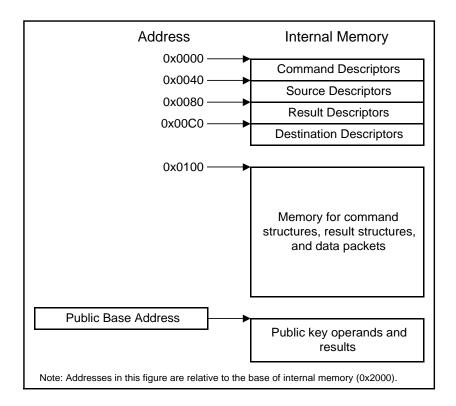

# 5.3 Internal Memory

Internal memory is mapped into the address range 0x2000 to 0x3FFF. The size of this memory is 8 Kbytes. Data may be read and written to this memory in the same manner as system memory.

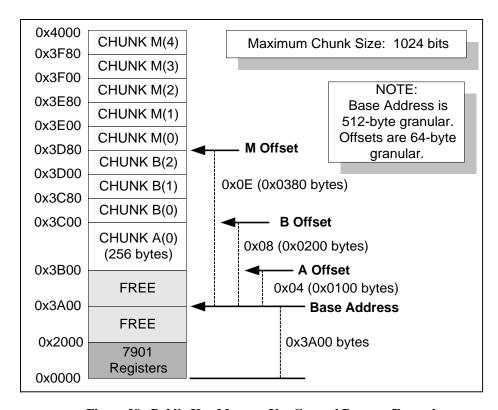

Certain regions of internal memory are reserved for special functions. These are identified in the internal memory map shown in Figure 16. The base address associated with descriptor rings is fixed. The base address associated with public key operations may be configured in the Public Base Address Register.

**Warning**: The Public Key memory space should not be accessed while a Public Key operation is taking place. The PUBLIC DONE bit in the Public Status Register may be used to determine if a Public Key operation is in progress.

Figure 16. Internal Memory Map

## External RAM

The RAM interface controls an external 16-bit memory device. Use of external memory is required only if data compression is used; otherwise, external memory is not required. This memory is dedicated to the compression engine and is not directly accessible from the system.

The 7902 supports up to 256Kx16 external memory. The RAM interface signals connect directly to the 7902 without any additional glue logic.

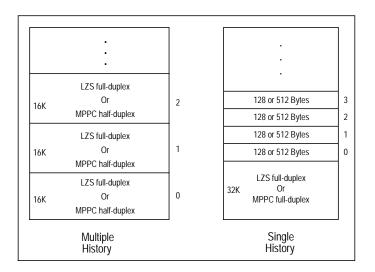

Each full-duplex LZS session requires 16 Kbytes of external RAM. Each full-duplex MPPC session requires 32 Kbytes. This allows support of up to 32 full-duplex LZS sessions or 16 full-duplex MPPC sessions.

The external RAM address used by the packet processor command is set by the SESSION # field in the Base Command Structure. The SESSION # field is an index into the external RAM. Each unit is an offset of 16 Kbytes starting at address location zero.

Separate encode and decode commands while using LZS compression may use the same SESSION # value. The memory use of compression and decompression do not overlap within the 16 Kbyte memory range.

However, MPPC requires separate session # values for encode and decode commands. Each half-duplex MPPC session requires a full 16 Kbytes.

## Processor Bus Interface

The 7902 CPU interfaces gluelessly to the MPC860 bus and with minimal external logic to the MPC8260 bus. Because there are some differences between the MPC860 and the MPC8260 bus interface, the bus mode interface is selected using the BMODE signal.

The MPC860 bus is a synchronous, burstable bus. The 7902 supports a subset of the transfer sizes available with the MPC860 controlled by the TSIZ[0-1] inputs.

The 7902 interface is similar in many respects to an SRAM. Data can be transferred between the CPU and the 7902 using standard load and store CPU operations or memory to memory DMA operations. It also supports a burst mode for faster read/write operations.

Other CPUs can be used with the 7902 provided the interface meets function and timing requirements (see Figure 42).

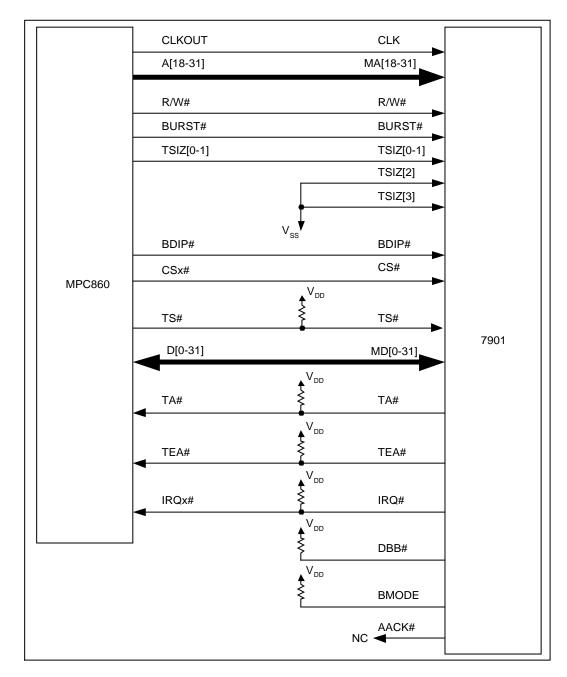

#### 7.1 MPC860/8260 Bus Interface

Since there are some differences between the MPC860 and MPC8260 buses, the BMODE input signal is provided to set the bus interface logic appropriately. When BMODE is active (high), the MPC860 mode is enabled.

#### 7.1.1 MPC860 Bus Interface

The 7902 incorporates the necessary logic to gluelessly interface to the MPC860. The 7902's interface logic supports a minimal subset of the MPC860's bus signals. These are the signals necessary to support both single-beat and burst data transfers.

Interfacing to the 7902 requires the use of one of the General Purpose Chipselect Machines (GPCMs) within the memory controller of the MPC860 to generate the chip select signal. The GPCM should be initialized for a 32-bit port size, no parity checking, burst, and external TA.

Figure 17 shows the interface connections between the MPC860 and the 7902.

#### 7.1.2 MPC8260 Bus Interface

With minimal external logic, the 7902 interfaces with the MPC8260 bus. For additional information, refer to the 7902 Application Note (AN-0023).

Figure 17. MPC860 / 7902 Interface

#### 7.2 Bus Transfer Overview – MPC860 Mode

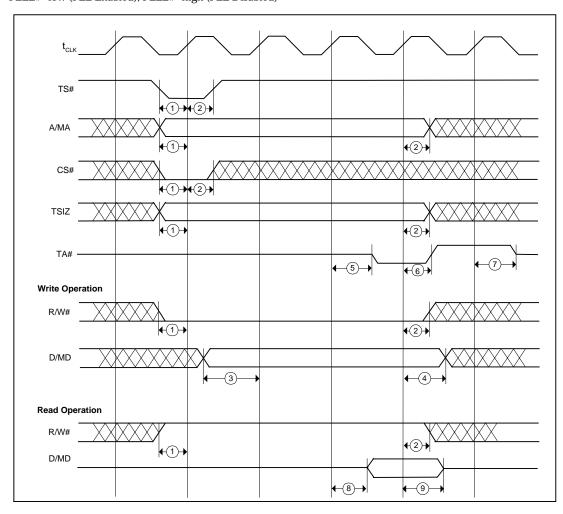

The data bus transfers information between the CPU and the 7902. Transfers are always performed using the full 32-bit width of the data bus.

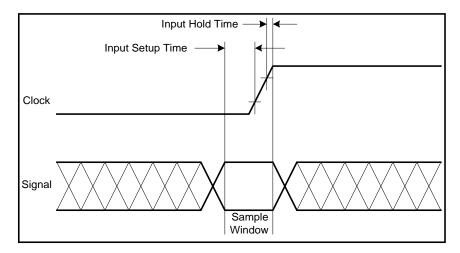

The 7902's address bus specifies the address for the transfer. Control signals indicate the beginning of the cycle and the type of cycle, as well as the address space and size of the transfer. The 7902 controls the cycle length with the TA# signal, which terminates the cycle. The strobe signal (TS#) indicates the validity of the address as well as the direction, type, and size of the transfer and provides timing information. Because the 7902's bus is synchronous, the bus and control input signals must be timed to set-up and hold times relative to the rising edge of the clock. The 7902 requires two wait states, so single-beat bus cycles are fixed at four clock cycles.

Furthermore, for all inputs, the 7902 latches the input's level during a sample window, shown in Figure 18, around the rising clock edge. To ensure that an input signal is recognized on a specific rising clock edge, that input must be stable during the sample window. If an input changes during the window, the level recognized by the 7902 is unpredictable; however, the 7902 always resolves the latched level to either a logical high or low before using it. For deterministic operation, all input signals must obey the protocols described in this chapter in addition to meeting input set up and hold times.

Figure 18. Input Sample Window

TSIZ[0-1] indicates the number of bytes to be transferred during an operand cycle (consisting of one or more bus cycles). These signals should be valid at the rising edge of the clock in which the transfer start signal (TS#) is asserted.

#### 7.2.1 Single-Beat Transfer

The 7902 supports the read and write of 4-byte single-beat transfers. The transfer must be word aligned (the two LSBs of the address bus must be 0) and TSIZ[0-1] driven appropriately, otherwise the TEA# signal is asserted to indicate a transfer error. The 7902 also has a fixed two-wait state requirement for read and write transfers regardless of the clock frequency.

The address transfer phase starts with the CPU asserting TS#. At the same time that TS# is asserted, CS# is also asserted and the address is placed on the address bus. TSIZ[0-1] is set appropriately for the transfer size and R/W# is driven to indicate the direction of the data transfer. TS# is only asserted for one cycle while all other signals are held valid (except CS#) by the CPU until the transfer is terminated. It is not required that CS# be held valid until the transfer is terminated although it is acceptable.

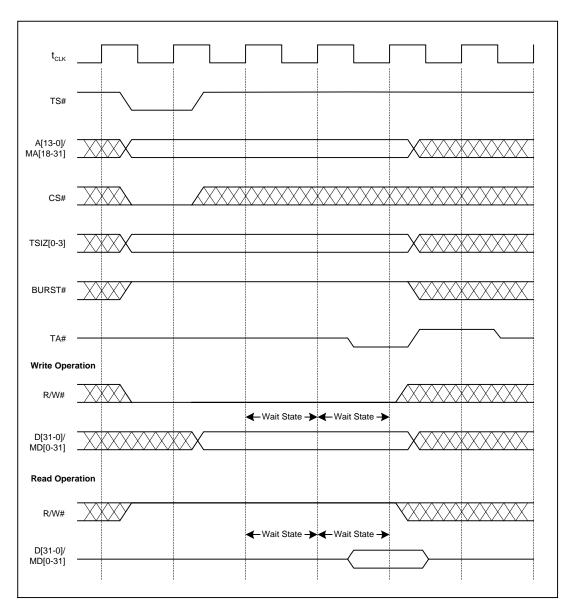

The data transfer starts one clock cycle after TS# has been asserted. At this time, the CPU drives the data bus with the data to be written if the transfer is a write; otherwise, the 7902 drives the data bus with the data to be read by the CPU. The 7902 has a fixed two-wait state requirement before the data can be latched for write operations or read for read operations. After two wait states TA# is asserted and the 7902 latches the data (write transfer) or indicates to the CPU that the data can be read (read transfer). TA# is then driven high for one clock and then released (tri-stated). Figure 19 shows the basic timing for a single-beat read/write transfer.

Figure 19. MPC860 Single-Beat Write and Read Timing

#### 7.2.2 Burst Transfers

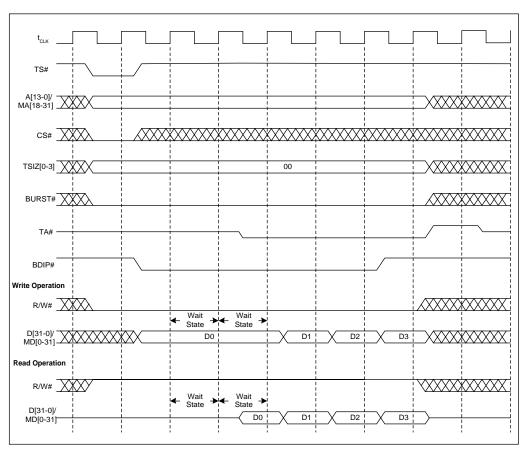

Burst transfers are similar in operation to a single-beat transfer. Single-beat transfers only support the read/write of 4-bytes while a burst transfer supports 16-bytes. Burst transfers must be aligned to a 16-byte memory boundary.

The CPU supplies the starting address that points to the first word and the 7902 samples/drives each word on the data bus until all four words are transferred.

Address and transfer attributes supplied by the CPU must remain stable (except CS#) during the entire transfer. Each word transfer on the data bus is terminated with the assertion of TA#; therefore, TA# is asserted for four clocks.

#### **Burst Write**

During the data transfer of a burst write cycle, the CPU sends data to the 7902. BDIP# is asserted to indicate that the CPU intends to continue the data transfer beyond the first word. When the 7902 receives the data word, it asserts TA# to indicate to the CPU that it is ready for the next word transfer. The CPU again drives the next data word and BDIP# remains asserted. If there is no more data to write, BDIP# is deasserted to indicate to the 7902 that the next data word is the last one in the burst write.

#### **Burst Read**

During the data transfer of a burst read cycle, the CPU receives data from the 7902. If the CPU needs more than one data word, it asserts BDIP#. The CPU deasserts BDIP# prior to the last word that is transferred. Thus, the 7902 stops driving new data at the rising clock edge after BDIP# goes high.

Since the 7902 only supports 32-bit transfers and 16-byte bursts, the burst must be 4 beats. See Figure 20 for the basic timing of read and write burst transfers.

Figure 20. MPC860 Burst Transfer Read and Write Timing

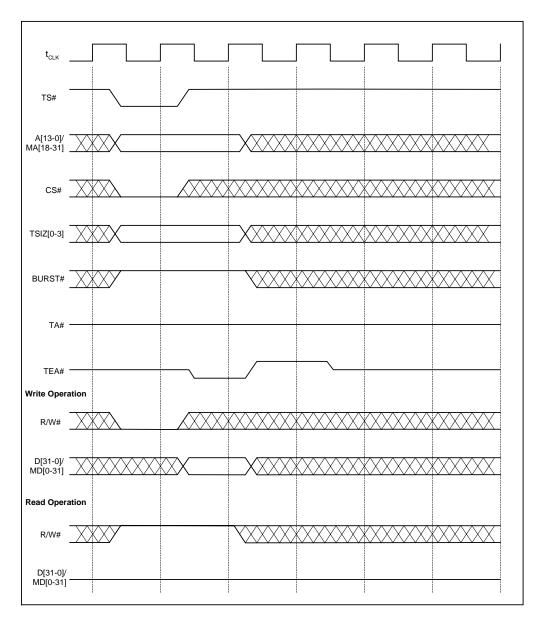

#### 7.2.3 Transfer Errors

The 7902 supports a subset of the transfer sizes and alignment available with the MPC860. See Figure 21 for the basic timing of TEA#. The transfer error acknowledge (TEA#) signal is used to indicate to the CPU when an unsupported transfer size is being attempted. If the transfer size being requested at the beginning of transfer (as set on the TSIZ[0-1] signals) is not a size supported (see Figure 22 for the sizes supported) then TEA# will be asserted. If the CPU attempts to do a data transfer that is not word aligned (A[0-1]/MA[31-30] are low) then TEA# will be asserted.

Figure 21. Transfer Error Acknowledge (TEA#) Timing

# 7.3 Processor Bus Interface Signal Descriptions

#### 7.3.1 Bus Interface Clock

The CLK input signal drives the Random Number Generator, Public Key, and Packet Engine as well as the synchronous bus interface. The MPC860/8260 processors' bus clock output must be tied to the 7902's CLK input for proper operation of the Processor Bus Interface.

#### 7.3.2 Address Bus (A[13-0]/MA[18-31])

The address bus signals have been given dual names to clearly indicate the correct connection to the CPU being used. The MA[18-31] signals are used with processors supporting the MPC860/8260 bit numbering conventions and the A[13-0] signals are used with other processors.

The address bus consists of 14 signals (A[13-0]/MA[18-31]) that are inputs. A[0]/MA[31] is the LSB and A[13]/MA[18] is the MSB of the address. The value on the bus specifies the physical address of the register or internal memory location being accessed. The address bus is sampled when TS# and CS# are asserted. The address must be held on the bus until the cycle is complete as indicated by the 7902 asserting TA#.

The 7902 only supports word (32-bit) aligned data transfers so A[0-1]/MA[31-30] must always be low during a data transfer. If both bits are not low, then TEA# is asserted to indicate a transfer error.

#### 7.3.3 Data Bus (D[31-0]/DM[31-0])

The data bus signals have been given dual names to clearly indicate the correct connection to the CPU being used. The MD[0-31] signals are used with processors supporting the MPC860/8260 bit numbering conventions and the D[31-0] signals are used with all other processors.

The data bus consists of 32 signals (D[31-0]/MD[0-31]) that are both inputs and outputs. D[0]/MD[31] is the LSB and D[31]/MD[0] is the MSB of the data. The data bus is normally in the input mode except during a read operation.

During a write operation the data is latched on the positive edge of the clock when TA# is asserted.

During a read operation, two clock cycles after TS# is asserted, the data bus is put in the output mode and the data is placed on the bus. The data is held valid while TA# is asserted and then the data bus is placed back in the input mode.

If a transfer error is detected the TEA# signal is asserted and the transfer cycle is terminated. If a transfer error occurs during a read operation, the data bus stays in the input mode, since no data is output.

#### 7.3.4 Burst Transfer (BURST#)

The burst transfer signal (BURST#) is an input. This signal is asserted at the beginning of a bus cycle (along with the address) to indicate that the data transfer is a burst transfer. In the MPC860 mode, a 16-byte burst is initiated when BURST# is low. The TSIZ[1-0] signals must be driven according to Figure 22 for proper burst transfer operation.

## 7.3.5 Transfer Size (TSIZ[0-3])

The transfer size signals (TSIZ[0-3]) are inputs and indicate the size of the data transfer for the current transaction. A subset of the various transfer sizes available with the MPC860 are supported as shown in Figure 22. TEA# is asserted when the transfer size for the current transaction is not supported.

| BURST# | TSIZ[0-1] | Transfer Size    |

|--------|-----------|------------------|

| 1      | 00        | Word (4 bytes)   |

| 0      | 00        | Burst (16 bytes) |

**Note:** In the MPC860 mode, TSIZ[3-2] are not used and should be tied low to prevent the input buffers from floating.

Figure 22. Transfer Sizes Supported (MPC860 Mode)

#### 7.3.6 Chip Select (CS#)

The chip select signal (CS#) is an input and indicates when the CPU is requesting a transfer. CS# is sampled on the positive edge of the clock when TS# is asserted. If CS# is asserted, a data transfer is initiated with the direction based on the state of the read/write (R/W#) signal.

#### 7.3.7 Transfer Start (TS#)

The transfer start signal (TS#) is an input and indicates the beginning of a transfer cycle. The TS# signal is a shared line among other devices on the bus and must be pulled high with a resistor. TS# is sampled on the positive edge of each clock. When TS# is asserted, CS# is sampled to determine if a transfer is being requested by the CPU. If CS# is asserted, then a data transfer is initiated with the direction based on the state of the read/write (R/W#) signal.

#### 7.3.8 Transfer Acknowledge (TA#)

The transfer acknowledge signal (TA#) is a tri-stateable output and indicates the end of a data transfer. The TA# signal is a shared line among other devices on the bus and must be pulled high with a resistor. It is in a tri-state mode unless it is being driven at the end of the data transfer. At the end of a data transfer, the TA# line is driven low for one clock to indicate to the CPU that the transfer is complete. After TA# has been driven low for one clock, it is driven high for one clock and then it is released (tri-stated). If a transfer error occurred and TEA# was asserted, TA# is not asserted.

#### 7.3.9 Address Acknowledge (AACK#)

The address acknowledge signal (AACK#) is only used in the MPC8260 mode and is a tri-stateable output. It should be left open when the MPC860 mode is used.

#### 7.3.10 Data Bus Busy (DBB#)

The data bus busy signal (DBB#) is an input and is only used in the MPC8260 mode. It must be tied high when the MPC860 mode is used.

#### 7.3.11 Read/Write (R/W#)

The read/write signal (RW#) is an input and indicates the direction of the data flow for data transfers. R/W# is sampled on the positive edge of the clock when TS# is asserted and must be held in that state during the entire transfer. If R/W# is driven high, a read data transfer is in progress; if it is low, a write transfer is in progress.

#### 7.3.12 Transfer Error Acknowledge (TEA#)

The transfer error acknowledge signal (TEA#) is an output that indicates to the CPU when an unsupported data transfer is requested (see Figure 22 for the transfer sizes supported). TEA# is asserted if an unsupported transfer size is attempted or if a non-word aligned data transfer is attempted (A[0-1]/MA[31-30] are not low). If a transfer error occurs, TEA# is asserted for one clock starting on the positive edge of the bus clock after TS# is sampled low.

# 7.3.13 Burst Data In Progress/Partial Data Valid (BDIP#/PSDVAL#)

In the MPC860 mode, this pin is the BDIP# signal and is an input indicating that a burst data transfer is in progress. BDIP# is sampled on the positive edge of the clock when TS# and BURST# are asserted. It must remain asserted for the duration of the burst data, and then be deasserted prior to the last data word.

#### 7.3.14 Bus Mode (BMODE)

The bus mode signal (BMODE) is an input and is used to set the bus interface mode. When BMODE is high, the MPC860 bus interface is used. When BMODE is low, the MPC8260 bus interface is used.

${f Note:}\,$  If another processor is used, it is recommended that BMODE be tied high and the MPC860 bus used.

#### 7.3.15 Interrupt Request (IRQ#)

The interrupt request signal (IRQ#) is a tri-stateable output and indicates an interrupt request. It should be pulled high with a resistor. It is in a tri-state mode unless it is being driven low indicating that an enabled interrupt condition has been met. The IRQ# signal remains low until the status bit for the event that caused the interrupt is cleared.

# 8 General Registers

# 8.1 General Configuration Register

| 31  | 30                                                                                                                                                                                                                                                                                                                                   | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22   | 21   | 20  | 19 | 18 | 17 | 16    | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | <br>4 | 3 | 2 | 1 | 0     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|------|------|-----|----|----|----|-------|-----|----|----|----|----|----|---|---|---|---|---|-------|---|---|---|-------|

|     |                                                                                                                                                                                                                                                                                                                                      |    |    |    |    |    |    |    |      |      |     |    |    | re | eser\ | red |    |    |    |    |    |   |   |   |   |   |       |   |   |   | Reset |

|     | Note: Bit 0 is the least-significant bit. Reserved bits must be written with 0s and ignored when read.  Addr: 0x0004-0x0007 Use this register to configure general 7902 functions.                                                                                                                                                   |    |    |    |    |    |    |    |      |      |     |    |    |    |       |     |    |    |    |    |    |   |   |   |   |   |       |   |   |   |       |

| Fie | ld                                                                                                                                                                                                                                                                                                                                   |    |    |    |    |    |    | D  | esci | ript | ion |    |    |    |       |     |    |    |    |    |    |   |   |   |   |   |       |   |   |   |       |

| RES | Set this bit to 1 to reset the device. When read, this bit is a 1 while the device is performing a reset operation (either a hardware or software reset). The device should not be accessed while this bit is a 1 (except to read the General Configuration Register). After the reset operation is complete, this bit returns to 0. |    |    |    |    |    |    |    |      |      |     |    |    |    |       |     |    |    |    |    |    |   |   |   |   |   |       |   |   |   |       |

# 8.2 Chip ID Register

| 31 30 29 28 27 26 25 24                                                                                                                  | 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                                                                                                                       |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Proc                                                                                                                                     | uct ID Revision ID                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Note: Bit 0 is the least-significa                                                                                                       | ant bit. Reserved bits must be written with 0s and ignored when read.                                                                                                                               |  |  |  |  |  |  |  |  |

| Addr: 0x0008-0x000B                                                                                                                      | This register reports the ChipID. The ChipID uniquely identifies this device. All fields are read-only.                                                                                             |  |  |  |  |  |  |  |  |

| Field                                                                                                                                    | Description                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| The Product ID value represents the identification number for the 7902 dev and will not change. The Product ID of this device is 0x0004. |                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| REVISIONID                                                                                                                               | The Revision ID value represents the actual revision number for the 7902. The Revision ID of this device is 0x0000. For this particular device, 0x0000 represents the first version of this device. |  |  |  |  |  |  |  |  |

# Public Key Engine & Random Number Generator

#### 9.1 Overview

9

Public key operations require CPU-intensive math calculations. The Public Key engine reduces the load on the CPU by performing the arithmetic in hardware.

Public key operations also require a cryptographic-quality random number for a high level of security. The random number generator provides an unpredictable number, and with minimal CPU processing a cryptographic-quality random number can be generated.

#### 9.2 Random Number Generator

The Random Number Generator is based on internal free-running oscillators whose frequencies drift relative to each other and to the internal clock of the 7902. The phase relation of these signals is unpredictable, and this is used to create entropy to generate a random bit stream.

The output of the random number generator only serves as the raw input to a cryptographic process that generates cryptographically secure random numbers. The process required is beyond the scope of this datasheet. Source code of the software required to perform this process is available from Hi/fn.

The Random Number Generator must be enabled after each reset by setting the RNG ENABLE bit in the Public Configuration register. Once enabled, the generator begins producing a random bit stream. It is important to note that the data obtained from the first read of the RNG data register after a reset should be discarded.

#### 9.3 Public Key Data Movement

The Public Key engine assists in performing CPU-intensive modular arithmetic, including modular exponentiation. The user first sets configuration registers, and then issues a starting command and opcode. The CPU determines whether the unit is idle or busy by checking the Public Status register.

Public Key data movement is outlined below:

#### Set up Source data

- 1. Place source operands in memory.

- 2. Set the public key base address pointer.

- 3. Set the public key operand length register.

#### **Issue a Command**

4. Set the Public Operation Register. Setting the Public Operation Register starts the Public Key engine.

#### **Read Out Result and Destination Data**

- 5. When the Public Key engine has completed, the Public Done bit in the Public Status Register is set and an interrupt is generated if the interrupt enable bit is set.

- 6. Read the result data from the internal memory.

- 7. Repeat (go to step 1).

# 9.4 Operations

The following table illustrates the operations supported by the Public Key engine. All operands and results must be of length MODLEN unless otherwise specified.

| Operation        | Description   |

|------------------|---------------|

| Add              | A + B         |

| Add w/Carry      | A + B + Carry |

| Subtract         | A – B         |

| Subtract w/Carry | A – B – Carry |

| Mod Add          | (A + B) mod M |

| Mod Sub          | (A – B) mod M |

| Inc A            | A + 1         |

| Dec A            | A – 1         |

| Mult             | A * B         |

| Mod Mult         | (A * B) mod M |

| Mod Red          | A mod M       |

| Mod Exp          | (A ^ B) mod M |

Figure 23. Public Key Operations

# 9.5 Operands

All operations use one, two, or three operands. These are labeled A, B, and M for operand A, operand B, and the modulus. Each of these operands are actually an array of elements in internal memory. The host sets the base address of each array by configuring the A, B, and M fields in the Public Operation Register. The values written to the A, B, and M fields are offsets into internal memory, relative to the PUBLIC BASE ADDRESS field set in the Public Base Address Register.

#### 9.5.1 Public Key Operand Storage

Operands are stored in the internal memory. Each operand is broken up into a series of 32-bit values. The least significant 32-bit value is stored in the lowest address location, and the most significant 32-bit value is stored in the highest address location.

Because data is always transferred as 32-bit values, the byte-endianess of system memory does not affect 7902 public key operands. 32-bit values are always presented on the CPU bus in proper byte order.

For example, if the Public Base Address is set to 0x3000, and the A Offset is set to 0x0000, operand A with a value of 0x0001020304050607 would be stored in internal memory as shown in Figure 24.

| Internal Address | 32-Bit Value |

|------------------|--------------|

| 0x3000           | 0x04050607   |

| 0x3004           | 0x00010203   |

Figure 24. Public Key Operand Storage in Internal Memory

| Field                  | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUBLIC BASE<br>ADDRESS | Base address of Public Key engine. Points anywhere in the internal memory. It must be 512-byte aligned. All other public key offsets are relative to this base address.                                                                                                                                                                                                                        |

| A OFFSET               | Offset of operand A from Public Base address. (Units of 64 bytes).                                                                                                                                                                                                                                                                                                                             |

| B OFFSET               | Offset of operand B from Public Base address. (Units of 64 bytes).                                                                                                                                                                                                                                                                                                                             |

| M OFFSET               | Offset of operand M from Public Base Address. (Units of 64 bytes).                                                                                                                                                                                                                                                                                                                             |

| MODLEN                 | Length of modulus (MODLEN=2 to 64). Actual modulus length in bits is MODLEN*32. Actual modulus length must be between 64 and 2,048 bits inclusive. The most significant bit of the <i>value</i> of the modulus (not the length) must be a 1.                                                                                                                                                   |

| REDLEN                 | Length of reducend. Actual reducend length in bits is (REDLEN+2)*MODLEN*32 (REDLEN = 0 to 13). Actual reducend length must be less than or equal to 2,048 bits or 15* MODLEN*32, (REDLEN=13), whichever is smaller. The minimum reducend length is 2* MODLEN*32 (REDLEN=0). There are no restrictions regarding the most significant bit of the <i>value</i> (not the length) of the reducend. |

| EXPLEN                 | Length of exponent. Actual exponent length in bits is EXPLEN+1. The minimum actual exponent length must be 2 (EXPLEN=1). The maximum actual exponent length must be less than or equal to 2,048 bits (EXPLEN=2,047) or MODLEN*32 (EXPLEN=MODLEN*32-1), whichever is smaller. The most-significant bit of the <i>value</i> of the exponent (not the length) must be a 1.                        |

Figure 25. Operand Pointers and Offsets

Some example values for pointers and offsets are shown in Figure 26.

| Field                  | Value of Field | Actual Bas Address in<br>Internal Memory |

|------------------------|----------------|------------------------------------------|

| PUBLIC BASE<br>ADDRESS | 0x3000         | 0x3000                                   |

| A OFFSET               | 0x0            | 0x3000                                   |

| B OFFSET               | 0x4            | 0x3100                                   |

| M OFFSET               | 0x8            | 0x3200                                   |

Figure 26. Field Values and Memory Locations

Each operand is an array of elements in internal memory. Each element has a size of MODLEN, as configured by the host in the Public Configuration Register. The number of elements used in each array varies by operation. This is shown in Figure 27.

#### Notes:

- 1. The results of each operation are stored after operand B, in B(1) and in the case of the multiply operation, B(2).

- 2. Mod Red operations destroy the contents of operand A.

- 3. Operands, modulus, result RAM, or scratch pad should not be modified while the Public Key engine is running.

| Operation        | Operand A   | Operand B | Operand M <sup>2</sup> | Result | Scratch                   |

|------------------|-------------|-----------|------------------------|--------|---------------------------|

| Add              | A(0)        | B(0)      |                        | B(1)   |                           |

| Add w/Carry      | A(0)        | B(0)      |                        | B(1)   |                           |

| Subtract         | A(0)        | B(0)      |                        | B(1)   |                           |

| Subtract w/Carry | A(0)        | B(0)      |                        | B(1)   |                           |

| Mod Add          | A(0)        | B(0)      | M(0)                   | B(1)   |                           |

| Mod Sub          | A(0)        | B(0)      | M(0)                   | B(1)   |                           |

| Inc A            | A(0)        |           |                        | B(1)   |                           |

| Dec A            | A(0)        |           |                        | B(1)   |                           |

| Mult             | A(0)        | B(0)      |                        | B(2-1) |                           |

| Mod Mult         | A(0)        | B(0)      | M(1-0)                 | B(1)   | B(2), M(4-2)              |

| Mod Red          | A(14-0)3, 4 |           | M(1-0)                 | B(1)   | B(2), M(4-2)              |

| Mod Exp          | A(0)        | B(0)      | M(1-0)                 | B(1)   | B(2), M(4-2) <sup>1</sup> |

Note 1: Host must clear M(2) prior to starting Mod Exp operation.

**Note 2:** M(1) is used to store the reciprocal of M(0). The MSB of M(0) must be a 1.

**Note 3:** Operand A is of size, in bytes, [RedLen+2]\*[ModLen]\*4, up to a maximum of 2048 bits. The value of RedLen is 0 to 13.

Note 4: Mod Red operations destroy the contents of operand A.

#### **General Notes:**

- 1. Blank entries are free for system use.

- 2. Byte address of references relative to internal memory:  $A(n)=[A Offset]^*64+n^*[ModLen]^*4$ ,  $B(n)=[B Offset]^*64+n^*[ModLen]^*4$ ,  $M(n)=[M Offset]^*64+n^*[ModLen]^*4$ .

Figure 27. Operand Use for Each Operation

#### 9.5.2 Public Key Memory Usage

Individual memory chunk addresses can be calculated using the following equations:

A(n) = BA + A + n\*chunksize B(n) = BA + B + n\*chunksizeM(n) = BA + M + n\*chunksize

Note: All quantities are in bytes.

#### Where:

chunksize = modulus size for current operation, 4-byte granular  $BA = Base \ Address \ (512-byte \ granular)$   $A = A \ Offset \ (64-byte \ granular)$   $B = B \ Offset \ (64-byte \ granular)$   $M = M \ Offset \ (64-byte \ granular)$   $A(n) = A \ operand \ memory \ chunk \ \#n \ address$   $B(n) = B \ operand \ memory \ chunk \ \#n \ address$   $M(n) = M \ operand \ memory \ chunk \ \#n \ address$

Note: All quantities are in bytes.

The maximum amount of memory used can be calculated using the following equation:

```

mem used = 256 + \text{max} chunksize * 8

```

#### Where:

mem\_used = size of memory space reserved for public key operations max\_chunksize = maximum supported modulus size, rounded up to a multiple of 64-bytes

#### **General Purpose Example**

This example sets the pointers to use the upper address space of the internal memory. In this example, it is assumed that the maximum key length to be supported is 1024 bits, so the maximum operand length is 1024 bits. A max\_chunksize of 1024 bits is used to minimize the amount of internal memory allocated for public key operations. Max\_chunksize can be larger than the maximum key length to be supported. Since internal memory is limited and a shared resource with the packet engine, the most efficient use is realized when max\_chunksize equals the maximum key length.

The equations to be used to determine the addresses are:

```

start_addr = max_addr - mem_used

BA = start_addr (rounded down to the nearest 512-byte)

A = start_addr - BA

B = A + 256

M = A + 256 + 3*max_chunksize

```

#### Where:

$max_addr = 16384$ start\_addr = lowest address that the public key engine will use mem\_used = size of memory space reserved for Public Key engine use BA = Base Address (512-byte granular) A = A Offset (64-byte granular)B = B Offset (64-byte granular) M = M Offset (64-byte granular) With substitution we get: mem\_used = 256 + max\_chunksize \* 8 (**Note:** all units in bytes)  $mem\_used = 256 + (1024 bits / 8 bits/byte) * 8$  $mem\_used = 1280 \text{ or } 0x500 \text{ bytes}$  $start\_addr = max\_addr - mem\_used$  $start\_addr = 0x4000 - 0x500$  $start_addr = 0x3B00$ BA = start\_addr (rounded down to the nearest 512-byte) BA = 0x3A00 $A = start \ addr - BA$ A = 0x3B00 - 0x3A00A = 256 or 0x100B = A + 256B = 256 + 256B = 512 or 0x200 $M = A + 256 + 3*max_chunksize$

M = 256 + 256 + 3\*(1024 bits/byte)

M = 896 or 0x380

Figure 28. Public Key Memory Use General Purpose Example

### 9.6 Reciprocal Calculations

The reciprocal is the key to performing modular reduction with a hardware multiplier (otherwise a divide function is required). Normally a reciprocal is thought of as the multiplicative inverse of a value:

if a is the reciprocal of x, then a \* x = 1

where a is any rational number.

In the integer realm of public key cryptography, a reciprocal has a slightly different definition—both the modulus and the reciprocal must be integers. This is done by choosing an appropriate value for the '1' normally associated with multiplicative inverses. For example, if 16-bit values are being dealt with:

$$x = 0xABCD$$

$a = ?$

and a 16-bit reciprocal is wanted, the '1' is represented by a one followed by 32 zeros. The reciprocal is computed by:

a = 0x100000000/x = 0x100000000/0xABCD = 0x17D77

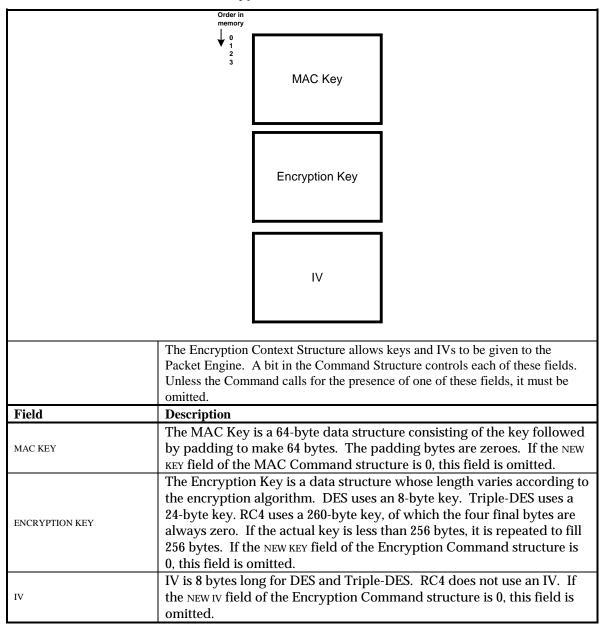

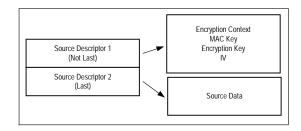

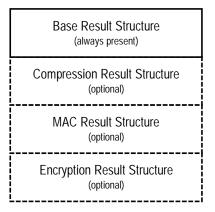

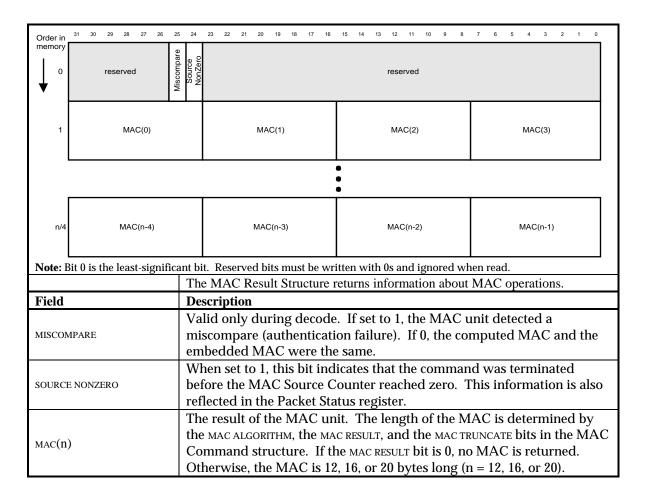

The result of integer division is just the integer quotient—any remainder is ignored. This reciprocal is an approximation, since a \* x is somewhat less than 0x100000000.