SCAS127B - MARCH 1990 - REVISED APRIL 1996

- **Members of the Texas Instruments** Widebus™ Family

- Inputs Are TTL-Voltage Compatible

- **Independent Registers for A and B Buses**

- **Multiplexed Real-Time and Stored Data**

- Flow-Through Architecture Optimizes **PCB Layout**

- Distributed V<sub>CC</sub> and GND Pin Configuration **Minimizes High-Speed Switching Noise**

- **EPIC™** (Enhanced-Performance Implanted CMOS) 1-µm Process

- 500-mA Typical Latch-Up Immunity at

- Package Options Include Plastic 300-mil Shrink Small-Outline (DL) Packages Using 25-mil Center-to-Center Pin Spacings and 380-mil Fine-Pitch Ceramic Flat (WD) Packages Using 25-mil Center-to-Center **Pin Spacings**

### description

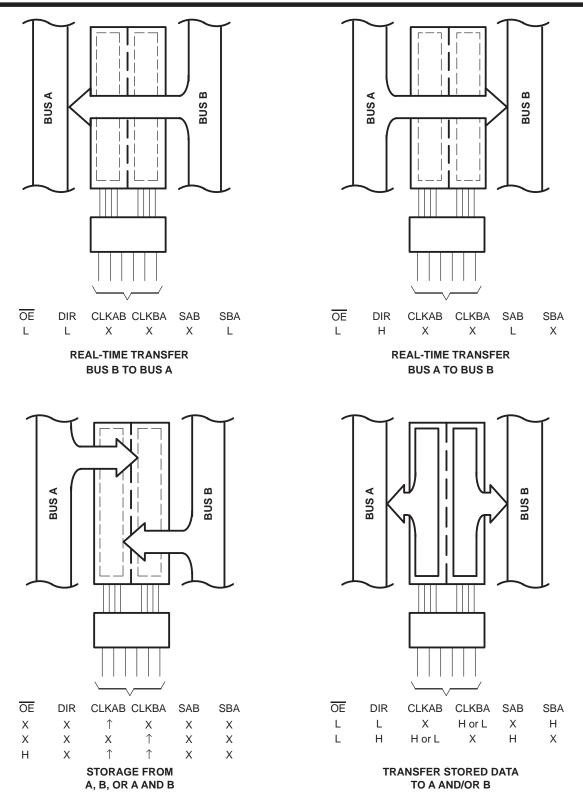

The 'ACT16646 are 16-bit bus transceivers consisting of D-type flip-flops and control circuitry with 3-state outputs arranged for multiplexed transmission of data directly from the data bus or from the internal storage registers. The devices can be used as two 8-bit transceivers or one 16-bit transceiver. Data on the A or B bus is clocked into the registers on the low-to-high transition of the appropriate clock (CLKAB or CLKBA) input. Figure 1 illustrates the four fundamental busmanagement functions that can be performed with the bus transceivers and registers.

**54ACT16646...WD PACKAGE** 74ACT16646...DL PACKAGE (TOP VIEW)

|                   |    | U |    | հ . <del></del>     |

|-------------------|----|---|----|---------------------|

| 1DIR              | 1  |   |    | 1 <u>OE</u>         |

| 1CLKAB            | 2  |   | 55 | 1CLKBA              |

| 1SAB [            | 3  |   | 54 | ] 1SBA              |

| GND [             | 4  |   | 53 | ] GND               |

| 1A1 [             | 5  |   | 52 | ] 1B1               |

| 1A2 [             | 6  |   | 51 | ] 1B2               |

| V <sub>CC</sub> [ | 7  |   | 50 | ] v <sub>cc</sub>   |

| 1A3 [             | 8  |   | 49 | ] 1B3               |

| 1A4 [             | 9  |   | 48 | ] 1B4               |

| 1A5 [             | 10 |   | 47 | ] 1B5               |

| GND [             | 11 |   | 46 | ] GND               |

| 1A6 [             | 12 |   | 45 | ] 1B6               |

| 1A7 [             | 13 |   | 44 | ] 1B7               |

| 1A8 [             | 14 |   | 43 | ] 1B8               |

| 2A1 [             | 15 |   | 42 | ] 2B1               |

| 2A2 [             | 16 |   | 41 | ] 2B2               |

| 2A3 [             | 17 |   | 40 | ] 2B3               |

| GND [             | 18 |   | 39 | ] GND               |

| 2A4 [             | 19 |   | 38 | ] 2B4               |

| 2A5 [             | 20 |   | 37 | ] 2B5               |

| 2A6 [             | 21 |   | 36 | ] 2B6               |

| V <sub>CC</sub> [ | 22 |   | 35 | ] v <sub>cc</sub>   |

| 2A7 [             | 23 |   | 34 | ] 2B7               |

| 2A8 [             | 24 |   | 33 | ] 2B8               |

| GND [             | 25 |   | 32 | ] GND               |

| 2SAB [            | 26 |   | 31 | ] 2SBA              |

| 2CLKAB [          | 27 |   | 30 | 2CLKBA              |

| 2DIR [            | 28 |   | 29 | ] 2 <mark>OE</mark> |

|                   |    |   |    |                     |

Output-enable (OE) and direction-control (DIR) inputs are provided to control the transceiver functions. In the transceiver mode, data present at the high-impedance port may be stored in either register or in both. The select controls (SAB and SBA) can multiplex stored and real-time (transparent mode) data. The circuitry used for select control eliminates the typical decoding glitch that occurs in a multiplexer during the transition between stored and real-time data. DIR determines which bus receives data when  $\overline{\mathsf{OE}}$  is low. In the isolation mode ( $\overline{\mathsf{OE}}$ high), A data may be stored in one register and/or B data may be stored in the other register.

When an output function is disabled, the input function is still enabled and may be used to store and transmit data. Only one of the two buses, A or B, may be driven at a time.

The 74ACT16646 is packaged in TI's shrink small-outline package, which provides twice the functionality of standard small-outline packages in the same printed-circuit-board area.

The 54ACT16646 is characterized for operation over the full military temperature range of -55°C to 125°C. The 74ACT16646 is characterized for operation from -40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC and Widebus are trademarks of Texas Instruments Incorporated.

SCAS127B - MARCH 1990 - REVISED APRIL 1996

Figure 1. Bus-Management Functions

### 54ACT16646, 74ACT16646 16-BIT BUS TRANSCEIVERS AND REGISTERS WITH 3-STATE OUTPUTS

SCAS127B - MARCH 1990 - REVISED APRIL 1996

#### **FUNCTION TABLE**

|    |     | INP    | UTS    |     |     | DATA        | \ I/O†      | OPERATION OR FUNCTION               |

|----|-----|--------|--------|-----|-----|-------------|-------------|-------------------------------------|

| OE | DIR | CLKAB  | CLKBA  | SAB | SBA | A1-A8       | B1-B8       | OPERATION OR FUNCTION               |

| Х  | Х   | 1      | Х      | Х   | Х   | Input       | Unspecified | Store A, B unspecified <sup>†</sup> |

| X  | Χ   | Χ      | 1      | Χ   | Χ   | Unspecified | Input       | Store B, A unspecified <sup>†</sup> |

| Н  | Х   | 1      | 1      | Х   | Х   | Input       | Input       | Store A and B data                  |

| Н  | Χ   | H or L | H or L | Χ   | X   | Input       | Input       | Isolation, hold storage             |

| L  | L   | Х      | Х      | Χ   | L   | Output      | Input       | Real-time B data to A bus           |

| L  | L   | Χ      | H or L | Χ   | Н   | Output      | Input       | Stored B data to A bus              |

| L  | Н   | Х      | Х      | L   | Х   | Input       | Output      | Real-time A data to B Bus           |

| L  | Н   | H or L | X      | Н   | X   | Input       | Output      | Stored A data to bus                |

<sup>†</sup> The data-output functions may be enabled or disabled by various signals at OE or DIR. Data-input functions are always enabled, i.e., data at the bus terminals is stored on every low-to-high transition of the clock inputs.

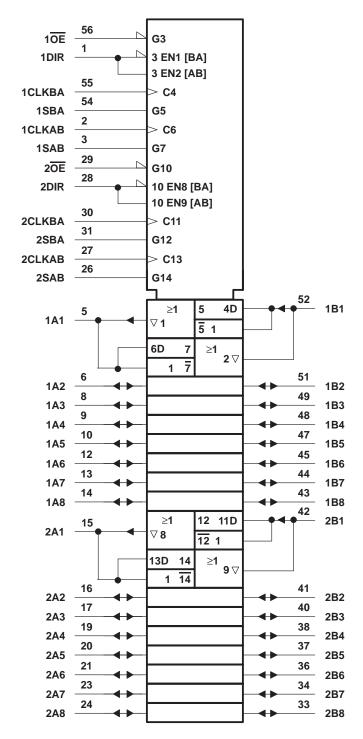

### logic symbol†

<sup>&</sup>lt;sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

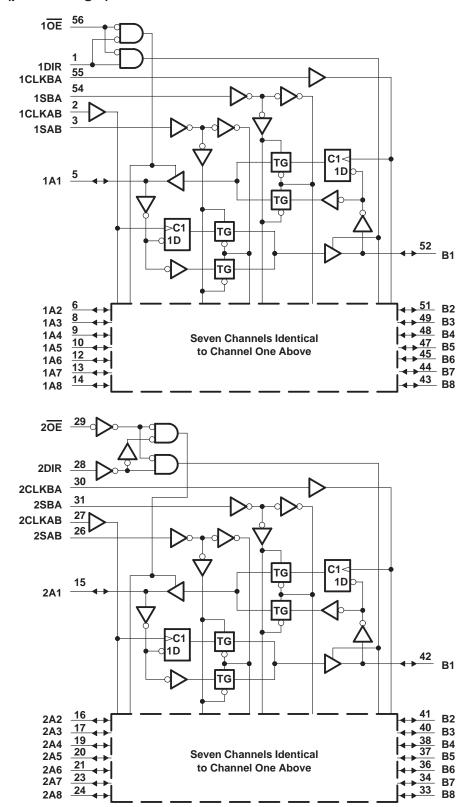

### logic diagram (positive logic)

### 54ACT16646, 74ACT16646 16-BIT BUS TRANSCEIVERS AND REGISTERS WITH 3-STATE OUTPUTS

SCAS127B - MARCH 1990 - REVISED APRIL 1996

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                                                              | $-0.5 \ V$ to $7 \ V$           |

|----------------------------------------------------------------------------------------------------|---------------------------------|

| Input voltage range, V <sub>I</sub> (see Note 1)                                                   | 5 V to V <sub>CC</sub> + 0.5 V  |

| Output voltage range, V <sub>O</sub> (see Note 1)–0.                                               | 5 V to V <sub>CC</sub> + 0.5 V  |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ )                                      | $\dots \dots \pm 20 \text{ mA}$ |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> )    | ±50 mA                          |

| Continuous output current, $I_O$ ( $V_O = 0$ to $V_{CC}$ )                                         | ±50 mA                          |

| Continuous current through V <sub>CC</sub> or GND                                                  | ±400 mA                         |

| Maximum package power dissipation at T <sub>A</sub> = 55°C (in still air) (see Note 2): DL package | 1.4 W                           |

| Storage temperature range, T <sub>Stg</sub>                                                        | 65°C to 150°C                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions (see Note 3)

|                 |                                    | 54ACT16646 |     | 74ACT | UNIT |      |

|-----------------|------------------------------------|------------|-----|-------|------|------|

|                 |                                    | MIN        | MAX | MIN   | MAX  | UNIT |

| Vcc             | Supply voltage (see Note 4)        | 4.5        | 5.5 | 4.5   | 5.5  | V    |

| VIH             | High-level input voltage           | 2          | 3   | 2     |      | V    |

| V <sub>IL</sub> | Low-level input voltage            |            | 0.8 |       | 0.8  | V    |

| ٧ <sub>I</sub>  | Input voltage                      | 0          | Vcc | 0     | VCC  | V    |

| VO              | Output voltage                     | 0          | Vcc | 0     | VCC  | V    |

| IOH             | High-level output current          | 2          | -24 |       | -24  | mA   |

| lOL             | Low-level output current           | 30/        | 24  |       | 24   | mA   |

| Δt/Δν           | Input transition rise or fall rate | 0          | 10  | 0     | 10   | ns/V |

| TA              | Operating free-air temperature     | -55        | 125 | -40   | 85   | °C   |

NOTES: 3. Unused inputs must be held high or low to prevent them from floating.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

<sup>2.</sup> The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils.

<sup>4.</sup> All V<sub>CC</sub> and GND pins must be connected to the proper voltage power supply.

SCAS127B - MARCH 1990 - REVISED APRIL 1996

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                           | TEST CONDITIONS                                               | V     | T,   | д = 25°C |      | 54ACT | 16646 | 74ACT | 16646 | UNIT |

|-----------------|---------------------------|---------------------------------------------------------------|-------|------|----------|------|-------|-------|-------|-------|------|

| PAI             | RAMETER                   | TEST CONDITIONS                                               | Vcc   | MIN  | TYP      | MAX  | MIN   | MAX   | MIN   | MAX   | UNII |

|                 |                           | Jan - 50 nA                                                   | 4.5 V | 4.4  |          |      | 4.4   |       | 4.4   |       |      |

|                 |                           | IOH = -50 μA                                                  | 5.5 V | 5.4  |          |      | 5.4   |       | 5.4   |       |      |

|                 |                           | I <sub>OH</sub> = -24 mA                                      | 4.5 V | 3.94 |          |      | 3.7   |       | 3.8   |       | V    |

| VOH             |                           | 10H = -24 IIIA                                                | 5.5 V | 4.94 |          |      | 4.7   |       | 4.8   |       | V    |

|                 |                           | $I_{OH} = -50 \text{ mA}^{\dagger}$                           | 5.5 V |      |          |      | 3.85  |       |       |       |      |

|                 |                           | $I_{OH} = -75 \text{ mA}^{\dagger}$                           | 5.5 V |      |          |      |       |       | 3.85  |       |      |

|                 |                           | I 50A                                                         | 4.5 V |      |          | 0.1  |       | 0.1   |       | 0.1   |      |

|                 |                           | I <sub>OL</sub> = 50 μA                                       | 5.5 V |      |          | 0.1  |       | 0.1   |       | 0.1   |      |

| <b> </b>        |                           | lo 24 mA                                                      | 4.5 V |      |          | 0.36 | 4     | 0.5   |       | 0.44  |      |

| VOL             |                           | I <sub>OL</sub> = 24 mA                                       | 5.5 V |      |          | 0.36 | 9     | 0.5   |       | 0.44  | V    |

|                 |                           | I <sub>OL</sub> = 50 mA <sup>†</sup>                          | 5.5 V |      |          |      | 90    | 1.65  |       |       |      |

|                 |                           | $I_{OL} = 75 \text{ mA}^{\dagger}$                            | 5.5 V |      |          |      | D'A   |       |       | 1.65  |      |

| Ιį              | Control inputs            | V <sub>I</sub> = V <sub>CC</sub> or GND                       | 5.5 V |      |          | ±0.1 |       | ±1    |       | ±1    | μΑ   |

| loz             | A or B ports <sup>‡</sup> | $V_O = V_{CC}$ or GND                                         | 5.5 V |      |          | ±0.5 |       | ±10   |       | ±5    | μΑ   |

| Icc             | •                         | $V_I = V_{CC}$ or GND, $I_O = 0$                              | 5.5 V |      |          | 8    |       | 160   |       | 80    | μΑ   |

| Δlcc§           |                           | One input at 3.4 V,<br>Other inputs at GND or V <sub>CC</sub> | 5.5 V |      |          | 0.9  |       | 1     |       | 1     | mA   |

| Ci              | Control inputs            | $V_I = V_{CC}$ or GND                                         | 5 V   |      | 4        |      |       |       |       |       | pF   |

| C <sub>io</sub> | A or B ports              | $V_O = V_{CC}$ or GND                                         | 5 V   |      | 12       |      |       |       |       |       | pF   |

<sup>†</sup> Not more than one output should be tested at a time, and the duration of the test should not exceed 10 ms.

## timing requirements over recommended ranges of supply voltage and operating free-air temperature, (unless otherwise noted) (see Figure 2)

|                 |                                                    |           | T <sub>A</sub> = 25°C |     | 54ACT16646 |      | 74ACT16646 |     | UNIT |

|-----------------|----------------------------------------------------|-----------|-----------------------|-----|------------|------|------------|-----|------|

|                 |                                                    |           | MIN                   | MAX | MIN        | MAX  | MIN        | MAX | UNIT |

| fclock          | Clock frequency                                    |           | 0                     | 90  | 0          | 90   | 0          | 90  | MHz  |

| t <sub>W</sub>  | Pulse duration, CLKAB or CLKBA high or low         |           | 5.5                   |     | 5.5        | 10,7 | 5.5        |     | ns   |

|                 | tsu Setup time. A before CLKABÎ or B before CLKBAÎ | Data high | 4                     |     | 4          |      | 4          |     | no   |

| <sup>t</sup> su |                                                    | Data low  | 6                     |     | 6          |      | 6          |     | ns   |

| th              | Hold time, A before CLKAB↑ or B before CLKBA↑      |           | 1.5                   |     | 1.5        |      | 1.5        |     | ns   |

<sup>‡</sup> For I/O ports, the parameter IOZ includes the input leakage current.

<sup>§</sup> This is the increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or VCC.

### 54ACT16646, 74ACT16646 16-BIT BUS TRANSCEIVERS AND REGISTERS WITH 3-STATE OUTPUTS

SCAS127B - MARCH 1990 - REVISED APRIL 1996

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature, (unless otherwise noted) (see Figure 2)

| PARAMETER        | FROM                    | то       | T <sub>A</sub> = 25°C |      |      | 54ACT | 16646 | 74ACT16646 |      | UNIT |

|------------------|-------------------------|----------|-----------------------|------|------|-------|-------|------------|------|------|

| PARAMETER        | (INPUT)                 | (OUTPUT) | MIN                   | TYP  | MAX  | MIN   | MAX   | MIN        | MAX  | UNII |

| f <sub>max</sub> |                         |          | 90                    |      |      | 90    |       | 90         |      | MHz  |

| <sup>t</sup> PLH | A or B                  | B or A   | 3.9                   | 7.5  | 9.4  | 3.9   | 11.5  | 3.9        | 10.6 | ns   |

| t <sub>PHL</sub> |                         | BOIA     | 3.4                   | 7.6  | 10.6 | 3.4   | 12.2  | 3.4        | 11.4 | 115  |

| <sup>t</sup> PZH | ŌĒ                      | A or B   | 3.2                   | 7.7  | 10.8 | 3.2   | 12.9  | 3.2        | 11.9 | ns   |

| t <sub>PZL</sub> |                         | AOIB     | 4.2                   | 9    | 12.2 | 4.2   | 14.6  | 4.2        | 13.5 | 115  |

| <sup>t</sup> PHZ | - OE                    | A or B   | 5.3                   | 7.7  | 9.6  | 5.3   | 10.4  | 5.3        | 10.2 | ns   |

| tPLZL            |                         | AOIB     | 4.9                   | 7.3  | 9.2  | 4.9   | 10.3  | 4.9        | 9.9  | 115  |

| <sup>t</sup> PLH | CLKBA or CLKAB          | A or B   | 4.9                   | 8.9  | 11.1 | 4.9   | 13.1  | 4.9        | 12.2 | ns   |

| t <sub>PHL</sub> | CLNBA OI CLNAB          |          | 5.1                   | 9    | 11   | 5.1   | 13.1  | 5.1        | 12.3 |      |

| <sup>t</sup> PLH | SAB or SBA <sup>†</sup> | A or B   | 5.2                   | 10.3 | 13.8 | 5.2   | 17.2  | 5.2        | 15.6 | ns   |

| <sup>t</sup> PHL | (with A or B high)      |          | 4.9                   | 8.2  | 10.6 | 4.9   | 12.5  | 4.9        | 11.7 | 115  |

| t <sub>PLH</sub> | SBA or SAB <sup>†</sup> | A or B   | 4.3                   | 7.8  | 9.9  | 4.3   | 12.1  | 4.3        | 11.1 | ns   |

| <sup>t</sup> PHL | (with A or B high)      | AOIB     | 5.9                   | 11.2 | 14.9 | 5.9   | 18.2  | 5.9        | 16.7 | 115  |

| <sup>t</sup> PZH | DIR                     | A or B   | 4.5                   | 9.5  | 13.6 | 4.5   | 16.2  | 4.5        | 15.2 | nc   |

| tPZL             | DIK                     | A UI B   | 4.3                   | 9.2  | 11.8 | 4.3   | 14.2  | 4.3        | 13.1 | ns   |

| <sup>t</sup> PHZ | DIR                     | A or B   | 4.5                   | 7.9  | 10.2 | 4.5   | 11.2  | 4.5        | 10.8 |      |

| t <sub>PLZ</sub> | DIK                     | AUID     | 4.4                   | 7.5  | 9.8  | 4.4   | 10.8  | 4.4        | 10.4 | ns   |

<sup>†</sup> These parameters are measured with the internal output state of the storage register opposite to that of the bus input.

### operating characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C

| PARAMETER       |                                               |                  |                        | TEST CONDITIONS |    |    |  |

|-----------------|-----------------------------------------------|------------------|------------------------|-----------------|----|----|--|

| C <sub>pd</sub> | Power discipation canaditance per transceiver | Outputs enabled  | C 50 pF                | f = 1 MHz       | 58 | pF |  |

|                 | Power dissipation capacitance per transceiver | Outputs disabled | $C_L = 50 \text{ pF},$ |                 | 13 |    |  |

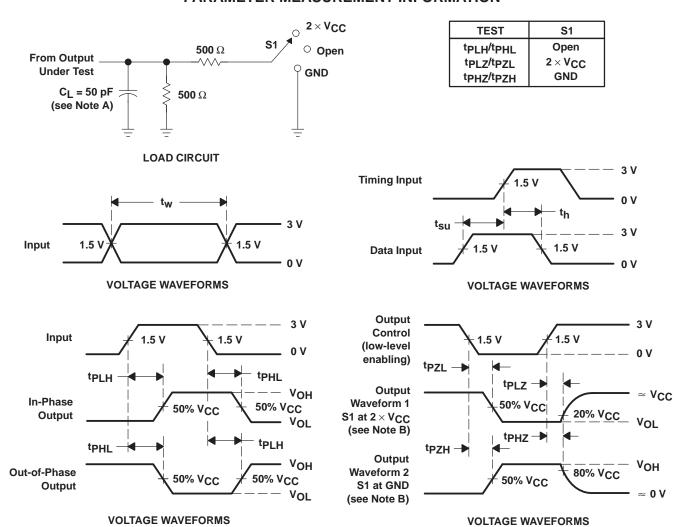

### PARAMETER MEASUREMENT INFORMATION

NOTES: A.  $C_L$  includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_{\rm O} = 50~\Omega$ ,  $t_{\rm f} = 3~{\rm ns}$ ,  $t_{\rm f} = 3~{\rm ns}$ .

- D. The outputs are measured one at a time with one input transition per measurement.

Figure 2. Load Circuit and Voltage Waveforms

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated