www.ti.com

# 24-Bit, 192kHz Sampling, 8-Channel, Enhanced Multilevel, Delta-Sigma DIGITAL-TO-ANALOG CONVERTER

#### **FEATURES**

- 24-BIT RESOLUTION

- ANALOG PERFORMANCE:

Dynamic Range: 100dB typ (PCM1608Y)

105dB typ (PCM1608KY)

**SNR: 100dB typ (PCM1608Y)**

105dB typ (PCM1608KY)

THD+N: 0.003% typ (PCM1608Y)

0.002% typ (PCM1608KY)

Full-Scale Output: 3.1Vp-p typ

● 4x/8x OVERSAMPLING INTERPOLATION

FILTER:

Stopband Attenuation: -55dB Passband Ripple: ±0.03dB

• SAMPLING FREQUENCY:

5kHz to 200kHz (Channels 1, 2, 7, and 8) 5kHz to 100kHz (Channels 3, 4, 5, and 6)

- ACCEPTS 16-, 18-, 20-, AND 24-BIT AUDIO DATA

- DATA FORMATS: Standard, I<sup>2</sup>S, and Left-Justified

- SYSTEM CLOCK: 128, 192, 256, 384, 512, or 768f<sub>s</sub>

- USER-PROGRAMMABLE FUNCTIONS: Digital Attenuation: 0dB to -63dB, 0.5dB/Step Soft Mute

Zero Flags May Be Used As General-Purpose Logic Output Digital De-Emphasis

Digital Filter Roll-Off: Sharp or Slow

- DUAL-SUPPLY OPERATION: +5V Analog, +3.3V Digital

- ◆ +5V TOLERANT DIGITAL LOGIC INPUTS

- PACKAGE: LQFP-48

#### **APPLICATIONS**

- INTEGRATED A/V RECEIVERS

- DVD MOVIE AND AUDIO PLAYERS

- HDTV RECEIVERS

- CAR AUDIO SYSTEMS

- DVD ADD-ON CARDS FOR HIGH-END PCs

- DIGITAL AUDIO WORKSTATIONS

- OTHER MULTICHANNEL AUDIO SYSTEMS

## **DESCRIPTION**

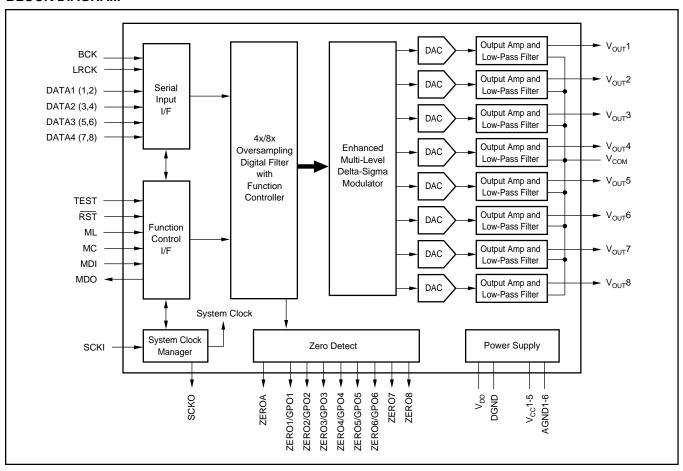

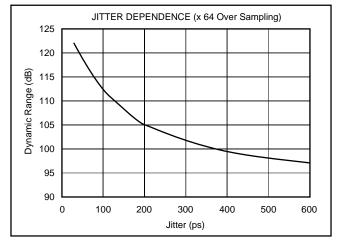

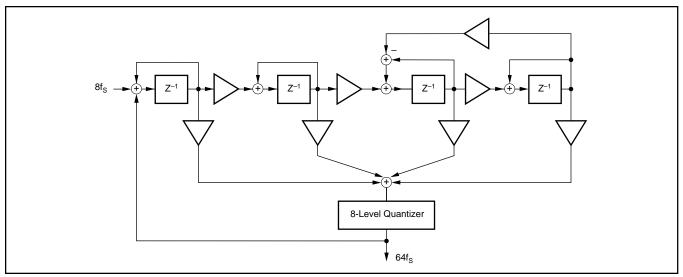

The PCM1608 is a CMOS monolithic integrated circuit that features eight 24-bit audio Digital-to-Analog Converters (DACs) and support circuitry in a small LQFP-48 package. The DACs utilize Texas Instrument's enhanced multi-level, delta-sigma architecture that employs fourth-order noise shaping and 8-level amplitude quantization to achieve excellent signal-to-noise performance and a high tolerance to clock jitter.

The PCM1608 accepts industry-standard audio data formats with 16- to 24-bit audio data. Sampling rates up to 200kHz (channels 1, 2, 7, and 8) or 100kHz (channels 3, 4, 5, and 6) are supported. A full set of user-programmable functions are accessible through a 4-wire serial control port that supports register write and read functions.

# **SPECIFICATIONS**

All specifications at  $T_A = +25$ °C,  $V_{CC} = 5.0$ V,  $V_{DD} = 3.3$ V, system clock = 384f<sub>S</sub> (f<sub>S</sub> = 44.1kHz), and 24-bit data, unless otherwise noted.

|                                                                                  |                                                                                  |                         | PCM1608Y<br>PCM1608KY  |                     |            |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------|------------------------|---------------------|------------|

| PARAMETER                                                                        | CONDITIONS                                                                       | MIN                     | TYP                    | MAX                 | UNITS      |

| RESOLUTION                                                                       |                                                                                  |                         | 24                     |                     | Bits       |

| DATA FORMAT Audio Data Interface Formats Audio Data Bit Length Audio Data Format |                                                                                  | Star<br>16, 1<br>MSB-Fi |                        |                     |            |

| Sampling Frequency (f <sub>S</sub> )                                             | V <sub>OUT</sub> 1, 2, 7, 8                                                      | 5                       |                        | 200                 | kHz        |

| 3 - 1 - 3 - 1 - 3 (3)                                                            | V <sub>OUT</sub> 3, 4, 5, 6                                                      | 5                       |                        | 100                 | kHz        |

| System Clock Frequency                                                           |                                                                                  | 128, 1                  | 192, 256, 384, 512     | , 768f <sub>S</sub> |            |

| DIGITAL INPUT/OUTPUT<br>Logic Family                                             |                                                                                  |                         | TTL-Compatible         |                     |            |

| Input Logic Level                                                                |                                                                                  |                         |                        |                     |            |

| V <sub>IH</sub><br>V <sub>IL</sub>                                               |                                                                                  | 2.0                     |                        | 0.8                 | VDC<br>VDC |

| Input Logic Current                                                              |                                                                                  |                         |                        | 40                  |            |

| I <sub>IH</sub> (1)                                                              | $V_{IN} = V_{DD}$                                                                |                         |                        | 10                  | μΑ         |

| Լ <sub>լլ</sub> (1)<br>Լլ <sub>լ(2)</sub>                                        | $V_{IN} = 0V$<br>$V_{IN} = V_{DD}$                                               |                         | 65                     | -10<br>100          | μΑ         |

|                                                                                  | $V_{IN} = V_{DD}$ $V_{IN} = 0V$                                                  |                         | 65                     | -10<br>-10          | μΑ         |

| I <sub>IL</sub> <sup>(2)</sup> Output Logic Level                                | v <sub>IN</sub> = 0 v                                                            |                         |                        | -10                 | μΑ         |

| V <sub>OH</sub>                                                                  | I <sub>OH</sub> = -4mA                                                           | 2.4                     |                        |                     | VDC        |

| V <sub>OL</sub>                                                                  | $I_{OL} = +4\text{mA}$                                                           | 2.4                     |                        | 1.0                 | VDC        |

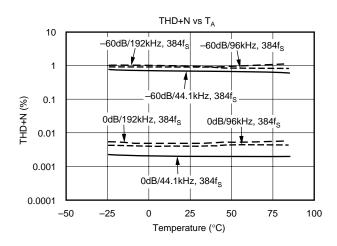

| DYNAMIC PERFORMANCE(3) (4) PCM1608Y                                              | ot.                                                                              |                         |                        |                     |            |

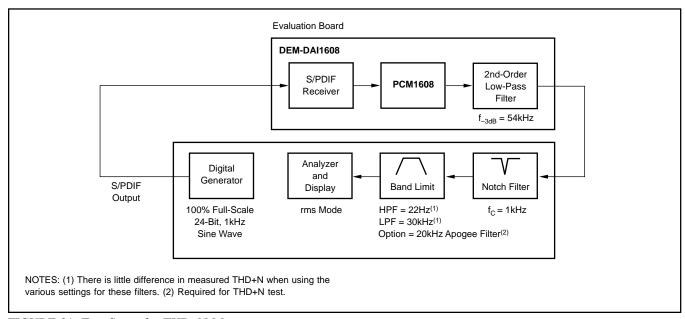

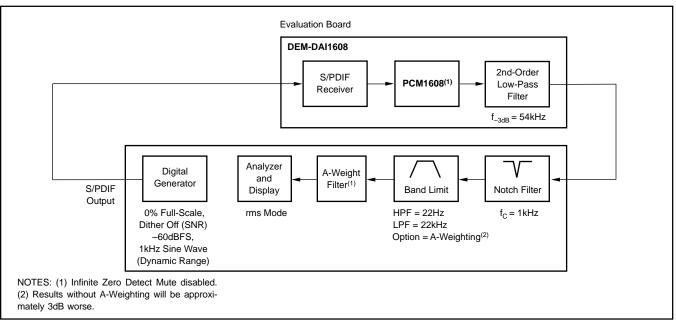

| THD+N at $V_{OUT} = 0$ dB                                                        | f <sub>S</sub> = 44.1kHz                                                         |                         | 0.003                  | 0.01                | %          |

| THIDTIN AL VOUT = OUB                                                            | $f_S = 96 \text{ Hz}$ $f_S = 192 \text{Hz}$                                      |                         | 0.005<br>0.006         | 0.01                | %<br>%     |

| THD+N at $V_{OUT} = -60$ dB                                                      | $f_S = 44.1 \text{kHz}$ $f_S = 96 \text{kHz}$                                    |                         | 1.25<br>1.40           |                     | %<br>%     |

| Dynamia Danga                                                                    | $f_S = 192kHz$                                                                   | 0.4                     | 1.65                   |                     | %          |

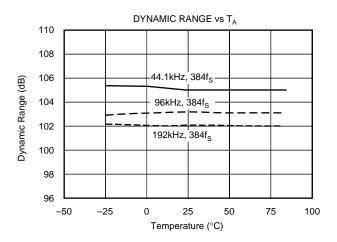

| Dynamic Range                                                                    | EIAJ, A-Weighted, f <sub>S</sub> = 44.1kHz<br>A-Weighted, f <sub>S</sub> = 96kHz | 94                      | 100<br>99              |                     | dB<br>dB   |

|                                                                                  | A-Weighted, f <sub>S</sub> = 90kHz                                               |                         | 98                     |                     | dB         |

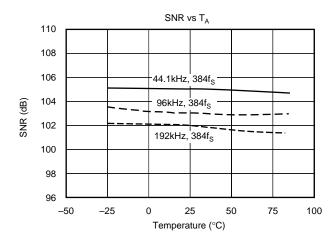

| Signal-to-Noise Ratio                                                            | EIAJ, A-Weighted, f <sub>S</sub> = 44.1kHz                                       | 94                      | 100                    |                     | dB         |

| orginal to Troise Traile                                                         | A-Weighted, f <sub>S</sub> = 96kHz                                               | ٠.                      | 99                     |                     | dB         |

|                                                                                  | A-Weighted, f <sub>S</sub> = 192kHz                                              |                         | 98                     |                     | dB         |

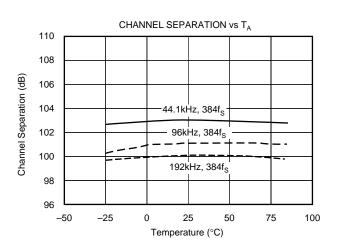

| Channel Separation                                                               | $f_S = 44.1 \text{kHz}$                                                          | 91                      | 98                     |                     | dB         |

|                                                                                  | $f_S = 96kHz$                                                                    |                         | 97                     |                     | dB         |

|                                                                                  | $f_S = 192kHz$                                                                   |                         | 96                     |                     | dB         |

| Level Linearity Error                                                            | $V_{OUT} = -90dB$                                                                |                         | ±0.5                   |                     | dB         |

| PCM1608KY                                                                        |                                                                                  |                         |                        |                     |            |

| THD+N at $V_{OUT} = 0dB$                                                         | $f_S = 44.1 \text{kHz}$                                                          |                         | 0.002                  | 0.008               | %          |

|                                                                                  | f <sub>S</sub> = 96kHz                                                           |                         | 0.004                  |                     | %          |

| TUD N W                                                                          | $f_S = 192kHz$                                                                   |                         | 0.005                  |                     | %          |

| THD+N at $V_{OUT} = -60$ dB                                                      | $f_S = 44.1 \text{kHz}$                                                          |                         | 0.7                    |                     | %          |

|                                                                                  | $f_S = 96kHz$ $f_S = 192kHz$                                                     |                         | 0.9                    |                     | %          |

| Dynamic Range                                                                    | $I_S = 192 \text{kHz}$<br>EIAJ, A-Weighted, $f_S = 44.1 \text{kHz}$              | 98                      | 1.0<br>105             |                     | %<br>dB    |

| Dynamic Kange                                                                    | A-Weighted, $f_S = 96$ kHz                                                       | 90                      | 103                    |                     | dB         |

|                                                                                  | A-Weighted, $f_S = 192$ kHz                                                      |                         | 102                    |                     | dB         |

| Signal-to-Noise Ratio                                                            | EIAJ, A-Weighted, f <sub>S</sub> = 44.1kHz                                       | 98                      | 105                    |                     | dB         |

|                                                                                  | A-Weighted, f <sub>S</sub> = 96kHz                                               |                         | 103                    |                     | dB         |

|                                                                                  | A-Weighted, $f_S = 192kHz$                                                       |                         | 102                    |                     | dB         |

| Channel Separation                                                               | $f_S = 44.1kHz$                                                                  | 94                      | 103                    |                     | dB         |

|                                                                                  | $f_S = 96kHz$                                                                    |                         | 101                    |                     | dB         |

| Level Linearity Error                                                            | $f_{S} = 192kHz$ $V_{OUT} = -90dB$                                               |                         | 100<br>±0.5            |                     | dB<br>dB   |

| DC ACCURACY                                                                      | V <sub>001</sub> = 300D                                                          |                         | ±0.0                   | 1                   | 1 45       |

| Gain Error                                                                       |                                                                                  |                         | ±1.0                   | +6                  | % of FSI   |

| Gain Error Gain Mismatch, Channel-to-Channel                                     |                                                                                  |                         | ±1.0<br>±1.0           | ±6<br>±3            | % of FS    |

| Bipolar Zero Error                                                               | V <sub>OUT</sub> = 0.5V <sub>CC</sub> at Bipolar Zero                            |                         | ±30                    | ±60                 | mV         |

| <u> </u>                                                                         | VOUT - 0.0 VCC at Dipolal Zelo                                                   |                         | ±50                    |                     | 1111       |

| ANALOG OUTPUT Output Voltage                                                     | Full Scale (-0dB)                                                                |                         | 62% of V <sub>CC</sub> |                     | \/n n      |

|                                                                                  | ruii Scale (-U0B)                                                                |                         | 1 04% UI Vcc           | 1                   | Vp-p       |

| Center Voltage                                                                   | , , ,                                                                            |                         | 50% V <sub>CC</sub>    |                     | VDC        |

# **SPECIFICATIONS (Cont.)**

All specifications at  $T_A = +25$ °C,  $V_{CC} = 5.0$ V,  $V_{DD} = 3.3$ V, system clock = 384f<sub>S</sub> (f<sub>S</sub> = 44.1kHz), and 24-bit data, unless otherwise noted.

|                                                |                                |                     | PCM1608Y<br>PCM1608KY |                     |       |

|------------------------------------------------|--------------------------------|---------------------|-----------------------|---------------------|-------|

| PARAMETER                                      | CONDITIONS                     | MIN                 | TYP                   | MAX                 | UNITS |

| DIGITAL FILTER PERFORMANCE                     |                                |                     |                       |                     |       |

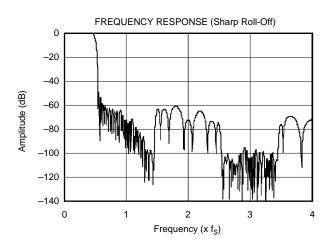

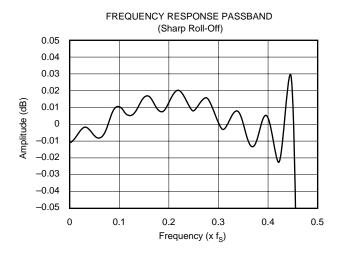

| Filter Characteristics 1, Sharp Roll-Off       |                                |                     |                       |                     |       |

| Passband                                       | ±0.03dB                        |                     |                       | 0.454f <sub>S</sub> |       |

| Passband                                       | −3dB                           |                     |                       | 0.487f <sub>S</sub> |       |

| Stopband                                       |                                | 0.546f <sub>S</sub> |                       |                     | dB    |

| Passband Ripple                                |                                |                     |                       | ±0.03               | dB    |

| Stopband Attenuation                           | Stopband = 0.546f <sub>S</sub> | -50                 |                       |                     | dB    |

| Stopband Attenuation                           | Stopband = $0.567f_S$          | -55                 |                       |                     |       |

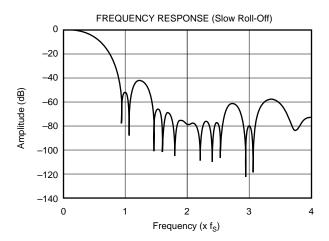

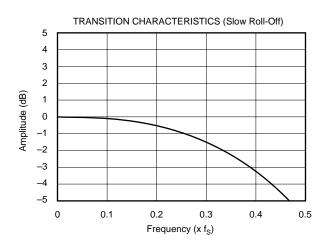

| Filter Characteristics 2, Slow Roll-Off        |                                |                     |                       |                     |       |

| Passband                                       | ±0.5dB                         |                     |                       | 0.198f <sub>S</sub> |       |

| Passband                                       | –3dB                           |                     |                       | 0.390f <sub>S</sub> |       |

| Stopband                                       |                                | 0.884f <sub>S</sub> |                       |                     |       |

| Passband Ripple                                |                                |                     |                       | ±0.5                | dB    |

| Stopband Attenuation                           | Stopband = 0.884f <sub>S</sub> | -40                 |                       |                     | dB    |

| Delay Time                                     |                                |                     | 20/f <sub>S</sub>     |                     | sec   |

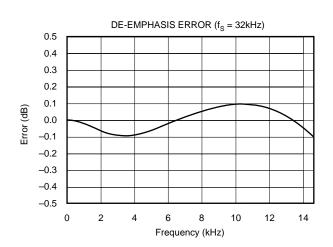

| De-Emphasis Error                              |                                |                     | ±0.1                  |                     | dB    |

| ANALOG FILTER PERFORMANCE                      |                                |                     |                       |                     |       |

| Frequency Response                             | f = 20kHz                      |                     | -0.03                 |                     | dB    |

|                                                | f = 44kHz                      |                     | -0.20                 |                     | dB    |

| POWER-SUPPLY REQUIREMENTS(4)                   |                                |                     |                       |                     |       |

| Voltage Range, V <sub>DD</sub>                 |                                | +3.0                | +3.3                  | +3.6                | VDC   |

| V <sub>CC</sub>                                |                                | +4.5                | +5.0                  | +5.5                | VDC   |

| Supply Current, I <sub>DD</sub> <sup>(5)</sup> | $f_S = 44.1kHz$                |                     | 18                    | 25                  | mA    |

|                                                | $f_S = 96kHz$                  |                     | 40                    |                     | mA    |

|                                                | $f_S = 192kHz$                 |                     | 40                    |                     | mA    |

| I <sub>cc</sub>                                | $f_S = 44.1 \text{kHz}$        |                     | 33                    | 46                  | mA    |

|                                                | $f_S = 96kHz$                  |                     | 36                    |                     | mA    |

|                                                | $f_S = 192kHz$                 |                     | 36                    |                     | mA    |

| Power Dissipation                              | $f_S = 44.1 \text{kHz}$        |                     | 224                   | 313                 | mW    |

| ·                                              | f <sub>S</sub> = 96kHz         |                     | 312                   |                     | mW    |

|                                                | $f_S = 192kHz$                 |                     | 312                   |                     | mW    |

| TEMPERATURE RANGE                              |                                |                     |                       |                     |       |

| Operation Temperature                          |                                | -25                 |                       | +85                 | °C    |

| Thermal Resistance $	heta_{JA}$                | LQFP-48                        |                     | 100                   |                     | °C/W  |

NOTES: (1) Pins 31, 38, 40, 41, 45-47 (DATA4, SCKI, BCK, LRCK, DATA1, DATA2, DATA3). (2) Pins 34-37 (MDI, MC, ML,  $\overline{\text{RST}}$ ). (3) Analog performance specifications are tested with a Shibasoku #725 THD Meter with 400Hz HPF on, 30kHz LPF on, average mode with 20kHz bandwidth limiting. The load connected to the analog output is  $5\text{k}\Omega$ , or larger, via capacitive loading. (4) Conditions in 192kHz operation are: system clock =  $128\text{f}_{\text{S}}$ , DAC3 through DAC6 disabled in Register 8, and oversampling rate =  $64\text{f}_{\text{S}}$  in Register 12. (5) CLKO is disabled.

#### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply Voltage, V <sub>DD</sub> | +4.0V                 |

|---------------------------------------|-----------------------|

| V <sub>CC</sub>                       | +6.5V                 |

| Ground Voltage Differences            | ±0.1V                 |

| Digital Input Voltage                 | 0.3V to (6.5V + 0.3V) |

| Input Current (except power supply)   | ±10mA                 |

| Operating Temperature Under Bias      | 40°C to +125°C        |

| Storage Temperature                   | 55°C to +150°C        |

| Junction Temperature                  | +150°C                |

| Lead Temperature (soldering, 5s)      | +260°C                |

| Package Temperature (IR reflow, 10s)  | +235°C                |

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT   | PACKAGE | PACKAGE<br>DRAWING<br>NUMBER | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(1)</sup> | TRANSPORT<br>MEDIA |

|-----------|---------|------------------------------|-----------------------------------|--------------------|-----------------------------------|--------------------|

| PCM1608Y  | LQFP-48 | 340                          | −25°C to +85°C                    | PCM1608Y           | PCM1608Y                          | 250-Piece Tray     |

| "         | "       | "                            | "                                 | "                  | PCM1608Y/2K                       | Tape and Reel      |

| PCM1608KY | LQFP-48 | 340                          | -25°C to +85°C                    | PCM1608KY          | PCM1608KY                         | 250-Piece Tray     |

| "         | "       | "                            | "                                 | "                  | PCM1608KY/2K                      | Tape and Reel      |

NOTE: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /2K indicates 2000 devices per reel). Ordering 2000 pieces of "PCM1608Y/2K" will get a single 2000-piece Tape and Reel.

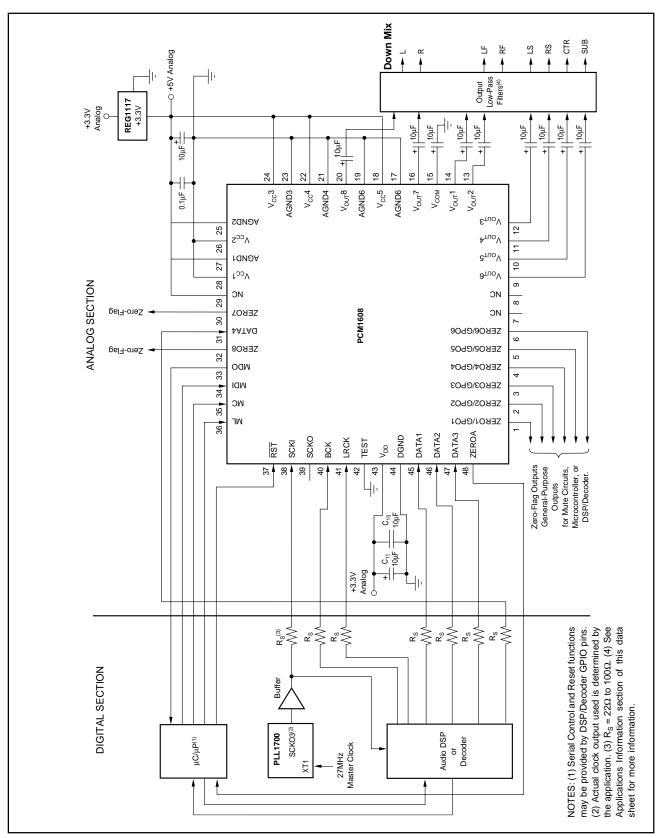

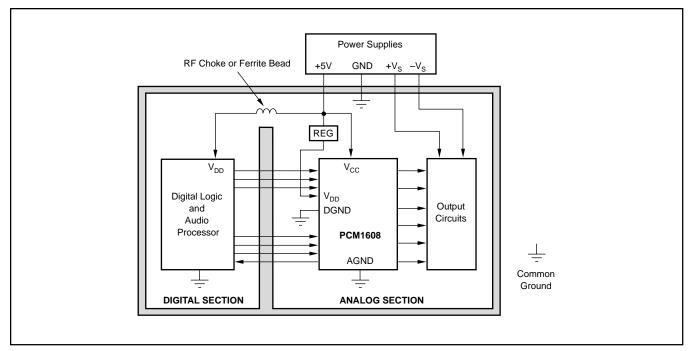

#### **BLOCK DIAGRAM**

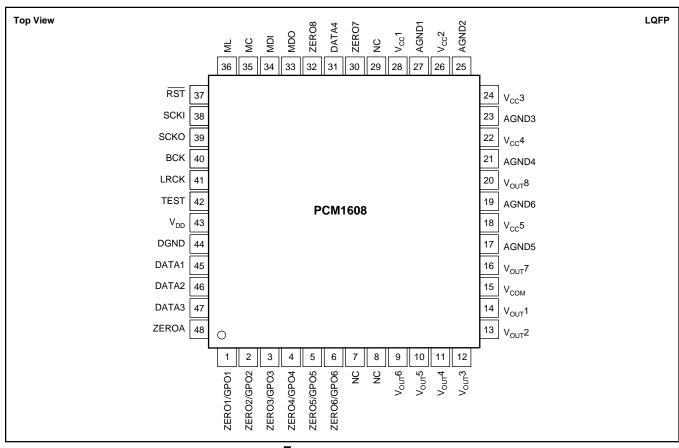

#### **PIN CONFIGURATION**

#### **PIN ASSIGNMENTS**

| PIN | NAME               | I/O | DESCRIPTION                                                                                                                                               |

|-----|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ZERO1/GPO1         | 0   | Zero Data Flag for V <sub>OUT</sub> 1. Can also be used as GPO pin.                                                                                       |

| 2   | ZERO2/GPO2         | 0   | Zero Data Flag for V <sub>OUT</sub> 2. Can also be used as GPO pin.                                                                                       |

| 3   | ZERO3/GPO3         | 0   | Zero Data Flag for $V_{OUT}$ 3. Can also be used as GPO pin.                                                                                              |

| 4   | ZERO4/GPO4         | 0   | Zero Data Flag for $V_{OUT}$ 4. Can also be used as GPO pin.                                                                                              |

| 5   | ZERO5/GPO5         | 0   | Zero Data Flag for $V_{OUT}$ 5. Can also be used as GPO pin.                                                                                              |

| 6   | ZERO6/GPO6         | 0   | Zero Data Flag for $V_{OUT}$ 6. Can also be used as GPO pin.                                                                                              |

| 7   | NC                 | _   | No Connection                                                                                                                                             |

| 8   | NC                 | _   | No Connection                                                                                                                                             |

| 9   | V <sub>OUT</sub> 6 | 0   | Voltage Output of Audio Signal Corresponding to Rch on DATA3. Up to 96kHz.                                                                                |

| 10  | V <sub>OUT</sub> 5 | 0   | Voltage Output of Audio Signal Corresponding to Lch on DATA3. Up to 96kHz.                                                                                |

| 11  | V <sub>OUT</sub> 4 | 0   | Voltage Output of Audio Signal Corresponding to Rch on DATA2. Up to 96kHz.                                                                                |

| 12  | V <sub>OUT</sub> 3 | 0   | Voltage Output of Audio Signal Corresponding to Lch on DATA2. Up to 96kHz.                                                                                |

| 13  | V <sub>OUT</sub> 2 | 0   | Voltage Output of Audio Signal Corresponding to Rch on DATA1. Up to 192kHz.                                                                               |

| 14  | V <sub>OUT</sub> 1 | 0   | Voltage Output of Audio Signal Corresponding to Lch on DATA1. Up to 192kHz.                                                                               |

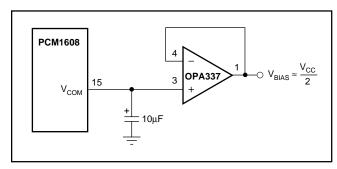

| 15  | V <sub>COM</sub>   | 0   | Common Voltage Output. This pin should be bypassed with a 10μF capacitor to AGND.                                                                         |

| 16  | V <sub>OUT</sub> 7 | 0   | Voltage Output for Audio Signal Corresponding to Lch on DATA4. Up to 192kHz.                                                                              |

| 17  | AGND5              | _   | Analog Ground                                                                                                                                             |

| 18  | V <sub>CC</sub> 5  | _   | Analog Power Supply, +5V                                                                                                                                  |

| 19  | AGND6              | _   | Analog Ground                                                                                                                                             |

| 20  | V <sub>OUT</sub> 8 | _   | Voltage Output for Audio Signal Corresponding to Rch on DATA4. Up to 192kHz.                                                                              |

| 21  | AGND4              | _   | Analog Ground                                                                                                                                             |

| 22  | V <sub>CC</sub> 4  | _   | Analog Power Supply, +5V                                                                                                                                  |

| 23  | AGND3              | _   | Analog Ground                                                                                                                                             |

| 24  | V <sub>CC</sub> 3  | _   | Analog Power Supply, +5V                                                                                                                                  |

| 25  | AGND2              | _   | Analog Ground                                                                                                                                             |

| 26  | V <sub>CC</sub> 2  | _   | Analog Power Supply, +5V                                                                                                                                  |

| 27  | AGND1              | _   | Analog Ground                                                                                                                                             |

| 28  | V <sub>CC</sub> 1  | _   | Analog Power Supply, +5V                                                                                                                                  |

| 29  | NC                 | _   | No Connection                                                                                                                                             |

| 30  | ZERO7              | _   | Zero Data Flag for V <sub>OUT</sub> 7                                                                                                                     |

| 31  | DATA4              | _   | Serial Audio Data Input for V <sub>OUT</sub> 7 and V <sub>OUT</sub> 8 <sup>(2)</sup>                                                                      |

| 32  | ZERO8              | _   | Zero Data Flag for V <sub>OUT</sub> 8                                                                                                                     |

| 33  | MDO                | 0   | Serial Data Output for Serial Control Port <sup>(3)</sup>                                                                                                 |

| 34  | MDI                | ı   | Serial Data Input for Serial Control Port <sup>(1)</sup>                                                                                                  |

| 35  | MC                 | I   | Shift Clock for Serial Control Port <sup>(1)</sup>                                                                                                        |

| 36  | ML_                | I   | Latch Enable for Serial Control Port <sup>(1)</sup>                                                                                                       |

| 37  | RST                | I   | System Reset, Active LOW <sup>(1)</sup>                                                                                                                   |

| 38  | SCKI               | I   | System Clock Input. Input frequency is 128, 192, 256, 384, 512, or 768f <sub>S</sub> . <sup>(2)</sup>                                                     |

| 39  | SCKO               | 0   | Buffered Clock Output. Output frequency is 128, 192, 256, 384, 512, or 768f <sub>S</sub> , or one-half of 128, 192, 256, 384, 512, or 768f <sub>S</sub> . |

| 40  | BCK                | ı   | Shift Clock Input for Serial Audio Data. Clock must be 32, 48, or 64f <sub>S</sub> . <sup>(2)</sup>                                                       |

| 41  | LRCK               | I   | Left and Right Clock Input. This clock is equal to the sampling rate, f <sub>S</sub> . <sup>(2)</sup>                                                     |

| 42  | TEST               | _   | Test Pin. This pin should be connected to DGND. <sup>(1)</sup>                                                                                            |

| 43  | V <sub>DD</sub>    | _   | Digital Power Supply, +3.3V                                                                                                                               |

| 44  | DGND               | _   | Digital Ground                                                                                                                                            |

| 45  | DATA1              | !   | Serial Audio Data Input for V <sub>OUT</sub> 1 and V <sub>OUT</sub> 2 <sup>(2)</sup>                                                                      |

| 46  | DATA2              | !   | Serial Audio Data Input for V <sub>OUT</sub> 3 and V <sub>OUT</sub> 4 <sup>(2)</sup>                                                                      |

| 47  | DATA3              | ı   | Serial Audio Data Input for V <sub>OUT</sub> 5 and V <sub>OUT</sub> 6 <sup>(2)</sup>                                                                      |

| 48  | ZEROA              | 0   | Zero Data Flag. Logical "AND" of ZERO1 through ZERO6.                                                                                                     |

NOTES: (1) Schmitt-Trigger input with internal pull-down, 5V tolerant. (2) Schmitt-Trigger input, 5V tolerant. (3) Tri-state output.

## TYPICAL PERFORMANCE CURVES

All specifications at  $T_A$  = +25°C,  $V_{CC}$  = 5.0V,  $V_{DD}$  = 3.3V, system clock = 384f<sub>S</sub> (f<sub>S</sub> = 44.1kHz), and 24-bit input data, unless otherwise noted.

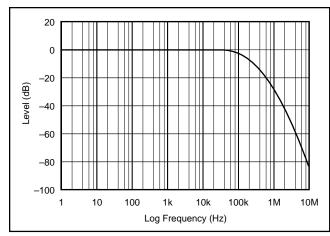

#### **DIGITAL FILTER**

Digital Filter (De-Emphasis Off,  $f_s = 44.1 \text{kHz}$ )

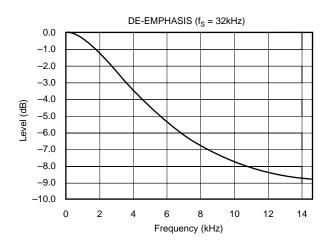

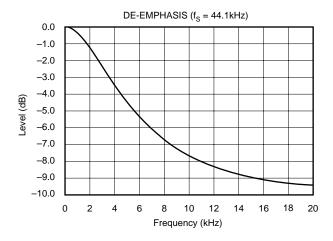

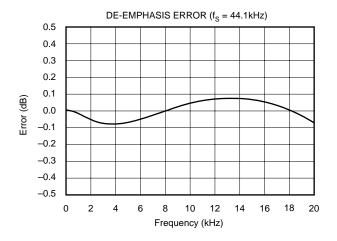

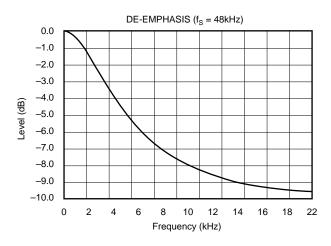

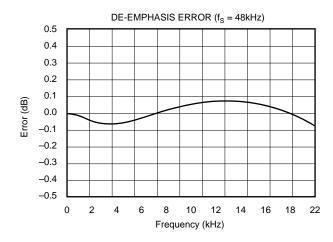

#### **De-Emphasis and De-Emphasis Error**

## TYPICAL PERFORMANCE CURVES (Cont.)

All specifications at  $T_A = +25^{\circ}C$ ,  $V_{CC} = 5.0V$ ,  $V_{DD} = 3.3V$ , system clock =  $384f_S$  ( $f_S = 44.1kHz$ ), and 24-bit input data, unless otherwise noted.

#### De-Emphasis and De-Emphasis Error (Cont.)

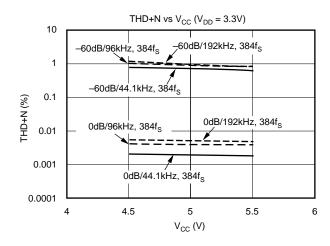

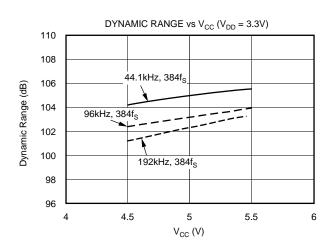

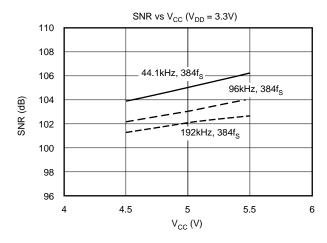

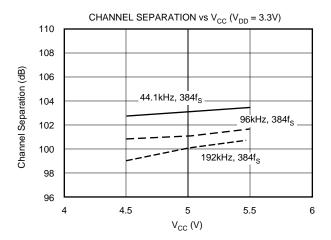

#### ANALOG DYNAMIC PERFORMANCE

All specifications at  $T_A = +25^{\circ}C$ ,  $V_{CC} = 5.0V$ ,  $V_{DD} = 3.3V$ , and 24-bit input data, unless otherwise noted. Conditions in 192kHz operation are: system clock = 128f<sub>S</sub>, DAC3 through DAC6 = disable of Register 8, and oversampling rate = 64f<sub>S</sub> of Redister 12.

#### **Supply-Voltage Characteristics**

# **TYPICAL PERFORMANCE CURVES (Cont.)**

All specifications at  $T_A = +25^{\circ}$ C,  $V_{CC} = 5.0$ V,  $V_{DD} = 3.3$ V, and 24-bit input data, unless otherwise noted. Conditions in 192kHz operation are: system clock = 128f<sub>S</sub>, DAC3 through DAC6 = disable of Register 8, and oversampling rate = 64f<sub>S</sub> of Redister 12.

#### Supply-Voltage Characteristics (Cont.)

#### **Temperature Characteristics**

# SYSTEM CLOCK AND RESET FUNCTIONS

#### SYSTEM CLOCK INPUT

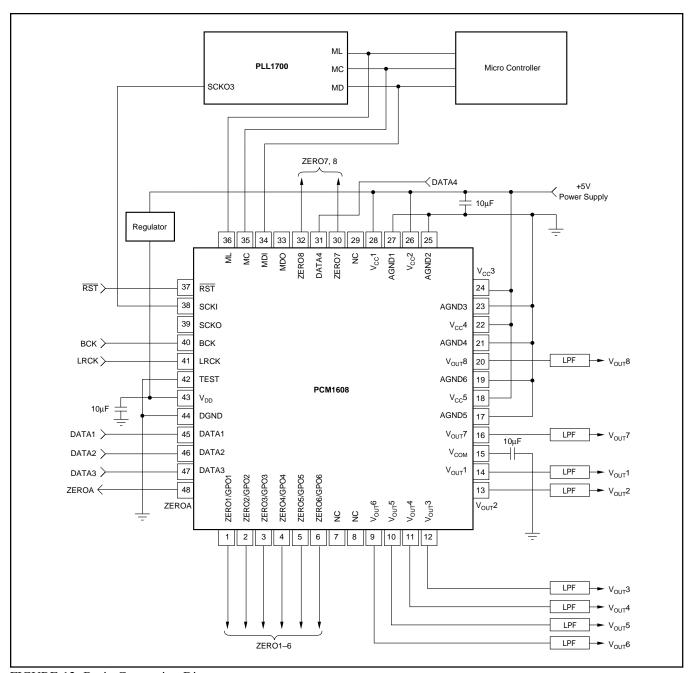

The PCM1608 requires a system clock for operating the digital interpolation filters and multilevel delta-sigma modulators. The system clock is applied at the SCKI input (pin 38). Table I shows examples of system clock frequencies for common audio sampling rates.

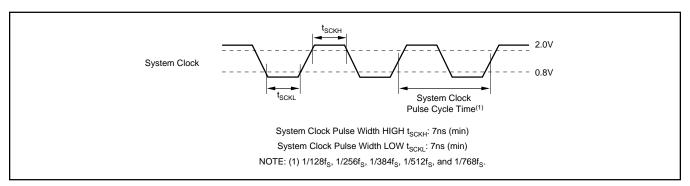

Figure 1 shows the timing requirements for the system clock input. For optimal performance, it is important to use a clock source with low phase jitter and noise. The PLL1700 multiclock generator from Texas Instruments is an excellent choice for providing the PCM1608 system clock.

The 192kHz sampling frequency operation is available on DATA1 for  $V_{OUT}1$  and  $V_{OUT}2$ , and DATA4 for  $V_{OUT}7$  and  $V_{OUT}8$ . It is recommended that  $V_{OUT}3$ ,  $V_{OUT}4$ ,  $V_{OUT}5$ , and  $V_{OUT}6$  be disabled when operating with  $f_S=192$ kHz. This is done by setting the DAC3, DAC4, DAC5, and DAC6 bits of Register 9 to a "1" state.

#### SYSTEM CLOCK OUTPUT

A buffered version of the system clock input is available at the SCKO output (pin 39). SCKO can operate at either full (f<sub>SCKI</sub>) or half (f<sub>SCKI</sub>/2) rate. The SCKO output frequency may be programmed using the CLKE bit of Register 9. If the SCKO output is not required, it is recommended to disable it using the CLKE bit. The default is SCKO enabled.

#### POWER-ON AND EXTERNAL RESET FUNCTIONS

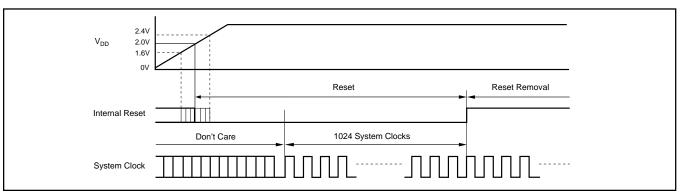

The PCM1608 includes a power-on reset function, as shown in Figure 2. With the system clock active, and  $V_{\rm DD} > 2.0 \rm V$  (typical, 1.6V to 2.4V), the power-on reset function will be enabled. The initialization sequence requires 1024 system clocks from the time  $V_{\rm DD} > 2.0 \rm V$ . After the initialization period, the PCM1608 will be set to its reset default state, as described in the Mode Control Register section of this data sheet.

The PCM1608 also includes an external reset capability using the  $\overline{RST}$  input (pin 37). This allows an external

| SAMPLING  | SYSTEM CLOCK FREQUENCY (f <sub>SCLK</sub> ) (MHz) |                   |                   |                   |                   |                   |   |   |   |   |   |   |   |   |       |   |         |         |         |         |

|-----------|---------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---|---|---|---|---|---|---|---|-------|---|---------|---------|---------|---------|

| FREQUENCY | 128f <sub>S</sub>                                 | 192f <sub>S</sub> | 256f <sub>S</sub> | 384f <sub>S</sub> | 512f <sub>S</sub> | 768f <sub>S</sub> |   |   |   |   |   |   |   |   |       |   |         |         |         |         |

| 8kHz      | _                                                 | _                 | 2.0480            | 3.0720            | 4.0960            | 6.1440            |   |   |   |   |   |   |   |   |       |   |         |         |         |         |

| 16kHz     | _                                                 | -                 | 4.0960            | 6.1440            | 8.1920            | 12.2880           |   |   |   |   |   |   |   |   |       |   |         |         |         |         |

| 32kHz     | _                                                 | -                 | 8.1920            | 12.2880           | 16.3840           | 24.5760           |   |   |   |   |   |   |   |   |       |   |         |         |         |         |

| 44.1kHz   | _                                                 | -                 | 11.2896           | 16.9344           | 22.5792           | 33.8688           |   |   |   |   |   |   |   |   |       |   |         |         |         |         |

| 48kHz     | _                                                 | _                 | _                 | _                 | _                 | _                 | _ | _ | ! | _ | _ | _ | _ | _ | 1 – 1 | _ | 12.2880 | 18.4320 | 24.5760 | 36.8640 |

| 96kHz     | _                                                 | _                 | 24.5760           | 36.8640           | 49.1520           | (1)               |   |   |   |   |   |   |   |   |       |   |         |         |         |         |

| 192kHz    | 24.5760                                           | 36.8640           | (2)               | (2)               | (2)               | (2)               |   |   |   |   |   |   |   |   |       |   |         |         |         |         |

TABLE I. System Clock Rates for Common Audio Sampling Frequencies.

FIGURE 1. System Clock Timing.

FIGURE 2. Power-On Reset Timing.

controller or master reset circuit to force the PCM1608 to initialize to its reset default state. For normal operation, RST should be set to a logic "1".

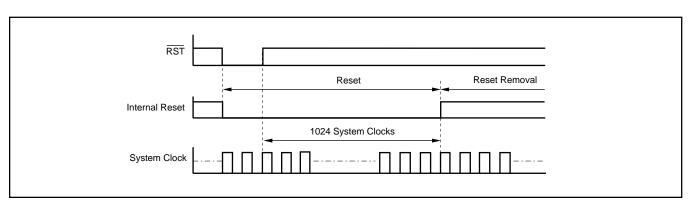

The external reset operation and timing is shown in Figure 3. The  $\overline{RST}$  pin is set to logic "0" for a minimum of 20ns. After the initialization sequence is completed, the PCM1608 will be set to its reset default state, as described in the Mode Control Registers section of this data sheet.

During the reset period (1024 system clocks), the analog outputs are forced to the bipolar zero level (or  $V_{\rm CC}/2$ ). After the reset period, the internal registers are initialized in the next  $1/f_{\rm S}$  period and, if SCKI, BCK, and LRCK are provided continuously, the PCM1608 provides proper analog output with unit-group delay, as specified in this data sheet.

The external reset is especially useful in applications where there is a delay between PCM1608 power-up and system clock activation. In this case, the RST pin should be held at a logic "0" level until the system clock has been activated.

#### **AUDIO SERIAL INTERFACE**

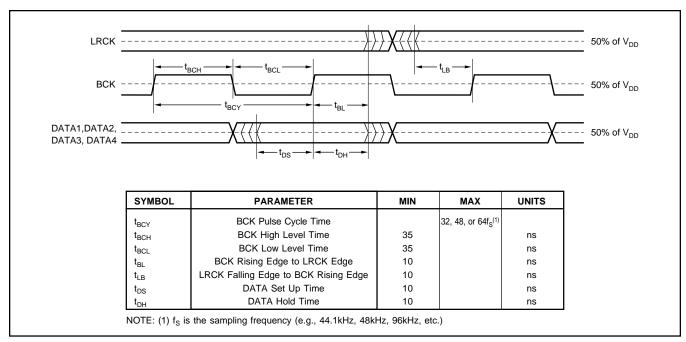

The audio serial interface for the PCM1608 is comprised of a 5-wire synchronous serial port. It includes LRCK (pin 41), BCK (pin 40), DATA1 (pin 45), DATA2 (pin 46), DATA3 (pin 47), and DATA4 (pin 31). BCK is the serial audio bit clock, and is used to clock the serial data present on DATA1, DATA2, DATA3, and DATA4 into the audio interface's serial shift register. Serial data is clocked into the PCM1608 on the rising edge of BCK. LRCK is the serial audio left/right word clock. It is used to latch serial data into the serial audio interface's internal registers.

Both LRCK and BCK must be synchronous to the system clock. Ideally, it is recommended that LRCK and BCK be derived from the system clock input, SCKI. LRCK is operated at the sampling frequency ( $f_s$ ). BCK may be operated at 32, 48, or 64 times the sampling frequency ( $I^2S$  format does not support BCK =  $32f_s$ ).

Internal operation of the PCM1608 is synchronized with LRCK. Accordingly, it is held when the sampling rate clock of LRCK is changed, or SCKI and/or BCK is broken at least for one clock cycle. If SCKI, BCK, and LRCK are provided continuously after this hold condition, the internal operation will be resynchronized automatically, less than  $3/f_{\rm S}$  period. In this resynchronize period, and following  $3/f_{\rm S}$ , the analog outputs are forced to the bipolar zone level (or  $V_{\rm CC}/2$ ). External resettling is not required.

#### **AUDIO DATA FORMATS AND TIMING**

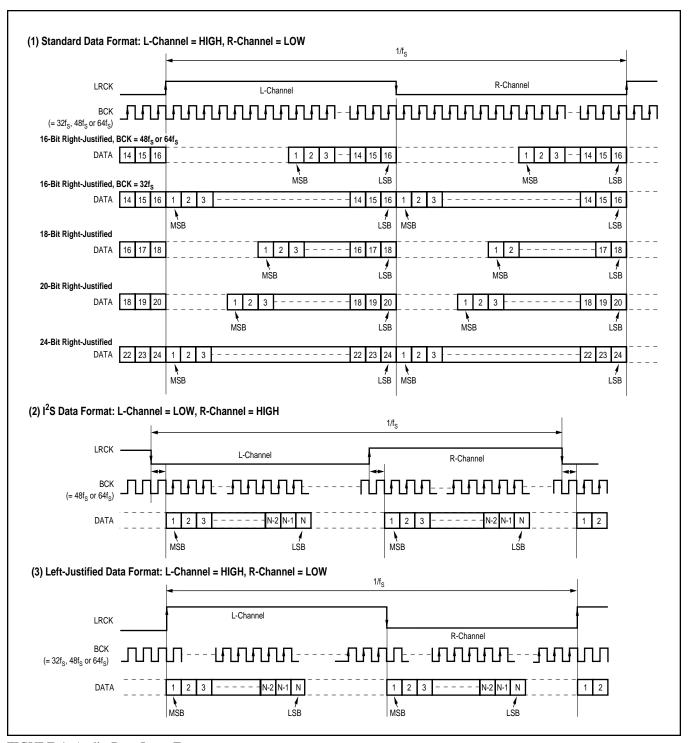

The PCM1608 supports industry-standard audio data formats, including Standard, I<sup>2</sup>S, and Left-Justified (see Figure 4). Data formats are selected using the format bits, FMT[2:0], in Register 9. The default data format is 24-bit Standard. All formats require Binary Two's Complement, MSB-first audio data. See Figure 5 for a detailed timing diagram of the serial audio interface.

DATA1, DATA2, DATA3, and DATA4 each carry two audio channels, designated as the Left and Right channels. The Left channel data always precedes the Right channel data in the serial data stream for all data formats. Table II shows the mapping of the digital input data to the analog output pins.

| DATA INPUT | CHANNEL | ANALOG OUTPUT                     |

|------------|---------|-----------------------------------|

| DATA1      | Left    | V <sub>OUT</sub> 1 <sup>(1)</sup> |

| DATA1      | Right   | V <sub>OUT</sub> 2 <sup>(1)</sup> |

| DATA2      | Left    | V <sub>OUT</sub> 3 <sup>(2)</sup> |

| DATA2      | Right   | V <sub>OUT</sub> 4 <sup>(2)</sup> |

| DATA3      | Left    | V <sub>OUT</sub> 5 <sup>(2)</sup> |

| DATA3      | Right   | V <sub>OUT</sub> 6 <sup>(2)</sup> |

| DATA4      | Left    | V <sub>OUT</sub> 7 <sup>(1)</sup> |

| DATA4      | Right   | V <sub>OUT</sub> 8 <sup>(1)</sup> |

NOTES: (1) Up to 192kHz. (2) Up to 96kHz, forced to bipolar zero when  $\rm f_{\rm S}$  = 96kHz.

TABLE II. Audio Input Data to Analog Output Mapping.

FIGURE 3. External Reset Timing.

#### SERIAL CONTROL INTERFACE

The serial control interface is a 4-wire synchronous serial port that operates asynchronously to the serial audio interface. The serial control interface is utilized to program and read the on-chip mode registers. The control interface includes MDO (pin 33), MDI (pin 34), MC (pin 35), and ML

(pin 36). MDO is the serial data output, used to read back the values of the mode registers; MDI is the serial data input, used to program the mode registers; MC is the serial bit clock, used to shift data in and out of the control port; and ML is the control port latch clock.

FIGURE 4. Audio Data Input Formats.

FIGURE 5. Audio Interface Timing.

#### **REGISTER WRITE OPERATION**

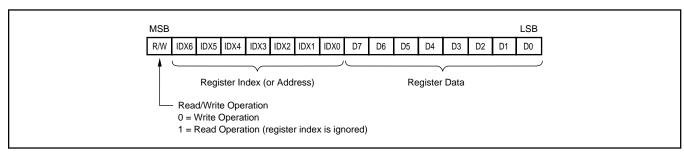

All Write operations for the serial control port use 16-bit data words. Figure 6 shows the control data word format. The most significant bit is the Read/Write (R/W) bit. When set to "0", this bit indicates a Write operation. There are seven bits, labeled IDX[6:0], that set the register index (or address) for the Write operation. The least significant eight bits, D[7:0], contain the data to be written to the register specified by IDX[6:0].

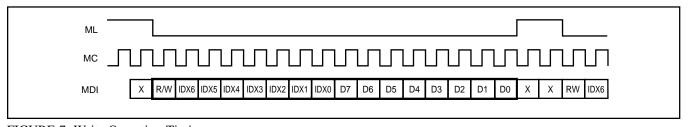

Figure 7 shows the functional timing diagram for writing the serial control port. ML is held at a logic "1" state until a register needs to be written. To start the register write cycle, ML is set to logic "0". Sixteen clocks are then provided on

MC, corresponding to the 16-bits of the control data word on MDI. After the sixteenth clock cycle has completed, ML is set to logic "1" to latch the data into the indexed mode control register.

#### SINGLE REGISTER READ OPERATION

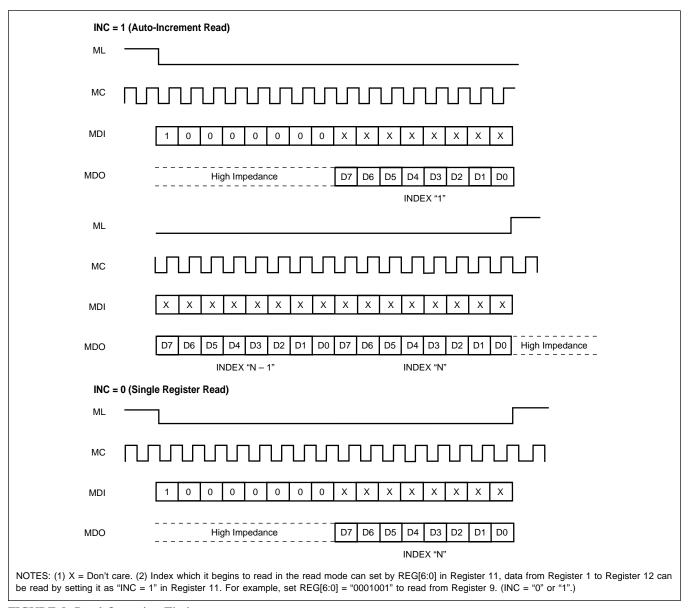

Read operations utilize the 16-bit control word format shown in Figure 6. For Read operations, the R/W bit is set to "1". Read operations ignore the index bits, IDX[6:0], of the control data word. Instead, the REG[6:0] bits in Control Register 11 are used to set the index of the register that is to be read during the Read operation. Bits IDX[6:0] should be set to  $00_{\rm H}$  for Read operations.

FIGURE 6. Control Data Word Format for MDI.

FIGURE 7. Write Operation Timing.

The details of the Read operation are shown in Figure 8. First, Control Register 11 must be written with the index of the register to be read back. Additionally, the INC bit must be set to logic "0" in order to disable the Auto-Increment Read function. The Read cycle is then initiated by setting ML to logic "0" and setting the R/W bit of the control data word to logic "1", indicating a Read operation. MDO remains at a high-impedance state until the last eight bits of the 16-bit read cycle, which corresponds to the eight data bits of the register indexed by the REG[6:0] bits of Control Register 11. The Read cycle is completed when ML is set to "1", immediately after the MC clock cycle for the least significant bit of indexed control register has completed.

#### **AUTO-INCREMENT READ OPERATION**

The Auto-Increment Read function allows for multiple registers to be read sequentially. The Auto-Increment Read function is enabled by setting the INC bit of Control Register 11 to "1". The sequence always starts with Register 1, and ends with the register indexed by the REG[6:0] bits in Control Register 11.

Figure 8 shows the timing of the Auto-Increment Read operation. The operation begins by writing Control Register 11, setting INC to "1", and setting REG[6:0] to the last register to be read in the sequence. The actual Read operation starts on the next HIGH to LOW transition of the ML pin.

FIGURE 8. Read Operation Timing.

The Read cycle starts by setting the R/W bit of the control word to "1", and setting all of the IDX[6:0] bits to "0". All subsequent bits input on the MDI are ignored while ML is set to "0". For the first eight clocks of the Read cycle, MDO is set to a high-impedance state. This is followed by a sequence of 8-bit words, each corresponding the data contained in Control Registers 1 through N, where N is defined by the REG[6:0] bits in Control Register 11. The Read cycle is completed when ML is set to "1", immediately

after the MC clock cycle for the least significant bit of Control Register N has completed.

#### **CONTROL INTERFACE TIMING REQUIREMENTS**

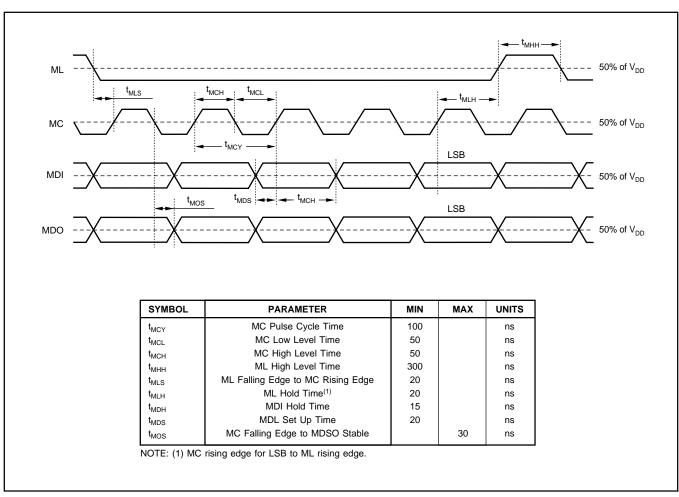

Figure 9 shows a detailed timing diagram for the Serial Control interface. Pay special attention to the setup and hold times, as well as  $t_{\rm MLS}$  and  $t_{\rm MLH}$ , which define minimum delays between edges of the ML and MC clocks. These timing parameters are critical for proper control port operation.

FIGURE 9. Control Interface Timing.

#### **MODE CONTROL REGISTERS**

#### **User-Programmable Mode Controls**

The PCM1608 includes a number of user-programmable functions that are accessed via control registers. The registers are programmed using the Serial Control Interface that was previously discussed in this data sheet. Table III lists the available mode control functions, along with their reset default conditions and associated register index.

#### **Register Map**

The mode control register map is shown in Table IV. Each register includes a R/W bit that determines whether a register read (R/W=1) or write (R/W=0) operation is performed. Each register also includes an index (or address) indicated by the IDX[6:0] bits.

| FUNCTION                                                 | RESET DEFAULT                    | CONTROL REGISTER    | INDEX, IDX[6:0]    |

|----------------------------------------------------------|----------------------------------|---------------------|--------------------|

| Digital Attenuation Control, 0dB to -63dB in 0.5dB Steps | 0dB, No Attenuation              | 1 through 6, 16, 17 | AT1[7:0], AT2[7:0] |

|                                                          |                                  |                     | AT3[7:0], AT4[7:0] |

|                                                          |                                  |                     | AT5[7:0], AT6[7:0] |

|                                                          |                                  |                     | AT7[7:0], AT8[7:0] |

| Soft Mute Control                                        | Mute Disabled                    | 7, 18               | MUT[8:1]           |

| DAC 1-8 Operation Control                                | DAC 1-6 Enabled                  | 8, 19               | DAC[8:1]           |

| Audio Data Format Control                                | 24-Bit Standard Format           | 9                   | FMT[2:0]           |

| Digital Filter Roll-Off Control                          | Sharp Roll-Off                   | 9                   | FLT                |

| SCKO Frequency Selection                                 | Full Rate (= f <sub>SCKI</sub> ) | 9                   | CLKD               |

| SCKO Output Enable                                       | SCKO Enabled                     | 9                   | CLKE               |

| De-Emphasis All Channel Function Control                 | De-Emphasis All Channel Disabled | 10                  | DMC                |

| De-Emphasis All Channel Sample Rate Selection            | 44.1kHz                          | 10                  | DMF[1:0]           |

| Output Phase Select                                      | Normal Phase                     | 10                  | DREV               |

| Zero Flag Polarity Select                                | High                             | 10                  | ZREV               |

| Read Register Index Control                              | REG[6:0] = 01 <sub>H</sub>       | 11                  | REG[6:0]           |

| Read Auto-Increment Control                              | Auto-Increment Disabled          | 11                  | INC                |

| General-Purpose Output Enable                            | Zero Flag Enabled                | 12                  | GPOE               |

| General-Purpose Output Bits (GPO1-GPO6)                  | Disabled                         | 12                  | GPO[6:1]           |

| Oversampling Rate Control                                | 64x                              | 12                  | OVER               |

TABLE III. User-Programmable Mode Controls.

| IDX<br>(B8-B14) | REGISTER       | B15      | B14    | B13       | B12       | B11      | B10       | В9    | В8      | В7                 | В6                 | В5                 | B4                 | В3                 | B2                 | B1                 | В0                 |

|-----------------|----------------|----------|--------|-----------|-----------|----------|-----------|-------|---------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| ,               |                |          |        |           |           |          |           |       |         |                    | _                  |                    |                    |                    |                    |                    |                    |

| 00 <sub>H</sub> | Register0      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | N/A <sup>(1)</sup> |

| 01 <sub>H</sub> | Register1      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | AT17               | AT16               | AT15               | AT14               | AT13               | AT12               | AT11               | AT10               |

| 02 <sub>H</sub> | Register2      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | AT27               | AT26               | AT25               | AT24               | AT23               | AT22               | AT21               | AT20               |

| 03 <sub>H</sub> | Register3      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | AT37               | AT36               | AT35               | AT34               | AT33               | AT32               | AT31               | AT30               |

| 04 <sub>H</sub> | Register4      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | AT47               | AT46               | AT45               | AT44               | AT43               | AT42               | AT41               | AT40               |

| 05 <sub>H</sub> | Register5      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | AT57               | AT56               | AT55               | AT54               | AT53               | AT52               | AT51               | AT50               |

| 06 <sub>H</sub> | Register6      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | AT67               | AT66               | AT65               | AT64               | AT63               | AT62               | AT61               | AT60               |

| 07 <sub>H</sub> | Register7      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | RSV <sup>(2)</sup> | RSV <sup>(2)</sup> | MUT6               | MUT5               | MUT4               | митз               | MUT2               | MUT1               |

| 08 <sub>H</sub> | Register8      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | RSV <sup>(2)</sup> | RSV <sup>(2)</sup> | DAC6               | DAC5               | DAC4               | DAC3               | DAC2               | DAC1               |

| 09 <sub>H</sub> | Register9      | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | RSV <sup>(2)</sup> | RSV <sup>(2)</sup> | FLT                | CLKD               | CLKE               | FMT2               | FMT1               | FMT0               |

| 0A <sub>H</sub> | Register10     | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | RSV <sup>(2)</sup> | ZREV               | DREV               | DMF1               | DMF0               | DMC                | DMC                | DMC                |

| 0B <sub>H</sub> | Register11     | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | INC                | REG6               | REG5               | REG4               | REG3               | REG2               | REG1               | REG0               |

| 0C <sub>H</sub> | Register12     | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | OVER               | GPOE               | GPO6               | GPO5               | GPO4               | GPO3               | GPO2               | GPO1               |

|                 |                |          |        |           |           |          |           |       |         |                    |                    |                    |                    |                    |                    |                    |                    |

| 10 <sub>H</sub> | Register 16    | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | AT77               | AT76               | AT75               | AT74               | AT73               | AT72               | AT71               | AT70               |

| 11 <sub>H</sub> | Register 17    | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | AT87               | AT86               | AT85               | AT84               | AT83               | AT82               | AT81               | AT80               |

| 12 <sub>H</sub> | Register 18    | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | RSV <sup>(2)</sup> | MUT8               | MUT7               |

| 13 <sub>H</sub> | Register 19    | R/W      | IDX6   | IDX5      | IDX4      | IDX3     | IDX2      | IDX1  | IDX0    | RSV <sup>(2)</sup> | DAC8               | DAC7               |

| NOTES: (        | 1) N/A = not a | ssigned. | No ope | ration ev | en if set | ting any | data. (2) | RSV = | reserve | for test           | operatio           | n. It sho          | ould be s          | set "0" du         | ring reg           | ular ope           | ration.            |

TABLE IV. Mode Control Register Map.

#### **REGISTER DEFINITIONS**

|            | B15 | B14  | B13  | B12  | B11  | B10  | В9   | B8   | B7   | В6   | B5   | B4   | В3   | B2   | B1   | В0           |

|------------|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|--------------|

| Register 1 | R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | AT17 | AT16 | AT15 | AT14 | AT13 | AT12 | AT11 | AT10         |

|            |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |              |

| Register 2 | R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | AT27 | AT26 | AT25 | AT24 | AT23 | AT22 | AT21 | AT20         |

|            |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |              |

| Register 3 | R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | AT37 | AT36 | AT35 | AT34 | AT33 | AT32 | AT31 | AT30         |

|            |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |              |

| Register 4 | R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | AT47 | AT46 | AT45 | AT44 | AT43 | AT42 | AT41 | AT40         |

|            |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |              |

| Register 5 | R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | AT57 | AT56 | AT55 | AT54 | AT53 | AT52 | AT51 | AT50         |

|            |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |              |

| Register 6 | R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | AT67 | AT66 | AT65 | AT64 | AT63 | AT62 | AT61 | A <b>T60</b> |

|            |     |      |      |      |      |      |      |      |      |      | ,    |      |      |      |      |              |

| Register 7 | R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | AT77 | AT76 | AT75 | AT74 | AT73 | AT72 | AT71 | AT70         |

|            | · · |      |      |      |      |      |      |      |      |      |      |      |      |      |      |              |

| Register 8 | R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | AT87 | AT86 | AT85 | AT84 | AT83 | AT82 | AT81 | A <b>T80</b> |

#### R/W Read/Write Mode Select

When R/W = 0, a write operation is performed.

When R/W = 1, a read operation is performed.

Default Value: 0

#### ATx[7:0] Digital Attenuation Level Setting

where x = 1 through 8, corresponding to the DAC output  $V_{OUT}x$ .

These bits are Read/Write. Default Value: 1111 1111<sub>B</sub>

Each DAC output,  $V_{OUT}1$  through  $V_{OUT}8$ , has a digital attenuator associated with it. The attenuator may be set from 0dB to -63dB, in 0.5dB steps. Changes in attenuator levels are made by incrementing or decrementing, by one step (0.5dB), for every  $8/f_S$  time interval until the programmed attenuator setting is reached. Alternatively, the attenuator may be set to infinite attenuation (or mute).

The attenuation level may be set using the formula below.

Attenuation Level (dB) =  $0.5 \text{ (ATx[7:0]}_{DEC} - 255)$

where:  $ATx[7:0]_{DEC} = 0$  through 255

for:  $ATx[7:0]_{DEC} = 0$  through 128, the attenuator is set to infinite attenuation.

The following table shows attenuator levels for various settings.

| ATx[7:0]               | Decimal Value | Attenuator Level Setting      |

|------------------------|---------------|-------------------------------|

| 1111 1111 <sub>B</sub> | 255           | 0dB, No Attenuation (default) |

| 1111 1110 <sub>B</sub> | 254           | -0.5dB                        |

| 1111 1101 <sub>B</sub> | 253           | -1.0dB                        |

| •                      | •             | •                             |

| •                      | •             | •                             |

| •                      | •             | •                             |

| $1000\ 0010_{\rm B}$   | 130           | -62.5dB                       |

| 1000 0001 <sub>B</sub> | 129           | -63.0dB                       |

| $1000\ 0000_{\rm B}$   | 128           | Mute                          |

| •                      | •             | •                             |

| •                      | •             | •                             |

| •                      | •             | •                             |

| 0000 0000 <sub>B</sub> | 0             | Mute                          |

Register 7

| B15 | B14  | B13  | B12  | B11  | B10  | В9   | B8   | B7  | B6  | B5   | B4   | B3   | B2   | B1   | B0   |

|-----|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|

| R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RSV | RSV | MUT6 | MUT5 | MUT4 | MUT3 | MUT2 | MUT1 |

#### R/W Read/Write Mode Select

When R/W = 0, a Write operation is performed.

When R/W = 1, a Read operation is performed.

Default Value: 0

#### **MUTx** Soft Mute Control

Where x = 1 through 6, corresponding to the DAC output  $V_{OUT}x$ .

These bits are Read/Write.

Default Value: 0

MUTx = 0 Mute Disabled (default)

MUTx = 1 Mute Enabled

The mute bits, MUT1 through MUT6, are used to enable or disable the Soft Mute function for the corresponding DAC outputs,  $V_{OUT}1$  through  $V_{OUT}6$ . The Soft Mute function is incorporated into the digital attenuators. When Mute is disabled (MUTx = 0), the attenuator and DAC operate normally. When Mute is enabled by setting MUTx = 1, the digital attenuator for the corresponding output will be decreased from the current setting to the infinite attenuation setting one attenuator step (0.5dB) at a time. This provides a quiet, pop-free muting of the DAC output. Upon returning from Soft Mute, by setting MUTx = 0, the attenuator will be increased one step at a time to the previously programmed attenuator level.

REGISTER 8

| B15 | B14  | B13  | B12  | B11  | B10  | В9   | В8   | B7  | В6  | B5   | B4   | В3   | B2   | B1   | В0   |

|-----|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|

| R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RSV | RSV | DAC6 | DAC5 | DAC4 | DAC3 | DAC2 | DAC1 |

#### R/W Read/Write Mode Select

When R/W = 0, a write operation is performed.

When R/W = 1, a read operation is performed.

Default Value: 0

#### DACx DAC Operation Control

where x = 1 through 6, corresponding to the DAC output  $V_{OUT}x$ .

These bits are Read/Write.

Default Value: 0

DACx = 0 DAC Operation Enabled (default)

DACx = 1 DAC Operation Disabled

The DAC operation controls are used to enable and disable the DAC outputs,  $V_{OUT}1$  through  $V_{OUT}6$ . When DACx = 0, the output amplifier input is connected to the DAC output. When DACx = 1, the output amplifier input is switched to the DC common-mode voltage ( $V_{COM}$ ), equal to  $V_{CC}/2$ .

REGISTER 9

| B15 | B14  | B13  | B12  | B11  | B10  | В9   | В8   | B7  | B6  | B5  | B4   | В3   | B2   | B1   | B0   |

|-----|------|------|------|------|------|------|------|-----|-----|-----|------|------|------|------|------|

| R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RSV | RSV | FLT | CLKD | CLKE | FMT2 | FMT1 | FMT0 |

#### R/W Read/Write Mode Select

When R/W = 0, a write operation is performed. When R/W = 1, a read operation is performed.

Default Value: 0

#### FLT Digital Filter Roll-Off Control

These bits are Read/Write.

Default Value: 0

| FLT = 0 | Sharp Roll-Off (default) |

|---------|--------------------------|

| FLT = 1 | Slow Roll-Off            |

The FLT bit allows the user to select the digital filter roll-off that is best suited to their application. Two filter roll-off sections are available: Sharp or Slow. The filter responses for these selections are shown in the Typical Performance Curves section of this data sheet.

#### CLKD SCKO Frequency Selection

This bit is Read/Write.

Default Value: 0

| CLKD = 0 | Full Rate, $f_{SCKO} = f_{SCKI}$ (default) |

|----------|--------------------------------------------|

| CLKD = 1 | Half Rate, $f_{SCKO} = f_{SCKL}/2$         |

The CLKD bit is used to determine the clock frequency at the system clock output pin, SCKO.

#### **CLKE** SCKO Output Enable

This bit is Read/Write.

Default Value: 0

| CLKE = 0 | SCKO Enabled (default) |

|----------|------------------------|

| CLKE = 1 | SCKO Disabled          |

The CLKE bit is used to enable or disable the system clock output pin, SCKO. When SCKO is enabled, it will output either a full or half rate clock, based upon the setting of the CLKD bit. When SCKO is disabled, it is set to a LOW level.

#### FMT[2:0] Audio Interface Data Format

These bits are Read/Write.

Default Value: 000<sub>B</sub>

| FMT[2:0] | Audio Data Format Selection                            |

|----------|--------------------------------------------------------|

| 000      | 24-Bit Standard Format, Right-Justified Data (default) |

| 001      | 20-Bit Standard Format, Right-Justified Data           |

| 010      | 18-Bit Standard Format, Right-Justified Data           |

| 011      | 16-Bit Standard Format, Right-Justified Data           |

| 100      | I <sup>2</sup> S Format, 16- to 24-bits                |

| 101      | Left-Justified Format, 16- to 24-Bits                  |

| 110      | Reserved                                               |

| 111      | Reserved                                               |

The FMT[2:0] bits are used to select the data format for the serial audio interface.

**REGISTER 10**

| B15 | B14  | B13  | B12  | B11  | B10  | B9   | B8   | B7  | В6   | B5   | B4   | B3   | B2  | B1  | В0  |

|-----|------|------|------|------|------|------|------|-----|------|------|------|------|-----|-----|-----|

| R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RSV | ZREV | DREV | DMF1 | DMF0 | DMC | DMC | DMC |

#### R/W Read/Write Mode Select

When R/W = 0, a write operation is performed. When R/W = 1, a read operation is performed.

Default Value: 0

#### DMF[1:0] Sampling Frequency Selection for the De-Emphasis Function

These bits are Read/Write.

Default Value: 00<sub>B</sub>

| DMF[1:0] | De-Emphasis Same Rate Selection |

|----------|---------------------------------|

| 00       | 44.1kHz (default)               |

| 01       | 48kHz                           |

| 10       | 32kHz                           |

| 11       | Reserved                        |

The DMF[1:0] bits are used to select the sampling frequency used for the Digital De-Emphasis function when it is enabled. The de-emphasis curves are shown in the Typical Performance Curves section of this data sheet. The table below shows the available sampling frequencies.

#### DMC Digital De-Emphasis, All Channels Function Control

This bit is Read/Write.

Default Value: 0

| DMC = 0 | De-Emphasis Disabled for All Channels (default) |

|---------|-------------------------------------------------|

| DMC = 1 | De-Emphasis Enabled for All Channels 1 and 2    |

The DMC bit is used to enable or disable the De-Emphasis function for all channels. To select more than one of three DMC bits, enable or disable the De-Emphasis function.

#### **DREV** Output Phase Select

Default Value: 0

| DREV = 0 | Normal Output (default) |

|----------|-------------------------|

| DREV = 1 | Inverted Output         |

The DREV bit is the output analog signal phase control.

#### **ZREV** Zero Flag Polarity Select

Default Value: 0

| ZREV = 0 | Zero Flag Pins HIGH at a Zero Detect (default) |

|----------|------------------------------------------------|

| ZREV = 1 | Zero Flag Pins LOW at a Zero Detect            |

The ZREV bit allows the user to select the polarity of the Zero Flag pins.

В8 **B6 B5** B0 **B15 B14 B13 B12 B11** B10 B9 **B7** B4 **B3** B2 **B**1 **REGISTER 11** R/W IDX6 IDX5 IDX4 IDX3 IDX2 IDX1 IDX0 INC REG6 REG5 REG4 REG3 REG2 REG1 REG0

#### R/W Read/Write Mode Select

When R/W = 0, a write operation is performed. When R/W = 1, a read operation is performed.

Default Value: 0

#### **INC Auto-Increment Read Control**

This bit is Read/Write. Default Value: 0

| INC = 0 | Auto-Increment Read Disabled (default) |

|---------|----------------------------------------|

| INC = 1 | Auto-Increment Read Enabled            |

The INC bit is used to enable or disable the Auto-Increment Read feature of the Serial Control Interface. Refer to the Serial Control Interface section of this data sheet for details regarding Auto-Increment Read operation.

#### **REG[6:0] Read Register Index**

These bits are Read/Write.

Default Value: 01<sub>H</sub>

The REG[6:0] bits are used to set the index of the register to be read when performing the Single Register Read operation. In the case of an Auto-Increment Read operation, the REG[6:0] bits indicate the index of the last register to be read in the Auto-Increment Read sequence. For example, if Registers 1 through 6 are to be read during an Auto-Increment Read operation, the REG[6:0] bits would be set to 06<sub>H</sub>. Refer to the Serial Control Interface section of this data sheet for details regarding the Single Register and Auto-Increment Read operations.

|             | B15 | B14  | B13  | B12  | B11  | B10  | В9   | В8   | B7   | B6   | B5   | B4   | В3   | B2   | B1   | В0   |

|-------------|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| REGISTER 12 | R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | OVER | GPOE | GPO6 | GPO5 | GPO4 | GPO3 | GPO2 | GPO1 |

#### **GPOx General-Purpose Logic Output**

Where: x = 1 through 6, corresponding pins GPO1 through GPO6.

These bits are Read/Write.

Default Value: 0

| GPOx = 0 | Set GPOx to "0" |

|----------|-----------------|

| GPOx = 1 | Set GPOx to "1" |

The general-purpose output pins, GPO1 through GPO6, are enabled by setting GPOE = 1. These pins are used as general-purpose outputs for controlling user-defined logic functions. When general-purpose outputs are disabled (GPOE = 0), they default to the zero-flag function, ZERO1 through ZERO6.

#### **GPOE General-Purpose Output Enable**

This bit is Read/Write.

Default Value: 0

| GPOE = 0 | General-Purpose Outputs Disabled                                         |

|----------|--------------------------------------------------------------------------|

|          | Pins default to zero-flag function (ZERO1 through ZERO6).                |

| GPOE = 1 | General-Purpose Outputs Enabled                                          |

|          | Data written to GPO1 through GPO6 will appear at the corresponding pins. |

#### **OVER** Oversampling Rate Control

This bit is Read/Write.

Default Value: 0

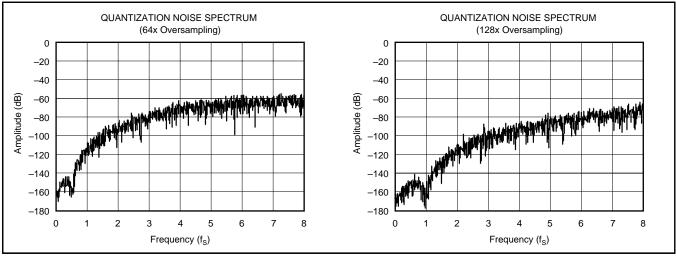

System Clock Rate = 256, 384, 512, or  $768f_S$ :

OVER = 0 64x Oversampling (default)

OVER = 1 128x Oversampling

System Clock Rate = 128 or  $192f_S$ :

OVER = 0 32x Oversampling (default)

OVER = 1 64x Oversampling

The OVER bit is used to control the oversampling rate of the delta-sigma DACs. The OVER = 1 setting is recommended when the oversampling rate is 192kHz (system clock rate is 128 or  $192f_S$ ).

REGISTER 18

| B15 | B14  | B13  | B12  | B11  | B10  | В9   | B8   | B7  | B6  | B5  | B4  | B3  | B2  | B1   | B0   |

|-----|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|------|------|

| R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RSV | RSV | RSV | RSV | RSV | RSV | MUT8 | MUT7 |

#### R/W Read/Write Mode Select

When R/W = 0, a write operation is performed.

When R/W = 1, a read operation is performed.

Default Value: 0

#### MUTx Soft Mute Control

Where x = 7-8, corresponding to the DAC output  $V_{OUT}x$ .

These bits are Read/Write.

Default Value: 0

MUTx = 0 Mute Disabled (default)

MUTx = 1 Mute Enabled

The mute bits, MUT7 through MUT8, are used to enable or disable the Soft Mute function for the corresponding DAC outputs,  $V_{OUT}$ 7 and  $V_{OUT}$ 8. The Soft Mute function is incorporated into the digital attenuators. When Mute is disabled (MUTx = 0), the attenuator and the DAC operate normally. When Mute is enabled by setting MUTx = 1, the digital attenuator for the corresponding output will be decremented from the current setting to the infinite attenuation setting one attenuator step (0.5dB) at a time. This provides a quiet, "pop"-free muting of the DAC output. Upon returning from Soft Mute, by setting MUTx = 0, the attenuator will be incremented one step at a time to the previously programmed attenuator level.

| B15 | B14  | B13  | B12  | B11  | B10  | В9   | B8   | В7  | В6  | B5  | B4  | В3  | B2  | B1   | B0   |

|-----|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|------|------|

| R/W | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RSV | RSV | RSV | RSV | RSV | RSV | DAC8 | DAC7 |

#### R/W Read/Write Mode Select

When R/W = 0, a write operation is performed. When R/W = 1, a read operation is performed.

Default Value: 0

#### DACx DAC Operation Control

Where x = 7-8, corresponding to the DAC output  $V_{OUT}x$ .

These bits are Read/Write.

Default Value: 0

| DACx = 0 | DAC Operation Disabled (default) |

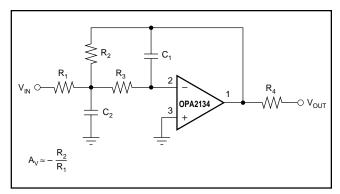

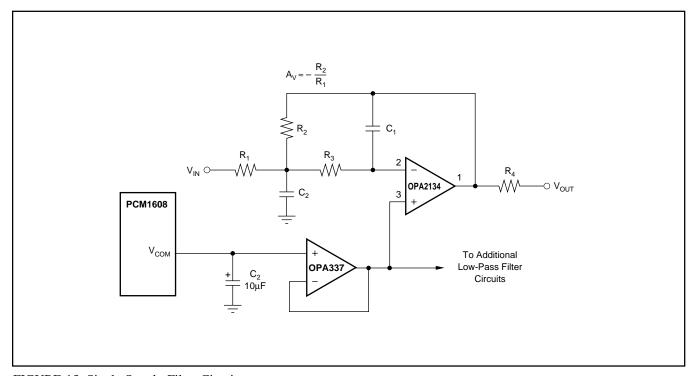

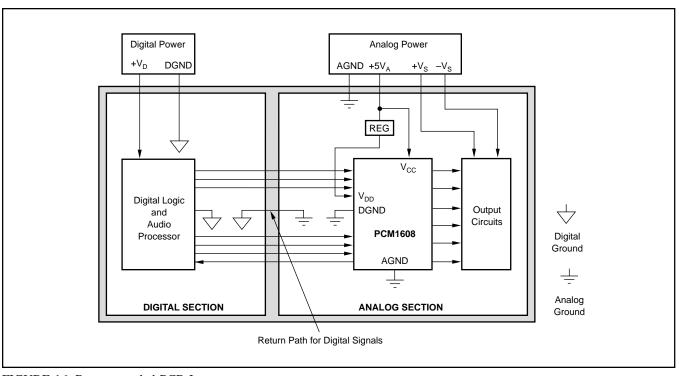

|----------|----------------------------------|