## **Winbond USB Scanner Processor**

## W6668F

The information described in this document is the exclusive intellectual property of Winbond Electronics Corporation and shall not be reproduced without permission from Winbond.

Winbond is providing this document only for reference purposes of W-based system design. Winbond assumes no responsibility for errors or omissions. All data and specifications are subject to change without notice.

Copyright © 1999 (all rights reserved) Winbond Electronics Corporation

## **W6668F Data Sheet Revision History**

|    | Pages | Dates    | Version | Version | Main Contents    |

|----|-------|----------|---------|---------|------------------|

|    |       |          |         | on Web  |                  |

| 1  | n.a.  | 11/07/00 | 0.50    | n.a.    | First published. |

| 2  |       |          |         |         |                  |

| 3  |       |          |         |         |                  |

| 4  |       |          |         |         |                  |

| 5  |       |          |         |         |                  |

| 6  |       |          |         |         |                  |

| 7  |       |          |         |         |                  |

| 8  |       |          |         |         |                  |

| 9  |       |          |         |         |                  |

| 10 |       |          |         |         |                  |

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

## LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

## **TABLE OF CONTENTS**

| 1. GENERAL DESCRIPTION                            | 1       |

|---------------------------------------------------|---------|

| 2. FEATURES AND APPLICATIONS                      | 1       |

| 2. FEATURES AND APPLICATIONS                      | I       |

| 1.1 Mega byte transfer rate during image scan in. | 3       |

| 3. PIN CONFIGURATION                              | Δ       |

|                                                   |         |

| 4. PIN DESCRIPTIONS                               | 5       |

| 5. BLOCK DIAGRAM & REGISTERS LIST                 | 9       |

| 5.1 Block Diagram                                 | <u></u> |

|                                                   |         |

| 5.2 Register List Tables                          |         |

| Part 3: Shading Gamma Part 4: Motor Control       |         |

| Part 4: Motor Control                             |         |

| Part 6: System Control                            |         |

| Part 7: General I/O and Special Registers         |         |

| 6. SCANNER ASIC CIRCUIT                           | 20      |

| 6.1 Command Decoder and Interrupt                 | 20      |

| 7. USB INTERFACE CIRCUIT                          | 24      |

| 7.2 Serial ROM Access                             |         |

|                                                   |         |

| 8. ELECTRICAL CHARACTERISTICS                     | 28      |

| 8.1. Maximum Ratings*                             | 28      |

| 8.2. Recommended Operating Conditions             | 28      |

| 8.3. Power Supply Characteristics                 | 29      |

| 8.4. Digital Characteristics                      | 30      |

| 8.5. | Analog Characteristics (measures from analog input to ADC output) | 30 |

|------|-------------------------------------------------------------------|----|

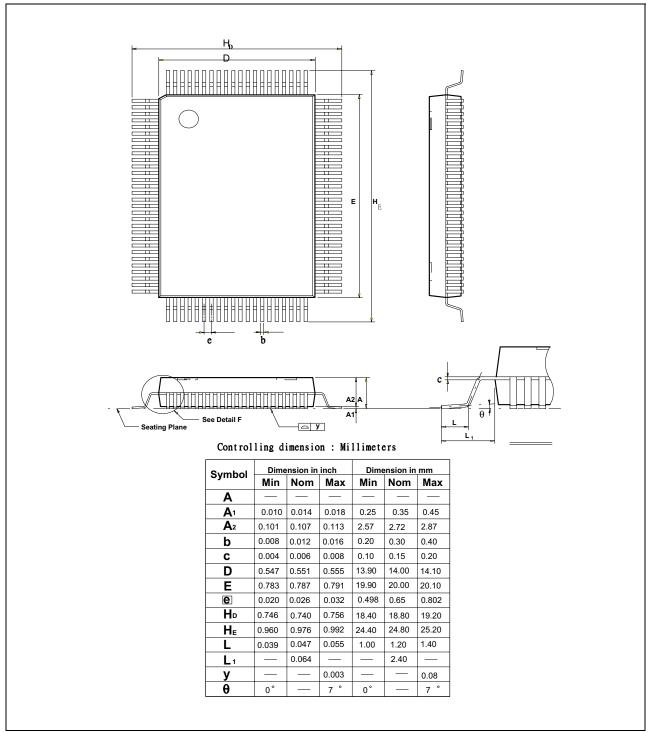

| 9.   | PACKAGE INFORMATION (W6668F)                                      | 32 |

| 10.  | HOW TO READ THE TOP MARKING                                       | 33 |

| 11.  | ORDERING INFORMATION                                              | 33 |

# WINBOND USB SCANNER PROCESSOR

#### 1. GENERAL DESCRIPTION

The W6668 is a highly integrated USB scanner control processor. It provides the system required signals for all necessary of a CCD/CIS scanner, the signal interface includes CCD/CIS sensor, image buffer memory, motor drive, lamp/LED drive and other mechanical input/output signals. The processor accept and process the analog image data, convert to digital data and store the data to the image buffer and then transfer to the host through USB bus. The scanner commands and status are transfer from or to the PC through USB bus without the aid of micro controller. The command and status also can be transfered through serial port and accessed by 8051 without the aids of USB port and windows operation system.

The only required additional active components are SRAM or DRAM for scanning image buffer, power regulator for 5V and 3.3V power source (if 3.3V component is in use) and power transistor array for the step motor.

## 2. FEATURES AND APPLICATIONS

#### Features:

Complete scanner on one chip solution for sheetfeed and flatbed scanners.

Internal timing generator for 300, 600 or 1200 dpi CCD/CIS sensor.

Builtin control signals for CCD lamp, CCD electric shutter, or CIS LED driver.

Multiple CCD transfer gate driver supported to extend CCD exposure time.

Exposure time of multiple CCD transfer gate driver can be programmed individually.

Horizontal and vertical of 1200, 800, 600, 400, 300, 200, 150, 100, 75 or 50 dpi selectable.

Three channels analog input with clamp circuit individually.

Integrated Correlated Double Sampler (CDS).

Integrated 6-bit Programmable Gain Amplifier (PGA) range from 1 to 6.

Integrated 8 + sign bits offset adjustment.

16-bit A/D Converter.

14-bit no missing Code Guaranteed.

24 MHz system clock and 1 MHz or 1.5 MHz or 2 MHz of pixel rate selectable by software reseting.

16-bit/8-bit image data capture.

R channel or G channel or B channel can be used in monochrome mode.

CIS LED light on overlap feature supported to get pure black and white monochrome scan.

Supports black and white of line art data format.

Direct access many types of SRAM/DRAM as image buffer.

32K. 64K. 128K. 256K or 512K with 8-bit data size of SRAM can be used.

64K, 256K, 1M or 4M with 8-bit or 16-bit data size of DRAM can be used.

Builtin shading and gamma correction process.

Shading and gamma process or gamma process only can be disabled.

8-bit or 16-bit of shading coefficient can be used.

8-bit or 14-bit of gamma coefficient can be used.

Full step, half step or micro step of step motor can be use.

Motor coil current can be fine tuned.

Support external bipolar PWM motor driver interface.

Motor speed can be selected from 2 times to 1/16 of exposure time each step.

0 to 255 back tracking step can be programmed.

Motor speed up and slow down with full, ½, ¼, 1/8 scan speed during scanning and back tracking.

Auto parking procedure supported.

Motor speed of scanning or auto-parking can be programmed individually.

CCD lamp PWM driver supported when external bipolar PWM motor driver is used.

LED indicator with on/off or 1/2 Hz, 1 Hz flash mode provided.

7-bit of general I/O port with latched and un-latched input port can be read.

Internal PLL provided to generate 48 MHz for USB SIE use.

Builtin USB transceiver, SIE and SIL processor.

Serial ROM interface for vendor ID and product ID code configuration.

USB Specification Version 1.1 Compliant.

High speed USB device with 12M bps data transmission rate.

Support suspend/resume mode, automatically/Host suspend and Host wake up (resume).

External wake up supported to wake up Host.

Support 1 device configuration and 1 device interface.

Support 4 endpoints includes:

Endpoint 0: Control transfer, 8 bytes packet size of bi-direction data transfer for device setup and configuration.

Endpoint 1: Bulk out transfer, 4 bytes or 8 bytes packet size of unidirection data transfer for scanner control command or scanner table download from Host to scanner.

Endpoint 2: Bulk in transfer, 64 bytes packet size double buffer of unidirection data transfer for scanner image data to Host. One or two bytes of unidirection data transfer for register data read or table read back to Host.

Endpoint 3: Interrupt transfer, 1 bytes packet size of unidirection data transfer for interrupt information to Host.

Bulid in USB 1.1 standard command decoder.

## 1.1 Mega byte transfer rate during image scan in.

Software USB driver for Win98 supported.

Support serial port access bypass USB interface.

Power saving mode supported.

CMOS compatible.

5 V analog and digital power required.

Builtin 5V to 3.3V regulator for the power source of internal logic and USB interface circuit.

100-pin PQFP package (W6668F).

## **Applications:**

Flatbed Scanners.

Sheetfeed Scanners.

Film Scanners.

## 3. PIN CONFIGURATION

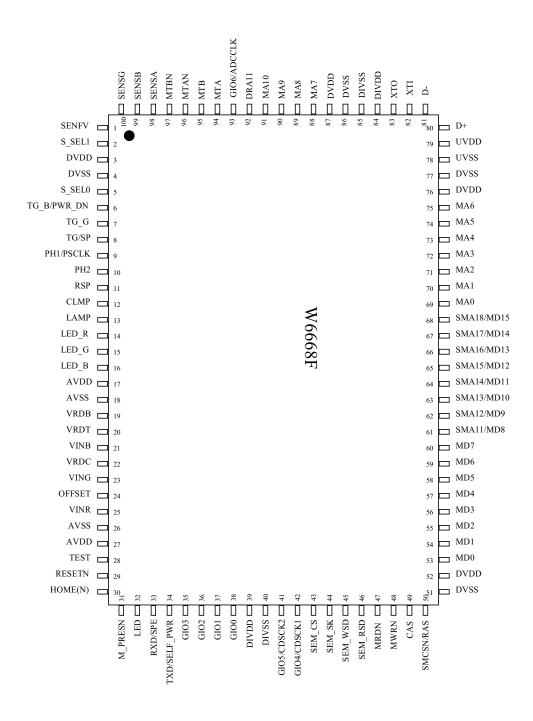

Fig.3-1 W6668F Pin Assignment.

## 4. PIN DESCRIPTIONS

| Pin    | Name            | Туре        | Description                                                                                                                                                                                                 |

|--------|-----------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                 | (mA)        |                                                                                                                                                                                                             |

| CCD/C  | IS Interface:   | T           |                                                                                                                                                                                                             |

| 8      | TG(_R)/SP       | DO(4)       | CCD Transfer Gate (R channel) or CIS Start Pulse.                                                                                                                                                           |

| 7      | TG_G            | DO(4)       | CCD Transfer Gate of G channel channel if three channel TG signal is enabled.                                                                                                                               |

| 6      | TG_B/<br>PWR_DN | DO(4)<br>DI | CCD Transfer Gate of B channel channel if three channel TG signal is enabled. Power down or USB Suspend output, polarity setting during hardware reset, active low if set low at the end of hardware reset. |

| 9      | PH1/PSCLK       | DO(4)       | CCD Phase 1 clock or CIS pixel shift clock.                                                                                                                                                                 |

| 10     | PH2             | DO(4)       | CCD Phase 2 clock.                                                                                                                                                                                          |

| 11     | RSP             | DO(6)       | CCD or CIS Reset Pulse.                                                                                                                                                                                     |

| 12     | CLMP            | DO(4)       | CCD Clamp or CIS Clamp.                                                                                                                                                                                     |

| 14     | LED_R           | DO(2)       | CIS red channel LED driver or CCD red channel electric shutter.                                                                                                                                             |

| 15     | LED_G           | DO(2)       | CIS green channel LED driver or CCD green channel electric shutter.                                                                                                                                         |

| 16     | LED_B           | DO(2)       | CIS blue channel LED driver or CCD blue channel electric shutter.                                                                                                                                           |

| 5      | S_SEL0          | DO(2)       | CCD/CIS sensor channel Select 0.                                                                                                                                                                            |

|        | <u>SMTA</u>     |             | Slave motor driver signal, positive A phase.                                                                                                                                                                |

| 2      | S_SEL1          | DO(2)       | CCD/CIS sensor channel Select 1.                                                                                                                                                                            |

|        | <u>SMTB</u>     |             | Slave motor driver signal, positive B phase.                                                                                                                                                                |

| Analog | Signals Input:  |             |                                                                                                                                                                                                             |

| 25     | VINR            | Al          | Analog Input, R channel.                                                                                                                                                                                    |

| 23     | VING            | Al          | Analog Input, G channel.                                                                                                                                                                                    |

| 21     | VINB            | Al          | Analog Input, B channel.                                                                                                                                                                                    |

| Analog | Reference:      |             |                                                                                                                                                                                                             |

| 20     | VRDT            | AO          | ADC Reference Voltage (Top), top level of the ADC reference range.                                                                                                                                          |

| 19     | VRDB            | AO          | ADC Reference Voltage (Bottom), bottom level of the ADC reference range.                                                                                                                                    |

| 22     | VRDC            | AO          | ADC Reference Voltage (Internal), internal bias level of the ADC reference voltage.                                                                                                                         |

| 24     | OFFSET          | AO/AI       | Clamp Offset Voltage Output or offset voltage input in CIS mode.                                                                                                                                            |

## 4. Pin Description, continued

| Pin    | Name              | Туре   | Description                                                                                |

|--------|-------------------|--------|--------------------------------------------------------------------------------------------|

|        |                   | (mA)   |                                                                                            |

| Analog | Power:            | II.    |                                                                                            |

| 17,27  | AVDD              | AP     | Analog Power (2 pins).                                                                     |

| 18,26  | AVSS              | AP     | Analog Ground (2 pins).                                                                    |

| Image  | Buffer Interface: |        |                                                                                            |

| 75-69  | MA[6:0]           | DO(2)  | Address line [8:0] of SRAM or address line [8:0] of DRAM.                                  |

| 91-88  | MA[10:7]          | DO(2)  | Address line [10:9] of SRAM or address line [10:9] of DRAM.                                |

| 92     | DRA11/            | DO(2)  | Row address line 11 of DRAM.                                                               |

|        | <u>SMTAN</u>      |        | Slave motor driver signal, negative A phase.                                               |

| 68-61  | SMA[18:11]/       | DO/    | Address line [18:11] of SRAM, high byte data bus of DRAM or data bus of                    |

|        | MD[15:8]          | DIO(2) | DRAM if 8-bit data is configured.                                                          |

| 60-53  | MD[7:0]           | DIO(2) | Data bus of SRAM or low byte data bus of DRAM .                                            |

| 50     | SMCSN/            | DO(2)  | Chip Select of SRAM or Raw address strobe of DRAM.                                         |

|        | RAS               |        |                                                                                            |

| 49     | CAS               | DO(2)  | Column Address Strobe of DRAM.                                                             |

| 47     | MRDN              | DO(2)  | Memory Read control signal, active low.                                                    |

| 48     | MWRN              | DO(2)  | Memory Write control signal, also can be used as RD/WR signal of DRAM or SRAM, active low. |

| Motor  | Control Driver S  | ignal: |                                                                                            |

| 94     | MTA               | DO(2)  | Motor driver signal, positive A phase.                                                     |

| 95     | МТВ               | DO(2)  | Motor driver signal, positive B phase.                                                     |

| 96     | MTAN              | DO(2)  | Motor driver signal, negative A phase.                                                     |

| 97     | MTBN              | DO(2)  | Motor driver signal, negative B phase.                                                     |

| 98     | SENSA             | Al     | Motor phase A current sense input signal.                                                  |

| 99     | SENSB             | Al     | Motor phase B current sense input signal.                                                  |

| 100    | SENSG             | Al     | GND (reference) signal of motor phase current sense input.                                 |

| 1      | SENFV             | AI/AO  | Full voltage of motor sense signal.                                                        |

## 4. Pin Description, continued

| Pin      | Name           | Туре  | Description                                                              |

|----------|----------------|-------|--------------------------------------------------------------------------|

|          |                | (mA)  |                                                                          |

| Serial I | ROM Interface: | -     |                                                                          |

| 43       | SEM_CS/        | DO(2) | Serial EEPROM Chip Select.                                               |

|          | DFT_PDS3       | DI    | Default vendorID and product ID select bit 3.                            |

| 44       | SEM_SK/        | DO(2) | Serial EEPROM Serial Clock.                                              |

|          | DFT_PDS2       | DI    | Default vendorID and product ID select bit 2.                            |

| 45       | SEM_WSD/       | DO(2) | Serial EEPROM command Write Serial Data.                                 |

|          | DFT_PDS1       | DI    | Default vendorID and product ID select bit 1.                            |

| 46       | SEM_RSD/       | DI    | Serial EEPROM Read Serial Data.                                          |

|          | DFT_PDS0       |       | Default vendorID and product ID select bit 0.                            |

| USB In   | terface:       |       |                                                                          |

| 80       | D+             | AIO   | USB D plus signal.                                                       |

| 81       | D-             | AIO   | USB D minus signal.                                                      |

| Crysta   | l Driver:      |       |                                                                          |

| 82       | XTI            | DI    | Clock driver input signal, may be used as external clock input.          |

| 83       | хто            | DO    | Clock driver output signal.                                              |

| I/O Sig  | nals:          |       |                                                                          |

| 30       | HOME(N)        | DI    | Optical module home sensor, may be active high or active low.            |

| 32       | LED            | DO(2) | LED indicator.                                                           |

| 13       | LAMP           | DO(2) | CCD Lamp driver, active high.                                            |

| 31       | M_PRESN        | DI    | Manual Push button input, active low, also used as remote wake up input. |

| 35-38    | GIO[3:0]       | DI/DO | General Input Output port [3:0].                                         |

|          |                | (2)   |                                                                          |

| 42       | GIO4/          | DI/DO | General Input Output port 4 or AFE circuit CDSCK1 clock signal.          |

|          | CDSCK1         | (2)   |                                                                          |

| 41       | GIO5/          | DI/DO | General Input Output port 5 or AFE circuit CDSCK2 clock signal.          |

|          | CDSCK2         | (2)   |                                                                          |

| 93       | GIO6/          | DI/DO | General Input Output port 6 or AFE circuit ADCCLK clock signal.          |

|          | ADCCLK/        | (2)   | Slave motor driver signal, negative B phase.                             |

|          | <u>SMTBN</u>   |       |                                                                          |

#### 4. Pin Description, continued

| Pin      | Name         | Туре  | Description                                                                                                  |

|----------|--------------|-------|--------------------------------------------------------------------------------------------------------------|

|          |              | (mA)  |                                                                                                              |

| Serial I | Port Signal: |       |                                                                                                              |

| 33       | RXD/SPE      | DI/DO | Receive Data pin or Serial Port Enable (high setting during reset), must left open when USB port is enabled. |

| 34       | TXD/         | DO/DI | Transmit Data pin when serial port is enabled or device SELF Power                                           |

|          | SELF_PWR     | (2)   | configured if it is high when serial port is disabled.                                                       |

| Other 9  | Signal:      |       |                                                                                                              |

| 29       | RESETN       | DI    | Reset input, hardware reset input, active low.                                                               |

| 28       | TEST         | DI    | Test Input, must left open in normal operation.                                                              |

| Power    |              |       |                                                                                                              |

| 3,52,    | DVDD         | DP    | Digital Power 5.0V (4 pins).                                                                                 |

| 76,87    |              |       |                                                                                                              |

| 4,51,    | DVSS         | DP    | Digital Ground (4 pins).                                                                                     |

| 77,86    |              |       |                                                                                                              |

| 39,84    | DIVDD        | DP    | Digital Internal Power 3.3V (2 pins).                                                                        |

| 40,85    | DIVSS        | DP    | Digital Internal Ground (2 pins).                                                                            |

| 79       | UVDD         | AP    | USB transceiver Power 3.3V.                                                                                  |

| 78       | UVSS         | AP    | USB transceiver Ground.                                                                                      |

Type: AP is Analog Power, AI is Analog Input, AO is Analog Output, DP is Digital Power, DI is Digital Input, DO is Digital Output.

#### 5. BLOCK DIAGRAM & REGISTERS LIST

## 5.1 Block Diagram

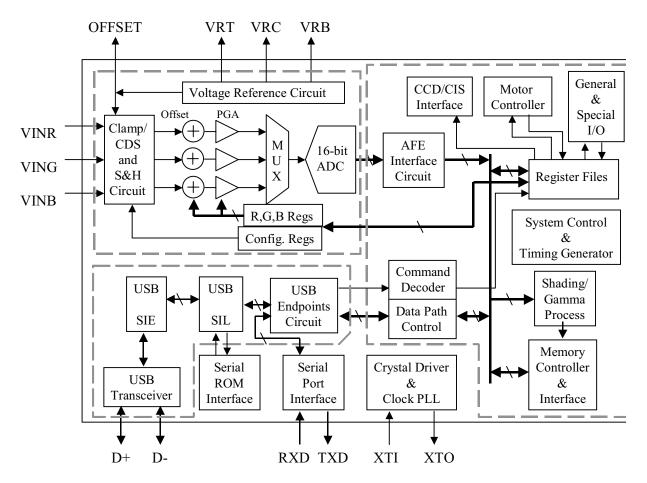

Fig. 5-1 Block Diagram of W6668 Device.

Note: Digital I/O pins are omitted on this figure.

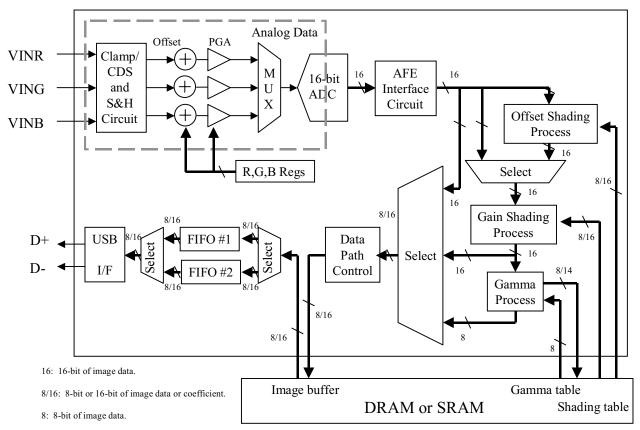

There are three major parts consisted in W6668 device: the first part is analog front end circuit, at the left-top of the block diagram and is described in section 6; the second part is scanner ASIC circuit, at the right side of the block diagram and is described in section 7; the third part is USB interface circuit, at the left-bottom and is described in section 8. USB standard device requests is described in section 9. Figure 5-2 shows the image data processing flow from three channels analog input to USB bulk in to Host.

Fig. 5-2 Image Data Process Flow of W6668 Device.

## 5.2 Register List Tables

Part 1: Analog Front End

| Addr  | Name        | Default |       |       |       | Con   | tent  |       |       |       |

|-------|-------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| (dec) |             | (hex)   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| 00H   | Config Reg. | F8      | IP_   | Vref  | 3-ch  | CDS   | ICLB  | AFE_  | 0     | 0     |

| (0)   |             |         | Span  |       |       |       |       | PD    |       |       |

| 01H   | AFE MUX     | C0      | 1     | Mon_R | Mon_G | Mon_B | 0     | 0     | 0     | 0     |

| (1)   | Reg.        |         |       |       |       |       |       |       |       |       |

| 02H   | PGA code    | 00      | 0     | 0     | PGA_  | PGA_  | PGA_  | PGA_  | PGA_  | PGA_  |

| (2)   | (R-ch)      |         |       |       | R5    | R4    | R3    | R2    | R1    | R0    |

| 03H   | PGA code    | 00      | 0     | 0     | PGA_  | PGA_  | PGA_  | PGA_  | PGA_  | PGA_  |

| (3)   | (G-ch)      |         |       |       | G5    | G4    | G3    | G2    | G1    | G0    |

| 4H    | PGA code    | 00      | 0     | 0     | PGA_  | PGA_  | PGA_  | PGA_  | PGA_  | PGA_  |

| (4)   | (B-ch)      |         |       |       | B5    | B4    | В3    | B2    | B1    | В0    |

| 05H   | DAC code    | 00      | DAC_  |

| (5)   | (R-ch)      |         | R7    | R6    | R5    | R4    | R3    | R2    | R1    | R0    |

| 06H   | DAC code    | 00      | DAC_  |

| (6)   | (G-ch)      |         | G7    | G6    | G5    | G4    | G3    | G2    | G1    | G0    |

| 07H   | DAC code    | 00      | DAC_  |

| (7)   | (B-ch)      |         | B7    | В6    | B5    | B4    | В3    | B2    | B1    | В0    |

| H80   | DAC SIGN    | 00      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | DSIGN |

| (8)   | (R-ch)      |         |       |       |       |       |       |       |       | _R    |

| 09H   | DAC SIGN    | 00      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | DSIGN |

| (9)   | (G-ch)      |         |       |       |       |       |       |       |       | _G    |

| 0AH   | DAC SIGN    | 00      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | DSIGN |

| (10)  | (B-ch)      |         |       |       |       |       |       |       |       | _B    |

Part 2: CCD/CIS and AFE Interface

| Addr  | Name               | Default |       |              |              | Con          | tent         |              |              |           |

|-------|--------------------|---------|-------|--------------|--------------|--------------|--------------|--------------|--------------|-----------|

| (dec) |                    | (hex)   | bit 7 | bit 6        | bit 5        | bit 4        | bit 3        | bit 2        | bit 1        | bit 0     |

| 10H   | Sensor             | 70      | 0     | LEDB_        | LEDG_        | LEDR_        | CLMP_        | PH1_P        | RS_P         | TG_P      |

| (16)  | Signal<br>Polarity |         |       | Р            | Р            | Р            | Р            |              |              |           |

| 11H   | Phase              | 00      | 0     | Diff_        | Three_       | NON_         | ODD/         | <u>PH_</u>   | <u>PH_</u>   | PH_EN     |

| (17)  | Behav<br>Register  |         |       | Exp_<br>MD   | TG           | DUTY         | EVEN_<br>CCD | <u>QBL</u>   | <u>DBL</u>   | _TG       |

| 12H   | Sensor             | 39      | 0     | 0            | S_Bsel       | S_Bsel       | S_Gsel       | S_Gsel       | S_Rsel       | S_Rsel    |

| (18)  | Channel<br>Select  |         |       |              | 1            | 0            | 1            | 0            | 1            | 0         |

| 13H   | TG shift           | 00      | 0     | 0            | 0            | TG_          | TG_          | TG_          | TG_          | TG_       |

| (19)  | (note 1)           |         |       |              |              | S4           | S3           | S2           | S1           | S0        |

| 14H   | TG width           | 00      | 0     | 0            | 0            | 0            | TG_          | TG_          | TG_          | TG_       |

| (20)  | (note 2)           |         |       |              |              |              | W3           | W2           | W1           | W0        |

| 15H   | RSP shift          | 00      | 0     | 0            | 0            | RSP_         | RSP_         | RSP_         | RSP_         | RSP_      |

| (21)  | (note 1)           |         |       |              |              | S4           | S3           | S2           | S1           | S0        |

| 16H   | RSP width          | 00      | 0     | 0            | 0            | RSP          | RSP          | RSP          | RSP          | RSP       |

| (22)  | (note 1)           |         |       |              |              | _W4          | _W3          | _W2          | _W1          | _W0       |

| 17H   | PH shift           | 00      | 0     | 0            | 0            | PH_          | PH_          | PH_          | PH_          | PH_       |

| (23)  | (note 1)           |         |       |              |              | S4           | S3           | S2           | S1           | S0        |

| 18H   | CLMP shift         | 00      | 0     | 0            | 0            | CLMP_        | CLMP_        | CLMP_        | CLMP_        | CLMP      |

| (24)  | (note 1)           |         |       |              |              | S4           | S3           | S2           | S1           | _S0       |

| 19H   | CLMP               | 00      | 0     | 0            | 0            | CLMP_        | CLMP_        | CLMP_        | CLMP_        | CLMP      |

| (25)  | width              |         |       |              |              | W4           | W3           | W2           | W1           | _W0       |

|       | (note 1)           |         |       | _            |              | 27.01/       | 27.01/       |              |              | 25.011    |

| 1AH   | CDSCK1             | 00      | 0     | 0            | 0            | CDCK<br>1_S4 | CDCK<br>1_S3 | CDCK<br>1_S2 | CDCK<br>1_S1 | CDCK<br>1 |

| (26)  | shift              |         |       |              |              | 0.           | 00           | 02           | 0.           | _S0       |

| 4511  | (note 1)           |         |       | 00.01        | 00.017       | 0001         |              | 0001         | 0001         |           |

| 1BH   | CDSCK<br>width     | 00      | 0     | CDCK<br>2_W2 | CDCK<br>2 W1 | CDCK<br>2_W0 | 0            | CDCK<br>1 W2 | CDCK<br>1_W1 | CDCK<br>1 |

| (27)  |                    |         |       |              | *            |              |              |              |              | wo        |

|       | (note 1)           |         |       |              |              |              |              |              |              | _W(       |

## W6668F

Part 2: CCD/CIS and AFE Interface, continued

| Addr        | Name                                             | Default |              |              |              | Con           | tent         |                 |              |                    |

|-------------|--------------------------------------------------|---------|--------------|--------------|--------------|---------------|--------------|-----------------|--------------|--------------------|

| (dec)       |                                                  | (hex)   | bit 7        | bit 6        | bit 5        | bit 4         | bit 3        | bit 2           | bit 1        | bit 0              |

| 1CH<br>(28) | CDSCK2<br>shift<br>(note 1)                      | 00      | 0            | 0            | 0            | CDCK<br>2_S4  | CDCK<br>2_S3 | CDCK<br>2_S2    | CDCK<br>2_S1 | CDCK<br>2<br>_S0   |

| 1DH<br>(29) | Add_Fun_<br>Reg1                                 | 00      | 0            | 0            | 0            | Mtr_no<br>_Mv | 2_Ph_<br>PWM | Algo_<br>Mtr_IF | Dumy_<br>TG  | RSP_<br>Dis_T<br>G |

| 1EH<br>(30) | Exposure time reg * (low byte)                   | ВС      | EXP<br>_T7   | EXP<br>_T6   | EXP<br>_T5   | EXP<br>_T4    | EXP<br>_T3   | EXP<br>_T2      | EXP<br>_T1   | EXP<br>_T0         |

| 1FH<br>(31) | Exposure time reg * (high byte)                  | 05      | EXP<br>_T15  | EXP<br>_T14  | EXP<br>_T13  | EXP<br>_T12   | EXP<br>_T11  | EXP<br>_T10     | EXP<br>_T9   | EXP<br>_T8         |

| 20H<br>(32) | Start of<br>LED R<br>channel *                   | 00      | STRT<br>_R7  | STRT<br>_R6  | STRT<br>_R5  | STRT<br>_R4   | STRT<br>_R3  | STRT<br>_R2     | STRT<br>_R1  | STRT<br>_R0        |

| 21H<br>(33) | (low byte)  Start of LED R channel * (high byte) | 00      | STRT<br>_R15 | STRT<br>_R14 | STRT<br>_R13 | STRT<br>_R12  | STRT<br>_R11 | STRT<br>_R10    | STRT<br>_R9  | STRT<br>_R8        |

| 22H<br>(34) | End of LED<br>R channel *<br>(low byte)          | 00      | END<br>_R7   | END<br>_R6   | END<br>_R5   | END<br>_R4    | END<br>_R3   | END<br>_R2      | END<br>_R1   | END<br>_R0         |

| 23H<br>(35) | End of LED<br>R channel *<br>(high byte)         | 00      | END<br>_R15  | END<br>_R14  | END<br>_R13  | END<br>_R12   | END<br>_R11  | END<br>_R10     | END<br>_R9   | END<br>_R8         |

| 24H<br>(36) | Start of<br>LED G<br>channel *<br>(low byte)     | 00      | STRT<br>_G7  | STRT<br>_G6  | STRT<br>_G5  | STRT<br>_G4   | STRT<br>_G3  | STRT<br>_G2     | STRT<br>_G1  | STRT<br>_G0        |

## W6668F

Part 2: CCD/CIS and AFE Interface, continued

| Addr  | Name                    | Default |       |       |       | Con   | tent  |       |       |       |

|-------|-------------------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| (dec) |                         | (hex)   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| 25H   | Start of<br>LED G       | 00      | STRT  |

| (37)  | channel *               |         | _G15  | _G14  | _G13  | _G12  | _G11  | _G10  | _G9   | _G8   |

|       | (high byte)             |         |       |       |       |       |       |       |       |       |

| 26H   | End of LED              | 00      | END   |

| (38)  | G channel * (low byte)  |         | _G7   | _G6   | _G5   | _G4   | _G3   | _G2   | _G1   | _G0   |

| 27H   | End of LED              | 00      | END   |

| (39)  | G channel * (high byte) |         | _G15  | _G14  | _G13  | _G12  | _G11  | _G10  | _G9   | _G8   |

| 28H   | Start of                | 00      | STRT  |

| (40)  | LED B channel *         |         | _B7   | _B6   | _B5   | _B4   | _B3   | _B2   | _B1   | _B0   |

|       | (low byte)              |         |       |       |       |       |       |       |       |       |

| 29H   | Start of                | 00      | STRT  |

| (41)  | LED B channel *         |         | _B15  | _B14  | _B13  | _B12  | _B11  | _B10  | _B9   | _B8   |

|       | (high byte)             |         |       |       |       |       |       |       |       |       |

| 2AH   | End of LED              | 00      | END   |

| (42)  | B channel * (low byte)  |         | _B7   | _B6   | _B5   | _B4   | _B3   | _B2   | _B1   | _B0   |

| 2BH   | End of LED              | 00      | END   |

| (43)  | B channel * (high byte) |         | _B15  | _B14  | _B13  | _B12  | _B11  | _B10  | _B9   | _B8   |

Part 3: Shading Gamma

| Addr        | Name                     | Default |             |             |            | Con        | tent       |            |            |       |

|-------------|--------------------------|---------|-------------|-------------|------------|------------|------------|------------|------------|-------|

| (dec)       |                          | (hex)   | bit 7       | bit 6       | bit 5      | bit 4      | bit 3      | bit 2      | bit 1      | bit 0 |

| 2CH         | Shad/gam                 | 00      | 0           | 0           | 16-bit_    | 14-bit_    | 0          | 0          | SH_        | SH_   |

| (44)        | ma set<br>Register       |         |             |             | SHAD       | Gamm       |            |            | GM_        | GM_   |

|             | register                 |         |             |             |            | а          |            |            | EN1        | EN0   |

| 2DH         | Start                    | 00      | 0           | 0           | SSDG       | SSDG       | SSDG       | SSDG       | SSDG       | 0     |

| (45)        | Shd_Gm_<br>Address       |         |             |             | _<br>      | _AD_2<br>0 | _AD_1<br>9 | _AD_1<br>8 | _AD_1<br>7 |       |

|             | Reg                      |         |             |             | AD_21      |            |            |            |            |       |

| 2EH         | Start G-ch               | 00      | STO_        | STO_        | STO_       | STO_       | 0          | 0          | 0          | 0     |

| (46)        | Offset Reg               |         | G11         | G10         | G9         | G8         |            |            |            |       |

| 2FH         | (low byte) Start G-ch    | 00      | 0           | 0           | 0          | STO_       | STO_       | STO_       | STO_       | STO_  |

| (47)        | Offset Reg               | 00      | U           | U           | 0          | G16        | G15        | G14        | G13        | G12   |

| (47)        | (high byte)              |         |             |             |            | 010        | 010        | 014        | 010        | 012   |

| 30H         | Start B-ch               | 00      | STO_        | STO_        | STO_       | STO_       | 0          | 0          | 0          | 0     |

| (48)        | Offset Reg               |         | B11         | B10         | В9         | B8         |            |            |            |       |

|             | (low byte)               |         |             | _           | _          |            |            |            |            |       |

| 31H         | Start B-ch<br>Offset Reg | 00      | 0           | 0           | 0          | STO_       | STO_       | STO_       | STO_       | STO_  |

| (49)        | (high byte)              |         |             |             |            | B16        | B15        | B14        | B13        | B12   |

| 32H         | Start R-ch               | 00      | STG_        | STG_        | STG_       | STG_       | 0          | 0          | 0          | 0     |

| (50)        | Gain Reg                 |         | R11         | R10         | R9         | R8         |            |            |            |       |

|             | (low byte)               |         |             |             |            |            |            |            |            |       |

| 33H         | Start R-ch<br>Gain Reg   | 00      | 0           | 0           | 0          | STG_       | STG_       | STG_       | STG_       | STG_  |

| (51)        | (high byte)              |         |             |             |            | R16        | R15        | R14        | R13        | R12   |

| 34H         | Start G-ch               | 00      | STG         | STG         | STG_       | STG        | 0          | 0          | 0          | 0     |

| (52)        | Gain Reg                 |         | G11         | G10         | G9         | G8         |            |            |            |       |

| (- )        | (low byte)               |         |             |             |            |            |            |            |            |       |

| 35H         | Start G-ch               | 00      | 0           | 0           | 0          | STG_       | STG_       | STG_       | STG_       | STG_  |

| (53)        | Gain Reg                 |         |             |             |            | G16        | G15        | G14        | G13        | G12   |

| 2011        | (high byte)              | 00      | 0.7.0       | 0.7.0       | 0.7.0      | OTO        | 0          |            | 0          |       |

| 36H<br>(54) | Start B-ch<br>Gain Reg   | 00      | STG_<br>B11 | STG_<br>B10 | STG_<br>B9 | STG_<br>B8 | 0          | 0          | 0          | 0     |

| (54)        | (low byte)               |         | DII         | БЮ          | D9         | Dŏ         |            |            |            |       |

## W6668F

PRELIMINARY

Part 3: Shading Gamma, continued

| Addr  | Name        | Default |       |       |       | Con   | tent  |       |       |       |

|-------|-------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| (dec) |             | (hex)   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| 37H   | Start B-ch  | 00      | 0     | 0     | 0     | STG_  | STG_  | STG_  | STG_  | STG_  |

| (55)  | Gain Reg    |         |       |       |       | B16   | B15   | B14   | B13   | B12   |

|       | (high byte) |         |       |       |       |       |       |       |       |       |

| 38H   | Start_Img   | 00      | STI_  | STI_  | STI_  | STI_  | 0     | 0     | 0     | 0     |

| (56)  | Reg         |         | AD11  | AD10  | AD9   | AD8   |       |       |       |       |

| , ,   | (low byte)  |         |       |       |       |       |       |       |       |       |

| 39H   | Start_Img   | 00      | 0     | 0     | 0     | STI_  | STI_  | STI_  | STI_  | STI_  |

| (57)  | Reg         |         |       |       |       | AD16  | AD15  | AD14  | AD13  | AD12  |

| ` ′   | (high byte) |         |       |       |       |       |       |       |       |       |

## Part 4: Motor Control

| Addr  | Name                   | Default |       |              |             | Con    | itent |        |       |       |

|-------|------------------------|---------|-------|--------------|-------------|--------|-------|--------|-------|-------|

| (dec) |                        | (hex)   | bit 7 | bit 6        | bit 5       | bit 4  | bit 3 | bit 2  | bit 1 | bit 0 |

| ЗАН   | Motor                  | 00      | AUTO  | <u>MTR</u>   | <u>DUAL</u> | Mtr_C_ | Micro | M_Full | MTR   | MTR   |

| (58)  | behav<br>register      |         | _PK   | <u>DRV_S</u> | <u>MTR</u>  | Ctrl   | _step | _step  | _2PH  | _CDIR |

| 3BH   | Motor                  | 00      | 0     | MTPK         | MTPK        | MTPK   | 0     | MTS    | MTS   | MTS   |

| (59)  | speed<br>register      |         |       | _SP2         | _SP1        | _SP0   |       | _SP2   | _SP1  | _SP0  |

| 3CH   | Motor                  | 00      | PWM_  | PWM_         | PWM_        | PWM_   | PWM_  | PWM_   | PWM_  | PWM_  |

| (60)  | PWM_P<br>register      |         | FC_7  | FC_6         | FC_5        | FC_4   | FC_3  | FC_2   | FC_1  | FC_0  |

| 3DH   | Motor                  | 00      | 0     | 0            | PWM_        | PWM_   | PWM_  | PWM_   | PWM_  | PWM_  |

| (61)  | PWM_D<br>register      |         |       |              | DC_5        | DC_4   | DC_3  | DC_2   | DC_1  | DC_0  |

| 3EH   | Motor                  | 00      | 1/4_  | 1/4_         | 1/4_        | 1/4_   | 1/2_  | 1/2_   | 1/2_  | 1/2_  |

| (62)  | speed up<br>register 1 |         | STP_3 | STP_2        | STP_1       | STP_0  | STP_3 | STP_2  | STP_1 | STP_0 |

| 3FH   | Motor                  | 00      | 0     | 0            | 0           | 0      | 1/8_  | 1/8_   | 1/8_  | 1/8_  |

| (63)  | speed up<br>register 2 |         |       |              |             |        | STP_3 | STP_2  | STP_1 | STP_0 |

| 40H   | Motor                  | 00      | 0     | 0            | 0           | 0      | Mtr_  | Mtr_   | Mtr_  | Mtr_  |

| (64)  | pause step<br>register |         |       |              |             |        | PS_3  | PS _2  | PS_1  | PS _0 |

| 41H   | Back                   | 00      | BKTR  | BKTR         | BKTR        | BKTR   | BKTR  | BKTR   | BKTR  | BKTR  |

| (65)  | tracking reg.          |         | 7     | 6            | 5           | 4      | 3     | 2      | 1     | 0     |

Part 5: Image Buffer, Line Art and Shading Process and Scanning Area

| Addr  | Name                            | Default |           |           |           | Con       | tent      |           |           |           |

|-------|---------------------------------|---------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| (dec) |                                 | (hex)   | bit 7     | bit 6     | bit 5     | bit 4     | bit 3     | bit 2     | bit 1     | bit 0     |

| 42H   | Memory                          | 80      | DRAM      | 0         | 0         | MDS       | 0         | ADDL      | ADDL      | ADDL      |

| (66)  | type<br>register                |         |           |           |           | -16       |           | _2        | _1        | _0        |

| 43H   | Line art                        | 00      | LART_     |

| (67)  | Threshold register              |         | TH7       | TH6       | TH5       | TH4       | TH3       | TH2       | TH1       | TH0       |

| 44H   | Img LL Th                       | 00      | lmg_      | Img_      |

| (68)  | register                        |         | LLT _7    | LLT _6    | LLT _5    | LLT _4    | LLT _3    | LLT _2    | LLT _1    | LLT _0    |

| 45H   | Img FML                         | 00      | lmg_      | Img_      | Img_      | Img_      | Img_      | Img_      | Img_      | lmg_      |

| (69)  | register                        |         | FML<br>_7 | FML<br>_6 | FML<br>_5 | FML<br>_4 | FML<br>_3 | FML<br>_2 | FML<br>_1 | FML<br>_0 |

| 46H   | Start point                     | 00      | STRT      |

| (70)  | of shading<br>reg (low<br>byte) |         | _SDN7     | _SDN6     | _SDN5     | _SDN4     | _SDN3     | _SDN2     | _SDN1     | _SDN0     |

| 47H   | Start point                     | 00      | 0         | 0         | 0         | 0         | STRT      | STRT      | STRT      | STRT      |

| (71)  | of shading<br>reg (high         |         |           |           |           |           | _SDN      | _SDN      | _SDN9     | _SDN8     |

|       | byte)                           |         |           |           |           |           | 11        | 10        |           |           |

| 48H   | Start point                     | 00      | STRT      |

| (72)  | of x-axis<br>reg (low<br>byte)  |         | _X7       | _X6       | _X5       | _X4       | _X3       | _X2       | _X1       | _X0       |

| 49H   | Start point                     | 00      | 0         | 0         | STRT      | STRT      | STRT      | STRT      | STRT      | STRT      |

| (73)  | of x-axis<br>reg (high<br>byte) |         |           |           | _X13      | _X12      | _X11      | _X10      | _X9       | _X8       |

| 4AH   | End point of                    | 00      | END       |

| (74)  | x-axis reg<br>(low byte)        |         | _X7       | _X6       | _X5       | _X4       | _X3       | _X2       | _X1       | _X0       |

| 4BH   | End point of                    | 00      | 0         | 0         | END       | END       | END       | END       | END       | END       |

| (75)  | x-axis reg<br>(high byte)       |         |           |           | _X13      | _X12      | _X11      | _X10      | _X9       | _X8       |

Part 5: Image Buffer, Line Art and Shading Process and Scanning Area, continued

| Addr        | Name                            | Default |             |             |            | Cor         | tent        |             |             |             |

|-------------|---------------------------------|---------|-------------|-------------|------------|-------------|-------------|-------------|-------------|-------------|

| (dec)       |                                 | (hex)   | bit 7       | bit 6       | bit 5      | bit 4       | bit 3       | bit 2       | bit 1       | bit 0       |

| 4CH<br>(76) | Start point of y-axis           | 00      | STRT<br>_Y7 | STRT<br>_Y6 | STRT<br>Y5 | STRT<br>_Y4 | STRT<br>_Y3 | STRT<br>_Y2 | STRT<br>_Y1 | STRT<br>_Y0 |

| (70)        | reg (low<br>byte)               |         | -           | _10         | _10        | _14         | _10         | _12         | _''         | _10         |

| 4DH         | Start point                     | 00      | STRT        | STRT        | STRT       | STRT        | STRT        | STRT        | STRT        | STRT        |

| (77)        | of y-axis<br>reg (high<br>byte) |         | _Y15        | _Y14        | _Y13       | _Y12        | _Y11        | _Y10        | _Y9         | _Y8         |

| 4EH         | End point of                    | 00      | END         | END         | END        | END         | END         | END         | END         | END         |

| (78)        | y-axis reg<br>(low byte)        |         | _Y7         | _Y6         | _Y5        | _Y4         | _Y3         | _Y2         | _Y1         | _Y0         |

| 4FH         | End point of                    | 00      | END         | END         | END        | END         | END         | END         | END         | END         |

| (79)        | y-axis reg<br>(high byte)       |         | _Y15        | _Y14        | _Y13       | _Y12        | _Y11        | _Y10        | _Y9         | _Y8         |

## Part 6: System Control

| Addr  | Name                   | Default |       |       |       | Con   | tent  |       |       |       |

|-------|------------------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| (hex) |                        | (hex)   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| 50H   | Modes                  | 00      | 0     | SHUT_ | COL_  | COL_  | 0     | L_ART | SPEE  | PIX_  |

| (80)  | configure<br>register  |         |       | OVLP  | TYP1  | TYP0  |       |       | D_MD  | MD    |

| 51H   | X-                     | 00      | 0     | 0     | AFE_  | AFE_  | REXL  | REXL  | REXL  | REXL  |

| (81)  | resolution<br>register |         |       |       | DS1   | DS0   | _X3   | _X2   | _X1   | _X0   |

| 52H   | Y-resolution           | 00      | 0     | 0     | 0     | 0     | REXL  | REXL  | REXL  | REXL  |

| (82)  | register               |         |       |       |       |       | _Y3   | _Y2   | _Y1   | _Y0   |

| 5CH   | Command                | 00      | ABRT_ | RESE  | MCKS  | MCKS  | 0     | PARK  | STRT_ | STRT_ |

| (92)  | register               |         | SCN   | T     | _1    | _0    |       |       | NSCN  | SCN   |

## Part 7: General I/O and Special Registers

| Addr         | Name                                  | Default |                |       |              | Con                | tent         |            |                    |            |

|--------------|---------------------------------------|---------|----------------|-------|--------------|--------------------|--------------|------------|--------------------|------------|

| (dec)        |                                       | (hex)   | bit 7          | bit 6 | bit 5        | bit 4              | bit 3        | bit 2      | bit 1              | bit 0      |

| 5EH<br>(94)  | General IO<br>direction<br>register 1 | 0F      | LTHP3          | LTHP2 | LTHP1        | LTHP0              | GDR3         | GDR2       | GDR1               | GDR0       |

| 5FH<br>(95)  | General IO<br>direction<br>register 2 | 07      | 0              | LTHP6 | LTHP5        | LTHP4              | 0            | GDR6       | GDR5               | GDR4       |

| 60H<br>(96)  | General IO register 1                 | 00      | LTHI3          | LTHI2 | LTHI1        | LTHI0              | GIO3         | GIO2       | GIO1               | GIO0       |

| 61H<br>(97)  | General IO register 2                 | 00      | 0              | LTHI6 | LTHI5        | LTHI4              | 0            | GIO6       | GIO5               | GIO4       |

| 62H<br>(98)  | Special_IP register                   | 00      | 0              | 0     | 0            | 0                  | 0            | HOME       | LTH_M<br>-<br>PRES | M_<br>PRES |

| 63H<br>(99)  | LL_driver register                    | 04      | CCD_<br>LPON   | 0     | LEDI_<br>ST1 | LEDI_<br>ST0       | SIG_O<br>_ON | HOME<br>_P | 0                  | 0          |

| 64H<br>(100) | Interrupt<br>enable<br>register       | 00      | Buffer_<br>FUL | EOS   | HOME         | LTH_M<br>-<br>PRES | LTHI3        | LTHI2      | LTHI1              | LTHI0      |

| 65H<br>(101) | Interrupt<br>clear<br>register        | 00      | Buffer_<br>FUL | EOS   | HOME         | LTH_M<br>-<br>PRES | LTHI3        | LTHI2      | LTHI1              | LTHI0      |

| 66H<br>(102) | Add_Fun_<br>Reg2                      | 00      | LAMP_<br>PWM   | 0     | 0            | 0                  | 0            | 0          | 0                  | 0          |

#### 6. SCANNER ASIC CIRCUIT

Scanner ASIC circuit services USB command from USB interface circuit, decodes the commands, control the scanner system and generates timing for CCD/CIS interface, AFE circuit, image buffer memory, motor control and other I/O interface. The image data converted by 16-bit ADC in AFE circuit is buffered in AFE interface circuit, the data will write to image buffer memory and finally transfered to the double FIFO in the USB interface circuit. The reference clock of scanner ASIC circuit is MCLK and is derived from 24 MHz crystal clock and 48 MHz of internal PLL output clock.

## 6.1 Command Decoder and Interrupt

The USB interface will be enabled if the RXD/SPE pin is low. The detail of USB bulk out, bulk in and interrupt in transaction refer to section 9, the address and data definition are listed in each bit content and address mapping tables.

There are four bytes of Host command: command code, address/index\_high, data/index\_low and extend byte.

#### **Command Code:**

Bit [1:0], select which channel of table access.

Bit [1:0] = 00: R-channel.

01: G-channel.

10: B-channel.

11: reserved.

Bit [3:2], select which table to be accessed.

Bit [3:2] = 00: reserved.

01: Offset shading table.

10: Gain shading table.

11: gamma table.

Bit [5:4], reserved (must set to 00).

Bit 6 = 1: table access.

0: register access.

Bit 7, read/write action.

Bit 7 = 1: register or table read.

0: register/command write or table download.

#### Address/Index\_high

#### Defines:

- 1. Register address.

- 2. Table index bit [15:8] of read table action.

#### Data/Index\_low

#### Defines:

- 1. Data of register write.

- 2. Table index bit [7:0] of read table action. 00H is the start byte (or word) of the table, 01H is the next content byte (or word) the table.

#### **Extend Byte:**

Reserved.

## **Command Type**

#### **Software Reset**

The software reset write from Host are via USB bulk out transaction at USB endpoint 1, this command will force to reset the USB command interface and scanner ASIC circuit, the system clock of scanner ASIC and enable/disable of internal 5V to 3.3V regulator also can be configured during software reset. This command must activated before any registers programmed.

- 1. Code byte = 00H.

- 2. Address byte, the address must be (5CH).

- 3. Data byte, the data must be any one of 40H, 48H, 50H, 58H, 60H or 68H.

40H when system clock is 24M, 50H when system clock is 36M, 60H when system clock is 48M, internal 5V to 3.3V power regulator can be disabled by set bit 3 to high.

4 Extend byte, reserved.

#### **Table Download Command**

The table may be offset/gain or gamma of R, G or B channel. The data length of shading table and gamma table is configured in shading/gamma set register. The following bulk out commands must be 8 bytes packet size to download the table, the bulk out command with zero length or less than 8 bytes must activated to end the table download.

- 1. Command code byte: 4XH, bit [3:0] select which channel of which table to be down-loaded.

- 2. Address, this byte is ignored.

- 3. Data byte, this byte is ignored.

- 4. Extend byte, reserved.

#### **Table Read Command**

The table may be offset/gain or gamma of R, G or B channel. The data length of shading table and gamma table is configured in shading/gamma set register. The following bulk in command has two byte to be read if the data length over 8 bits.

- 1. Command code byte: CXH, bit [3:0] select which channel of which table to be read.

- 2. Index high byte: high byte of the table index.

- 3. Index low byte: low byte of the table index.

- 4. Extend byte, reserved.

The USB bulk in transaction for data read in are listed as follows:

- 1. Data byte or data high byte.

- 2. Data low byte, when the data length of the read table is over 8 bits.

#### **Register or Command Write**

The register write or command write from Host are via USB bulk out transaction at USB endpoint 1. The USB bulk out transaction for register or command write are listed as follows:

- 1. Code byte = 00H.

- 2. Address byte:

Bit [7:0], defines the register address map of the W6668.

3. Data byte:

Bit [7:0], is the data to be write to the assigned register.

4. Extend byte, reserved.

#### Register Read

There are two stages for the register read access, the first stage is read command and register address activates from Host through USB bulk out transaction at USB endpoint 1 and the second stage is the data read in via USB bulk in transaction at USB endpoint 2. The start scan, start no scan and park command also can be read back to check the command is processing or finished. The USB bulk out transaction for register read are listed as follows:

- 1. Code byte = 80H.

- 2. Address byte:

Bit [7:0], defines the register address map of the W6668.

3. Data byte:

Bit [7:0], is ignored during read.

4. Extend byte, reserved.

The USB bulk in transaction for data read in are listed as follows:

1. Data byte, data content to be read

#### Scan Command and Image Data In

The image data in command from Host are via USB bulk out transaction at USB endpoint 1. The USB bulk out transaction for scan command and image data in are listed as follows:

- 1. Code byte = 00H.

- 2. Address byte:

The address must be (5CH).

3. Data byte:

The data must be 01H.

4. Extend byte, reserved.

The image data in to Host are via USB bulk in transaction at USB endpoint 2.

#### **Abort Scan Command Write**

The abort scan command write from Host are via USB bulk out transaction at USB endpoint 1, this command will force to transmit the abort scan command from Host to scanner ASIC circuit even if the image data in transaction is going on.

- 1. Code byte = 00H.

- 2. Address byte:

The address must be (5CH).

3. Data byte:

The data must be 80H.

4. Extend byte, reserved.

#### Interrupt In

The data length of interrupt in is one byte, the USB interrupt transaction will be activated if any bit changing from low to high, the interrupt source can be masked (disabled) if write 0 to the related bit in the interrupt enable register. The content of the interrupt in is:

- Bit [3:0]: Latched GIO[3:0] pin, when the signal of LTHI[3:0] bits in General IO register is set.

- Bit 4: Latched M\_PRES, when the signal of LTH\_M\_PRES bit in Special IP register is set.

- Bit 5: HOME, active when the optical module has been back to home position.

- Bit 6: End of Scan, this bit will issue interrupt if the scan command or start no scan command has been processed completely.

- Bit 7: Image buffer full, the motor will stop scan forward and interrupt will be activated with this bit high.

#### 7. USB INTERFACE CIRCUIT

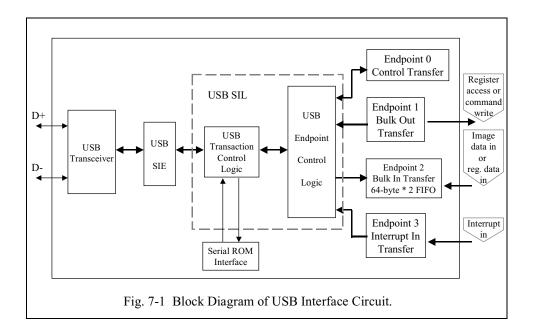

USB interface circuit includes USB transceiver, USB serial interface engine (SIE), USB transaction control logic, USB endpoint control logic and endpoint circuit. The USB transaction control logic and USB endpoint control logic also called USB serial interface logic (SIL). Figure 7-1 shows the detail block diagram of USB interface circuit.

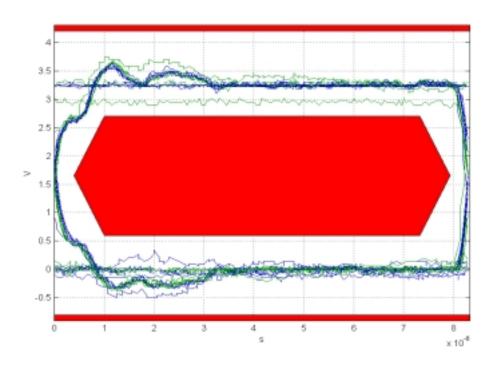

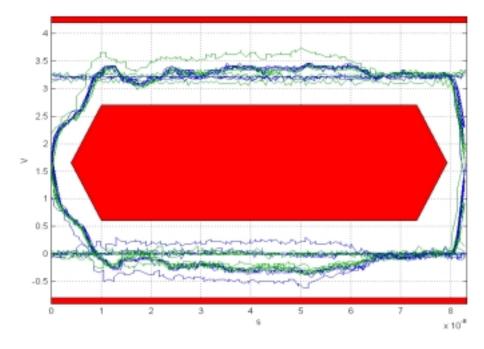

USB transceiver accept analog USB D+ and D- signal from USB Host or USB Hub. The internal digital data stream is converted from the USB D+ and D- and the USB bus state of connect, disconnect, idle, resume and reset are also recognized by the USB transceiver. USB transceiver accept transmit data stream from SIE, convert to analog USB D+ and D- signal and transmit to USB Host or USB Hub. Figure 7-2and 7-3 show the analog eye pattern of USB D+ and D- waveform with 1M of USB cable and 5M of USB cable.

Figure 7-2 Eye Pattern of USB D+ and D- Signals with 1M of USB Cable.

Figure 7-3 Eye Pattern of USB D+ and D- Signals with 5M of USB Cable.

Serial interface engine (SIE) accept the serial data stream from USB transceiver, recognize packet boundary, convert to parallel data and transfer to SIL circuit. The transmit data also converted to serial data stream, packeted and transfered to USB transceiver.

USB serial interface logic (SIL) is consisted of USB transaction control logic and USB endpoint control logic. There are four endpoints consisted in USB interface circuit. Endpoint 0 is control transfer, the transaction is 8 bytes packet size of bi-direction data transfer for device setup and configuration. Endpoint 1 is bulk out transfer, the transaction is 4 bytes packet size of unidirection data transfer for scanner control command from Host to scanner, another transaction is 8 bytes packet size of unidirection data transfer for shading and gamma table download from Host to scanner. Endpoint 2 is bulk in transfer, the main transaction is 64 bytes packet size double buffer of unidirection data transfer for scanner image data to Host, another transaction is one byte of unidirection data transfer for register data read back to Host or one or two bytes of unidirection data transfer for shading and gamma table data read back to Host. There are two 64-byte FIFO in the endpoint 2 circuit and are used to buffered the image data between image buffer memory and USB bulk in transaction. Endpoint 3 is interrupt transfer, the transaction is 1 bytes packet size of unidirection data transfer for interrupt information to Host.

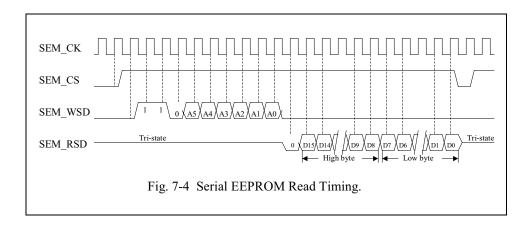

#### 7.2 Serial ROM Access

The serial ROM interface is used to access the serial EEPROM as 93C46 type. The vender ID, product ID are pre-stored in and can be read back after the system is power on or after reset action. Figure 7-4 is the read timing of serial ROM interface. The following table is the content description of the serial EEPROM.

| Address* | Content                             | Description                           |

|----------|-------------------------------------|---------------------------------------|

| 0        | iVender / Device Desc, Low-byte.    | Vender ID.                            |

| 1        | iVender / Device Desc, High-byte.   | Vender ID.                            |

| 2        | iProduct / Device Desc, Low-byte.   | Product ID.                           |

| 3        | iProduct / Device Desc, High-byte.  | Product ID.                           |

| 4        | bcdDevice / Device Desc, Low-byte.  | Device releaseNo. in bcd code.        |

| 5        | bcdDevice / Device Desc, High-byte. | Device releaseNo. in bcd code.        |

| 6        | bmAttribute / Configuration Desc.   | Bit7: Bus Powered.                    |

|          |                                     | Bit6: Self Powered.                   |

|          |                                     | Bit[5:0]: Reserved.                   |

| 7        | MaxPower / Configuration Desc.      | Maximum Power consumption = n x 2 mA. |

<sup>\*:</sup> The address is the byte address not the write address of the EEPROM except address 0.

Table 7-1: Content description of EEPROM.

If no serial ROM is used, the SEM\_CS, SEM\_SK, SEM\_WSD and SEM\_RSD pins also can be used to select the default vender ID and product ID codes during hardware reset action by connecting these four pins to high, the un-connected pin will be recognized as low state. Any of these four pins driven high will disable serial ROM read action and default vender ID and product ID code will be configured. The following table listed the default vendor/product ID can be selected.

| Item | DFT_PDS[3:0] | Vendor/Product ID Code | Description                     |

|------|--------------|------------------------|---------------------------------|

| 0    | 0000         |                        | Serial ROM read access.         |

| 1    | 0001         | 0416/6481              | Winbond Vendor/Product ID Code. |

| 2    | 0010         |                        | Vendor/Product ID Code 1.       |

| 3    | 0011         |                        | Vendor/Product ID Code 2.       |

| 4    | 0100         |                        | Vendor/Product ID Code 3.       |

| 5    | 0101         |                        | Vendor/Product ID Code 4.       |

| 6    | 0110         |                        | Vendor/Product ID Code 5.       |

| 7    | 0111         |                        | Vendor/Product ID Code 6.       |

| 8    | 1000         |                        | Vendor/Product ID Code 7.       |

| 9    | 1001         |                        | Vendor/Product ID Code 8.       |

| 10   | 1010         |                        | Vendor/Product ID Code 9.       |

| 11   | 1011         |                        | Vendor/Product ID Code 10.      |

| 12   | 1100         |                        | Vendor/Product ID Code 11.      |

| 13   | 1101         |                        | Vendor/Product ID Code 12.      |

| 14   | 1110         |                        | Vendor/Product ID Code 13.      |

| 15   | 1111         |                        | Vendor/Product ID Code 14.      |

Table 7-2: Default vendor ID and product ID select table.

## 8. ELECTRICAL CHARACTERISTICS

## 8.1. Maximum Ratings\*

|   | Parameter                                                        | Symbol             | Rating                         | Units                  |

|---|------------------------------------------------------------------|--------------------|--------------------------------|------------------------|

| 1 | Supply Voltage with respect to V <sub>AVSS</sub> (at AVDD pin)   | V <sub>AVDD</sub>  | -0.3 to 6                      | <b>V</b>               |

| 2 | Supply Voltage with respect to V <sub>DVSS</sub> (at DVDD pin)   | $V_{\text{DVDD}}$  | -0.3 to 6                      | ٧                      |

| 3 | Supply Voltage with respect to V <sub>DIVSS</sub> (at DIVDD pin) | $V_{\text{DIVDD}}$ | -0.3 to 6                      | V                      |

| 4 | Supply Voltage with respect to V <sub>UVSS</sub> (at UVDD pin)   | V <sub>UVDD</sub>  | -0.3 to 6                      | V                      |

| 5 | Voltage on any pin other than V <sub>DVSS</sub> supplies         |                    | -0.3 to V <sub>dd5</sub> + 0.3 | V                      |

| 6 | Current at any pin other than supplies                           |                    | 0 to 10                        | mA                     |

| 7 | Storage Temperature                                              | T <sub>st</sub>    | -65 to 150                     | $^{\circ}\!\mathbb{C}$ |

<sup>\*</sup> Exceeding these values may cause permanent damage.

## 8.2. Recommended Operating Conditions

|   | Characteristics                              | Symbol             | Rating       | Unit                   |

|---|----------------------------------------------|--------------------|--------------|------------------------|

| 1 | Operation Voltage (referenced to AVSS pin).  | V <sub>AVDD</sub>  | 4.75 to 5.25 | V                      |

| 2 | Operation Voltage (referenced to DVSS pin).  | $V_{DVDD}$         | 4.75 to 5.25 | V                      |

| 3 | Operation Voltage (referenced to DIVSS pin). | $V_{\text{DIVDD}}$ | 3.0 to 3.6   | V                      |

| 4 | Operation Voltage (referenced to UVSS pin).  | V <sub>UVDD</sub>  | 3.0 to 3.6   | V                      |

| 5 | Clock Frequency                              | fXTL               | 24           | MHz                    |

| 6 | Clock Frequency Tolerance                    | ΔfC                | 100          | PPM                    |

| 7 | Operation Temperature                        | T <sub>op</sub>    | 0 to 70      | $^{\circ}\!\mathbb{C}$ |

## 8.3. Power Supply Characteristics

|   | Parameter                | Condition           | Symbol | Min | Тур‡ | Max  | Units | Test   |

|---|--------------------------|---------------------|--------|-----|------|------|-------|--------|

| 1 | Standby Supply Current   | Power Supply        | IQAVDD |     |      | 0.08 | mA    | Test 1 |

| 2 | Operating Supply Current | $(V_{AVDD} = 5.0V)$ | lavdd  |     | 40   | TBD  | mA    | Test 2 |

<sup>‡:</sup> Typical figure are at  $V_{AVDD}$  = 5.0V and temperature = 25  $^{\circ}$ C and are for design aid only, not guaranteed and not subject to production testing.

Test 1: Configure as power down mode, no analog input.

Test 2: 24 MHz system clock configured.

|   | Parameter                | Condition           | Symbol | Min | Тур‡ | Max  | Units | Test   |

|---|--------------------------|---------------------|--------|-----|------|------|-------|--------|

| 1 | Standby Supply Current   | Power Supply        | IQDVDD |     |      | 0.01 | mA    | Test 1 |

| 2 | Operating Supply Current | $(V_{DVDD} = 5.0V)$ | IDVDD  |     | 5    | TBD  | mA    | Test 2 |

<sup>‡:</sup> Typical figure are at  $V_{DVDD}$  = 5V and temperature = 25  $^{\circ}$ C and are for design aid only, not guaranteed and not subject to production testing.

Test 1: All input pins are  $V_{\text{DVDD}}$  or  $V_{\text{DVSS}}$ , configure as power down mode, output without loading.

Test 2: 24 MHz system clock configured.

|   | Parameter                | Condition            | Symbol             | Min | Тур‡ | Max  | Units | Test   |

|---|--------------------------|----------------------|--------------------|-----|------|------|-------|--------|

| 1 | Standby Supply Current   | Power Supply         | I <sub>Q3.3V</sub> |     |      | 0.05 | mA    | Test 1 |

| 2 | Operating Supply Current | $(V_{DIVDD} = 3.3V)$ | I <sub>D3.3V</sub> |     | 40   | TBD  | mA    | Test 2 |

<sup>‡:</sup> Typical figure are at  $V_{DIVDD}$  = 3.3V and temperature = 25  $^{\circ}$ C and are for design aid only, not guaranteed and not subject to production testing.

Test 1: All input pins are  $V_{\text{DVDD}}$  or  $V_{\text{DVSS}}$ , configure as power down mode, output without loading.

Test 2: 24 MHz system clcok configured.

## 8.4. Digital Characteristics

|   | Parameter                | Condition    | Symbol          | Min | Тур‡ | Max | Units | Notes |

|---|--------------------------|--------------|-----------------|-----|------|-----|-------|-------|

| 1 | Output High Voltage      | (VDVDD = 5V) | Vон             | 4.5 |      |     | V     | 1     |

| 2 | Output Low Voltage       | (VDVDD = 5V) | VOL             |     |      | 0.5 | V     | 2     |

| 3 | High Level Input Voltage | (VDVDD = 5V) | V <sub>IH</sub> | 2.5 |      |     | V     |       |

| 4 | Low Level Input Voltage  | (VDVDD = 5V) | V <sub>IL</sub> |     |      | 1.4 | V     |       |

| 5 | Input Current            |              | lin             |     |      | 1   | uA    |       |

| 6 | Input Capacitance        |              | Cin             |     | 10   |     | pF    |       |

$<sup>\</sup>ddagger$ : Typical figure are at  $V_{DVDD}$  = 5V and temperature = 25  $\,^{\circ}$ C and are for design aid only, not guaranteed and not subject to production testing.

#### **Notes:**

- 1: The current must below or equal to the maximum source current as listed in pin descriptions section.

- 2: The current must below or equal to the maximum sink current as listed in pin descriptions section.

## 8.5. Analog Characteristics (measures from analog input to ADC output)

|     | Parameter                 | Symbol | Min | Тур‡ | Max     | Units | Test Conditions |

|-----|---------------------------|--------|-----|------|---------|-------|-----------------|

| Ana | log to Digital Converter  |        |     |      |         |       |                 |

| 1   | Maximum Conversion Rate   | SPS    |     | 6    |         | MHz   |                 |

| 2   | Resolution                |        |     | 16   |         | Bits  |                 |

| 3   | Integral Nonlinearity     | INL    |     |      | +/- 8   | LSB   |                 |

| 4   | Differential Nonlinearity | DNL    |     |      | +/- 1.5 | LSB   |                 |

8.5. Analog Characteristics (measures from analog input to ADC output), continued

|     | Parameter                                        | Symbol             | Min  | Тур‡   | Max  | Units | Test Conditions          |  |

|-----|--------------------------------------------------|--------------------|------|--------|------|-------|--------------------------|--|

| PG  | PGA & Offset DAC                                 |                    |      |        |      |       |                          |  |

| 1   | PGA Gain Range                                   | G                  | 1.0  |        | 6.0  | V/V   |                          |  |

| 2   | PGA Gain Resolution                              | G <sub>RES</sub>   |      | 6      |      | bits  | Note 1                   |  |

| 3   | Offset Range                                     | OFS                | -350 |        | +350 | mV    | V <sub>AVDD</sub> = 5.0V |  |

| 4   | DAC bit number                                   |                    |      | 8+sign |      | bits  | Note 1                   |  |