# Q2334 DUAL DIRECT DIGITAL SYNTHESIZER

### Other QUALCOMM VLSI Products

- 10-bit and 12-bit Digital to Analog Converters (DAC)

- Phase Locked Loop (PLL)

Frequency Synthesizers

- DDS and PLL Evaluation Boards

- Viterbi Decoders 256 Kbps to 25 Mbps Maximum Data Rates

- Pragmatic Trellis Modulation Codecs to 75 Mbps

- Variable Rate Vocoders

Copyright © 1995. QUALCOMM Incorporated. All rights reserved. Printed in the United States of America.

QUALCOMM® is a registered trademark of QUALCOMM Incorporated.

May 1995 DL90-2334 C

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

|                                                                                                 | NRC Enable 14                                                                        |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                                                                                                 | NRC Enable 14                                                                        |

| FEATURES 4                                                                                      | Accumulator Reset Register                                                           |

|                                                                                                 | (ARR) 15                                                                             |

| APPLICATIONS 4                                                                                  | Asynchronous Hop Clock                                                               |

|                                                                                                 | (AHC) 15                                                                             |

| INTRODUCTION 4                                                                                  | Phase Increment Multiplexer                                                          |

|                                                                                                 | Control 15                                                                           |

| GENERAL DESCRIPTION 5                                                                           | Phase Accumulator 15                                                                 |

| Double Buffered Registers 6                                                                     | Phase Modulation Control 15                                                          |

| Other Registers 6                                                                               | Sine Lookup Function 15                                                              |

|                                                                                                 | Noise Reduction Circuit (NRC) 16                                                     |

| Q2334M-30L MILITARY VERSION                                                                     |                                                                                      |

| DESCRIPTION 6                                                                                   | INPUT/OUTPUT SIGNALS 18                                                              |

|                                                                                                 | Signals Common for                                                                   |

| THEORY OF OPERATION6                                                                            | Both DDSs 18                                                                         |

| General Q2334 DDS Operation 7                                                                   | Signals Independent for                                                              |

| Phase Increment Value 7                                                                         | Each DDS 19                                                                          |

| Frequency Resolution 7                                                                          |                                                                                      |

| Typical DDS Application 8                                                                       | MODES OF OPERATION 20                                                                |

| Spectral Purity 8                                                                               | Basic Synthesizer Mode 20                                                            |

| Clock Source9                                                                                   | Phase Modulation Mode 21                                                             |

| Phase Truncation 9                                                                              | Internal Phase Modulation 21                                                         |

| Amplitude Quantization9                                                                         | External Phase Modulation 21                                                         |

| Spurs Due to Sampling and                                                                       | Binary Frequency Shift Keying (BFSK)                                                 |

| DAC Non-Linearities 10                                                                          | Modulation Mode 22                                                                   |

| Modulation Techniques 10                                                                        | Minimum Shift Keying (MSK)                                                           |

|                                                                                                 | Modulation Mode 22                                                                   |

| INTERNAL ARCHITECTURE 11                                                                        | Frequency Hopping Mode 22                                                            |

| Processor Interface 11                                                                          |                                                                                      |

| Phase Increment Registers (PIRs) 11                                                             | PIPELINE DELAY 23                                                                    |

| Mode Control Registers 11                                                                       |                                                                                      |

| Synchronous Mode Control                                                                        | TYPICAL EXAMPLES AND INITIAL                                                         |

| (SMC) Register 11                                                                               | SETUP OPERATIONS                                                                     |

| Hop Clock Phase Modulation                                                                      | Simple Oscillator Mode                                                               |

| Enable (HPME)                                                                                   | Binary Frequency Shift Keying (BFSK)                                                 |

| External Multiplexer Enable                                                                     | Mode                                                                                 |

| (EME) 12                                                                                        | External Phase Modulation Mode 25                                                    |

| External Phase Modulation                                                                       | Frequency Hopping Mode                                                               |

| Enable (EPME)                                                                                   | Internal Phase Modulation Mode 27                                                    |

| Asynchronous Mode Control                                                                       | DECICAL CONCEDED ATTONIC MUTTE                                                       |

| (AMC) Register                                                                                  | DESIGN CONSIDERATIONS WITH                                                           |

| DAC Strobe, DAC Strobe Invert                                                                   | THE Q2334 28                                                                         |

| (DACSTB, DACSTB/) 13                                                                            | TECHNICAL SPECIFICATIONS 29                                                          |

| Phase Modulation Add                                                                            |                                                                                      |

| Enable (PMAE) 14                                                                                | Absolute Maximum Ratings 29                                                          |

| 2<br>QUALCOMM Incorporated, VLSI Products<br>6455 Lusk Boulevard, San Diego, CA 92121-2779, USA | E-mail: vlsi-products@qualcomm.com<br>Telephone: (619) 658-5005, Fax: (619) 658-1556 |

9003336 0000880 44T **188**

| $\Gamma$ | OC Electrical Characteristics 29                                                    | 6.  | Asynchronous Mode Control                                                            |  |  |  |

|----------|-------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------|--|--|--|

| Т        | iming Specifications 30                                                             |     | (AMC) Register 13                                                                    |  |  |  |

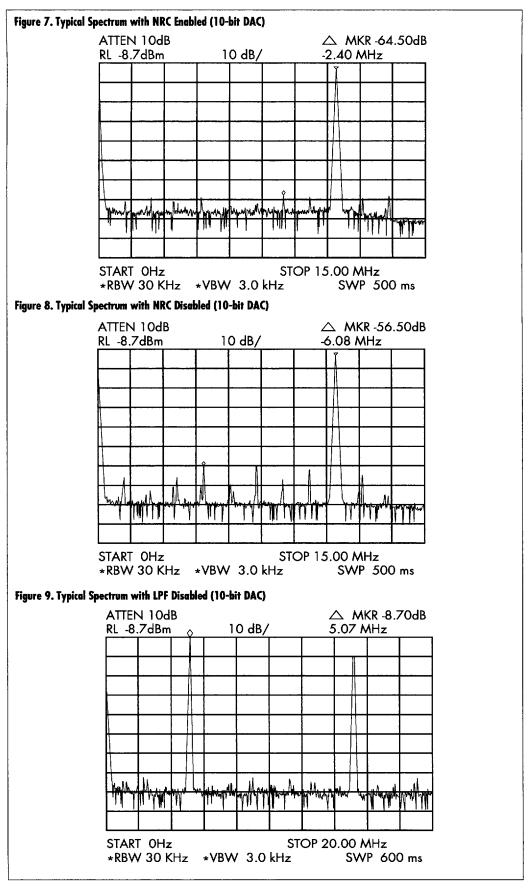

|          |                                                                                     | 7.  | Typical Spectrum with NRC                                                            |  |  |  |

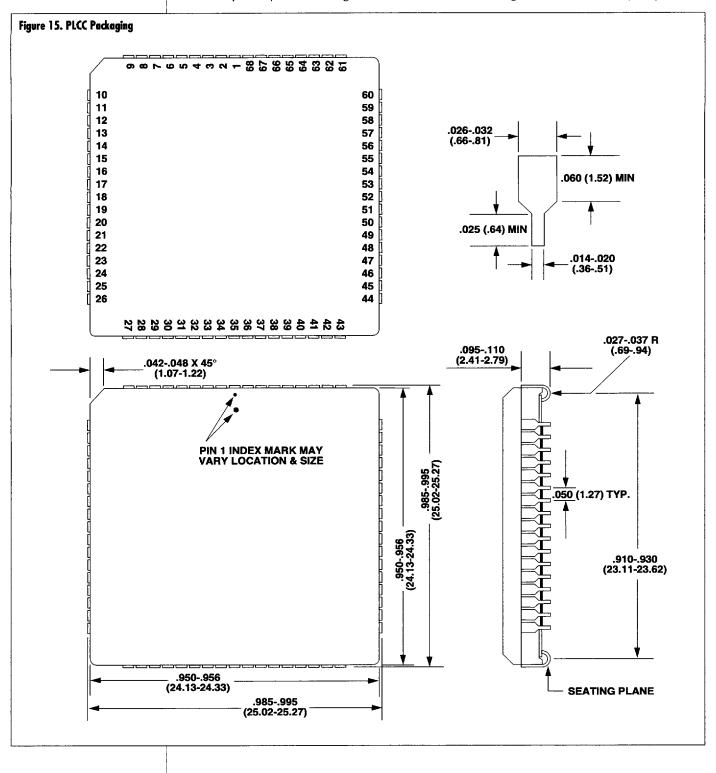

| PLC      | CC PACKAGING (Q2334I-20N,                                                           |     | Enabled (10-bit DAC)17                                                               |  |  |  |

| C        | (2334C-50N)34                                                                       | 8.  | Typical Spectrum with NRC                                                            |  |  |  |

|          |                                                                                     |     | Disabled (10-bit DAC) 17                                                             |  |  |  |

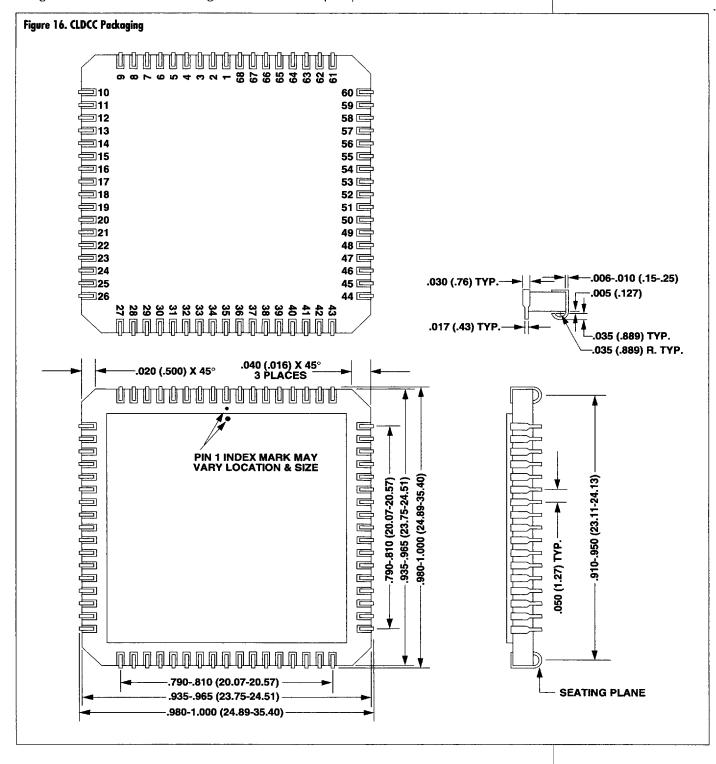

| CLI      | OCC PACKAGING                                                                       | 9.  | Typical Spectrum with LPF                                                            |  |  |  |

| (0       | Q2334M-20L)35                                                                       |     | Disabled (10-bit DAC) 17                                                             |  |  |  |

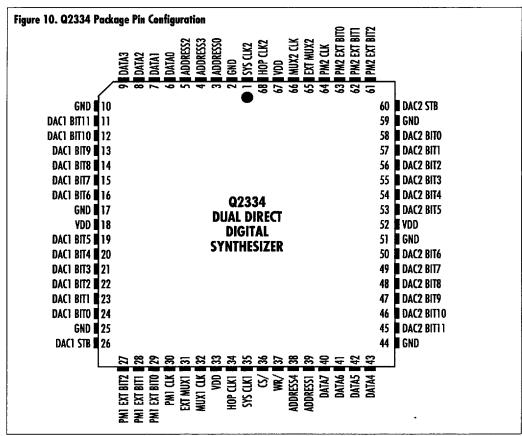

|          |                                                                                     | 10. | Q2334 Package Pin                                                                    |  |  |  |

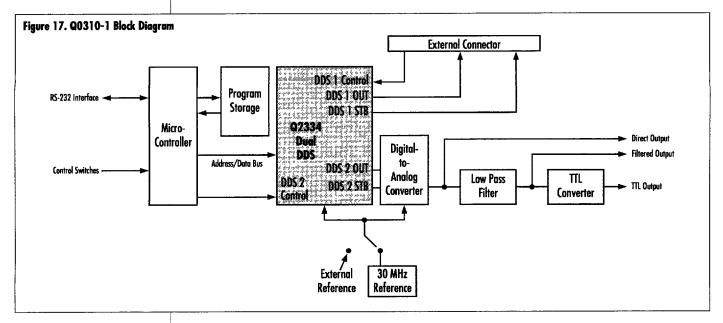

| Q03      | 10-1 DDS EVALUATION                                                                 |     | Configuration 18                                                                     |  |  |  |

| В        | OARD 36                                                                             | 11. | Processor Interface Timing 30                                                        |  |  |  |

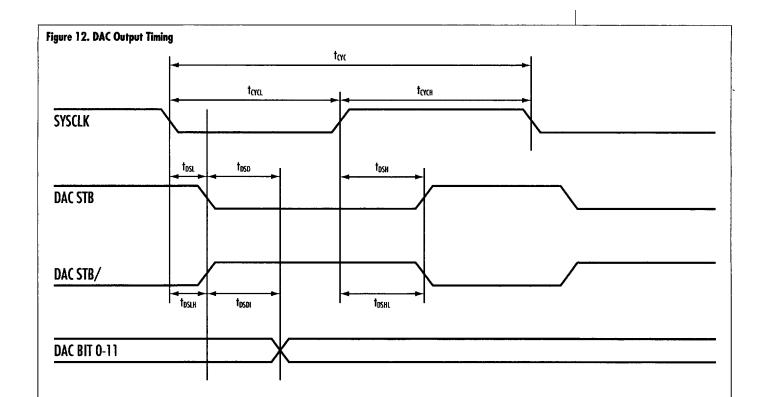

|          |                                                                                     | 12. | DAC Output Timing 31                                                                 |  |  |  |

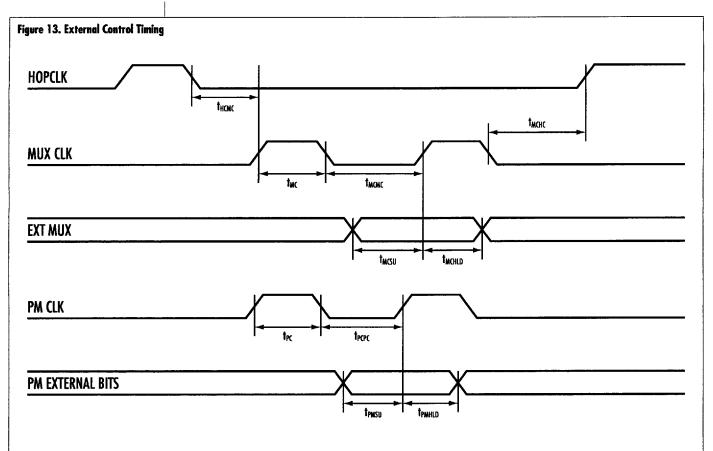

| REC      | COMMENDED SOCKETS 36                                                                | 13. | External Control Timing 32                                                           |  |  |  |

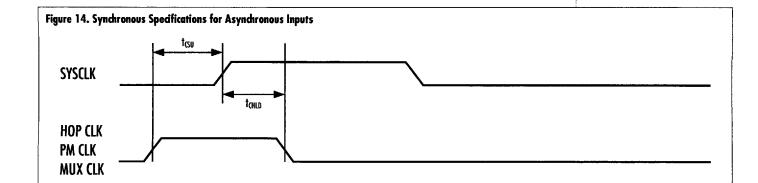

|          |                                                                                     | 14. | Synchronous Specifications for                                                       |  |  |  |

| REC      | COMMENDED DACS 36                                                                   |     | Asynchronous Inputs 33                                                               |  |  |  |

|          |                                                                                     | 15. | PLCC Packaging34                                                                     |  |  |  |

| APF      | PLICATION EXAMPLES AND                                                              | 16. | CDLCC Packaging 35                                                                   |  |  |  |

| F        | REQUENTLY ASKED                                                                     | 17. | Q0310-1 Block Diagram 36                                                             |  |  |  |

| ς        | QUESTIONS 37                                                                        | 18. | Q2334 DDS System 37                                                                  |  |  |  |

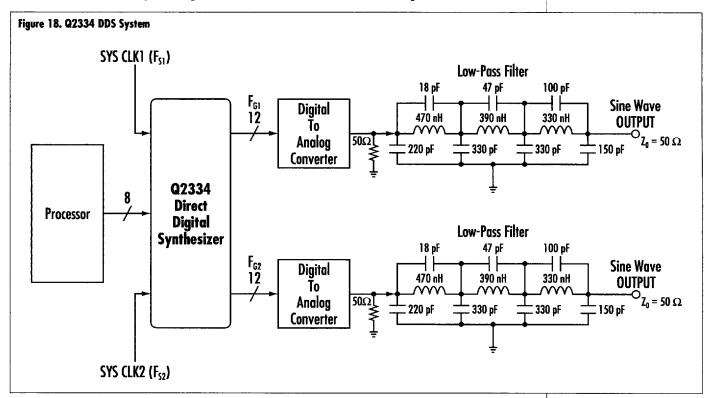

| Γ        | DDS System Diagram 37                                                               | 19. | Quadrature Signal                                                                    |  |  |  |

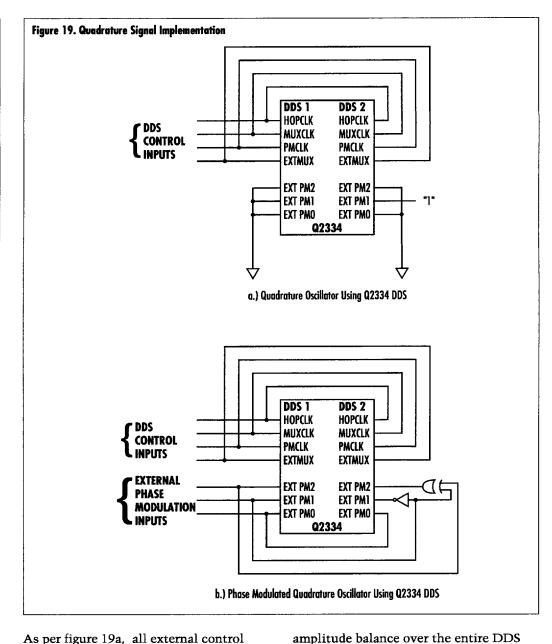

|          | Quadrature Signal Generation with                                                   |     | Implementation                                                                       |  |  |  |

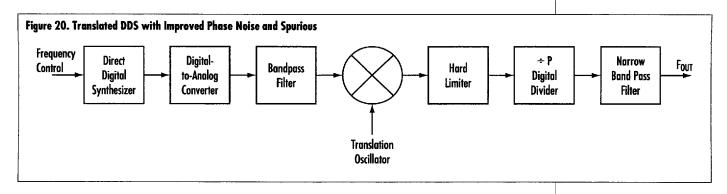

|          | the Q2334 37                                                                        | 20. | Translated DDS with Improved                                                         |  |  |  |

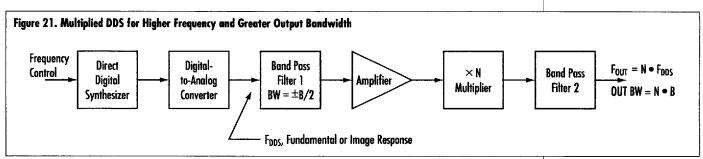

| Г        | Divided/Multiplied/Translated DDS                                                   |     | Phase Noise and Spurious 39                                                          |  |  |  |

|          | Fundamental or Image 39                                                             | 21. | Multiplied DDS for Higher                                                            |  |  |  |

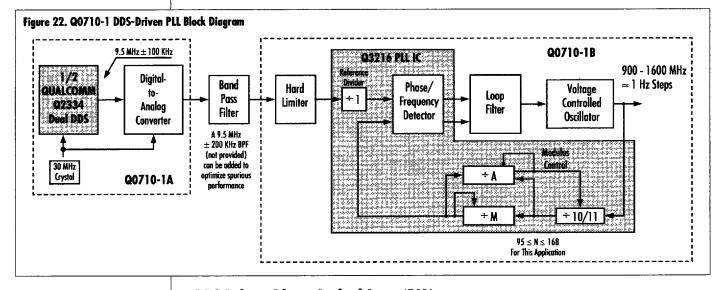

| Г        | DDS-Driven Phase Locked                                                             |     | Frequency and Greater Output                                                         |  |  |  |

|          | Loop (PLL) 40                                                                       |     | Bandwidth 39                                                                         |  |  |  |

| C        | Common Questions about the                                                          | 22. |                                                                                      |  |  |  |

|          | Q2334 DDS 41                                                                        |     | Diagram 40                                                                           |  |  |  |

|          | •                                                                                   |     | J                                                                                    |  |  |  |

| GLO      | OSSARY 42                                                                           | TAI | BLES                                                                                 |  |  |  |

|          |                                                                                     | 1.  | Microprocessor Interface Register                                                    |  |  |  |

| REL      | ATED QUALCOMM                                                                       |     | Address Map 10                                                                       |  |  |  |

|          | ITERATURE 43                                                                        | 2.  | DAC Output Formats 14                                                                |  |  |  |

|          |                                                                                     | 3.  | External Phase Modulation Offset                                                     |  |  |  |

| PAT      | TENT REFERENCES 43                                                                  |     | Settings 16                                                                          |  |  |  |

|          |                                                                                     | 4.  | Q2334 Input/Output Signals 19                                                        |  |  |  |

| ORI      | DERING INFORMATION 43                                                               | 5.  | Absolute Maximum Ratings 29                                                          |  |  |  |

|          |                                                                                     | 6.  | DC Electrical Characteristics 29                                                     |  |  |  |

| FIG      | URES                                                                                | 7.  | Q2334 Ordering Information 43                                                        |  |  |  |

| 1.       | Q2334 Dual DDS Block Diagram . 5                                                    |     |                                                                                      |  |  |  |

| 2.       | Sample Sine Wave 6                                                                  |     |                                                                                      |  |  |  |

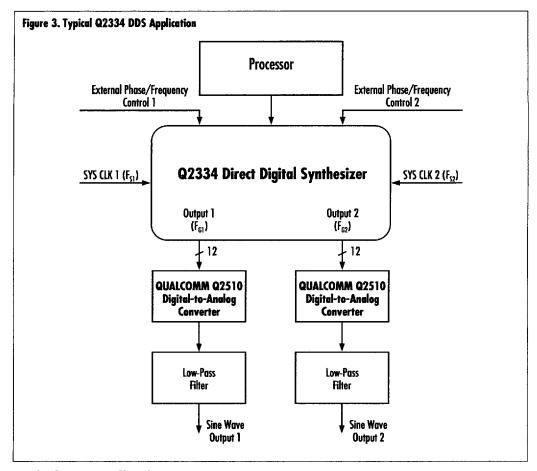

| 3.       | Typical Q2334 DDS Application 8                                                     |     |                                                                                      |  |  |  |

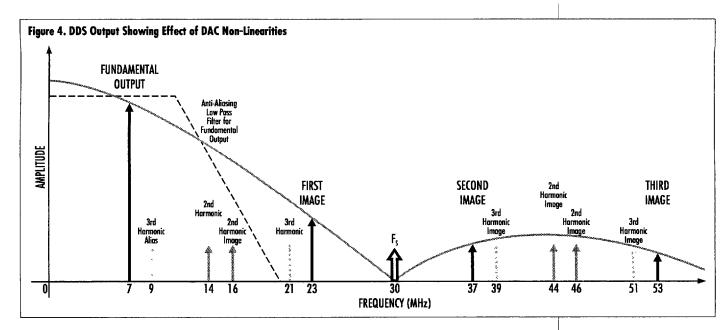

| 4.       | DDS Output Showing Effect of                                                        |     |                                                                                      |  |  |  |

| •        | DAC Non-Linearities9                                                                |     |                                                                                      |  |  |  |

| 5.       | Synchronous Mode Control                                                            |     |                                                                                      |  |  |  |

|          | (SMC) Register 11                                                                   |     |                                                                                      |  |  |  |

|          | , , , ,                                                                             |     | 3                                                                                    |  |  |  |

|          | ALCOMM Incorporated, VLSI Products<br>Lusk Boulevard, San Diego, CA 92121-2779, USA |     | E-mail: vlsi-products@qualcomm.com<br>Telephone: (619) 658-5005, Fax: (619) 658-1556 |  |  |  |

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

### **FEATURES**

- Two Complete Direct Digital Synthesizer Functions On-chip

- MIL-STD 883 Screened Devices Available

- Processor Interface for Control of Phase and Frequency

- Patented Algorithmic Sine Lookup

Function

- Patented Noise Reduction Circuit

- Synchronous PSK and FSK Modulation Inputs

- 2 Maximum Clock Speed Versions:

20 MHz, and 50 MHz

- Phase Resolution: 0.00000008° using Processor-controlled Phase Adjustment

- Double Buffered Registers Allow Synchronous, Phase Coherent Frequency Change

- Simple External Multiplex Control for Binary Frequency Shift Keying (BFSK) Modulation

- Low Power: 267 mW maximum at 20 MHz, and 667 mW maximum at 50 MHz Clock Frequency per DDS

- Evaluation Board Available Q0310-1

- Built-in frequency ramp function available using internal chirp mode

### **APPLICATIONS**

- Spread Spectrum Modulators

- Quadrature Oscillators

- Programmable Frequency Synthesizers

- Satellite Receivers

- Cellular Base Stations

- Magnetic Resonance Imaging

- VXI-based ATE

- SONAR/RADAR

- Paging Systems

- High Performance Test Equipment

- Digital Radios and Modems

- HF Transceivers

- Local Oscillator Generation for VSAT, DBS, and GPS Applications

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA

### INTRODUCTION

The QUALCOMM Q2334 family of Dual Direct Digital Synthesizers (DDS) generates high resolution digitized sine wave signals using phase accumulation techniques combined with a patented onchip sine lookup and Noise Reduction Circuit (NRC). The Q2334 contains two independent DDS functions controlled from a single microprocessor interface. This interface controls both the phase and the frequency of the generated sine waves as well as the device's operating mode. Synchronous inputs are also provided to allow for phase and frequency modulation.

The Q2334 provides greater than 76 dB rejection of phase truncation spurs and 72 dB amplitude quantization signal-to-noise ratio. Two pin compatible versions of the Q2334 DDS are available: 20 MHz and 50 MHz maximum clock speeds. This synthesizer is ideally suited for applications requiring high resolution sine wave generation, fast phase and frequency switching, and excellent phase and frequency stability.

The two independent on-chip DDS functions provide an efficient technique for implementation of full-duplex systems, quadrature oscillators, and spread spectrum systems.

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

Q2334

■ 212 S880000 4EEE00P ■

### **GENERAL DESCRIPTION**

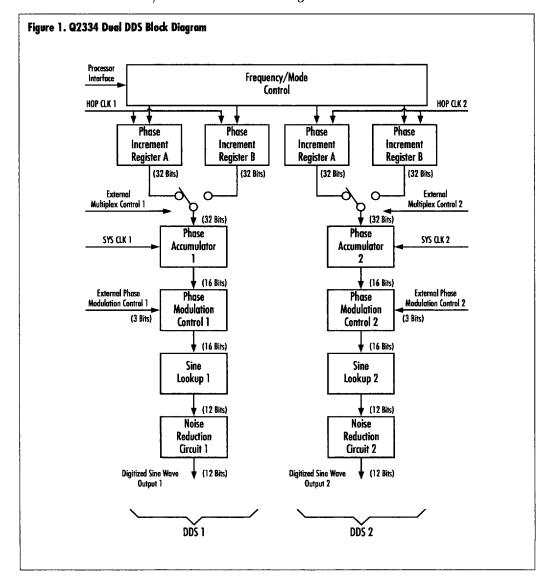

The Q2334 device consists of two independent DDS functions, each controlled by a common microprocessor interface, as illustrated in the figure 1 block diagram. Each DDS contains the following:

- Two Phase Increment Registers (PIR),

A and B

- External Multiplex (Phase Increment Register) Control

- 32-Bit Wide Phase Accumulator

- 3-Bit External Phase Modulation Control

- Patented Sine Lookup Algorithm (see Patent Reference 1)

Patented Noise Reduction Circuit (NRC) (see Patent Reference 2)

The processor interface controls the phase and frequency of the Q2334 DDS. The specific mode of the DDS operation is controlled by the Synchronous Mode Control (SMC) register and the Asynchronous Mode Control (AMC) register. The SMC register is double buffered. That is, values loaded into the SMC registers are synchronously enabled when the HOP CLK signal is asserted. The value loaded into the AMC registers does not require activation by any other signal.

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556 Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

**-** 9003336 0000883 159 **-**

### **Double Buffered Registers**

The SMC register and the two PIRs are double buffered. That is, these registers can be loaded at any time using the processor interface, but the values become active only when the signal HOP CLK is asserted. This makes possible the advanced synchronous phase and frequency change features of the Q2334 device which are especially important when using the device in modulation or phase-locked loop applications.

The Asynchronous Hop Clock (AHC) can also be used to activate the double-buffered settings. See the Asynchronous Hop Clock section on page 15 for more information.

### **Other Registers**

The AMC register has an active value once the information has been written to it. This register does not require a HOP CLK signal to become active.

# Q2334M-30L MILITARY VERSION DESCRIPTION

The Q2334M-30L is packaged in a 68-pin hermetically sealed ceramic leaded chip carrier (CLDCC). Device assembly is in accordance with MIL-STD-883 for Class B microcircuits. Screening and inspection of all devices is in accordance with Method 5004. Quality conformance

inspection requirements of all devices are in accordance with Method 5005 of MIL-STD-883 for Class B microcircuits for Group A and Group B testing.

The maximum sustainable junction temperature for the device is +150°C. Based on testing, the Q2334M-30L can be safely rated for continuous operation in still, ambient air at +125°C. Higher ambient conditions may be possible if active cooling or other means to convect thermal energy away from the part is provided. It is the customer's responsibility to perform the necessary thermal calculations for operation above 125°C.

### THEORY OF OPERATION

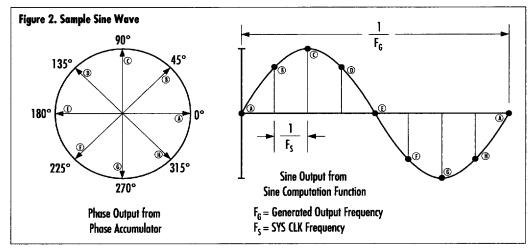

A Direct Digital Synthesizer works on the principle that a digitized waveform of a given frequency can be generated by accumulating phase changes at a higher frequency. Sampling theory requires that the generated frequency be no more than ½ of the clock frequency (Nyquist rate).

Figure 2 shows the phase accumulation of a generated sine wave whose frequency is equal to ½th of the clock frequency. The circle shows the phase accumulation process of ¾ at each clock cycle. The dots on the circle represent the phase value at a given time and the sine wave shows the

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

■ 900333b 0000884 095 **■**

corresponding amplitude representation. This phase to amplitude conversion occurs in the sine lookup. Note that the phase increment added during each clock period is  $\frac{\pi}{4}$  radians, which =  $\frac{1}{8}$ th of  $2\pi$ .

### **General Q2334 DDS Operation**

The block diagram in figure 1 shows the internal structure of the Q2334 DDS device. The phase value stored in PIRA or PIRB is added to the value in the phase accumulator once during each period of the system clock. The resulting phase value (from 0 to  $2\pi$ ) is then applied to the patented sine lookup once during each clock cycle. The lookup converts the phase information to its corresponding sine amplitude, as is illustrated in figure 2. This value is then passed through the patented NRC, which, when enabled, reduces spur heights caused by periodic repetition of the amplitude quantization error (reference the Noise Reduction Circuit section on page 16). The digital word is then output from the Q2334 DDS device.

### **Phase Increment Value**

To output a particular frequency, the associated phase increment value must be loaded into the PIR. The generated frequency ( $F_G$ ) and clock frequency ( $F_S$ ) are related to the phase increment value ( $\Delta \varphi$ ) by the following equation:

$$F_G = \frac{F_S \bullet \Delta \phi}{2^N} \tag{1}$$

where N equals the number of bits in the phase accumulator.

Using this formula, frequency resolution can be generated in exact Hz steps. For example, given a system clock of 30 MHz and a desired generated frequency of 7.5 MHz with a 32-bit phase

accumulator:

$$F_S = 30 \text{ MHz}$$

$$F_G = 7.5 \text{ MHz}$$

$$N = 32$$

Using formula (1) above

7.5 MHz =

$$(30 \text{ MHz} \bullet \Delta \phi)/2^{32}$$

$\Delta \phi = (7.5 \text{ MHz})(2^{32})/30 \text{ MHz}$

=  $2^{30} = 40000000 \text{ (hex)}$

For example, using 2<sup>25</sup> Hz (33,554,432Hz) as the clock frequency, an exact decimal frequency (in Hz) can be generated:

Given:

$$F_S = 2^{25} \text{ Hz} = 33,554,432 \text{ Hz}$$

$$N = 32$$

Frequency Resolution =  $2^{25} \text{ Hz}/2^{32}$

$$= 1 \text{ Hz}/2^7$$

Therefore,  $F_G = \{1 \text{ Hz}/2^7\} \bullet \Delta \phi$

if we choose  $\Delta \phi = 2^7 \text{ (80 hex)}$ ,

then  $F_G = 1 \text{ Hz}$

if we choose  $\Delta \phi = 2^8 \text{ (100 hex)}$ ,

then  $F_G = 2 \text{ Hz}$

if we choose  $\Delta \phi = 2^7 \text{ (200 hex)}$ ,

then  $F_G = 4 \text{ Hz}$

### **Frequency Resolution**

Any frequency can be generated by programming the phase change within the bit resolution of the phase accumulator (the Q2334 DDS phase accumulator registers are 32 bits wide). The frequency resolution can be determined by the following formula:

Frequency Resolution =

$$F_S/2^N$$

(2)

where

$F_S$  = frequency of the system clock N = # of bits in the phase accumulator

For example, using the Q2334I-20N where the  $F_S = 20$  MHz, and N = 32:

Frequency Resolution =  $20 \text{ MHz}/2^{32}$ = 0.00465 Hz

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556 Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

### Typical DDS Application

Figure 3 illustrates a typical synthesizer application of the Q2334 Dual DDS. This figure shows all of the external functions required for a powerful two-channel synthesizer system. Each digitized sine wave output from the DDS device is converted to an analog waveform by a Digital-to-Analog Converter (DAC). The output of the DAC has the desired sine wave as a major component, but also includes the higher frequency image components due to the conversion of a sampled waveform. A Low Pass Filter (LPF) is used to reduce these image signals to the desired level, as shown in figure 4. The pass band of the LPF should be equal to or less than half the sample frequency.

The two DDS devices contained in the Q2334 function independently and the use of a single clock source or two

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA independent clock sources is supported. The DDS outputs are totally independent from one another unless a relationship is established between the two.

### **Spectral Purity**

The spectral quality of a DDS system is dependent upon a number of factors, including: the phase noise of the clock source; the number of phase bits applied to the sine lookup function (i.e., phase truncation, which is an internal operation of the DDS and cannot be externally influenced); and the number of bits output from the lookup (i.e., amplitude truncation).

The specifications of the DAC, LPF design, and circuit card design also affect the quality of the converted sine wave. The linearity and glitch energy specifications of the DAC are especially important to the generation of pure sine

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

■ 9003336 0000886 968 **■**

wave signals. Careful attention to layout of the printed circuit design is important to limiting the noise of the synthesizer. Digital switching and power supply noise must be limited from coupling with clock and analog signals.

### Clock Source

The clock source input to a DDS system is the major contributor to the phase noise of the system, even though its effect is reduced by the frequency division process of the DDS. The phase noise of the DDS output will show an improvement over phase noise of the clock source itself of 20 • log(F<sub>S</sub>/F<sub>G</sub>), where F<sub>S</sub> is the system clock frequency and F<sub>G</sub> is the generated frequency.

The frequency accuracy of the clock is propagated through the DDS. Therefore, if the sampling frequency is 1000 PPM higher than desired, the output frequency will be higher by 1000 PPM.

### **Phase Truncation**

The Q2334 accumulates 32 bits of phase information. The 16 Most Significant Bits (MSB) are input to the sine lookup algorithm. This reduced number of phase

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA bits input to the sine lookup function is called phase truncation. Phase Truncation is an internal operation of DDSs and cannot be externally influenced. The truncation of the 16 Least Significant Bits (LSB) is a loss of phase information and contributes errors. However, the spurs caused by phase truncation errors are below 76 dBc.

### **Amplitude Quantization**

Amplitude quantization occurs in the sine lookup process. The lookup takes in 16 bits of phase information and converts it to the equivalent sine amplitude. Since an ideal sine representation would require an infinite number of bits for most values, the value must be truncated. The Q2334 quantizes the values and outputs the 12 MSBs as the sine amplitude representation, which is the current limit of practical high-speed DACs.

Since the sine function is a periodic function, errors associated with the quantization can become highly correlated and produce noticeable spurs. To ensure the highest possible performance, QUALCOMM developed a

Telephone: (619) 658-5005, Fax: (619) 658-1556

E-mail: vlsi-products@qualcomm.com

02334 **DUAL DIRECT** DIGITAL SYNTHESIZER TECHNICAL DATA SHEET DATA SUBJECT TO CHANGE WITHOUT NOTICE

9003336 0000887 814

Noise Reduction Circuit (NRC) to minimize the effects of amplitude quantization (see Patent Reference 2). Reference the Noise Reduction Circuit section on page 16 for more information.

### Spurs Due To Sampling And DAC Non-Linearities

The frequencies of the discrete spurs and the amplitude of each are dependent on the ratio of the generated frequency ( $F_G$ ) to the clock frequency ( $F_S$ ), as well as the phase relationship of the output waveform to the sample clock. The 12-bit digitized sine output theoretically will provide a broadband signal-to-spurious ratio of 72 dB, again depending on the quality of the DAC and the LPF design as well as the printed circuit characteristics and the phase noise of the clock frequency.

The DDS device is able to generate frequencies from 0 Hz to ½ the frequency of the clock. However, limitations on the slope of the roll off of the LPF determine the practical upper limit of the output frequency to about 40% of the clock

frequency. Let  $F_S$  indicate the frequency of the system clock, and  $F_G$  indicate the generated frequency. Discrete images due to sample rate aliasing will be produced at frequencies of  $F_S$ - $F_G$ ,  $F_S$ + $F_G$ ,  $2F_S$ - $F_G$ ,  $2F_S$ + $F_G$ , and so forth, unless the LPF filters these images to acceptable levels (see figure 4).

Notice a sinc  $[(\pi \bullet F_G)/F_S]$  envelope is impressed upon all of the DDS outputs in figure 4 ( $\approx \Delta$  4dB from DC up to  $(F_S/2)$ ).

### **Modulation Techniques**

The use of phase and frequency modulation techniques has become common for the transmission of digital bitstreams through channels ranging from telephone lines to high data rate satellite channels. The Q2334 DDS device provides features which allow the basic frequency synthesis function to be expanded and used for a variety of phase and frequency modulation schemes. Reference the Modes of Operation section beginning on page 20 for more information.

| Table 1. Microprocessor | Interface Register Address Map |

|-------------------------|--------------------------------|

|-------------------------|--------------------------------|

| DDS1 REGISTER<br>ADDRESS | DDS2 REGISTER ADDRESS | FUNCTION                                  |

|--------------------------|-----------------------|-------------------------------------------|

| 00H                      | 10H                   | Phase Increment A (PIRA) bits 0-7 (LSB)   |

| 01H                      | 11H                   | Phase Increment A (PIRA) bits 8-15        |

| 02H                      | 12H                   | Phase Increment A (PIRA) bits 16-23       |

| 03H                      | 13H                   | Phase Increment A (PIRA) bits 24-31 (MSB) |

| 04H                      | 14H                   | Phase Increment B (PIRB) bits 0-7 (LSB)   |

| 05H                      | 15H                   | Phase Increment B (PIRB) bits 8-15        |

| 06H                      | 16H                   | Phase Increment B (PIRB) bits 6-23        |

| 07H                      | 17H                   | Phase Increment B (PIRB) bits 24-31 (MSB) |

| 08H                      | 18H                   | Synchronous Mode Control (SMC)            |

| 09H                      | 19H                   | Reserved                                  |

| OAH                      | 1AH                   | Asynchronous Mode Control (AMC)           |

| OBH                      | 1 BH                  | Reserved                                  |

| OCH                      | 1CH                   | Accumulator Reset Register (ARR)          |

| ODH                      | 10H                   | Reserved                                  |

| OEH                      | 1EH                   | Asynchronous Hop Clock (AHC)              |

| OFH                      | 1FH                   | Reserved                                  |

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

**9**003336 0000888 730 **5**

### INTERNAL ARCHITECTURE

The Q2334 device includes two identical, independent DDS functions with a common microprocessor interface (see figure 1). Each DDS includes two double-buffered phase increment registers, two mode control registers (SMC, and AMC), a phase increment multiplexer, a phase accumulator, a phase modulation control, a sine lookup function, and a noise reduction function. These components, and the processor interface, are described in detail in the following paragraphs.

### **Processor Interface**

The processor interface is compatible with commonly used 8-bit microprocessors. This interface includes address decoding, chip selection, and write controls to load all on-chip control and phase increment registers. Table 1 provides the register address map for the device. Each register is write-only and is decoded from the five-bit input address bus. It is important to note that the addresses listed as "Reserved" are not used and should not be written.

### Phase Increment Registers (PIRs)

Two independent 32-bit phase increment registers (A and B) are provided for each DDS function in the Q2334 device. Each phase increment register is 32-bits wide. Phase Increment Register A (PIRA) of each DDS provides the phase increment

for the most basic single-frequency operation. Phase Increment Register B (PIRB) provides the phase increment for a range of functions useful in various modes of operation of the DDS. The 32-bit value for each register is loaded using four 8-bit write operations. As stated previously, each PIR is double-buffered and the phase increment used by the phase accumulator is unaffected by this new stored value until a positive transition in the HOP CLK signal occurs.

### **Mode Control Registers**

Each DDS function on the Q2334 device includes two mode control registers: a Synchronous Mode Control (SMC) register and an Asynchronous Mode Control (AMC) register. The SMC is used for operations that may change throughout the operation of the DDS. The AMC should be setup once during initialization (please note that in figures 5 and 6, the unused bits must be set to "0" for proper operation).

### Synchronous Mode Control (SMC) Register

The Synchronous Mode Control (SMC) register is double buffered to update control information, which will affect the actual DDS operation only when synchronously enabled by the transition of the HOP CLK signal. Figure 5 provides the bit definition for this SMC register. Bit 0 (LSB), 4, 5, 6, and 7 are reserved and

| D7 | D6 | D5 | D4 | D3                                       | D2                            | D1                                   | DO |

|----|----|----|----|------------------------------------------|-------------------------------|--------------------------------------|----|

| 0* | 0* | 0* | 0* | HOP CLK<br>PHASE MOD<br>ENABLE<br>(HPME) | EXT<br>MUX<br>ENABLE<br>(EME) | EXT PHASE<br>MOD<br>ENABLE<br>(EPME) | 0* |

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA

E-mail: vlsi-products@qualcomm.com Telephone: {619} 658-5005, Fax: {619} 658-1556

11

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

**■** 9003336 0000889 677 **■**

should be set to logic "0." The remaining bits of the SMC register are the Hop Clock Phase Modulation Enable (HPME), External Multiplexer Enable (EME), and the External Phase Modulation Enable (EPME). Each of these bits is described below.

### Hop Clock Phase Modulation Enable (HPME)

The HPME bit is used when operating in the Internal Phase Modulation mode. When the HPME bit is set to logic "1," the phase increment value stored in PIRB is added to the phase accumulator once each time the HOP CLK signal is asserted. If the Phase Modulation Add Enable (PMAE) bit is set to logic "0", all 32 bits of PIRB are used for the one time. However, if the PMAE bit is set to "1," the 8 MSB of PIRB are added to the 8 MSB of PIRA to form the 8 MSB to be accumulated with the 24 LSB of PIRA.

When the HPME bit is set to a logic "1", the HOP CLK signal is internally extended to two SYS CLK cycles. The two SYS CLK cycles make it possible for the phase accumulator to add the contents from PIRB once, and then switch the process immediately back to PIRA. To disable the Internal Phase Modulation mode, as is the case when you want to reconfigure operation to the basic oscillator mode for example, the HPME bit is reset to "0". The HOP CLK is required to initiate this change and during the HPME's transition from "1" to "0", the HOP CLK is no longer internally extended to two SYS CLK cycles and therefore the accumulation process will still accumulate the contents from PIRB. In order to switch the accumulation process back to PIRA, re-load PIRA with the intended frequency value, then assert another HOP CLK (asserting a successive HOP CLK without re-loading PIRA will not switch the accumulation process

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA from PIRB to PIRA). If desired, the contents of PIRB can be loaded with the same contents intended for PIRA concurrently with the HPME bit being disabled to "0". If this is done, then when the HPME transitions, the output will look as though only PIRA is being accumulated, although the user will want to make sure to re-load PIRA with the desired value and assert another HOP CLK so the accumulation process ends up on PIRA.

### External Multiplexer Enable (EME)

The EME bit enables the External Multiplex Control. When this bit is set to logic "1," the EXT MUX signal determines whether the value stored in PIRA or PIRB will be used for the phase accumulation process. The selection on the EXT MUX signal is synchronously activated on the rising edge of the MUX CLK signal when the EME is set to logic "1." If the EME bit is set to logic "0," then the External Multiplex Control is disabled and the signal on EXT MUX is ignored. In this case, the contents of PIRA will be used for the accumulation process.

### External Phase Modulation Enable (EPME)

The EPME enables the external phase modulation function. When this bit is set to "1," the PM EXT BITS are read and the corresponding phase offset is latched into the Q2334 each time the PM CLK is asserted. If external phase modulation is not used, set the EPME bit to "0" (see the External Phase Modulation section on page 22).

### Asynchronous Mode Control (AMC) Register

The Asynchronous mode Control (AMC) register of each DDS function includes control bits which should only be configured during initialization of the Q2334 device. The AMC commands

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

**- 9003336 0000890 399**

should be activated before any other commands are asserted to the DDS in order for all commands to be received and processed properly. These control bits, as shown in figure 6, include the DAC Strobe or DAC Strobe Invert (DACSTB,

DACSTB/), Phase Modulation Add Enable (PMAE), Output Format, and NRC Enable. Each of these is described below. Bits 4 and 6 of the AMC register are reserved and should be set to "0".

Figure 6. Asynchronous Mode Control (AMC) Register

| D7      | D6 | D5                                   | D4 | D3                 | D2 | D1            | D0 |

|---------|----|--------------------------------------|----|--------------------|----|---------------|----|

| DAC STB | 0* | PHASE MOD<br>ADD<br>ENABLE<br>(PMAE) | 0* | OUTPUT<br>FORMAT** | NR | C ENABLE BITS |    |

ADDRESS ×A Thex 1

<sup>\*</sup> These bits must be set to 0.

| **Output Format  | D3 |

|------------------|----|

| Two's Complement | 0  |

| Offset Binary    | 1  |

| ***DAC SIZE<br>(# OF BITS) | D2 | D1  | DO |

|----------------------------|----|-----|----|

| 6                          | 0  | 0   | 0  |

| 7                          | 0  | 0   | 1  |

| 8                          | 0  | 1   | 0  |

| 9                          | 0  | ] ] | 1  |

| 10                         | 1  | 0   | 0  |

| 11                         | 1  | 0   | 1  |

| 12                         | 1  | 1   | 0  |

| DISABLE NRC                | 1  | 1   | 1  |

### DAC Strobe, DAC Strobe Invert (DACSTB, DACSTB/)

The DAC Strobe is a delayed version of the system clock which is provided along with the DAC BIT outputs in order to facilitate strobing this digitized sine value into a sample-and-hold DAC or other register. A non-inverted or inverted DAC Strobe is provided so that DAC devices with different triggering requirements can be easily accommodated. The DAC Output Timing specifications must be synchronized with respect to the falling edge of SYS CLK and are therefore only guaranteed in relation to the falling edge

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA of SYS CLK. Trying to use the DACSTB timing associated with the rising edge of SYS CLK could potentially violate DAC setup time and result in strobing erroneous DAC BIT data.

When the AMC's D7 register is set to a "0", the DAC Strobe is non-inverted in relation to the system clock. This allows the falling edge of DACSTB to be used in compliance with SYS CLK. When the D7 register is set to a "1", the sense of the DAC Strobe is inverted in relation to the system clock. This allows the rising edge of DACSTB to be used in compliance with SYS CLK.

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

13

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

**-** 9003336 0000891 225 **-**

### Phase Modulation Add Enable (PMAE)

The PMAE bit is not used unless the HPME bit is set to "1." The PMAE bit controls the way in which the value stored in PIRB is used for the one-time accumulation by the phase accumulator. When the PMAE bit is set to logic "1" and PIRB is active for accumulation, the 8 MSB of PIRB are added to the 8 MSB of PIRA to form the 8 MSB to be accumulated. The 24 LSB of PIRA are used as the 24 LSB of the phase accumulator input value. This technique is useful for systems utilizing the Internal Phase Modulation mode of operation. By storing the synthesizer frequency in the PIRA and modifying only the most significant byte of the PIRB, a 256-state phase modulator is implemented. This feature saves computation time in the processor controlling the DDS operation when a phase modulation system with 256-state (i.e.,  $360^{\circ}/256 = 1.41$  degrees) phase resolution is adequate. Using only the 8 MSB of PIRB to control the phase

modulation allows the user to establish a byte-wide Direct Memory Access (DMA) control from the processor to the DDS function phase modulation register (i.e., PIRB), thus simplifying the processor overhead required to control the DDS function in rapidly switching phase modulation systems. When the PMAE bit is set to logic "0," all 32-bits of PIRB will be accumulated in the phase accumulator when PIRB is active allowing a phase resolution of 360°/2<sup>32</sup>, i.e, 84 nanodegrees.

### **Output Format**

The Output Format bit determines the binary coding of the DAC output bits of each DDS function. When this bit is set to logic "1," the DAC output is encoded in offset binary format. When this bit is set to logic "0," the DAC output bits are encoded in two's complement format. Table 2 shows the effect of the setting of the Output Format bit.

| Table 2. DAC Output Format |

|----------------------------|

|----------------------------|

| VALUE            | OUTPUT FORMAT = 1<br>(OFFSET BINARY) | OUTPUT FORMAT = 0<br>(TWO's COMPLEMENT) |  |  |

|------------------|--------------------------------------|-----------------------------------------|--|--|

|                  | MSB LSB                              | MSB LSB                                 |  |  |

| Maximum Value    | 111111111111                         | 01111111111                             |  |  |

| •••              | 111111111110                         | 011111111110                            |  |  |

| •••              | •••                                  | •••                                     |  |  |

| •••              | •••                                  | •••                                     |  |  |

| Half Maximum + 1 | 10000000000                          | 00000000000                             |  |  |

| Half Maximum — 1 | 01111111111                          | 111111111111                            |  |  |

| ***              | •••                                  | •••                                     |  |  |

|                  | •••                                  | •••                                     |  |  |

| •••              | 00000000001                          | 100000000001                            |  |  |

| Minimum Value    | 00000000000                          | 100000000000                            |  |  |

### **NRC** Enable

When using the on-chip Noise Reduction Circuit (NRC) function, the number of significant bits to be used from the DAC Outputs must be programmed into NRC Enable bits. The DAC bit-width is encoded in three bits as shown in figure 6. When using a DAC with fewer than 12-bits resolution, the most significant DAC output bits are valid. The NRC function is disabled when the NRC Enable bits are set to 111 (binary).

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

14 QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

**■ 400333**P 0000**9**45 **1**P**1 ■**

The function of the NRC circuit is described in the Noise Reduction Circuit section on page 16.

### **Accumulator Reset Register (ARR)**

Each DDS function on the Q2334 device includes an Accumulator Reset Register (ARR). By writing any value to the ARR, the accumulator reset function is armed. The next time the HOP CLK is asserted the phase accumulator is reset to zero.

### Asynchronous Hop Clock (AHC)

Each DDS function includes an Asynchronous Hop Clock (AHC) register. When any value is written to this register, the previously stored values in the double-buffered PIRA, PIRB, and SMC registers are activated. This allows processor control of activation of these settings in an identical fashion as with the assertion of the HOP CLK signal. Note that the HOP CLK signal must be low when the AHC register is accessed in order to activate the new register values. Also note that the timing for the AHC is exactly the same as the HOP CLK signal. Activation of the stored settings occurs within four SYS CLK periods after writing to the AHC register.

### Phase Increment Multiplexer Control

The phase increment multiplexer function selects which PIR (A or B) is used for the accumulation process. This multiplexing function provides a simple Binary Frequency Shift Keying (BFSK) interface to the DDS.

The signal EXT MUX controls the selection of the value stored in either PIRA or PIRB. For EXT MUX = 0, PIRA is selected; for EXT MUX = 1, PIRB is selected. The signal MUX CLK enables the selection made by the EXT MUX signal. The selection made by the EXT

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA MUX signal is activated synchronously once during the low-to-high transition on the MUX CLK signal.

The MUX CLK signal is internally synchronized to the SYS CLK signal of the DDS (reference the Asynchronous Input information contained in figure 14 on page 33). The selection of the EXT MUX control may occur as frequently as once every four periods of SYS CLK (reference the External Control Timing information information contained in figure 13 on page 32).

### Phase Accumulator

Two 32-bit wide phase accumulators are included in the Q2334 device, one for each DDS function. These Accumulators compute and store the sum of the previously computed phase value and the phase increment value from either PIRA or PIRB once during each period of SYS CLK.

### **Phase Modulation Control**

Using the external phase modulation inputs, PM EXT BITO-2, the output of the phase accumulator can be offset by phase increments of 45 degrees (from 0 degrees to 315 degrees) without affecting the operation of the phase accumulator. Table 3 shows the phase offset for the possible settings of the 3-bit external phase modulation inputs. These inputs are latched into the DDS function when the signal PM CLK is asserted. Changes in the external phase modulation are synchronized internally to the DDS function. This provides a simple 8-Phase Shift Keying (8PSK) interface to the DDS.

Reference the Modes of Operation section on page 20 for more detailed information on phase modulation.

### **Sine Lookup Function**

The Q2334 DDS implements a patented

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

Q2334 **DUAL DIRECT** DIGITAL SYNTHESIZER TECHNICAL DATA SHEET DATA SUBJECT TO CHANGE WITHOUT NOTICE technique to generate a sine wave lookup (see Patent Reference 1). This algorithm takes the 16 MSB from the phase accumulator to generate a 12-bit sine wave value. Using this high precision lookup function the phase truncation noise of the sine wave output is kept

below 76 dB. This technique differs considerably from the traditional method of using a ROM lookup function. This advanced look-up technique provides highly accurate and precise sine wave generation.

**Table 3. External Phase Modulation Offset Settings**

| PM EXT<br>BIT 2 | PM EXT<br>BIT 1 | PM EXT<br>BIT 0 | ABSOLUTE PHASE OFFSET (degrees) |

|-----------------|-----------------|-----------------|---------------------------------|

| 0               | 0               | 0               | 0                               |

| 0               | 0               | ]               | 45                              |

| 0               | 1               | 0               | 90                              |

| 0               | 1               | 1               | 135                             |

| 1               | 0               | 0               | 180                             |

| 1               | 0               | 1               | 225                             |

| 1               | 1               | 0               | 270                             |

| 1               | 1               | 1               | 315                             |

### **Noise Reduction Circuit (NRC)**

Noise due to amplitude quantization is often assumed to be random and uniformly distributed. However, because a sine wave function is periodic, this is not always the case. At certain output frequencies, amplitude quantization errors become highly correlated, thereby causing spurs.

Spurs associated with round-off errors of the quantized sine wave outputs can be significantly reduced by enabling the onchip Noise Reduction Circuit (NRC). This patented circuit distributes the noise energy evenly across the frequency band, thus reducing the amplitudes of peak spurious components (see Patent Reference 2).

It is important to properly set the NRC Enable bits, because the operation of the NRC is scaled to the LSB. If an incorrectly sized DAC is specified, performance will be reduced.

If the Q2334 is used to generate narrowband outputs and a low noise floor is required, the signal should be bandpass

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA filtered and the NRC disabled. As stated above, when the NRC is enabled it distributes the noise evenly across the frequency band and raises the noise floor. When the NRC is disabled, the noise floor is slightly lower and the quantization errors show up as discrete spurious. However, since the signal is bandpass filtered, the broadband spurious will be negligible.

The output of the NRC (a 12-bit wide digitized sine wave) is normally connected to an external DAC function. This output value can be encoded in offset binary or two's complement format (see figure 6).

Figures 7 and 8 show typical spectra of the analog converted outputs from the Q2334 device with the NRC enabled and disabled. These spectra were measured with the DDS operating with a 10-bit DAC. The synthesized frequency in each of these figures is 10.8 MHz from a 30 MHz system clock frequency. The measurement frequency spans from 0 to 15 MHz, the resolution bandwidth is

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

■ 9003336 0000894 T34 **■**

17

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

9003336 0000895 970 🖿

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

30 kHz, the video bandwidth is 3 kHz, and the scale is 10 dB per vertical division.

Figure 9 shows the typical performance of the Q2334 DDS when operating with a 10-bit DAC with NRC disabled and no LPF. This figure shows a

5 MHz output generated from a 20 MHz system clock frequency and the image at 15 MHz. This 15 MHz spur results from the negative image folded around the 30 MHz clock frequency. This image would normally be filtered by a LPF at the output of the DAC.

### INPUT/OUTPUT SIGNALS

Figure 10 provides the pin configuration of the Q2334 DDS package and Table 4 provides a summary of the input/output signal pin assignments.

### Signals Common for Both DDSs

The following signals are used in common for both DDS functions on the Q2334 device.

### DATAO...DATA7

Inputs (6, 7, 8, 9, 43, 42, 41, 40)

8-bit data bus for writing values to the on-chip processor interface registers.

This bus is used for write operations

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA only. DATA0 is the LSB.

### ADDRESSO...ADDRESS4

Inputs (3, 39, 5, 4, 38)

5-bit address bus to select the internal processor interface registers. Addresses must be held fixed during the active period of the WR/ signal. ADDRESSO is the LSB.

### CS/

input (36)

Chip Select. Must be held low during processor write accesses to the Q2334 device. Can be held low all the time.

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

**■** 9003336 0000896 807 **■**

Table 4. Q2334 Input/Output Signals

| P              | IN# | NAME            | I/O TYPE | DESCRIPTION                                     | PIN# | NAME            | I/O TYPE | DESCRIPTION                                             |

|----------------|-----|-----------------|----------|-------------------------------------------------|------|-----------------|----------|---------------------------------------------------------|

|                | 1   | SYS CLK2        | INPUT    | System clock to DDS #2                          | 35   | SYS CLK1        | INPUT    | System Clock to DDS#1                                   |

|                | 2   | GND             | INPUT    | Ground Connection                               | 36   | CS/             | INPUT    | Chip Select - Low during processor writes               |

|                | 3   | ADDRESSO        | INPUT    | Processor Interface address bus-bit O (LSB)     |      | WR/             | INPUT    | Writes the value of data bus into register - Active Low |

|                | 4   | ADDRESS3        | INPUT    | Processor Interface address bus-bit 3           | 38   | ADDRESS4        | INPUT    | Processor interface address bus-bit 4 (MSB)             |

|                | 5   | ADDRESS2        | INPUT    | Processor Interface address bus-bit 2           | 39   | ADDRESS1        | INPUT    | Processor interface address bus-bit 1                   |

| $\Gamma$       | 6   | DATAO           | INPUT    | Processor Interface data bus-bit 0 (LSB)        | 40   | DATA7           | INPUT    | Processor interface data bus-bit 7 (MSB)                |

|                | 7   | DATA1           | INPUT    | Processor Interface data bus-bit 1              | 41   | DATA6           | INPUT    | Processor interface data bus-bit 6                      |

|                | 8   | DATA2           | INPUT    | Processor Interface data bus-bit 2              | 42   | DATA5           | INPUT    | Processor interface data bus-bit 5                      |

| $\  \Gamma \ $ | 9   | DATA3           | INPUT    | Processor Interface data bus-bit 3              | 43   | DATA4           | INPUT    | Processor interface data bus-bit 4                      |

| Г              | 10  | GND             | INPUT    | Ground Connection                               | 44   | GND             | INPUT    | Ground Connection                                       |

|                | 11  | DAC1 BIT11      | OUTPUT   | DDS#1 Digitized sine wave output-bit 11 (MSB)   | 45   | DAC2 BIT11      | OUTPUT   | DDS#2 Digitized sine wave output-bit 11 (MSB)           |

|                | 12  | DAC1 BIT10      | OUTPUT   | DDS#1 Digitized sine wave output-bit 10         | 46   | DAC2 BIT10      | OUTPUT   | DDS#2 Digitized sine wave output-bit 10                 |

|                | 13  | DAC1 BIT9       | OUTPUT   | DDS#1 Digitized sine wave output-bit 9          | 47   | DAC2 BIT9       | OUTPUT   | DDS#2 Digitized sine wave output-bit 9                  |

| Г              | 14  | DAC1 BIT8       | OUTPUT   | DDS#1 Digitized sine wave output-bit 8          | 48   | DAC2 BIT8       | OUTPUT   | DDS#2 Digitized sine wave output-bit 8                  |

|                | 15  | DAC1 BIT7       | OUTPUT   | DDS#1 Digitized sine wave output-bit 7          | 49   | DAC2 BIT7       | OUTPUT   | DDS#2 Digitized sine wave output-bit 7                  |

|                | 16  | DACI BIT6       | OUTPUT   | DDS#1 Digitized sine wave output-bit 6          | 50   | DAC2 BIT6       | OUTPUT   | DDS#2 Digitized sine wave output-bit 6                  |

|                | 17  | GND             | INPUT    | Ground Connection                               | 51   | GND             | INPUT    | Ground Connection                                       |

|                | 18  | V <sub>oo</sub> | INPUT    | +5V power supply connection                     | 52   | V <sub>ob</sub> | INPUT    | +5V power supply connection                             |

|                | 19  | DAC1 BIT5       | OUTPUT   | DDS#1 Digitized sine wave output-bit 5          | 53   | DAC2 BIT5       | OUTPUT   | DDS#2 Digitized sine wave output-bit 5                  |

| Г              | 20  | DAC1 BIT4       | OUTPUT   | DDS#1 Digitized sine wave output-bit 4          | 54   | DAC2 BIT4       | OUTPUT   | DDS#2 Digitized sine wave output-bit 4                  |

| $\  \Gamma \ $ | 21  | DAC1 BIT3       | OUTPUT   | DDS#1 Digitized sine wave output-bit 3          | 55   | DAC2 BIT3       | OUTPUT   | DDS#2 Digitized sine wave output-bit 3                  |

|                | 22  | DAC1 BIT2       | OUTPUT   | DDS#1 Digitized sine wave output-bit 2          | 56   | DAC2 BIT2       | OUTPUT   | DDS#2 Digitized sine wave output-bit 2                  |

|                | 23  | DAC1 BIT1       | OUTPUT   | DDS#1 Digitized sine wave output-bit 1          | 57   | DAC2 BIT1       | OUTPUT   | DDS#2 Digitized sine wave output-bit 1                  |

|                | 24  | DAC1 BITO       | OUTPUT   | DDS#1 Digitized sine wave output-bit ( (LSB)    | 58   | DAC2 BITO       | OUTPUT   | DDS#2 Digitized sine wave output-bit 0 (LSB)            |

|                | 25  | GND             | INPUT    | Ground connection                               | 59   | GND             | INPUT    | Ground connection                                       |

| Г              | 26  | DAC1 STB        | OUTPUT   | DDS#1 Synchronous strobe to facilitate clocking | 60   | DAC2 STB        | OUTPUT   | DDS#2 Synchronous strobe to facilitate clocking         |

|                |     |                 |          | the DAC BITs into a DAC                         |      |                 |          | the DAC BITs into a DAC                                 |

| ľ              | 27  | PM1 EXT BIT2    | INPUT    | DDS#1 Controls the external PM value-bit 2      | 61   | PM2 EXT BIT2    | INPUT    | DDS#2 Controls the external PM value-bit 2              |

|                | 28  | PM1 EXT BIT1    | INPUT    | DDS#1 Controls the external PM value-bit 1      | 62   | PM2 EXT BIT1    | INPUT    | DDS#2 Controls the external PM value-bit 1              |

|                | 29  | PM1 EXT BITO    | INPUT    | DDS#1 Controls the external PM value-bit 0      | 63   | PM2 EXT BITO    | INPUT    | DDS#2 Controls the external PM value-bit 0              |

|                | 30  | PM1 CLK         | INPUT    | DDS#1 Enables the values in PM EXT BITs         | 64   | PM2 CLK         | INPUT    | DDS#2 Enables the values in PM EXT BITs                 |

|                | 31  | EXT MUX1        | INPUT    | DDS#1 Controls which PIR is being accumulated   | 65   | EXT MUX2        | INPUT    | DDS#2 Controls which PIR is being accumulated           |

|                | 32  | MUX1 CLK        | INPUT    | DDS#1 Enables the value on EXT MUX1             | 66   | MUX2 CLK        | INPUT    | DDS#2 Enables the value on EXT MUX2                     |

|                | 33  | V <sub>DD</sub> | INPUT    | +5V power supply connection                     | 67   | <b>V</b> DD     | INPUT    | +5V power supply connection                             |

|                | 34  | HOP CLK1        | INPUT    | Hop Clock to DDS#1                              | 68   | HOP CLK2        | INPUT    | Hop Clock to DDS#2                                      |

### WR/

Input

(37)

When low while CS/ is low, writes the value of the Data Bus to the register determined by the Address Bus.

### $\mathbf{V}_{\mathrm{DD}}$

Input

(18, 33, 52, 67)

Provides power to all Q2334 circuitry.

### GND

Input

(2,10,17, 25, 44, 51, 59)

Provides electrical ground reference for

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA signal and power inputs.

### Signals Independent for each DDS

The following signals pertain to a specific DDS function (1 or 2) on the Q2334 device.

### SYS CLK1, SYS CLK2

Input

(35, 1)

Provides the fundamental clock frequency of the synthesized sine waveform. Internal operations of the phase accumulator, external phase

19

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556 Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

**■** 9003336 0000897 743 **■**

modulation, and phase increment registers are synchronized to this clock signal.

### HOP CLK1, HOP CLK2

Input (34, 68)

The HOP CLK signal controls the activation of the selection of the double buffered registers. HOP CLK must be active (high) for at least one SYS CLK period and can be asserted once every ten SYS CLK periods.

### **EXT MUX1, EXT MUX2**

Input

(31, 65)

When latched into the DDS with the signal MUX1 CLK (or MUX2 CLK) this signal determines which PIR (A or B) will be used for the incremental phase accumulator input value. When the EXT MUX signal is set to "1," the value stored in PIRB will be used by the phase accumulator. When the EXT MUX signal is set to "0," the value stored in PIRA will be used.

### MUX1 CLK, MUX2 CLK

Input

(32, 66)

The rising edge of this signal latches and enables the value on the EXT MUX inputs. This signal must be held high for a minimum of three SYS CLK periods. Activation of the EXT MUX inputs is synchronized internally to SYS CLK.

### PM1 EXT BITO...PM1 EXT BIT2, PM2 EXT BIT0...PM2 EXT BIT2

Inputs

(29, 28, 27, 63, 62, 61)

External phase modulation inputs which control 45 degree phase offsets in the phase accumulated values in accordance with the settings provided in Table 3. PM EXT BITs are active when the signal PM CLK is asserted and are synchronized internally to the DDS function to SYS CLK.

20

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA

### PM1 CLK, PM2 CLK

Input

The rising edge of this signal latches and enables the value on the PM EXT BIT inputs. This signal must be held high for a minimum of three SYS CLK periods. The PM EXT BIT inputs are synchronized internally to SYS CLK.

(30, 64)

DAC1 BIT0...DAC1 BIT11, DAC2 BIT0...DAC2 BIT11

Outputs (24, 23, 22, 21, 20, 19, 16, 15, 14, 13,

12, 11, 58, 57, 56, 55, 54, 53, 50, 49, 48, 47, 46, 45)

Digitized sine wave outputs encoded in offset binary or two's complement format, depending on settings in the AMC Registers. One sample is generated during each period of SYS CLK. DAC BIT 0 is the LSB.

### DAC1 STB, DAC2 STB

Output (26, 60)

Provides a synchronous strobe to facilitate clocking of the DAC BIT outputs into an external register or sampled DAC. One DAC STB is generated during each period of SYS CLK. Essentially, the DAC STB (or DAC STB/) is a delayed version of SYS CLK.

### MODES OF OPERATION

Each DDS can be independently set to perform a wide range of expanded functions of the basic operation, as described in the following paragraphs.

### **Basic Synthesizer Mode**

In its most basic operational mode each DDS on the Q2334 device can provide a fixed frequency digitized sine wave output. The frequency of this sine output is determined by the frequency of the clock input and the value stored in the PIRs (see formula (1) in the Phase Increment Value section on page 7).

To set the Q2334 up in a single frequency output mode, the SMC should

E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

San Diego, CA 92121-2779, USA

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

02334

**DUAL DIRECT**

■ 9003336 0000898 68T **■**

be set to "00" (hex). The AMC should be set according to the size of the DAC selected and the desired output format. The PMAE bit should also be set to "0" (reference the Simple Oscillator Mode example section on page 24).

### **Phase Modulation Mode**

The Q2334 provides two means to implement phase modulation of a basic frequency output, referred to as Internal Phase Modulation and External Phase Modulation.

Internal Phase Modulation provides extremely fine resolution up to  $0.00000008^{\circ}$  of the phase adjustment  $(2^{32}$  - state phase resolution), while External Phase Modulation is designed for  $45^{\circ}$  increment phase shifts.

### Internal Phase Modulation

Internal Phase Modulation operates as a differential phase adjustment technique and requires use of the processor interface. The Internal Phase Modulation mode is activated by loading PIRA with the correct phase increment for the basic frequency without phase modulation. PIRB is then loaded with the phase increment value equal to the phase increment value stored in PIRA plus the value of the desired phase offset. The phase accumulator uses PIRA for most phase accumulations.

Setting the HPME bit in the SMC register to logic "1" arms the DDS to use the 32-bit value in PIRB for one phase accumulation cycle when the signal HOP CLK is asserted. Since the phase increment value in PIRB is only used once for each HOP CLK assertion, the net effect is to cause a phase change to the generated sine wave.

When the PMAE bit is set to logic "1," the 8 MSB of PIRB are added to the 8 MSB

of PIRA to form the 8 MSB to be accumulated with the 24 LSB of PIRA. This 32-bit value is used for one-time accumulation. If PMAE is "0," all 32 units of PIRB will be used for the accumulation.

The one-time phase shift occurs every time the HOP CLK signal is asserted. The phase shift can occur as often as the HOP CLK signal can be asserted (see Processor Interface Timing shown in figure 11 on page 30).

If it is desired to change the phase offset value, PIRB must be reloaded before the HOP CLK cycle with the new phase offset for the next HOP CLK period. The HPME bit will remain set to "1" until reset by the processor (reference the Hop Clock Phase Modulation Enable section on page 12).

### **External Phase Modulation**

External Phase Modulation operates as an absolute phase adjustment technique and utilizes special synchronous inputs separate from the processor interface. When using the External Phase Modulation mode, the phase increment value for the unmodulated input is written into PIRA. PIRB is not used in the External Phase Modulation mode.

The External Phase Modulation Enable (EPME) bit in the SMC register is set to logic "1" to enable the External Phase Modulation mode. When the EPME bit is set to "1," the phase offset determined by the PM EXT BITs are latched into the DDS function each time the signal PM CLK is asserted. This PM EXT BIT setting causes a phase offset in 45° increments as indicated in table 3. This mode of operation allows very simple control of the DDS as a binary, quartenary, or 8-ary phase shift keyed (8PSK) modulator.

21

QUALCOMM Incorporated, VLSI Products 6455 Lusk Boulevard, San Diego, CA 92121-2779, USA E-mail: vlsi-products@qualcomm.com Telephone: (619) 658-5005, Fax: (619) 658-1556

9003336 0000899 516 🖿

Q2334

DUAL DIRECT

DIGITAL SYNTHESIZER

TECHNICAL DATA SHEET

DATA SUBJECT TO CHANGE WITHOUT NOTICE

# Binary Frequency Shift Keying (BFSK) Modulation Mode

Two PIRs are provided for each DDS function allowing for Binary Frequency Shift Keyed (BFSK) modulation without any additional hardware. The Q2334 provides signals allowing this switch to occur synchronously.

BFSK Modulation is achieved by setting the phase increment value in PIRA to generate the first frequency and the value in the PIRB to generate the second frequency. The EME bit is then set to logic "1" to enable the external multiplexer controls.

If the EXT MUX signal is set to logic "1," when the MUX CLK signal is asserted the phase accumulator will choose the phase increment value from PIRB. If the EXT MUX signal is set to logic "0," when the MUX CLK is asserted the phase accumulator will choose the phase increment value from PIRA. Changing the value of the EXT MUX input causes the alternation between the frequency controlled by PIRA and the frequency controlled by PIRB.

After the BFSK mode is set up and the PIRA and PIRB contents are active, the EXT MUX signal can be changed as fast as the MUX CLK can be asserted (see External Control Timing shown in figure 13 on page 32). The MUX CLK timing is the only restriction on how fast the accumulation can be switched from PIRA to PIRB.