## MC68230

## Technical Summary

## Parallel Interface/Timer

The MC68230 parallel interface/timer (PI/T) provides versatile double-buffered parallel interfaces and a system-oriented timer for MC68000 systems. The parallel interfaces operate in unidirectional or bidirectional modes, either 8 or 16 bits wide. In the unidirectional modes, an associated data direction register determines whether each port pin is an input or output. In the bidirectional modes, the data direction registers are ignored, and the direction is determined dynamically by the state of four handshake pins. These programmable handshake pins provide an interface flexible enough for connection to a wide variety of low-, medium-, or high-speed peripherals or other computer systems. The PI/T ports allow use of vectored or autovectored interrupts, and also provide a direct memory access (DMA) request pin for connection to the MC68450 direct memory access controller (DMAC) or a similar circuit. The PI/T timer contains a 24-bit-wide counter and a 5-bit prescaler. The timer may be clocked by the system clock (PI/T CLK pin) or by an external clock (TIN pin), and a 5-bit prescaler can be used. The PI/T can generate periodic interrupts, a square wave, or a single interrupt after a programmed time period; it can also be used for elapsed time measurement or as a device watchdog.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

- M68000 Bus Compatible

- Port Modes Include:

Bit I/O

8- and 16-Bit Unidirectional

8- and 16-Bit Bidirectional

- Programmable Handshaking Options

- 24-Bit Programmable Timer Modes

- Five Separate Interrupt Vectors, Four of which May Be Dedicated to External Interrupt Service Requests

- Separate Port and Timer Interrupt Service Requests

- Registers Are Read/Write and Directly Addressable

- Registers Are Addressed for Move Peripheral (MOVEP) and DMAC Compatibility

#### INTRODUCTION

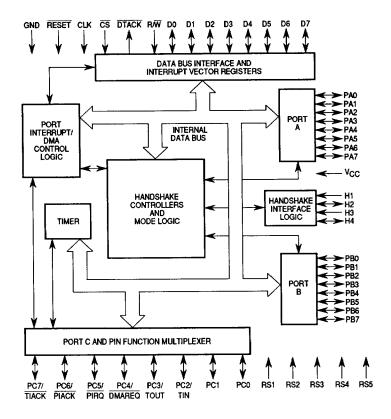

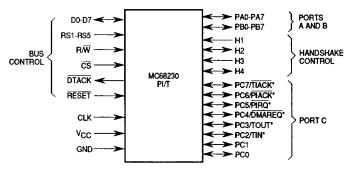

The PI/T consists of two logically independent sections: the ports and the timer. The port section consists of port A (PA0-PA7), port B (PB0-PB7), four handshake pins (H1, H2, H3, and H4), two general input/output (I/O) pins, and six dual-function pins. The dual-function pins can individually operate as a third port (port C) or as an alternate function related to port A, port B, or the timer. The four programmable handshake pins, depending on the mode, can control data transfer to and from the ports, can be used as general-purpose I/O pins, or can be used as interrupt-generating edge-sensitive inputs with corresponding interrupt vector numbers (see Figure 1).

9

Figure 1. Block Diagram

The timer consists of a 24-bit counter, optionally clocked by a 5-bit prescaler. Three pins provide complete timer I/O: PC2/TIN, PC3/TOUT, and PC7/TIACK. Only the ones needed for the given configuration perform the timer function, while the others remain port C I/O.

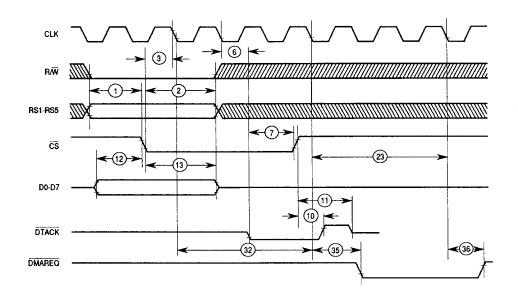

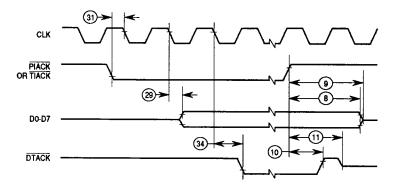

The system bus interface provides for asynchronous transfer of data from the PI/T to a bus master over the data bus (D0–D7). Data transfer acknowledge (DTACK), register selects (RS1–RS5), timer interrupt acknowledge (TIACK), read/write (R/W), chip select (CS), or port interrupt acknowledge (PIACK) control data transfers between the PI/T and an M68000 processor.

#### PORT MODE DESCRIPTION

The primary focus of most applications will be on port A, port B, the handshake pins, the port interrupt pins, and the DMA request pin. They are controlled in the following way: the port general-control register contains a 2-bit field that specifies one of four operation modes. These modes govern the overall operation of the ports and determine their interrelationships. Some modes require additional information from each port's control register to further define its operation. Each port control register contains a 2-bit submode field that serves this purpose. Each port mode/submode combination specifies a set of programmable characteristics that fully define the behavior of that port and two of the handshake pins. This structure is summarized in Table 1 and Figure 2.

9-4

M68000 FAMILY REFERENCE MANUAL

Port A

Submode 00 — Pin-Definable Double-Buffered Input or Single-Buffered Output

H1 — Latches input data

H2 — Status/interrupt generating input, general-purpose output, or operation with H1 in the interlocked or pulsed handshake protocols

Submode 01 — Pin-Definable Double-Buffered Output or Nonlatched Input

H1 — Indicates data received by peripheral

H2 — Status/interrupt generating input, general-purpose output, or operation with H1 in the interlocked or pulsed handshake protocols

Submode 1X — Pin-Definable Single-Buffered Output or Nonlatched Input

H1 — Status/interrupt generating input

H2 — Status/interrupt generating input or general-purpose output

Port B

H3/H4 — Identical to port A submodes, H1 and H2

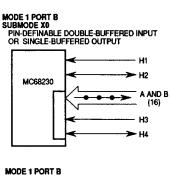

#### Mode 1 (Unidirectional 16-Bit Mode)

Port A — Most Significant Data Byte or Nonlatched Input or Single-Buffered Output

Submode XX — (Not Used)

H1 — Status/interrupt generating input

H2 — Status/interrupt generating input or general-purpose output

Port B - Least Significant Data Byte

Submode X0 — Pin-Definable Double-Buffered Input or Single-Buffered Output

H3 — Latches input data

H4 — Status/interrupt generating input, general-purpose output, or operation with H3 in the interlocked or pulsed handshake protocols

Submode X1 — Pin-Definable Double-Buffered Output or Nonlatched Input

H3 — Indicates data received by peripheral

H4 — Status/interrupt generating input, general-purpose output, or operation with H3 in the interlocked or pulsed handshake protocols

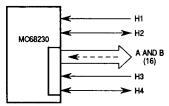

#### Mode 2 (Bidirectional 8-Bit Mode)

Port A - Bit I/O

Submode XX — (Not Used)

Port B — Double-Buffered Bidirectional Data

Submode XX — (Not Used)

H1 — Indicates output data received by the peripheral and controls output drivers

H2 — Operating with H1 in the interlocked or pulsed output handshake protocols

H3 — Latches input data

H4 — Operation with H3 in the interlocked or pulsed input protocols

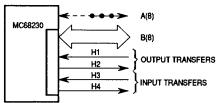

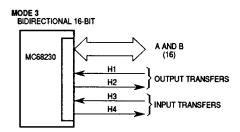

#### Mode 3 (Bidirectional 16-Bit Mode)

Port A — Double-Buffered Bidirectional Data (Most Significant Data Byte)

Submode XX — (Not Used)

Port B — Double-Buffered Bidirectional Data (Least Significant Data Byte)

Submode XX — (Not Used)

H1 — Indicates output data received by peripheral and controls output drivers

H2 — Operation with H1 in the interlocked or pulsed output handshake protocols

H3 — Latches input data

H4 — Operation with H3 in the interlocked or pulsed input handshake protocols

a

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

LEGEND:

MODE 1 PORT B SUBMODE X0 PIN-DEFINABLE DOUBLE-BUFFERED OUTPUT OR NONLATCHED INPUT

MODE 2

PORT A - BIT I/O

PORT B - DOUBLE-BUFFERED BIDIRECTIONAL

DATA

A/O

Figure 2. Port Mode Layout

9-6

9

**M68000 FAMILY REFERENCE MANUAL**

#### SIGNAL DESCRIPTION

The input and output signals are illustrated functionally in Figure 3 and described in the following paragraphs.

<sup>\*</sup> Individually Programmable Dual-function Pin

Figure 3. Functional Signal Groups

#### **BIDIRECTIONAL DATA BUS (D0-D7)**

The active-high data bus pins, D0-D7, form an 8-bit bidirectional data bus to/from an M68000 bus master.

#### **REGISTER SELECT PINS (RS1-RS5)**

The register select pins, RS1–RS5, are active-high high-impedance inputs that determine which of the 23 internal registers is being selected. They are provided by the M68000 bus master or other bus master.

## READ/WRITE (R/W)

$R/\overline{W}$  is a high-impedance read/write input signal from the M68000 bus master, indicating whether the current bus cycle is a read (high) or write (low) cycle.

9

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

## **CHIP SELECT (CS)**

CS is a high-impedance input that selects the PI/T registers for the current bus cycle. The data strobe (upper or lower) of the bus master, along with the appropriate address bits, must be included in the chip-select equation. A low level corresponds to an asserted chip select.

## DATA TRANSFER ACKNOWLEDGE (DTACK)

DTACK is an active-low output that signals the completion of the bus cycle. During read or interrupt acknowledge cycles, DTACK is asserted after data has been provided on the data bus; during write cycles, it is asserted after data has been accepted on the data bus. DTACK is compatible with the MC68000 and with other M68000 bus mastsers such as the MC68450 DMAC. A pullup resistor is required to maintain DTACK high between bus cycles.

## RESET (RESET)

RESET is a high-impedance input used to initialize all PI/T functions. All control and data direction registers are cleared, and most internal operations are disabled by the assertion of RESET (low).

#### CLOCK (CLK)

The clock pin is a high-impedance TTL-compatible signal with the same specifications as the MC68000. Since the PI/T contains dynamic logic, this clock must not be gated off at any time. It is not necessary that this clock maintain any particular phase relationship with the M68000 system clock. It may be connected to an independent frequency source (faster or slower) as long as all bus specifications are met.

## PORTS A AND B (PA0-PA7 and PB0-PB7)

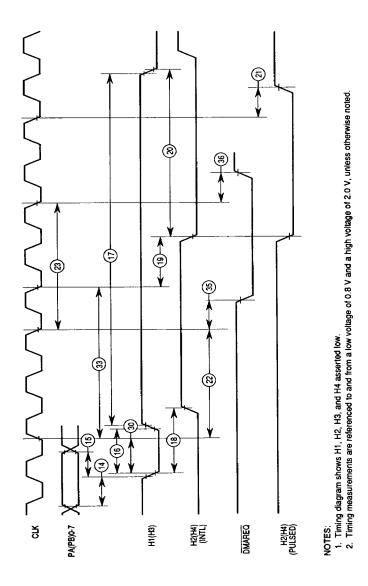

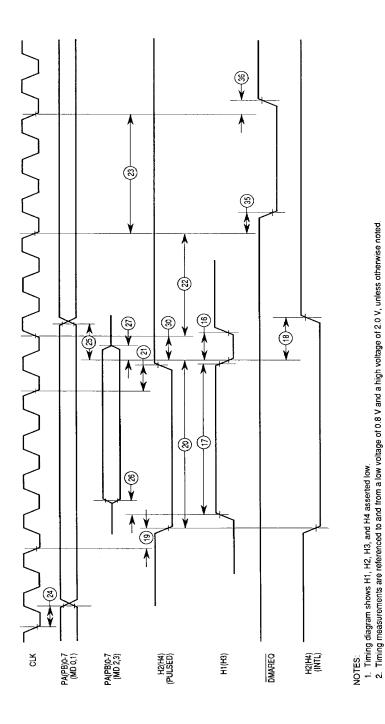

Ports A and B are 8-bit ports that may be concatenated to form a 16-bit port in certain modes. The ports may be controlled in conjunction with the handshake pins, H1–H4. For stabilization during system power-up, ports A and B have internal pullup resistors to  $V_{CC}$ . All port pins are active high.

9

M68000 FAMILY REFERENCE MANUAL

**MOTOROLA**

#### HANDSHAKE PINS (H1-H4)

Handshake pins H1–H4 are multipurpose pins that (depending on the operational mode) may provide an interlocked handshake, a pulsed handshake, interrupt-generating edge-sensitive inputs (independent of data transfers), or simple I/O pins. For stabilization during system power-up, H2 and H4 have internal pullup resistors to VCC. The sense of H1–H4 (active high or low) may be programmed in bits 3-0 of the port general-control register. Independent of the mode, the instantaneous level of the handshake pins can be read from the port status register.

#### PORT C (PC0-PC7/ALTERNATE FUNCTION)

This port can be used as eight general-purpose I/O pins (PC0–PC7) or any combination of six special-function pins and two general-purpose I/O pins (PC0–PC1). Each dual-function pin can be a standard I/O or a special function independent of the other port C pins. When used as a port C pin, these pins are active high. They can be individually programmed as inputs or outputs by the port C data direction register. The dual-function pins are defined in the following paragraphs.

The alternate functions TIN, TOUT, and TIACK are timer I/O pins. TIN may be used as a rising-edge-triggered external clock input or an external run/halt control pin (the timer is in the run state if run/halt is high and in the halt state if run/halt is Iow). TOUT may provide an active-low timer interrupt request output or a general-purpose square-wave output, initially high. TIACK is an active-low high-impedance input used for timer interrupt acknowledge.

The port functions of the PI/T (ports A and B) have an independent pair of active-low interrupt request (PIRQ) and interrupt acknowledge (PIACK) pins.

The direct memory access request (DMAREQ) pin provides an active-low DMAC request pulse for three clock cycles, completely compatible with the MC68450 DMAC. If these pins are used for an alternate function, the corresponding bit in the port C data direction register must be programmed as an input (0).

a

**MOTOROLA**

M68000 FAMILY REFERENCE MANUAL

#### SIGNAL SUMMARY

Table 2 is a summary of all signals discussed in the previous paragraphs.

Table 2. Signal Summary

| Signal Name                      | Input/Output                    | Active State         | Edge/Level Sensitive    | Output States              |  |

|----------------------------------|---------------------------------|----------------------|-------------------------|----------------------------|--|

| CLK                              | Input                           | _                    | Falling and Rising Edge | _                          |  |

| <u>cs</u>                        | Input                           | Low                  | Level                   | -                          |  |

| D0-D7                            | Input/Output                    | High = 1, Low = 0    | Level                   | High, Low, High Impedance  |  |

| DMAREQ                           | Output                          | Low                  | _                       | High, Low                  |  |

| DTACK                            | Output                          | Low                  | _                       | High, Low, High Impedance* |  |

| H1(H3)***                        | Input                           | Low or High          | Asserted Edge           | _                          |  |

| H2(H4)**                         | Input or Output                 | Low or High          | Asserted Edge           | High, Low, High Impedance  |  |

| PA0-PA7**, PB0-PB7**,<br>PC0-PC7 | Input/Output<br>Input or Output | High=1, Low=0        | Level                   | High, Low, High Impedance  |  |

| PIACK                            | Input                           | Low                  | Level                   | _                          |  |

| PIRO                             | Output                          | Low                  |                         | Low, High Impedance*       |  |

| RS1-RS5                          | Input                           | High = 1, Low = 0    | Level                   | _                          |  |

| R/W                              | Input                           | High Read, Low Write | Level                   | _                          |  |

| RESET                            | Input                           | Low                  | Level                   | _                          |  |

| TIACK                            | Input                           | Low                  | Level                   |                            |  |

| TIN (External Clock)             | Input                           |                      | Rising Edge             | _                          |  |

| TIN (Run/Halt)                   | Input                           | High                 | Level                   | _                          |  |

| TOUT (Square Wave)               | Output                          | Low                  |                         | High, Low                  |  |

| TOUT (TIRQ)                      | Output                          | Low                  | _                       | Low, High Impedance*       |  |

<sup>\*</sup>Pullup resistors required.

9

<sup>\*\*</sup>Note these pins have internal pullup resistors.

<sup>\*\*\*</sup>H1 is level sensitive for output buffer control in modes 2 and 3.

## 9

#### **BUS INTERFACE OPERATION**

The PI/T has an asynchronous bus interface, primarily designed for use with an MC68000 microprocessor. With care, however, it can be connected to synchronous buses.

In an asynchronous system, the PI/T clock may operate at a significantly different frequency (higher or lower) than the bus master and other system components if all bus specifications are met. The MC68230 CLK pin has the same specifications as the MC68000 CLK pin and must not be gated off.

The following signals generate normal read and write cycles to the PI/T:  $\overline{CS}$ , R/W, RS1–RS5, DO–D7, and  $\overline{DTACK}$ . To generate interrupt acknowledge cycles, PC6/PIACK or PC7/TIACK is used instead of  $\overline{CS}$ , and RS1–RS5 are ignored. No combination of the following pin functions may be asserted simultaneously:  $\overline{CS}$ , PIACK, or TIACK.

#### **TIMER OPERATION**

The MC68230 timer can provide several facilities needed by MC68000 operating systems. It can generate periodic interrupts, a square wave, or a single interrupt after a programmed time period. Also, it can be used for elapsed-time measurement or as a device watchdog.

The PI/T contains a 24-bit synchronous down-counter that is loaded from three 8-bit counter preload registers. The 24-bit counter may be clocked by the output of a 5-bit (divide-by-32) prescaler or by an external timer input (TIN). If the prescaler is used, it may be clocked by the system clock (CLK) or by the TIN. The counter signals the occurrence of an event primarily through zero detection. (A zero is when the counter of the 24-bit timer is equal to zero). This sets the zero detect status (ZDS) bit in the timer status register. This bit may be checked by the processor or may be used to generate a timer interrupt. The ZDS bit can be reset by writing a one to the timer status register in that bit position, independent of timer operation.

The general operation of the timer is flexible and easily programmable. The timer is fully configured and controlled by programming the 8-bit timer control register. It controls 1) the choice between the port C operation of three timer pins, 2) whether the counter is loaded from the counter preload register or rolls over when zero detect is reached, 3) the clock input, 4) whether the prescaler is used, and 5) whether the timer is enabled.

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

**REGISTER MODEL**

A register model that includes the corresponding register selects is shown in Table 3.

|   |   |                     |    |   |               |             |               | able 3        | . Regi                    | ster M              | odel                     |                           |                                   |                                    |

|---|---|---------------------|----|---|---------------|-------------|---------------|---------------|---------------------------|---------------------|--------------------------|---------------------------|-----------------------------------|------------------------------------|

|   | S | gis<br>elec<br>Bits | ct |   |               |             |               |               |                           |                     |                          |                           | Register<br>Hex<br>Value<br>After | Register                           |

| 5 | 4 | 3                   | 2  | 1 | 7             | 6           | 5             | 4             | 3                         | 2                   | 1                        | 0                         | RESET                             |                                    |

| 0 | 0 | 0                   | 0  | 0 | Port I<br>Con |             | H34<br>Enable | H12<br>Enable | H4<br>Sense               | H3<br>Sense         | H2<br>Sense              | H1<br>Sense               | 00                                | Port General-<br>Control Register  |

| 0 | 0 | 0                   | 0  | 1 | *             | SVC<br>Sel  |               | IP<br>Sel     |                           |                     | ort Interru<br>ority Con |                           | 00                                | Port Service<br>Request Register   |

| 0 | 0 | 0                   | 1  | 0 | Bit<br>7      | Bit<br>6    | Bit<br>5      | Bit<br>4      | Bit<br>3                  | Bit<br>2            | Bit<br>1                 | Bit<br>0                  | 00                                | Port A Data<br>Direction Register  |

| 0 | 0 | 0                   | 1  | 1 | Bit<br>7      | Bit<br>6    | Bit<br>5      | Bit<br>4      | Bit<br>3                  | Bit<br>2            | Bit<br>1                 | Bit<br>0                  | 00                                | Port B Data<br>Direction Register  |

| 0 | 0 | 1                   | 0  | 0 | Bit<br>7      | Bit<br>6    | Bit<br>5      | Bit<br>4      | Bit<br>3                  | Bit<br>2            | Bit<br>1                 | Bit<br>0                  | 00                                | Port C Data<br>Direction Register  |

| 0 | 0 | 1                   | 0  | 1 |               | Inte        | errupt Ve     | ctor Num      | ber                       |                     | *                        | *                         | 0F                                | Port Interrupt<br>Vector Register  |

| 0 | 0 | 1                   | 1  | 0 | Por<br>Subr   |             | ŀ             | H2 Contro     | ı                         | H2<br>Int<br>Enable | H1<br>SVCRQ<br>Enable    | H1<br>Stat<br>Control     | 00                                | Port A Control<br>Register         |

| 0 | 0 | 1                   | 1  | 1 |               | t B<br>node | H4 Control    |               | ı                         | H4<br>Int<br>Enable | H3<br>SVCRQ<br>Enable    | H3<br>Stat<br>Control     | 00                                | Port B Control<br>Register         |

| 0 | 1 | 0                   | 0  | 0 | Bit<br>7      | Bit<br>6    | Bit<br>5      | Bit<br>4      | Bit<br>3                  | Bit<br>2            | Bit<br>1                 | Bit<br>0                  | **                                | Port A Data<br>Register            |

| 0 | 1 | 0                   | 0  | 1 | Bit<br>7      | Bit<br>6    | Bit<br>5      | Bit<br>4      | Bit<br>3                  | Bit<br>2            | Bit<br>1                 | Bit<br>0                  | **                                | Port B Data<br>Register            |

| 0 | 1 | 0                   | 1  | 0 | Bit<br>7      | Bit<br>6    | Bit<br>5      | Bit<br>4      | Bit<br>3                  | Bit<br>2            | Bit<br>1                 | Bit<br>0                  | ***                               | Port A Alternate<br>Register       |

| 0 | 1 | 0                   | 1  | 1 | Bit<br>7      | Bit<br>6    | Bit<br>5      | Bit<br>4      | Bit<br>3                  | Bit<br>2            | Bit<br>1                 | Bit<br>0                  | ***                               | Port B Alternate<br>Register       |

| 0 | 1 | 1                   | 0  | 0 | Bit<br>7      | Bit<br>6    | Bit<br>5      | Bit<br>4      | Bit<br>3                  | Bit<br>2            | Bit<br>1                 | Bit<br>0                  | ****                              | Port C Data<br>Register            |

| 0 | 1 | 1                   | 0  | 1 | H4<br>Level   | H3<br>Level | H2<br>Level   | H1<br>Level   | H4S                       | H3S                 | H2S                      | H1S                       | ****                              | Port Status<br>Register            |

| 0 | 1 | 1                   | 1  | 0 | *             | *           | *             | *             | *                         | *                   | *                        | *                         | 00                                | (Null)                             |

| 0 | 1 | 1                   | 1  | 1 | *             | *           | *             | *             | *                         | *                   | *                        | *                         | 00                                | (Null)                             |

| 1 | 0 | 0                   | 0  | 0 | Т             | OUT/TIAC    |               |               | ock Timer<br>strol Enable |                     | 00                       | Timer Control<br>Register |                                   |                                    |

| 1 | 0 | 0                   | 0  | 1 | Bit<br>7      | Bit<br>6    | Bit<br>5      | Bit<br>4      | Bit<br>3                  | Bit<br>2            | Bit<br>1                 | Bit<br>0                  | 0F                                | Timer Interrupt<br>Vector Register |

| 1 | 0 | 0                   | 1  | 0 | *             | *           | *             | *             | *                         | *                   | *                        | *                         | 00                                | (Null)                             |

M68000 FAMILY REFERENCE MANUAL

**Table 3. Register Model (Continued)**

| 5 | S | gis<br>ele<br>Bits<br>3 | ct | 1 | 7             | 6             | 5             | 4             | 3           | 2           | 1           | 0           | Register<br>Hex<br>Value<br>After<br>RESET | Register                           |

|---|---|-------------------------|----|---|---------------|---------------|---------------|---------------|-------------|-------------|-------------|-------------|--------------------------------------------|------------------------------------|

| 0 | 0 | 0                       | 0  | 0 | Port I<br>Cor | Mode<br>itrol | H34<br>Enable | H12<br>Enable | H4<br>Sense | H3<br>Sense | H2<br>Sense | H1<br>Sense | 00                                         | Port General-<br>Control Register  |

| 1 | 0 | 0                       |    | 1 | Bit<br>23     | Bit<br>22     | Bit<br>21     | Bit<br>20     | Bit<br>19   | Bit<br>18   | Bit<br>17   | Bit<br>16   | **                                         | Counter Preload<br>Register (High) |

| 1 | 0 | 1                       | 0  | 0 | Bit<br>15     | Bit<br>14     | Bit<br>13     | Bit<br>12     | Bit<br>11   | Bit<br>10   | Bit<br>9    | Bit<br>8    | **                                         | Counter Preload<br>Register (Mid)  |

| 1 | 0 | 1                       | 0  | 1 | Bit<br>7      | Bit<br>6      | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2    | Bit<br>1    | Bit<br>0    | **                                         | Counter Preload<br>Register (Low)  |

| 1 | 0 | 1                       | 1  | 0 | *             | *             | *             | *             | *           | *           | *           | *           | 00                                         | (Null)                             |

| 1 | 0 | 1                       | 1  | 1 | Bit<br>23     | Bit<br>22     | Bit<br>21     | Bit<br>20     | Bit<br>19   | Bit<br>18   | Bit<br>17   | Bit<br>16   | **                                         | Count Register<br>(High)           |

| 1 | 1 | 0                       | 0  | 0 | Bit<br>15     | Bit<br>14     | Bit<br>13     | Bit<br>12     | Bit<br>11   | Bit<br>10   | Bit<br>9    | Bit<br>8    | **                                         | Count Register<br>(Mid)            |

| 1 | 1 | 0                       | 0  | 1 | Bit<br>7      | Bit<br>6      | Bit<br>5      | Bit<br>4      | Bit<br>3    | Bit<br>2    | Bit<br>1    | Bit<br>0    | **                                         | Count Register<br>(Low)            |

| 1 | 1 | 0                       | 1  | 0 | *             | *             | *             | *             | *           | *           | *           | ZDS         | 00                                         | Timer Status                       |

| 1 | 1 | 0                       | 1  | 1 | *             | *             | *             | *             | *           | *           | *           | *           | 00                                         | (Null)                             |

| 1 | 1 | 1                       | 0  | 0 | *             | *             | *             | *             | *           | *           | *           | *           | 00                                         | (Null)                             |

| 1 | 1 | 1                       | 0  | 1 | *             | *             | *             | *             | *           | *           | *           | *           | 00                                         | (Null)                             |

| 1 | 1 | 1                       | 1  | 0 | *             | *             | *             | *             | *           | *           | *           | *           | 00                                         | (Null)                             |

| 1 | 1 | 1                       | 1  | 1 | . *           | *             | *             | *             | *           | *           | *           | *           | 00                                         | (Nutl)                             |

<sup>\*</sup>Unused, read as zero

J

<sup>\*\*</sup>Value before RESET

<sup>\*\*\*</sup>Current value on pins

<sup>\*\*\*\*</sup>Undetermined value

## **ELECTRICAL SPECIFICATIONS**

#### **MAXIMUM RATINGS**

| Characteristic              | Symbol           | Value         | Unit |

|-----------------------------|------------------|---------------|------|

| Supply Voltage              | v <sub>cc</sub>  | -0.3 to +7.0  | ٧    |

| Input Voltage               | V <sub>in</sub>  | -0.3 to +7.0  | V    |

| Operating Temperature Range | TA               | 0 to 70       | °C   |

| Storage Temperature         | T <sub>stg</sub> | - 55 to + 150 | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precuations be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or VCC).

#### THERMAL CHARACTERISTICS

| Characteristic                                      | Symbol          | Value<br>(Max) | Symbol | Value<br>(Max) | Rating |

|-----------------------------------------------------|-----------------|----------------|--------|----------------|--------|

| Thermal Resistance<br>Ceramic (L/LC)<br>Plastic (P) | ΑL <sup>θ</sup> | 40<br>40       | θJC    | 15*<br>20*     | °C/W   |

## **DC ELECTRICAL SPECIFICATIONS** ( $V_{CC} = 5.0 \text{ Vdc} \pm 5\%$ ; $T_A = 0 \text{ to } 70^{\circ}\text{C}$ ; unless otherwise noted)

| Characteristic                                                                                                                                             |                                                                                  | Symbol           | Min       | Max             | Unit     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|-----------|-----------------|----------|

| Input High Voltage                                                                                                                                         | All Inputs                                                                       | v <sub>IH</sub>  | GND +2.0  | v <sub>cc</sub> | ٧        |

| Input Low Voltage                                                                                                                                          | All Inputs                                                                       | V <sub>IL</sub>  | GND -0.3  | GND + 0.8       | ٧        |

| Input Leakage Current (V <sub>in</sub> =0 to 5.25 V)                                                                                                       | H1, H3, R/W, RESET,<br>CLK, RS1–RS5, CS                                          | l <sub>in</sub>  | _         | 10.0            | μА       |

| Hi-Z (Off State) Input Current<br>(V <sub>in</sub> = 0.4 to 2.4 V)                                                                                         | DTACK, PC0-PC7, D0-D7<br>H2, H4, PA0-PA7, PB0-PB7                                | I <sub>TSI</sub> | —<br>-0.1 | 20<br>1.0       | μA<br>mA |

| Output High Voltage ( $I_{Load} = -400 \mu A$ , $V_{CC} = Min$ ) ( $I_{Load} = -150 \mu A$ , $V_{CC} = Min$ ) ( $I_{Load} = -100 \mu A$ , $V_{CC} = Min$ ) | DTACK, D0-D7<br>H2, H4, PB0-PB7, PA0-PA7<br>PC0-PC7                              | v <sub>ОН</sub>  | GND +2.4  |                 | ٧        |

| Output low Voltage ( $I_{Load}$ = 8.8 mA, $V_{CC}$ = Min) ( $I_{Load}$ = 5.3 mA, $V_{CC}$ = Min) ( $I_{Load}$ = 2.4 mA, $V_{CC}$ = Min) PA0-PA7, F         | PC3/TOUT, PC5/PIRO<br>D0-D7, DTACK<br>PB0-PB7, H2, H4, PC0-PC2,<br>PC4, PC6, PC7 | V <sub>OL</sub>  | -         | 0.5             | ٧        |

| Maximum Internal Power Dissipation (Mea                                                                                                                    | sured at T <sub>A</sub> = 0°C)                                                   | P <sub>INT</sub> | _         | 750             | mW       |

| Input Capacitance (V <sub>in</sub> = 0, T <sub>A</sub> = 25°C, f = 1                                                                                       | MHz)                                                                             | C <sub>in</sub>  | _         | 15              | pF       |

a

M68000 FAMILY REFERENCE MANUAL

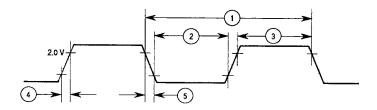

| Num.    | Characteristic            |                                    | 8 1      | ЛНz        | 10 MHz   |            |      |  |

|---------|---------------------------|------------------------------------|----------|------------|----------|------------|------|--|

| ivuiii. | Characteristic            | Symbol                             | Min      | Max        | Min      | Max        | Unit |  |

|         | Frequency of Operation    | f                                  | 2.0      | 8.0        | 2.0      | 10.0       | MHz  |  |

| 1       | Cycle Time                | tcyc                               | 125      | 500        | 100      | 500        | ns   |  |

| 2,3     | Clock Pulse Width         | <sup>†</sup> CL<br><sup>†</sup> CH | 55<br>55 | 250<br>250 | 45<br>45 | 250<br>250 | ns   |  |

| 4,5     | Clock Rise and Fall Times | <sup>t</sup> Cr<br><sup>t</sup> Cf | _        | 10<br>10   | _        | 10<br>10   | ns   |  |

#### NOTE:

Timing measurements are referenced to and from a low voltage of 0.8 V and high voltage of 2.0 V, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise of fall with be linear between 0.8 V and 2.0 V.

Figure 4. Clock Input Timing Diagram

y

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

#### q

9-16

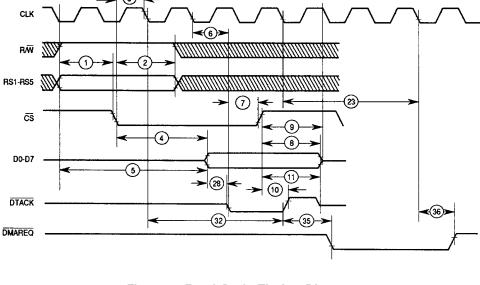

# AC ELECTRICAL SPECIFICATIONS ( $V_{CC} = 5.0 \, \text{Vdc} \pm 5\%$ ; GND = 0 Vdc; $T_A = 0^{\circ}\text{C}$ to 70°C, unless otherwise noted; see Figures 5–10)

|                    |                                                                                                                   | 8 N | 1Hz | 10 1 | ИНz      |           |

|--------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------|----------|-----------|

| Num.               | Characteristic                                                                                                    | Min | Max | Min  | Max      | Unit      |

| 1                  | R/W, RS1-RS5 Valid of CS Low (Setup Time)                                                                         | 0   |     | 0    | _        | ns        |

| 2                  | CS Low to R/W and RS1-RS5 Invalid (Hold Time)                                                                     | 100 | _   | 65   | _        | ns        |

| 31                 | CS Low to CLK Low (Setup Time)                                                                                    | 30  |     | 20   | _        | ns        |

| 4 <sup>2</sup>     | CS Low to Data Out Valid                                                                                          |     | 75  | _    | 60       | ns        |

| 5                  | RS1–RS5 Valid to Data Out Valid                                                                                   | _   | 140 | _    | 100      | ns        |

| 6                  | CLK Low to DTACK Low (Read/Write Cycle)                                                                           | 0   | 70  | 0    | 60       | ns        |

| 73                 | DTACK Low to CS High (Hold Time)                                                                                  | 0   | _   | 0    | _        | ns        |

| 8                  | CS or PIACK or TIACK High to Data Out Invalid (Hold Time)                                                         | 0   |     | 0    | _        | ns        |

| 9                  | CS or PIACK or TIACK High to D0-D7 High Impedance                                                                 | -   | 50  | _    | 45       | ns        |

| 10                 | CS or PIACK or TIACK High to DTACK High                                                                           |     | 50  | _    | 45       | ns        |

| 11                 | CS or PIACK or TIACK High to DTACK High Impedance                                                                 | -   | 100 | _    | 55       | ns        |

| 12                 | Data In Valid to CS Low (Setup Time)                                                                              | 0   | _   | 0    |          | ns        |

| 13                 | CS Low to Data In Invalid (Hold Time)                                                                             | 100 | _   | 65   | _        | ns        |

| 14                 | Port Input Data Valid to H1(H3) Asserted (Setup Time)                                                             | 100 | _   | 60   | _        | ns        |

| 15                 | H1(H3) Asserted to Port Input Data Invalid (Hold Time)                                                            | 20  |     | 20   |          | ns        |

| 16                 | Handshake Input H1(H4) Pulse Width Asserted                                                                       | 40  | _   | 40   | _        | ns        |

| 17                 | Handshake Input H1(H4) Pulse Width Negated                                                                        | 40  | _   | 40   |          | ns        |

| 18                 | H1(H3) Asserted to H2(H4) Negated (Delay Time)                                                                    |     | 150 | _    | 120      | ns        |

| 19                 | CLK Low to H2(H4) Asserted (Delay Time)                                                                           |     | 100 | _    | 100      | ns        |

| 204                | H2(H4) Asserted to H1(H3) Asserted                                                                                | 0   | _   | 0    | _        | ns        |

| 215                | CLK Low to H2(H4) Pulse Negated (Delay Time)                                                                      | _   | 125 | _    | 125      | ns        |

| 229,10             | Synchronized H1(H3) to CLK Low on which DMAREQ Is Asserted                                                        | 2.5 | 3.5 | 2.5  | 3.5      | Clk. Per. |

| 23                 | CLK Low on which $\overline{\text{DMAREQ}}$ is Asserted to CLK Low on which $\overline{\text{DMAREQ}}$ Is Negated | 2.5 | 3   | 2.5  | 3        | Clk. Per. |

| 24                 | CLK Low to Port Output Data Valid (Delay Time) (Modes 0 and 1)                                                    | _   | 150 |      | 120      | ns        |

| 25 <sup>9,10</sup> | Synchronized H1(H3) to Port Output Data Invalid (Modes 0 and 1)                                                   | 1.5 | 2.5 | 1.5  | 2.5      | Clk. Per. |

| 26                 | H1 Negated to Port Output Data Valid (Modes 2 and 3)                                                              | _   | 70  |      | 50       | ns        |

| 27                 | H1 Asserted to Port Output Data High Impedance<br>(Modes 2 and 3)                                                 | 0   | 70  | 0    | 70       | ns        |

| 28                 | Read Data Valid to DTACK Low (Setup Time)                                                                         | 0   | _   | 0    | _        | ns        |

| 29                 | CLK Low to Data Output Valid, Interrupt Acknowledge Cycle                                                         |     | 120 | _    | 100      | ns        |

| 30 <sup>7</sup>    | H1(H3) Asserted to CLK High (Setup Time)                                                                          | 50  |     | 40   | <u> </u> | ns        |

| 31                 | PIACK to TIACK Low to CLK Low (Setup Time)                                                                        | 50  | _   | 40   | <u> </u> | ns        |

| 32 <sup>10</sup>   | Synchronized CS to CLK Low on which DMAREQ is Asserted                                                            | 3   | 3   | 3    | 3        | Clk. Per. |

| 339,10             | Synchronized H1(H3) to CLK Low on which H2(H4) Is Asserted                                                        | 3.5 | 4.5 | 3.5  | 4.5      | Clk. Per. |

M68000 FAMILY REFERENCE MANUAL

#### AC ELECTRICAL SPECIFICATIONS (Continued)

| Num.             | Characteristic                                                | 8 1 | ИHz | 10  | ]   |                        |

|------------------|---------------------------------------------------------------|-----|-----|-----|-----|------------------------|

| Muin.            | Characteristic                                                | Min | Max | Min | Max | Unit                   |

| 34               | CLK Low to DTACK Low Interrupt Acknowledge Cycle (Delay Time) | -   | 100 | _   | 100 | ns                     |

| 35               | CLK Low to DMAREQ Low (Delay Time                             | 0   | 120 | 0   | 100 | ns                     |

| 36               | CLK Low to DMAREQ High (Delay Time)                           | 0   | 120 | 0   | 100 | ns                     |

| 37 <sup>10</sup> | Synchronized H1(H3) to CLK Low on which PIRQ Is Asserted      | 3.5 | 3.5 | 3.5 | 3.5 | Clk. Per.              |

| 38 <sup>10</sup> | Synchronized CS to CLK Low on which PIRQ is High Impedance    | 3   | 3   | 3   | 3   | Clk. Per.              |

| 39               | CLK Low to PIRQ Low or High Impedance                         | 0   | 250 | 0   | 225 | ns                     |

| 408              | TIN Frequency (External Clock) — Prescaler Used               | 0   | 1   | 0   | 1   | f <sub>clk</sub> (Hz)6 |

| 41               | TIN Frequency (External Clock) — Prescaler Not Used           | 0   | 1/8 | 0   | 1/8 | f <sub>clk</sub> (Hz)6 |

| 42               | TIN Pulse Width High or Low (External Clock)                  | 55  | _   | 45  | _   | ns                     |

| 43               | TIN Pulse Width Low (Run/Halt Control)                        | 1   | _   | 1   | _   | Clk. Per.              |

| 44               | CLK Low to TOUT High, Low, or High Impedance                  | 0   | 250 | 0   | 225 | ns                     |

| 45               | CS, PIACK, or TIACK High to CS, PIACK, or TIACK Low           | 50  | _   | 30  | _   | ns                     |

#### NOTES:

- 1. This specification only applies if the PI/T had completed all operations initiated by the previous bus cycle when  $\overline{\text{CS}}$  was asserted. Following a normal read or write busy cycle, all operations are complete within three clocks after the falling edge of the CLK pin on which  $\overline{\text{DTACK}}$  was asserted. If  $\overline{\text{CS}}$  is asserted prior to completion of these operations, the new bus cycle and  $\overline{\text{DTACK}}$  are postponed. If all operations of the previous bus cycle were complete when  $\overline{\text{CS}}$  was asserted, this specification is made only to ensure that  $\overline{\text{DTACK}}$  is asserted with respect to the falling edge of the CLK pin as shown in the timing diagram not to guarantee operation of the part. If the  $\overline{\text{CS}}$  setup time is violated, DTACK may be asserted as shown or may be asserted one clock later.

- 4. This specification assures recognition of the asserted edge of H1(H3).

- This specification applies only when a pulsed handshake option is chosen, and the pulse is not shortened due to any early asserted edge of H1(H3).

- 6. CLK refers to the actual frequency of the CLK pin, not the maximum allowable CLK frequency.

- If the setup time on the rising edge of the clock is not met, H1(H3) may not be recognized until the next rising of the clock.

- 8. This limit applies to the frequency of the signal at TIN compared to the frequency of the CLK signal during each clock cycle. If any period of the waveform at TIN is smaller than the period of the CLK signal at that instant, then it is likely that the timer circuit will completely ignore one cycle of the TIN signal. If these two signals are derived from different sources they will have different instantaneous frequency variations. In this case, the frequency applied to the TIN pin must be distinctly less than the frequency at the CLK pin to avoid lost cycles of the TIN signal. With signals derived from different crystal oscillators applied to the TIN and CLK pins with fast rise and fall times, the TIN frequency can approach 80 to 90% of the frequency of the CLK signal without loss of a TIN cycle. If these two signals are derived from the same frequency source, then the frequency of the signal applied to TIN can be 100% of the frequency at the CLK pin. They may be generated by different buffers from the same signal or one may be an inverted version of the other. The TIN signal may be generated by an AND function of the clock and a control signal.

- 9. The maximum value is caused by a peripheral access (H1(H3) asserted) and bus access (CS asserted) occurring simultaneously.

- Synchronized means that the input signal has been seen by the PI/T on the appropriate edge of the clock (rising edge for H1(H3) and falling edge for CS).

**MOTOROLA**

M68000 FAMILY REFERENCE MANUAL

Figure 5. Read Cycle Timing Diagram

Figure 6. Write Cycle Timing Diagram

9-18 M68000 FAMILY REFERENCE MANUAL

**MOTOROLA**

9

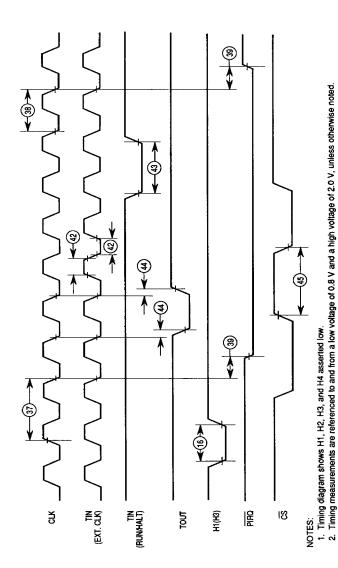

NOTE: Timing measurements are referenced to and from a low voltage of 0.8 V and a high voltage of 2.0 V, unless otherwise noted.

Figure 7. IACK Timing Diagram

**MOTOROLA**

**M68000 FAMILY REFERENCE MANUAL**

9-20

Figure 8. Peripheral Input Timing Diagram

Figure 9. Peripheral Output Timing Diagram

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

Figure 10. TIN, TOUT, PIRQ Timing Diagram

**M68000 FAMILY REFERENCE MANUAL**

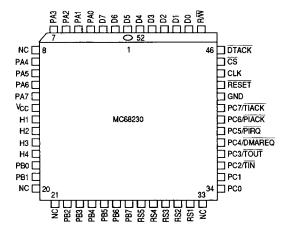

## **PIN ASSIGNMENTS**

## **48-LEAD DUAL-IN-LINE PACKAGE**

| D5  | Ц | 1  |   | $\cup$  |   | 48 | þ | D4         |

|-----|---|----|---|---------|---|----|---|------------|

| D6  | Ц | 2  |   |         |   | 47 | þ | D3         |

| D7  | ₫ | 3  |   |         |   | 46 | þ | D2         |

| PA0 | d | 4  |   |         |   | 45 | þ | D1         |

| PA1 | d | 5  |   |         |   | 44 | ם | D0         |

| PA2 | ₫ | 6  |   |         |   | 43 | þ | R∕W        |

| PA3 | ₫ | 7  |   |         |   | 42 | ם | DTACK      |

| PA4 | ┨ | 8  |   |         |   | 41 |   | CS         |

| PA5 | d | 9  |   |         |   | 40 | þ | CLK        |

| PA6 | d | 10 |   |         |   | 39 |   | RESET      |

| PA7 | ┨ | 11 |   |         |   | 38 | þ | GND        |

| Vcc | d | 12 | ١ | MC68230 | ) | 37 | þ | PC7/TIACK  |

| H1  | D | 13 |   |         |   | 36 | þ | PC6/PIACK  |

| H2  | Ц | 14 |   |         |   | 35 | þ | PC5/PIRQ   |

| H3  | D | 15 |   |         |   | 34 | þ | PC4/DMAREQ |

| H4  | Q | 16 |   |         |   | 33 | ۵ | PC3/TIOUT  |

| PB0 | D | 17 |   |         |   | 32 |   | PC2/TIN    |

| PB1 | d | 18 |   |         |   | 31 | þ | PC1        |

| PB2 | Ճ | 19 |   |         |   | 30 | þ | PC0        |

| PB3 | d | 20 |   |         |   | 29 | þ | RS1        |

| PB4 | ឰ | 21 |   |         |   | 28 | þ | RS2        |

| PB5 | d | 22 |   |         |   | 27 | þ | RS3        |

| PB6 | d | 23 |   |         |   | 26 | þ | RS4        |

| PB7 | þ | 24 |   |         |   | 25 | þ | RS5        |

|     | L |    |   |         |   |    | 4 |            |

MOTOROLA M68000 FAMILY REFERENCE MANUAL

**M68000 FAMILY REFERENCE MANUAL**