T-75-11-09

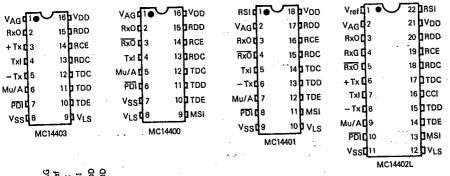

# **MOTOROLA** SEMICONDUCTOR \_\_\_\_ **TECHNICAL DATA**

#### CODEC-FILTER PCM-MONO-CIRCUIT

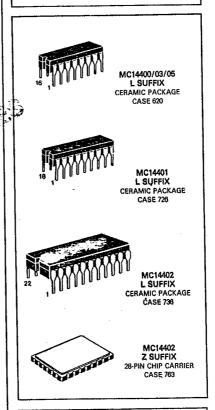

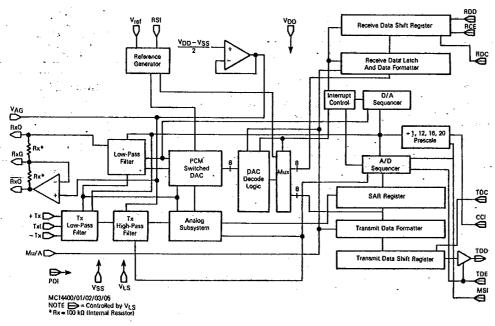

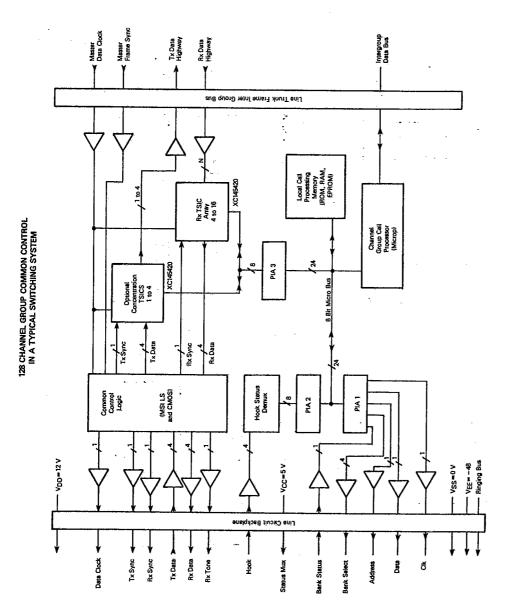

The MC14400, MC14401, MC14402, MC14403, and MC14405 are all per channel codec-filter PCM mono-circuits. These devices perform the voice digitizing and recovery, as well as the band limiting and signal restoration necessary in PCM systems. The MC14400 and MC14403 are general purpose devices that are offered in a 16-pin package. They are designed to operate in both synchronous and asynchronous applications and contain an on-chip precision voltage reference. The MC14401 is the same device, but offered in an 18-pin package. In addition, it offers the user the capability of selecting from three peak overload voltages (2.5, 3.15 and 3.78 V). The MC14405 is a synchronous device in a 16-pin package intended for instrument use. The MC14402 is the full feature device which presents all of the options available on the chip. This device is packaged in a 22-pin DIP and 28-pin chip carrier package, and contains all the features of the MC14400 and MC14401 plus several more. Most of these features can be made available in a lower pin count package tailored to a specific user's application. Contact the factory for further details.

The devices were designed to be upward compatible with the MC14404/06/07 codecs and other industry standard codecs. They also maintain compatibility with Motorola's family of TSACs (MC14416/MC14417/MC14418) as well as the MC3419 SLIC.

The PCM codec-filter mono-circuits utilize CMOS due to its reliable low power performance and proven capability for complex analog/ digital LSI functions

MC14400

16-Pin Package

On-Chip Precision Voltage Reference (3.15 M

Power Dissipation - 45 mW at 2.048 MHz at 10 V 0.1 mW Powered Down at 10 V ±5; ±6,

Compatibility with Various Supply Configurations: + 12 Volts (5%)

Pin Selectable TTL and CMOS Digital Levels

Automatic Prescale Divide of Any One of 5 Clock Frequencies (128 kHz, 1.536 MHz, 1.544 MHz, 2.048 MHz, or 2.56 MHz) to Generate the Internal Sequencing Clock

Pin Selection of Both A-LAW/Mu-LAW Companding and D3/D4 or CCITT Digital Formats

Output Drive Capability for 600 and 900 Ohm Loads of + 12 dBm

Synchronous and Asynchronous Operation On-Chip Attendent Interrupt Conferencing

Transmit Bandpass and Receive Low-Pass Filters on Chip

MC14401 - All of the Above Plus:

18-Pin Package

Selectable Peak Overload Voltages (2.5, 3.15 and 3.78 Volts)

Access to the "Minus" Input of the Tx Input Op Amp MC14402 - All of the Above Plus:

22-Pin Package

Variable Data Clocks (64 kHz to 3.088 MHz)

Access to Transmit Input Amplifier

An External Precision Reference May Be Used

External Gain Adjust for Complex SLIC Configurations MC14403

16-Pin Package

Same Device as MC14400 with Access to Transmit Input Amplifier with Single Ended Receive Output

MSI Tied Internally to TDE

MC14405

16-Pin Package

Same Device as MC14403 with Common 64 kHz to 3.088 MHz Data Clocks

MC14400 MC14401 MC14402 MC14403 MC14405

## **CMOS LSI**

(LOW-POWER COMPLEMENTARY MOS)

**CODEC-FILTER** PCM MONO-CIRCUIT

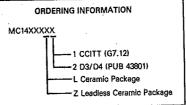

#### PCM MONO-CIRCUIT BLOCK DIAGRAM

#### **DEVICE DESCRIPTIONS**

There are five distinct versions of the Motorola PCM mono-circuit.

#### MC14400

The MC14400 PCM mono-circuit is a PCM codec-filter intended for standard word interleaved synchronous or asynchronous applications. The TDC pln on this device is the input to both the TDC and CCI functions in the pin description. Consequently, for MSI=8 kHz, TDC can be one of five discrete frequencies. These are 128 kHz (40 to 60% duty) 1.536, 1.544, 2.048 or 2.56 MHz. (For other data clock frequencies see MC14402 or MC14405.) The internal reference is set for 3.15 volts peak full scale, and the full scale input level at Txl and output level at RxO is 6.3 volts peak-to-peak. This is the +3 dBmO level of the PCM mono-circuit, All other functions are described in the pin description.

## MC14401

The MC14401 PCM mono-circuit offers the same features and is for the same application as the MC14400, but offers two additional pins and features. The reference select input allows the full scale level of the device to be set at 2.5 Vp, 3.15 Vp or 3.78 Vp. The — Tx pin allows for external transmit gain adjust and simplifies interface to the MC3419 SLIC. Otherwise, it is identical to MC14400.

#### MC14402

The MC14402 PCM mono-circuit is the full featured 22-pin device. It is intended for use in applications requiring maximum flexibility. The MC14402 contains all the features of the

MC14400 and MC14401. The MC14402 is intended for bit interleaved or word interleaved operation with data clock frequencies which are non standard or time varying. One of the five standard frequencies (listed above) is applied to the CCI input and the data clock inputs can be any frequency between 64 kHz and 3.088 MHz. The  $V_{\rm ref}$  pin allows for use of an external shared reference or selection of the internal reference and RxG and + Tx provide maximum flexibility for analog interface.

#### MC14403

The MC14403 PCM mono-circuit is intended for standard word interleaved asynchronous or synchronous applications. TDC can be one of five discrete frequencies. These are 128 kHz (40 to 60% duty) 1.536, 1.544, 2.048 or 2.56 MHz. (For other data clock frequencies see MC14402 or MC14405.) The internal reference is set of 3.15 volts peak full scale, and the full scale input level at Txl and output level at RxO is 6.3 volts peak-to-peak. This is the  $\pm 3$  dBm0 level of the PCM monocircuit. The  $\pm$ Tx and  $\pm$ Tx inputs provide maximum flexibility for analog interface. All other functions are described in the pin description.

#### MC14405

The MC14405 PCM mono-circuit is Intended for word interleaved synchronous applications. The MC14405 has all the features of the MC14403 but internally connects TDC and RDC (see pin description) to the DC pin. One of five standard frequencies (listed above) should be applied to CCI and the DC input can be any frequency between 64 kHz and 3.088 MHz.

T-75-11-09

| S | VAG C<br>RxO C<br>+ Tx C<br>Txl C<br>- Tx C<br>Mu/A C<br>PDI I | 3<br>4<br>5<br>6<br>7 | 16 V <sub>DD</sub> 16 ROD 14 RCE 13 DC 12 CCI 11 TOD 10 TDE 9 VLS |

|---|----------------------------------------------------------------|-----------------------|-------------------------------------------------------------------|

|---|----------------------------------------------------------------|-----------------------|-------------------------------------------------------------------|

| MAXIMUM RATINGS (Voltage Referenced to VSS)   |                                  | T               | Unit |

|-----------------------------------------------|----------------------------------|-----------------|------|

| Reting                                        | Symbol                           | Value           | Unit |

| DC Supply Voltage                             | V <sub>DD</sub> -V <sub>SS</sub> | -0.5 to 13      | V    |

|                                               | V                                | -0.5 to VDD+0.5 | V    |

| Voltage, Any Pin to VSS                       |                                  | . 10            | mAdo |

| DC Current Drain per Pin (Excluding VDD, VSS) | TA                               | -40 to +85      | °C   |

| Operating Temperature Range                   |                                  | -85 to +150     | °C   |

| Storage Temperature Range                     | ¹ stg                            | -00 10 1 100    |      |

RECOMMENDED OPERATING CONDITIONS

|                                                                                 |                               |                                    | 0 to 70°C | 25°C_                               | 0 to 70°C        |      |

|---------------------------------------------------------------------------------|-------------------------------|------------------------------------|-----------|-------------------------------------|------------------|------|

| Parameter                                                                       |                               | Pins                               | Min       | Тур                                 | Max              | Unit |

| DC Supply Voltage                                                               |                               | VCC to VSS                         | 6         | 10 to 12                            | 13               |      |

| Power Dissipation CMOS Mode 10 V TTL Mode 10 V                                  |                               | V <sub>DD</sub> to V <sub>SS</sub> | _         | 45<br>76                            | 70<br>110        | mW   |

| Power Down Dissipation 10 V                                                     |                               | V <sub>DD</sub> to V <sub>SS</sub> |           | 0.1                                 | 1.0              | mW   |

| Frame Rate Transmit and Receive                                                 |                               | MSI                                | 7.5       | 8.0                                 | 8.5              | kHz  |

| Data Rate MC14400, MC14401, and MC14403 (Must Use One of These Frequencies) ±2% |                               | TDC, RDC                           |           | 128<br>1536<br>1544<br>2048<br>2560 | -<br>-<br>-<br>- | kHz  |

| Data Rate MC14402, MC14405                                                      |                               |                                    | 64        | -                                   | 3088             | kHz  |

| Full Scale Output and Input Levels MC14400, MC14403, MC144                      | 405                           |                                    | -         | 3.15                                | -                |      |

| MC14401 and MC14402, V <sub>ref</sub> = V <sub>SS</sub>                         | RSI=VDD<br>RSI=VSS<br>RSI=VAG | RxO, Txl                           | · -<br>-  | 3.78<br>3.15<br>2.50                | -<br>-<br>-      | Vp   |

DIGITAL LEVELS (TA = 0 to 70°C)

| Parameter                                  |        | Symbol | V <sub>DD</sub> to V <sub>SS</sub> | Min                   | Тур                  | Max     | Unit        |

|--------------------------------------------|--------|--------|------------------------------------|-----------------------|----------------------|---------|-------------|

| CMOS Mode                                  |        |        | 1 20 00                            |                       | · · · / F            | - 1000  | - Oint      |

| TDE, RCE, RDD, PDI, RDC, TDC, DC, CCI, MSI | "0"    |        | 12                                 | _                     | 5.25                 | 3.6     | Ì           |

|                                            | "1"    | _      | 12                                 | 8.4                   | 6.75                 | _       | V           |

| TTL Mode                                   | -      |        | <del> </del>                       | -                     |                      |         | ┝╾          |

| TDE, RCE, RDD, PDI, RDC, TDC, DC, CCI, MSI | "0"    | _      | 10                                 |                       | VLS+1.0              | VLS+0.8 | ļ           |

|                                            | "1"    |        | 10                                 | V <sub>LS</sub> + 2.0 | V <sub>LS</sub> +1.8 |         | ٧ ا         |

| TDD Output Current                         |        |        | 1                                  |                       |                      | ····    | <del></del> |

|                                            | =2.4 V | IOH    | 10                                 | 150                   | -                    | _       | μA          |

| VOL                                        | =0.8 V | lor    | -                                  | 1.6                   | -                    | -       | ma          |

| Characteristic                                                                                                                   | j E1                               | AG=0, T                      | A                    | /D                              |                      | /A                               | 7               |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------|----------------------|---------------------------------|----------------------|----------------------------------|-----------------|

| <del></del>                                                                                                                      | Min                                | Max                          | Min                  | Max                             | Min                  | Max                              | Unit            |

| Absolute Gain (0 dBm0 @ 1.02 kHz)                                                                                                | -0.3                               | +0.3                         | -0.3                 | +0.3                            | -0.3                 | +0.3                             | ₫B              |

| Gain vs Level Tone (Relative to 10 dBm0, 1.02 kHz)<br>+3 to 40 dBm0<br>40 to 50 dBm0<br>55 dBm0                                  | -0.4<br>-0.8<br>-1.6               | +0.4<br>+0.8<br>+1.6         | -0.2<br>-0.4<br>-1.0 | +0.2<br>+0.4<br>+1.0            | -0.2<br>-0.4<br>-0.8 | +0.2<br>+0.4<br>+0.8             | dB              |

| Gein vs Level — Pseudo Noise (A-Law Only, MC144XXL1 Only) (Relative to — 10 dBm0) — 10 to — 55 dBm0 — 60 dBm0                    | -0.45<br>-0.90                     | +0.45<br>+0.90               |                      | -                               | -                    | -                                | dB              |

| Total Distortion — 1.02 kHz Tone (C Message) 0 to -30 dBm0 -40 dBm0 -45 dBm0                                                     | 35<br>29<br>24                     | -<br>-<br>-                  | 35<br>29<br>24       |                                 | 36<br>30<br>25       | -                                | dВ              |

| Total Distortion with Noise (A-Law Only, MC144XXL1 Only)  - 3 dBm0  - 34 dBm0  - 40 dBm0  - 55 dBm0  idle Noise                  | 27.5<br>35<br>33.1<br>28.5<br>13.5 | <br><br>                     | -                    | -                               | -                    | -<br>-<br>-<br>-                 | dB              |

| (Mu Law, C Message)<br>(A Law, Psophometric MC144XXL1 Only)                                                                      | _                                  | 18<br>-68                    |                      | 18<br>-68                       | -                    | 13<br>- 75                       | dBrnCo<br>dBmOp |

| Frequency Response (Relative to 10 dBm0, 1.02 kHz) 15 to 60 Hz 300 to 3000 Hz 3400 Hz 4000 Hz 4600 Hz                            | <br>0.30<br>1.6<br>                | 23<br>+0.30<br>0<br>28<br>60 | -0.15<br>-0.8<br>-   | -23<br>+0.15<br>0<br>-14<br>-32 | -0.15<br>-0.8<br>-   | 0.15<br>+0.15<br>0<br>-14<br>-30 | dBm0            |

| Inband Spurious (1.02 kHz@0 dBm0)<br>300 to 3400 Hz                                                                              | _                                  | -43                          |                      | -43                             | +                    | - 43                             | dBm0            |

| Out-of-Band Spurious (0 to 12 kHz in, @0 dBm0)<br>0 to 3400 Hz<br>3400 to 4600 Hz<br>4600 Hz to 12 kHz<br>dle Noise Selective    | 1 1 1                              | 30<br>28<br>30               | 1 1 -                | -30<br>-<br>-                   |                      | -<br>-<br>-                      | dBm0            |

| @ 8 kHz with VAG = Txl Measure at RxO, 30 Hz Bandwidth                                                                           | _                                  | <b>∽50</b>                   | _                    |                                 | _                    |                                  | dBm0            |

| Group Delay Difference 0 dBm0, TDC, RDC = 2.048 MHz 500 to 600 Hz 600 to 1000 Hz 1000 to 2600 Hz 2600 to 2800 Hz 2600 to 2800 Hz | -<br>-<br>-<br>-                   | 80<br>60<br>140<br>80        | 1 1 1                | <br>-<br>-                      | -<br>-<br>-          | -<br>-<br>-                      | µsес            |

| o to Return Crosstalk @0 dBm0  Txl to TDD @ RxO  RDD to RxO @ TDD                                                                | _                                  | -                            |                      | -65                             | -                    | -65                              | dBm0            |

| Absolute Group Delay @ 1.02 kHz<br>TDC= RDC= 2.048 MHz                                                                           |                                    | 460                          |                      |                                 |                      |                                  |                 |

T-75-11-09

ANALOG ELECTRICAL CHARACTERISTICS (VDD = (10-12 V) ±5%, 0 to 70°C)

| Characteristic                               |                                       | Symbol | Min      | Тур        | Max                                              | Unit     |

|----------------------------------------------|---------------------------------------|--------|----------|------------|--------------------------------------------------|----------|

|                                              | -Tx, +Tx, (Txl for MC14400)           | lin    |          | ±0.01      | ±30                                              | Ī        |

| Input Current                                | Txl (for MC14400) to VAG              | Zin    | 100      | 200        | _                                                | kΩ       |

| AC Input Impedance (1 kHz)                   | -Tx. +Tx to VAG                       | Zin    | 1.5      | 5.0        | -                                                | МΩ       |

| AC Input Impedance (1 kHz)                   | -Tx, +Tx                              | VICE   | +1.5     | _          | +8.0                                             | ٧        |

| Input Common Mode Voltage Range VDD = 10.0 V | - 10, 1 10                            | -ion   |          |            |                                                  |          |

| Output Voltage Range                         | RXO, RXO                              | VORto  | 4.0      | ٠          | +4.0                                             |          |

| RL=20 k to VAG                               | Each                                  | VAG    | -3.2     | -          | +3.2                                             | l v      |

| RL=600 to VAG                                | Output                                | 7.0    | -3.9     | -          | +3.9                                             |          |

| RL=900 to VAG                                | V <sub>OH</sub> =V <sub>DD</sub> −0.8 | -      | -5.0     | -          | <b>-</b>                                         | mA       |

| Output Current RxO, RxO                      | V <sub>OL</sub> =0.8                  | -      | +5.0     | <u>  -</u> |                                                  |          |

| D. C. D. C.                                  | RxO to VAG                            | PSRR   | 30       | 40         | -                                                | d8       |

| Power Supply Rejection Ratio                 | RxO to VAG                            | i      | 30       | 40         | <u> </u>                                         | <u> </u> |

| V <sub>DD</sub> = 12 V ± 0.05 V peak @ 1 kHz | V <sub>ref</sub> to VAG               |        | 2.0      | Γ-         | 3.8                                              | l V      |

| Shared External Reference                    | 1(8)                                  | lin    | 1        | 0.3        | Γ-                                               | mA       |

| Vref Input Current                           | Source                                | IVAG   | +        | 200        | <del>                                     </del> | μA       |

| VAG Output Current                           |                                       |        | +        | 8.0        | <del> -</del>                                    | mA       |

|                                              | Sink                                  | VAG    | <b>I</b> | 10.0       | <u> </u>                                         | 1.110    |

MODE CONTROL LOGIC (VSS=0 V, 0 to 70°C)

| Characteristics                                 |                         | V <sub>DD</sub> | Min      | Тур          | Max        | Unit       |

|-------------------------------------------------|-------------------------|-----------------|----------|--------------|------------|------------|

| V <sub>LS</sub> Voltage for TTL Mode            |                         | 10<br>12        | 0        | -            | 6.0<br>8.0 | ٧          |

| ALS Appliage for LLE mode                       |                         | 10              | 9.5      | _            |            | V          |

| VLS Voltage for CMOS Mode                       |                         | 12              | 11.5     |              |            | _ <u>_</u> |

| Mu/A Select Voltage                             |                         | ١ ا             |          | 1            |            | l          |

| Mu-Law Mode                                     |                         | 10              | 9.5      | -            | -          | ĺ          |

| MG-Edst Micco                                   |                         | 12              | 11.5     | -            | 6.0        | ĺ          |

| Sign Magnitude Mode                             |                         | 10              | 4.0      | -            | 7.0        | l۷         |

| aigh Magnitude Modo                             |                         | 12              | 5.0      | -            |            | ľ          |

| A-Law Mode                                      |                         | 10              | <b>–</b> | -            | 0.5        |            |

| W-FRM MICOR                                     |                         | 12              |          | <u> </u>     | 0,5        | ļ.,        |

| A                                               | 3.78 V Mode             | 10              | 9.5      | -            | -          | ļ۷         |

| Reference Select Voltage                        |                         | 12              | 11.5     | <u> </u>     | <u> </u>   | <u> </u>   |

|                                                 | 2.5 V Mode              | 10              | 4.0      | I -          | 6.0        | V          |

|                                                 |                         | 12              | 5.0      | <u> </u>     | 7.0        | <u> </u>   |

|                                                 | 3,15 V Mode             | 10              | Γ-       | <b>–</b>     | 0.5        | V          |

|                                                 |                         | 12              | I        | l <u>-</u> . | 0.5        | <u> </u>   |

|                                                 | External Reference Mode | 10              | 4.0      | T            | <b>—</b>   | ١v         |

| V <sub>ref</sub> Mode Voltage                   | Exterior mordrenes mass | 12              | 5.0      | <b>1</b>     | l          | <u>L</u>   |

| •                                               | Internal Reference Mode | 10              | T -      | T -          | 0.5        |            |

|                                                 | internal floraration    | 12              | <u> </u> |              | 0.5        | 上          |

| MOL-COL                                         |                         | 10              | -        | 128          | -          | kH         |

| Analog Test Mode Selection Frequency, MSI = CCI |                         | 12              | ļ -      | 128          | l –        | Ľ          |

| See Pin Description; Test Modes                 |                         |                 |          |              |            |            |

2

| Charac                                                                                                                | teristic                                                                                                                      | Symbol                                 | Min                     | Тур                                 | Max                                  | Unit     |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------|-------------------------------------|--------------------------------------|----------|

| Output Rise Time<br>Output Fall Time                                                                                  | · · TDD                                                                                                                       | tTLH<br>tTHL                           | -                       | 30                                  | 80)                                  | ns       |

| Input Rise Time<br>Input Fall Time                                                                                    | DC, TDE, CCI, RCE, RDC, TDC, MSI                                                                                              | tTLH<br>tTHL                           | -                       | -                                   | 4                                    | μS       |

| Pulse Width                                                                                                           | DC, TDE Low, CCI, RCE, RDC, TDC, MSI                                                                                          | twH                                    | 100                     | _                                   | _                                    | ns       |

| Clock Pulse Frequency                                                                                                 | DC, TDC, RDC                                                                                                                  | fcl.                                   | 64                      | -                                   | 3088                                 | kHz      |

| Clock Pulse Frequency (MSI = 8 kHz) This Pin Will Accept One of These 5 Discrete Cloc to Produce Internal Sequencing. | k Frequencies and Compensate 2 3 4 5                                                                                          | fCL1<br>fCL2<br>fCL3<br>fCL4<br>fCL5   |                         | 128<br>1536<br>1544<br>2048<br>2560 |                                      | kHz      |

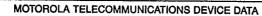

| Propagation Delay Time TTL CMOS TTL CMOS TTL CMOS TTL CMOS                                                            | TDE to TDD Low Impedance TDE to TDD Low Impedance TDE to TDD High Impedance TDE to TDD High Impedance TDC* to TDD TDC* to TDD | tp1<br>tp1<br>tp2<br>tp2<br>tp3<br>tp3 | 85<br>50<br>-<br>-<br>- | 130<br>100<br>50<br>20<br>120<br>80 | 180<br>160<br>75<br>40<br>180<br>160 | ns       |

| TDE Rising Edge to TDC Falling Edge Setup Time                                                                        |                                                                                                                               | tsu1                                   | 20<br>100               | 1 1                                 |                                      | ns<br>ns |

| RCE Rising Edge to RDC Falling Edge Setup Time                                                                        |                                                                                                                               | tsu3                                   | 20<br>100               | -                                   | _                                    | ns<br>ns |

| MSI Rising Edge to CCI Falling Edge Setup Time                                                                        |                                                                                                                               | tsu6                                   | 20<br>100               |                                     | -                                    | ns<br>ns |

| RDD Valid to RDC Falling Edge Setup Time                                                                              |                                                                                                                               | t <sub>su5</sub>                       | 60                      | 40                                  | _                                    | ns       |

| OD Hald Time Common Collins To Land                                                                                   | ·                                                                                                                             | -out                                   |                         | .,,                                 |                                      |          |

For the sign bit, tp3 is measured from TDE or TDC, whichever is last.

#### PIN DESCRIPTION

RDD Hold Time from RDC Falling Edge

#### DIGITAL

VLS selects CMOS or TTL compatibility for all digital I/Os. VLS=VDD; all I/O is CMOS, (VDD to VSS swing). VLS<VDD-4 volts; all I/O is TTL with switchpoint 1.4 V above VLS. The pins controlled by VLS are inputs MSI, CCI, TDC, RDC, TDE, RCE, RDD, PDI and output TDD. In TTL applications VLS is Digital GND.

MSI is a continuous 8 kHz (for sampling rate) signal which is used as a time base for internally selecting a prescale divider for CCI input. MSI should be tied to the frame sync or system sync signal, but has no relation to transmit or receive data timing, except as described under TDE. MSI should be derived from the transmit timing in asynchronous applications. In many applications MSI can be tied to TDE. (MSI is tied to TDE in MCI4403/05.)

CCI input is designed to accept five discrete clock frequencies. These are 128 kHz 40 to 60% duty cycle, 1.536 MHz, 1.544 MHz, 2.048 MHz or 2.56 MHz. The frequency at this input is compared with MSI and prescale divided to produce the internal sequencing clock at 128 kHz (or 16 times the sampling rate). The four clocks in the MHz frequency range have only minimum pulse width duty cycle requirements. In the asynchronous applications, CCI should be derived from transmit timing. (CCI is tied to TDC in MC14400/01/03).

TDC is the transmit data bit rate input. It can be any frequency from 64 kHz to 3,088 MHz, and is often tied in common to CCI if the data rate is equal to one of the five discrete frequencies. This clock is the shift clock for the transmit shift register and leading edges produce successive data bits at TDD. In asynchronous applications, TDE should be derived from this clock. (TDC and RDC are tied together in MC14405 and are called DC.)

TDE serves two functions for the transmit data timing. It establishes the transmit sync in conjunction with MSI. If the leading edges of TDE occur at 8 kHz and both MSI and TDE

are derived from TDC, then the MSI relationship is transparent and TDE is simply transmit sync. The leading edge of TDE produces the sign bit at TDD during the current TDC period. The TDC shifts out the remaining bits at the TDC rate. The TDD pin is active as long as TDE is high. If there is more than one TDE leading edge per frame, then the first TDE after MSI is the Tx sync. Thus, TDE may be taken low to three state TDD after the first leading edge. The additional TDE high periods before the next MSI merely un-three-states TDD. This can be used for bit interleaved systems. In asynchronous applications, TDE is derived from TDC.

100 60

ns

TDD is the digital data output. It operates in sync with TDC and TDE. It is a three-state output. TDC, TDE, and TDD independently control transmit data timing. The data format (Mu-Law, A-Law or sign magnitude) is controlled by Mu/A. This output may be made high-speed CMOS compatible using a pullup resistor.

RDC is the receive data clock and works in conjunction with RCE and RDD to produce all receive data timing. These three signals must be synchronous, but can be asynchronous with all other digital pins. RDC provides the receive register clock. The RDC clock may be any frequency from 64 kHz to 3.088 MHz.

RCE — The rising edge of RCE should identify the sign bit of a receive word on RDD. The next falling edge of RDC, after a rising RCE, loads the first bit of the PCM word into the receive register. The next seven falling edges enter the remainder of the PCM word. On the ninth rising edge, the receive word is transferred to the receive buffer register and the A/D sequence is interrupted to commence the decode process. In the asynchronous mode and with an 8 kHz transmit sample rate, the receive sample rate should be between 7.5 and 8.5 kHz. Two receive words may be decoded each transmit frame to allow on chip conferencing.

RDD is the digital data input. It operates synchronously with RDC and RCE. The data format is determined by the Mu/A pin.

T-75-11-09

| Code         | Sign/<br>Magnitude | Mu-Law    | A-Law<br>(CCITT) |

|--------------|--------------------|-----------|------------------|

| + fuil scale | 1111 1111          | 1000 0000 | 1010 1010        |

| + zero       | 1000 0000          | 1111 1111 | 1101 0101        |

| - zero       | 0000 0000          | 0111 1111 | 0101 0101        |

| - full scale | 0111 1111          | 0000 0010 | 0010 1010        |

| Sign<br>Bit | Che | ord Sel | ect | Step Select |   |   |   |

|-------------|-----|---------|-----|-------------|---|---|---|

| 0           | 1   | 2       | 3   | 4           | 5 | 6 | 7 |

Note: Starting from sign magnitude, to change format:

To Mu-Law

MSB is unchanged (sign)

invert remaining seven bits if code is 0000 0000, change to 0000 0010 (for zero code

suppression) To A-Law --

MSB is unchanged (sign) invert odd numbered bits

ignore zero code suppression

Mu/A Select — This pin selects the companding law and the data format at TDD and RDD.

Mu/A = VDD; Mu255 Companding D3 Data Format with Zero Code Supress

Mu/A=VAG; Mu255 Companding with Sign Magnitude **Data Format**

Mu/A=Vss; A-law Companding with CCITT Data Format Bit Inversions

PDI - The power down input disables the bias circuitry and gates off all clock inputs. This puts the TxI, RxO, RxO, and TDD outputs into a high impedance state. The power dissipation is reduced to 0.1 mW when  $\overrightarrow{PD} = VLS$  or VSS. The circuit operates normally with  $\overrightarrow{PD} = VDD$  or with a logic high as defined by connection at VLS. TDD will not come out of high impedance for two MSI cycles after PDI goes high.

DC - In the MC14405, TDC and RDC are internally connected to this pin.

## **ANALOG**

#### VAG Analog Ground

Each version of the PCM mono-circuit produces its own analog ground internally. The DC voltage is approximately (VDD-VSS)/2. All analog functions within the device use this as a reference point for signal processing. In symetric dual supply systems (±5, ±6, etc.), VAG may externally be tied to the system analog ground supply. The VAG output will sink more than 8 mA of current, but can source only 200 μA. When RxO or RxO are output drives for 600 or 900 loads tied to VAG, a pullup resistor to VDD will be required to boost the source current capability if VAG is not tied to the supply ground.

# Vref Positive Voltage Reference Input (MC14402 Only)

The V<sub>ref</sub> pin provides for the supply of an external voltage reference or for the selection of an internal reference within the PCM mono-circuit. If V<sub>ref</sub> is tied to V<sub>SS</sub>, the internal reference is selected. If V<sub>ref</sub> > V<sub>AG</sub>, then the external mode

is selected. In each case, the overload or full scale gains of the codec are selected by the reference select pin (RSI). Both the internal and external references are inverted within the PCM mono-circuit for negative input voltage such that only one reference is required.

46E D

External Mode — In the external reference mode (Vref > VAG), a 2.5 volt reference like the MC1403 is connected vAGI, a 2.5 voit reference like the intervals is considered from Vref to VAG. A single external reference may be shared by tying together a number of Vrefs and VAGs from different PCM mono-circuits. In special applications, the reference voltage may be between 2 and 4 volts. However, the gain selection logic associated with RSI must be considered to artise at the field PCM mono-circuit rain. rive at the desired PCM mono-circuit gain.

- In the internal reference mode Internal Mode (Vref=VSS), an internal reference supplies the reference voltage for the PCM mono-circuit.

# RSI Reference Select Input (MC14401/02 Only)

The RSI input allows the selection of three different overload or full scale voltages independent of the internal or external reference mode. The selection of maximum signed level is made by connecting RSI to VDD, VAG or VSS. The various modes of operation are summarized in the table below. The internal reference is designed to give internal gains equal to those obtained with an external 2.5 volt

## RxO and RxO Receive Analog Outputs

These two complimentary outputs are generated from the I hese two complimentary outputs are generated from the output of the receive filter. They are equal in magnitude and out of phase. The maximum signal output of each is equal to the maximum peak-to-peak signal described with the reference. If a 2.5 V reference is used with RSI tied to VAG and a + 3 dBm0 sine wave is decoded, the RXO output will be a 5 V peak-to-peak signal. RXO will also have a signal output of 5 V peak-to-peak signal. RXO will also have a signal output of 5 V peak-to-peak. put of 5 V peak-to-peak. External loads may be connected put of  $\sigma$  v peak-to-peak. External roads may be connected from RxO to RxO for a 6 dB push-pull signal gain or from either RxO or RxO to VAG. With RSI tied to VSS, each output will drive 600  $\Omega$  to +9 dBm. With RSI tied to VDD, each output will drive 900 \Omega to +9 dBm.

## ADDITIONAL PIN DESCRIPTIONS

# fixG Receive Output Gain Adjust (MC14402 Only)

If RxG is left open, then the output signal at RxO will be inverted and output at RxO. Thus the push-pull gain to a load from RxO to RxO is two times the output level at RxO. If external resistors are applied from RxO to RxG (RI) and from RxG to  $\overline{\text{RxO}}$  (RG), the gain of  $\overline{\text{RxO}}$  can be set differently from -1. These resistors should be in the range of 10 k $\Omega$ . The RxO output level is unchanged by the resistors and the RxO gain is equal to minus RG/RI(VRxO). The purpose of RxG is to allow external receive gain adjustment. The circuit for RxG and RxO is shown in the block diagram.

# + Tx Positive Tx Amplifier Input (MC14402/03/05 Only)

-Tx Negative Tx Amplifier Input (MC14401/02/03/05 Only) The Txl pin is the input to the transmit bandpass filter. If

+Tx or -Tx are available, then there is an internal amplifier preceding the filter whose pins are +Tx, -Tx and Txl. These pins allow access to the amplifier terminals to tailor the input gain with external resistors. The resistors should be in the range of 10 k. If +Tx is not available, it is internally tied to VAG. If -Tx and +Tx are not available, the Txl is a unity gain high impedance input.

## Txl Analog Input

Txl is the input to the transmit filter. It is also the output of the transmit gain amplifiers of the Mc14401/02/03/05. The input impedance is greater than 100 k to VAG in the Mc14400. The Txl input has an internal gain of 1.0, such that a +3 dBm0 signal at Txl corresponds to the peak-to-peak swing of RxO described above. For  $\pm 2.5$  V shared references and RSI=VAG, the +3 dBm0 input should be 5.0 volt peak-to-peak,

#### **Power Supplies**

$\mbox{V}_{\mbox{\scriptsize DD}}$  — Most Positive Supply.  $\mbox{V}_{\mbox{\scriptsize DD}}$  is typically 10 to 12 volts.

$\mbox{VSS} - \mbox{Most}$  Negative Supply. This is the most negative supply pin.

For single-supply systems, these are the only power pins. VLS will be tied to VSS or VDD and VAG is an output. In dual-supply systems, VLS may be digital ground and VAG may be analog ground.

#### Testing Considerations (MC14400/01/02 Only)

An analog test mode is activated by connecting MSI and CCI to 128 kHz. In this mode, the input of the codec (the output of the Tx filter) is available on the PDI pin. This input is a DC auto zeroed access to the A/D side of the codec. If monitored with a high-impedance buffer, the output of the Tx low-pass filter can also be measured at the PDI pin. This test mode allows independent evaluation of the transmit low-pass filter and A/D side of the codec. The receive channel of the mono-circuit is tested with the codec and filter together.

#### **TEST CIRCUIT**

#### **OPTIONS AVAILABLE BY PIN SELECTION**

| RSI*<br>Pin Level | V <sub>ref</sub> *<br>Pin Level | Peak-to-Peak Overload Voltage (Txl, RxO) |

|-------------------|---------------------------------|------------------------------------------|

| VDD               | Vss                             | 7.56 Vpp                                 |

| VDD               | Vag+Vext                        | (3.02 × V <sub>EXT</sub> ) Vpp           |

| VAG               | Vss                             | 5 Vpp                                    |

| VAG               | Vag + Vext                      | (2 × V <sub>EXT</sub> ) Vpp              |

| VSS               | Vss                             | 6.3 Vpp                                  |

| VSS               | Vag + Vext                      | (2.52 × V <sub>EXT</sub> ) Vpp           |

$<sup>^{\</sup>circ}$  On MC14400/03/05, RSI and V<sub>ref</sub> tied internally to VSS- On MC14401, V<sub>ref</sub> tied internally to VSS.

# SUMMARY OF OPERATION CONDITIONS USER PROGRAMMED THROUGH PINS VDD, VAG, AND VSS

| Pin<br>Programmed<br>Logic<br>Level |                                                                              | RSI<br>Peak Overload<br>Voltage | V <sub>LS</sub>       |

|-------------------------------------|------------------------------------------------------------------------------|---------------------------------|-----------------------|

| V <sub>DD</sub>                     | Mu-Law Companding Curve and D3/D4<br>Digital Formats with Zero Code Suppress | 3.78                            | CMO\$<br>Logic Levels |

| VAG                                 | Mu-Law Companding Curve and Sign<br>Magnitude Data Format                    | 2.50                            | TTL Levels<br>VAG Up  |

| Vss                                 | A-Law Companding Curve and CCITT Digital Format                              | 3.15                            | TTL Levels<br>VSS Up  |

T-75-11-09

T-75-11-09

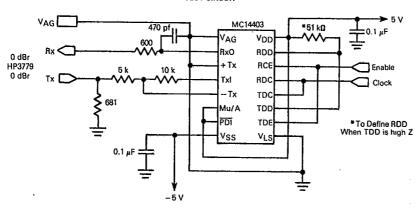

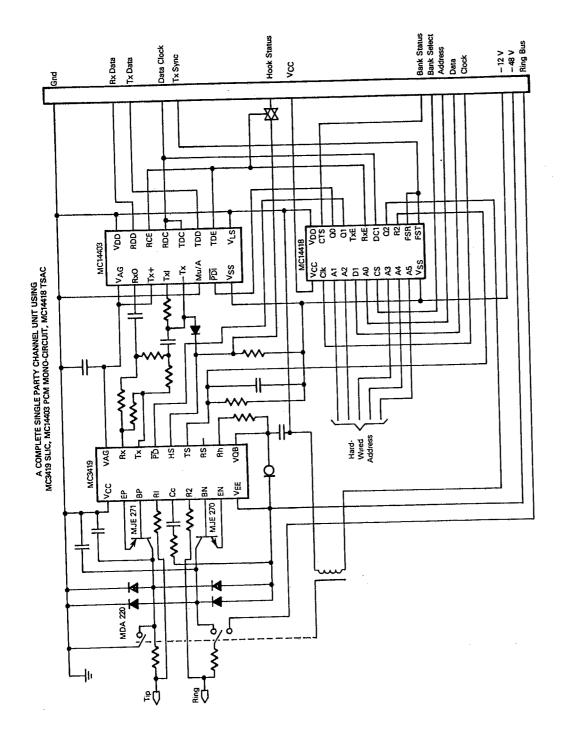

THE BASIC VOICE CHANNEL USING THE MC14400 PCM CODEC/FILTER MONO-CIRCUIT

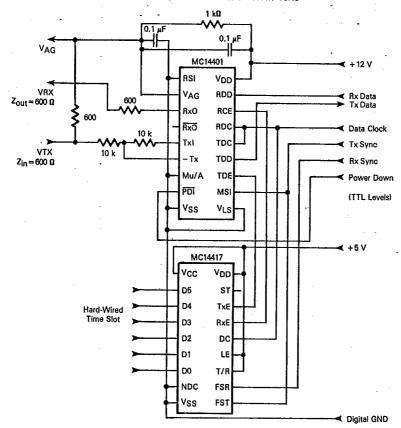

MC14401 PCM MONO-CIRCUIT WITH MC14417 TSAC

T-75-11-09

2

T-75-11-09

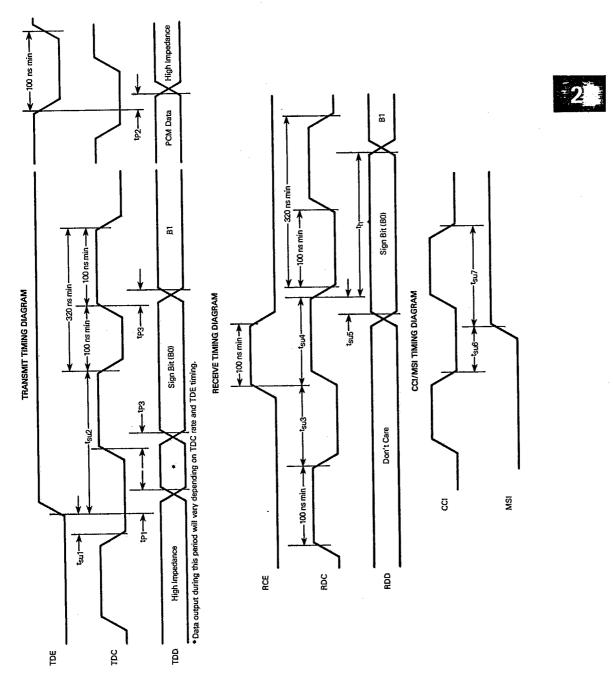

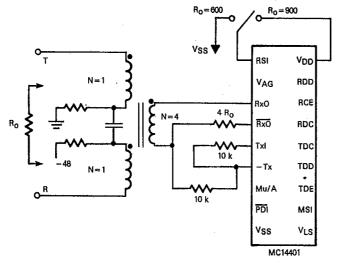

# HYBRID INTERFACES TO MC14401 PCM CODEC FILTER MONO-CIRCUIT

Simplified Transformer Hybrid Using MC14401

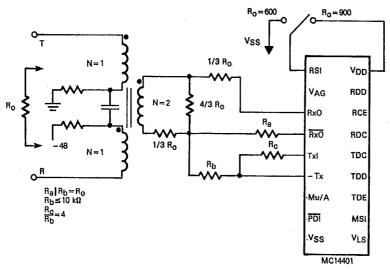

"T" Padded Transformer Hybrid Using MC14401

7-75-11-09

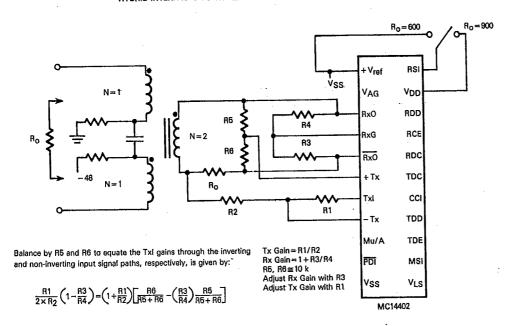

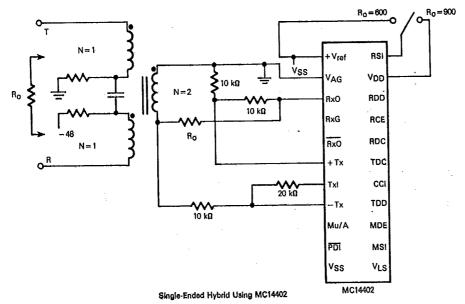

# HYBRID INTERFACES TO THE MC14402 PCM CODEC/FILTER MONO-CIRCUIT

#### Universal Transformer Hybrid Using MC14402

T-75-11-09

NOTE: See single party line drawing for line card details.