#### **Features**

- Parallel E<sup>2</sup>PROM Memory (8 bit word)

- · Gate Array for Logic Design

- Up to 120 I/O

- Low Voltage Operation (2.7 to 5.5 Volts)

- Single Voltage Supply Operation

- Performs Page Write Function

- Manufactured Using Low Power CMOS Technology

- Write or Erase Time: 10 ms Maximum

- Temperature Range from -40°C to 85°C

- · ESD Immunity > 4K Volts

- · High Reliability and Endurance:

- 10,000 Write/Erase Cycles

- 10 Years Data Retention

- Ideal for Portable, Secure Applications Including PCMCIA Cards, Smart Cards, ID Tags, Keys, etc.

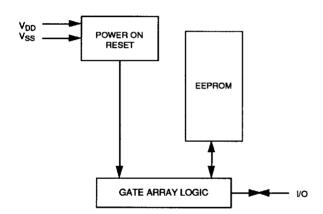

### **Block Diagram**

### Description

The AT88SCXXX provides 1K to 16K bits of E<sup>2</sup>PROM (Electrically Erasable and Programmable Read Only Memory) with 800 to 10K CMOS usable gates for use as personalization, security, and glue logic. The AT88SCXXX is ideal for new portable applications requiring an E<sup>2</sup>PROM with custom logic.

The outputs of the AT88SCXXX can sink and source up to 8 mA. There are up to 120 buffer sites which are configurable as inputs, outputs, bidirectional, CMOS or TTL operation. The device also provides pull-down and pull-up capability for floating signals. The AT88SCXXX is manufactured using low-power CMOS technology and features its own internal high voltage pump for single voltage supply operation. The devices are guaranteed to 10,000 erase/write cycles and 10 years data retention.

# E<sup>2</sup> Logic ICs

Serial / Parallel E<sup>2</sup>PROM with Gate Array

AT88SC150 AT88SC200 AT88SC220 AT88SC250 AT88SC410 AT88SC450 AT88SC8100 AT88SC1610

**Preliminary**

0319B

8-3

1074177 0009194 5TO

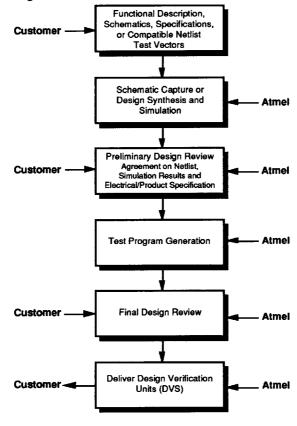

Atmel or the customer can personalize the gate array as described in Figure 1. The customer's design can be accepted in one of three formats:

- · Functional Description

- Schematic

E<sup>2</sup> Logic Family

Compatible Netlist

Compatible netlists can be generated from Mentor™,

Cadence™, Viewlogic™. The personalized devices are

Cadence<sup>™</sup>, Viewlogic<sup>™</sup>. The personalized devices available in wafer, die, or standard packages.

| EEPROM Bits | Number of Usable Gates                                      | Number of I/O                                                                                  | Package Type                                                                                                           |  |  |

|-------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| 1,024       | 5,000                                                       | 100                                                                                            | PQFP/TQFP/PLCC                                                                                                         |  |  |

| 2,048       | 800                                                         | 8 PDIP/SOIC                                                                                    |                                                                                                                        |  |  |

| 2,048       | 2,000                                                       | 64 PQFP/TQFP/PLCC                                                                              |                                                                                                                        |  |  |

| 2,048       | 5,000                                                       | 100                                                                                            | PQFP/TQFP/PLCC                                                                                                         |  |  |

| 4,096       | 1,000                                                       | 24                                                                                             | PDIP/SOIC                                                                                                              |  |  |

| 4,096       | 5,000                                                       | 100                                                                                            | PQFP/TQFP/PLCC                                                                                                         |  |  |

| 8,192       | 10,000                                                      | 128                                                                                            | PQFP/TQFP/PLCC                                                                                                         |  |  |

| 16,384      | 1,000                                                       | 8                                                                                              | PDIP/SOIC                                                                                                              |  |  |

|             | 1,024<br>2,048<br>2,048<br>2,048<br>4,096<br>4,096<br>8,192 | 1,024 5,000   2,048 800   2,048 2,000   2,048 5,000   4,096 1,000   4,096 5,000   8,192 10,000 | 1,024 5,000 100   2,048 800 8   2,048 2,000 64   2,048 5,000 100   4,096 1,000 24   4,096 5,000 100   8,192 10,000 128 |  |  |

Figure 1. AT88SCXXX Design Flow

Cadence, Mentor, and Viewlogic may be trademarks of others.

E<sup>2</sup> Logic ICs

8-4

**■ 1**074177 0009195 437 **■**

## **Absolute Maximum Ratings\***

| Operating Temperature55°C to +125°C                                      |  |  |  |  |

|--------------------------------------------------------------------------|--|--|--|--|

| Storage Temperature65°C to +150°C                                        |  |  |  |  |

| Voltage on Any Pin with Respect to Ground0.6 V to V <sub>CC</sub> +0.6 V |  |  |  |  |

| Maximum Operating Voltage6.1 V                                           |  |  |  |  |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DC** Characteristics

$T_{AMB} = -40$ °C to +85°C,  $V_{CC} = 5 \text{ V} \pm 10$ %,  $V_{SS} = 0 \text{ V}$  (unless otherwise specified)

| Symbol          | Characteristics                                            | Min                   | Тур | Max                   | Unit |

|-----------------|------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| Icc             | Supply Current on V <sub>CC</sub>                          |                       | TBD |                       | mA   |

|                 | $(t_{AMB} = + 25^{\circ}C)$                                |                       |     |                       |      |

|                 | (open output buffers)                                      |                       |     |                       |      |

| ICCP            | Supply Current on V <sub>CC</sub> during E <sup>2</sup> Pf | ROM                   | TBD |                       | mA   |

|                 | Program ( $t_{AMB} = + 25$ °C).                            |                       |     |                       |      |

| VIL             | TTL Input Low Voltage                                      |                       |     | 0.8                   | V    |

| V <sub>IL</sub> | CMOS Input Low Voltage                                     |                       |     | 0.3 x V <sub>DD</sub> | ٧    |

| ViH             | TTL Input High Voltage                                     | 2.0                   |     |                       | V    |

| V <sub>IH</sub> | CMOS Input High Voltage                                    | 0.7 x V <sub>DD</sub> |     |                       | V    |

| V <sub>OL</sub> | Output Low Level (I <sub>OL</sub> = 8 mA)                  |                       |     | 0.4                   | ٧    |

| V <sub>OH</sub> | Output High Level (I <sub>OH</sub> = 8 mA)                 | 0.7 x V <sub>DD</sub> |     |                       | V    |

| ΙL              | I/O Leakage Current                                        | -50                   |     | 50                    | μА   |

#### **Packaging**

All Atmel  $E^2$  logic memory ICs are available in wafer, die, or standard packaging. Back grinding is an option.

# **Packaging Options**

| ackage Type Pin Count         |  |

|-------------------------------|--|

| 44, 52, 64, 80, 100, 120, 128 |  |

| 32, 44, 64, 80, 100, 120, 128 |  |

| 20, 32, 44, 52, 68, 84        |  |

| 8, 16, 24, 32, 40             |  |

| 8, 16, 32                     |  |

| Waffle Packs                  |  |

| Wafer Form                    |  |

|                               |  |

8-5

1074177 0009196 373