# **SIEMENS**

### **Pulse-Width Modulator**

**SLE 4520**

#### MOS IC

### **Features**

- Digital sine synthesis for controlling the speed and torque of three-phase motors

- 2-chip solution (e.g. SAB 8051 with SLE 4520) for easy configuration of a powerful frequency converter.

- Motor frequencies from 0 to 3 kHz selectable at a switching frequency up to 23.4 kHz

- Adaptation to different output stages through programmable dead time.

- Functional and performance features determined by dedicated software.

| Туре        | Ordering Code | Package  |

|-------------|---------------|----------|

| ■ SSLE 4520 | Q671000-H8271 | P-DIP-28 |

Not for new design

### Application

The new pulse-width modulator (PWM) converts an 8-bit data word into a rectangular signal of corresponding width.

Three independently operating channels consisting of a latch, loadable counter and zero detector are used for this purpose. Together with a microcontroller (e.g. SAB 8051) and suitable software, pulses are generated to drive AC converters and inverters (three-phase) with an almost unlimited range of waveforms (sinusoidal, triangular) and phase relationships. An oscillator with clock output, a programmable prescaler to adapt the switching frequency to the requirements of the output stage, an interlocking stage with status flipflop and the ability to program dead times are features that recommend the SLE 4520 for use in frequency converters to drive three-phase induction motors.

Speed control of three-phase motors is easily done when such motors are supplied with a three-phase voltage the *Vff* ratio of which is kept almost constant with variable frequency. For the generation of this three-phase voltage a frequency converter is required, which rectifies and filters the AC supply voltage and, subsequently, reconverts it into an AC voltage of another frequency the aid of a drive circuit and three power half-bridges. In order to avoid high losses the output stages operate in switched mode and are driven by rectangular pulses which increase or decrease in width, depending on the waveform of the sinusoidal function. To produce such pulses with a repetition frequency (switching frequency) up to and above the audible range, a drive block consisting of the SAB 8051 microcontroller and the SLE 4520 PWM as a minimum configuration has proved to be best suited to do the job.

Semiconductor Group

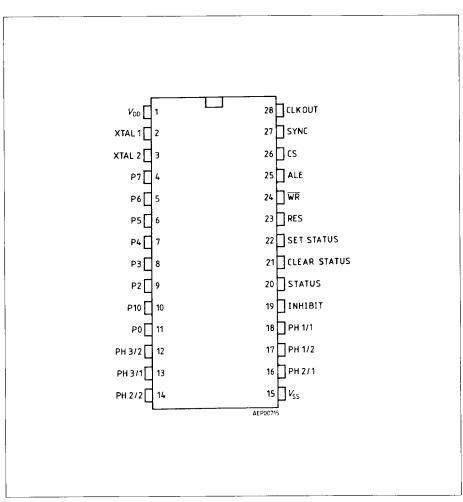

Pin Configuration (top view)

## **SIEMENS**

### **Pin Definitions and Functions**

| Pin      | Symbol                 | Function                                                   |

|----------|------------------------|------------------------------------------------------------|

| 1 2      | V <sub>DD</sub>        | + 5 V pin<br>Crystal pin                                   |

| 3        | XTAL2                  | Crystal pin                                                |

| 4 5      | P7<br>P6               |                                                            |

| 6        | P5                     |                                                            |

| 7        | P4                     | Data bus pins (inputs)                                     |

| 8<br>9   | P3<br>P2               | Sala sas pino (inpato)                                     |

| 10       | P10                    |                                                            |

| 11       | P0                     |                                                            |

| 12       | PH3/2                  | Output phase 3 inverted                                    |

| 13       | PH3/1                  | Output phase 3 normal (active low)                         |

| 14       | PH2/2                  | Output phase 2 inverted                                    |

| 15       | Vss .                  | Ground                                                     |

| 16       | PH2/1                  | Output phase 2 normal (active low)                         |

| 17<br>18 | PH1/2<br>PH1/1         | Output phase 1 inverted Output phase 1 normal (active low) |

| -        |                        | <u> </u>                                                   |

| 19       | INHIBIT                | Inhibit (active high) sets all phase outputs to high       |

| 20       | STATUS<br>CLEAR STATUS | Output of status flipflop Resets status flipflop           |

| 21<br>22 | SET STATUS             | Sets status flipflop                                       |

| 23       | RES                    | Chip reset                                                 |

| 24       | WR .                   | Input for WR pulse from microcontroller                    |

| 25       | ALE                    | Input for ALE clock from microcontroller                   |

| 26       | cs                     | Chip select                                                |

| 27       | SYNC                   | Input for trigger pulse from microcontroller               |

| 28       | CLK OUT                | Output crystal frequency for microcontroller               |

**SLE 4520**

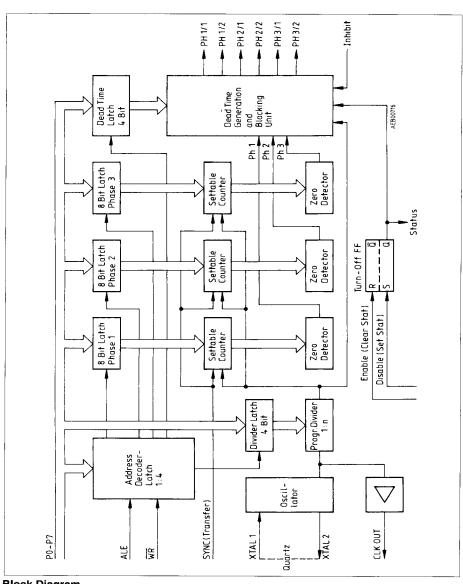

**Block Diagram**

Semiconductor Group

### **Functional Description**

The following description deals with the combination of the SAB 8051 microcontroller and the SLE 4520 PWM and a program developed by Siemens. Other hardware combinations are possible as well.

An on-chip oscillator directly feeds the programmable prescaler and has a buffered output for the connected microcontroller. The interface to the microcontroller has a width of 8 bits.

Data from the SAB 8051 microcontroller to the SLE 4520 PWM are transferred via the data bus P0 using the control signals ALE and WR. In the PWM component three 8-bit registers for the three phases and two 4-bit registers for dead time and divider ratio respectively as well as an address decoder latch to buffer the relevant addresses are connected to the internal data bus of the SLE 4520 (see Block Diagram).

Addresses are as follows:

| Address | Register                   |  |  |

|---------|----------------------------|--|--|

| 00      | 8-bit register for phase 1 |  |  |

| 01      | 8-bit register for phase 2 |  |  |

| 02      | 8-bit register for phase 3 |  |  |

| 03      | dead time control register |  |  |

| 04      | divider control register   |  |  |

The last two registers have to be written only once when being initialized. In the case of a controller output the above-mentioned 3-bit address is latched and decoded with the falling edge of the ALE clock. With the rising edge of the WR signal data are loaded from the bus into the registers of the pulse-width modulator.

The required divider ratio for the production of low switching frequencies at a simultaneously high operating frequency of the microcontroller is set by the divider control register. The divider control register is best loaded with an adequate value in the starting routine.

Allocation of value and divider ratio is shown in table 1:

Table 1

Allocation of Value in the Divider Register to the Divider Ratio by which the SLE 4520 Operating Frequency is Selected

| Value | Divider Ratio<br>Counter | Divider Ratio<br>Delay Clock |  |  |

|-------|--------------------------|------------------------------|--|--|

| 0     | 1:4                      | 1:4                          |  |  |

| 1     | 1:6                      | 1:6                          |  |  |

| 2     | 1:8                      | 1:4                          |  |  |

| 3     | 1:12                     | 1:6                          |  |  |

| 4     | 1:16                     | 1:4                          |  |  |

| 5     | 1:24                     | 1:6                          |  |  |

| 6     | 1:32                     | 1:4                          |  |  |

| 7     | 1:48                     | 1:6                          |  |  |

Semiconductor Group

After the ratio has been determined, the length of the switching frequency cycle should be selected in such a way that the maximum pulse width is just reached. This means that with a PWM counter clock of, e.g. 1 MHz (oscillator frequency of 12 MHz, divider ratio 1:12) and a table value of 127 (7 bits) the counter reaches zero after 128  $\mu$ s (switching frequency cycle 128  $\mu$ s).

**Table 2** gives a number of useful allocations of counter frequency and switching frequency for the SAB 8051 (12-MHz clock).

Table 2

Allocation of Counter Frequency and Switching Frequency of SAB 8051

| Divider Ratio | Counter<br>Frequency | Operating Time<br>Timer 0 | Switching<br>Frequency | Resolution |  |

|---------------|----------------------|---------------------------|------------------------|------------|--|

| 1:6           | 2 MHz                | 64 μs                     | 15.6 kHz               | 7 bit      |  |

| 1:6           | 2 MHz                | 128 μs                    | 7.8 kHz                | 8 bit      |  |

| 1:12          | 1 MHz                | 128 µs                    | 7.8 kHz                | 7 bit      |  |

| 1:12          | 1 MHz                | 256 μs                    | 3.9 kHz                | 8 bit      |  |

| 1:24          | 500 kHz              | 256 μs                    | 3.9 kHz                | 7 bit      |  |

| 1:24          | 500 kHz              | 2 × 256 μs                | 1.95 kHz               | 8 bit      |  |

| 1:48          | 250 kHz              | 2 × 256 μs                | 1.95 kHz               | 7 bit      |  |

| 1:48          | 250 kHz              | 4 × 256 μs                | 975 Hz                 | 8 bit      |  |

|               | 1                    |                           | 1                      |            |  |

### Converting a Data Word into a Pulse Width

Pulse generation in the three processing channels is done by a presettable 8-bit down-counter and a zero detector (NOR gate) which is connected to the eight counter outputs. With the transfer pulse from the microcontroller (width 1 instruction cycle), whose repetition rate determines the length of the switching frequency, the presettable counter is loaded with the contents of the appropriate register and 0 appears at the zero detector's output (provided the register does not contain 00H).

This 0 digit enables the counter and starts it running down. When zero is reached the pulse ends and the counter is stopped until the next transfer pulse arrives. The crystal frequency multiplied by the divider ratio serves as clock frequency for the PWM counter.

# Dead-time Control Register and Dead-Time Setting in Order to Avoid Overlapping Switching Operations

The dead time between the drive pulses for the two transistors of a half-bridge must consider the storage times of the bipolar driver and the power transistors, otherwise dangerous overlapping switching operations might occur. In the pulse-width modulator the dead time is obtained by linking the pulse-width modulated signal source with a delay signal. The delay is obtained by passing the source signal through a 15-bit shift register with 15 outputs.

The shift pulse is either  $f_{\text{CRYSTAL}}$  or  $f_{\text{CRYSTAL}}$ , depending on the values in the divider control register. 6 4

Semiconductor Group

By writing a value between 0 and  $0F_H$  into the appropriate control register 16 dead times are presettable (incl. zero dead time).

The dead time depends on the crystal frequency and the preset divider ratio. Programmable dead times for a 12-MHz crystal frequency are shown in **table 3**.

Table 3

Dead Times Presettable in the Dead Time Control Register

Using Divider Ratios of 1:4 and 1:6

| Word in Dead Time<br>Memory | Divider Ratio 1:4<br>Dead Time (μs) | Divider Ratio 1:6<br>Dead Time (μs) |  |

|-----------------------------|-------------------------------------|-------------------------------------|--|

| 0                           | 0                                   | 0                                   |  |

| 1                           | 0.33                                | 0.5                                 |  |

| 2                           | 0.66                                | 1                                   |  |

| 3                           | 1.0                                 | 1.5                                 |  |

| 4                           | 1.33                                | 2                                   |  |

| 5                           | 1.66                                | 2.5                                 |  |

| 6                           | 2.0                                 | 3                                   |  |

| 7                           | 2.33                                | 3.5                                 |  |

| 8                           | 2.66                                | 4                                   |  |

| 9                           | 3.0                                 | 4.5                                 |  |

| 10                          | 3.33                                | 5                                   |  |

| 11                          | 3.66                                | 5.5                                 |  |

| 12                          | 4.0                                 | 6                                   |  |

| 13                          | 4.33                                | 6.5                                 |  |

| 14                          | 4.66                                | 7                                   |  |

| 15                          | 5.0                                 | 7.5                                 |  |

### The Interface to the Power Circuit is Provided by Outputs PH1/1 to PH3/2

Without dead time PH1/2 is inverted to PH1/1, PH2/2 to PH2/1 and PH3/2 to PH3/1. The active switching state is low.

With a programmed dead time the negative edges of the output signal are shifted to the right by the dead time.

The outputs are capable of directly driving TTL devices or optocouplers for voltage isolation of drive block and power circuit with a current up to 20 mA.

### Static or Dynamic Interlocking of Outputs is Possible

Within the duration of the inhibit signal (pin 19) all six outputs can be set to high level. In case the outputs are connected to optocouplers the light emitting diodes are currentless and all six individual transistors of the power circuit are blocked. This option is particularly necessary when switching on the drive block, as proper pulses at the pulse-width modulator output are only available after the oscillator output has been built up and the initialization routine has been executed.

As the SAB 8051 sets the port outputs to high when switched on, only one port pin of the microcontroller has to be connected to inhibit. At the end of the initialization routine this port pin is set to low.

Semiconductor Group

Another way of inhibiting the outputs (hold function) is to apply a high pulse to the "Set" input (pin 22) of the status flipflop. This inhibit state is indicated by the "Status" output (pin 20) and can be used to indicate or inform the microcontroller (active high; used, for example, in the event of power failure, short circuit, overtemperature etc.).

The status flipflop is cleared by a high pulse at the "Clear Status" input (pin 21).

### **Features**

- Generation of three pairs of pulse-width modulated rectangular pulses (phase angle between one phase and the next is, for example, 120°) to drive six individual transistors of an inverter power block.

- Programmable dead time to reliably drive both power switches of a half-bridge from 0 to  $15 \times \frac{6}{f_{\text{crystal}}}$  or  $15 \times \frac{4}{f_{\text{crystal}}}$  in 15 steps.

It is the negative edge which is in each case delayed because the output signal is active low.

- Programmable divider in the pulse-width modulator to obtain low switching frequencies (for output stages with thyristors, GTOs, and bipolar transistors) and to simultaneously operate the microcontroller at higher crystal frequencies.

- Direct drive of an optocoupler interface to isolate control and load circuits (I<sub>sink</sub> = 20 mA maximum).

- All six outputs of the SLE 4520 are set to high level either dynamically by an inhibit signal (INHIBIT) or statically by an R-S flipflop (SET STATUS). Thus blocking of all six individual transistors of the power circuit is possible.

- DC braking by selecting different, fixed duty cycles in the three output pairs.

- Direction of rotation is software-reversed by changing between two phases.

- Sine-wave frequency range about 0 to > 2600 Hz.

- Switching frequency range < 1 to > 20 kHz. 8-bit resolution of the desired sine-wave function with a switching frequency of  $\frac{f_{\text{crystal}}}{6 \times 2^8}$  or 7 bits with a switching frequency of  $\frac{f_{\text{crystal}}}{6 \times 2^7}$  ( $f_{\text{crystal}} = 12$  MHz and resolution = 7 bits result in a 15.6-kHz switching frequency).

- Smallest increment of the pulse-width is 333 ns with  $f_{\text{crystal}} = 12 \text{ MHz}$  and divider ratio 1:4.

- Changing the switching frequency cycle in 1-μs steps allows the transition from one sine-wave frequency stage to the next quasi continuously (virtually analog).

- Evaluating the bit pattern at one port of the microcontroller enables many (256) different speed-control programs to be selected.

- Low current consumption of the pulse-width modulator due to ACMOS technology.

°C

85

### **SIEMENS**

### **Absolute Maximum Ratings**

| Parameter                                             | Symbol                 | Limit Values |      |                       | Unit     |

|-------------------------------------------------------|------------------------|--------------|------|-----------------------|----------|

|                                                       |                        | min.         | typ. | max.                  |          |

| Supply voltage                                        | $V_{DD}$               | - 0.3        |      | 6                     | ٧        |

| Input voltage                                         | Vi                     | - 0.3        |      | V <sub>DD</sub> + 0.3 | ٧        |

| Storage temperature                                   | Tstg                   | - 50         |      | 125                   | ,C       |

| Total power dissipation Power dissipation per output  | P <sub>tot</sub><br>PQ |              |      | 500<br>50             | mW<br>mW |

| Operating Range                                       |                        |              |      |                       |          |

| Supply voltage Supply current (outputs not connected) | Vcc<br>IDD             | 4.5          | 5    | 5.5<br>15             | V<br>mA  |

| Operating frequency                                   | fclk                   |              |      | 12                    | MHz      |

- 40

$T_{\mathsf{A}}$

# Ambient temperature DC Characteristics

$T_A = 25\,^{\circ}\text{C}$

| Parameter             | Symbol          | Limit Values          |           |          | Unit | Test                           |

|-----------------------|-----------------|-----------------------|-----------|----------|------|--------------------------------|

|                       |                 | min.                  | typ.      | max.     |      | Condition                      |

| All Input Signals Exc | cept XTAL2      |                       |           |          |      |                                |

| H-input voltage       | ViH             | 2.2                   |           | $V_{DD}$ | V    |                                |

| L-input voltage       | $V_{IL}$        | 0                     |           | 0.8      | V    |                                |

| Input capacitance     | $C_1$           |                       |           | 10       | pF   |                                |

| Input current         | I IL            |                       |           | 1        | μA   |                                |

| Input Signal XTAL2    |                 | 1                     |           |          | 1    |                                |

| H-input voltage       | Vıн             | 4.0                   |           |          | V    |                                |

| L-input voltage       | VIL             | 0                     |           | 0.3      | V    |                                |

| Input capacitance     | Cı              |                       |           | 10       | pF   |                                |

| Input current         | IIL             |                       |           | 1        | μΑ   |                                |

| Output Signals STA    | TUS, CLK OL     | JT                    |           |          |      |                                |

| H-output voltage      | V <sub>OH</sub> | V <sub>DD</sub> - 0.8 |           |          | V    | $I_{Q} = 0.5  \text{m/s}$      |

| L-output voltage      | $V_{QL}$        |                       |           | 0.4      | V    | $I_{\Omega} = 1.6  \text{m/s}$ |

| Output Signals PH 1   | /1, PH 1/2, PI  | H 2/2, PH 3/          | 1, PH 3/2 | 2        |      |                                |

| L-output voltage      | $V_{QL}$        |                       |           | 1        | V    | Ia = 20 mA                     |

| H-output voltage      | $V_{QH}$        | $V_{DD} - 0.8 V$      |           |          | V    | $I_Q = 1 \text{ mA}$           |

Semiconductor Group

### **AC Characteristics**

| Parameter                                | Symbol        | Lin     | Unit         |    |  |

|------------------------------------------|---------------|---------|--------------|----|--|

|                                          |               | min.    | max.         |    |  |

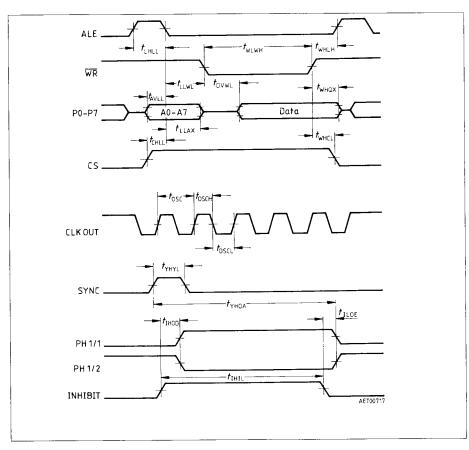

| ALE pulse width                          | 1 LHLL        | 100     |              | ns |  |

| Address setup to ALE                     | f AVLL        | 30      |              | ns |  |

| Address hold after ALE                   | f LLAX        | 30      |              | ns |  |

| WRN pulse width                          | 1 WLWH        | 200     |              | ns |  |

| WRN high to ALE high                     | 1 WHLH        | 50      |              | ns |  |

| Data setup after WRN low                 | 1 DVWL        |         | 20           | ns |  |

| ALE low to WRN low                       | 1 LLWL        | 100     |              | ns |  |

| Data hold after WRN 1)                   | t whax        | 30      |              | ns |  |

| Oscillator period                        | tosc          | 83      |              | ns |  |

| High time                                | t osch        | 35      |              | ns |  |

| Low time                                 | f OSCL        | 35      |              | ns |  |

| SYNC pulse width                         | 1 YHYL        | 200     |              | ns |  |

| INHIBIT low to output enable             | t ILOE        |         | 100          | ns |  |

| Delay between SYNC high to output active | f YHOA        | 4 tosc  | 97 tosc + 20 | ns |  |

| Chip select setup to ALE low             | t CHLL        | 20      |              | ns |  |

| Chip select hold after WRN high          | 1 WHCL        | 30      |              | ns |  |

| Reset pulse width                        | f RHRL        | 12 tosc |              | ns |  |

| Set status pulse width                   | 1 SHSL        | 200     |              | ns |  |

| Clear status pulse width                 | 1 CHCL        | 200     |              | ns |  |

| INHIBIT high to output disable           | t ihod        |         | 100          | ns |  |

| Set status high to output disable        | t shod        |         | 100          | ns |  |

| Clear status high to output enable       | t CHOD        |         | 100          | ns |  |

| Set status pulse length                  | <i>t</i> shth | 100     |              | ns |  |

| Clear status pulse length                | 1 CHTL        | 100     |              | ns |  |

| Inhibit pulse length                     | t IHIL        | 100     |              | ns |  |

Semiconductor Group

<sup>1)</sup> If t which is less than 2 t osc + 20 ns, then t which is 50 ns

**Pulse Diagrams**