# 6500 Public Key Processor Data Sheet

Hifn<sup>TM</sup> supplies the Internet's most important raw materials for the creation of intelligent and secure networks: compression, encryption, and flow classification. This is central to the growth of the Internet, helping to make electronic mail, web browsing, Internet shopping and multimedia communications better, faster and more secure.

750 University Avenue Los Gatos, CA 95032 info@hifn.com http://www.hifn.com Tel: 408-399-3500

Fax: 408-399-3501

For technical support, please contact your local Hifn sales office, representative or distributor. For locations check: www.hifn.com.

#### Disclaimer

Hifn reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

Hifn warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with Hifn's standard warranty. Testing and other quality control techniques are utilized to the extent Hifn deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

HIFN SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of Hifn products in such critical applications is understood to be fully at the risk of the customer. Questions concerning potential risk applications should be directed to Hifn through a local sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

Hifn does not warrant that its products are free from infringement of any patents, copyrights or other proprietary rights of third parties. In no event shall Hifn be liable for any special, incidental or consequential damages arising from infringement or alleged infringement of any patents, copyrights or other third party intellectual property rights.

"Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals," must be validated for each customer application by customer's technical experts.

The use of this product in stateful compression protocols (for example, PPP or multi-history applications) with certain configurations may require a license from Motorola. In such cases, a license agreement for the right to use Motorola patents may be obtained through Hifn or directly from Motorola.

DS-0016-02 (05/01) ©2001 by Hi/fn®, Inc., including one or more U.S. patents No.: 4,701,745, 5,003,307, 5,016,009, 5,126,739, 5,146,221, 5,414,425, 5,414,850, 5,463,390, 5,506,580, 5,532,694. Other patents pending. Hi/fn and LZS® are registered trademarks of Hi/fn, Inc. Hifn is a trademark of Hi/fn, Inc. All other trademarks are the property of their respective holders.

This product must be exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law prohibited.

# **Table of Contents**

| 1 | Ove  | rview                                       | 7  |

|---|------|---------------------------------------------|----|

|   | 1.1  | Scope of Document                           | 7  |

|   | 1.2  | Features                                    | 7  |

|   | 1.3  | Supported Network Security Protocols        | 7  |

|   | 1.4  | System block diagrams                       | 8  |

| 2 | Arcl | hitecture                                   | 10 |

|   | 2.1  | Detailed block diagram                      | 10 |

|   | 2.2  | Operation                                   | 10 |

|   | 2.3  | Functional Units                            | 11 |

| 3 | Men  | nory Map and Addressing                     | 14 |

|   | 3.1  | Introduction                                | 14 |

|   | 3.2  | Addressing the Data Registers               | 16 |

|   | 3.3  | Addressing the Length Registers             | 18 |

|   | 3.4  | Addressing the Random Number FIFO           | 19 |

|   | 3.5  | Addressing the Instruction Memory           | 19 |

|   | 3.6  | Addressing the Control and Status Registers | 20 |

| 4 | Sign | nals and I/O                                | 21 |

|   | 4.1  | Clocks                                      | 21 |

|   | 4.2  | Direct-Access I/O                           | 21 |

|   | 4.3  | PCI I/O                                     | 24 |

| 5 | Reg  | ister Descriptions                          | 28 |

|   | 5.1  | Command Register                            | 28 |

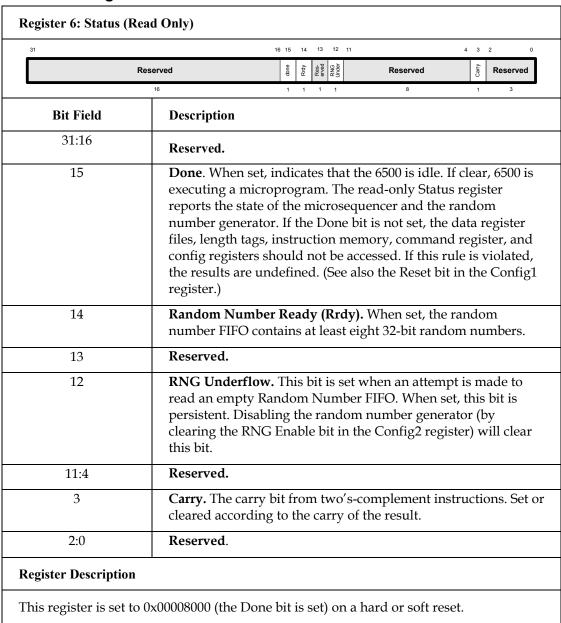

|   | 5.2  | Status Register                             | 29 |

|   | 5.3  | Interrupt Enable Register                   | 30 |

|   | 5.4  | Rngconfig Register                          | 31 |

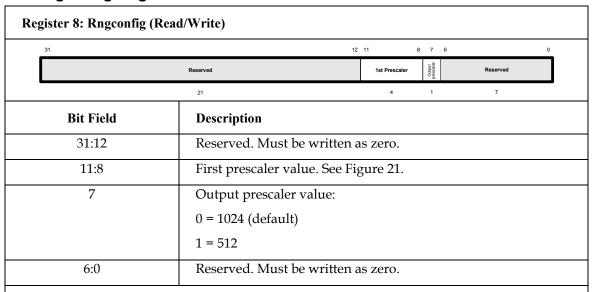

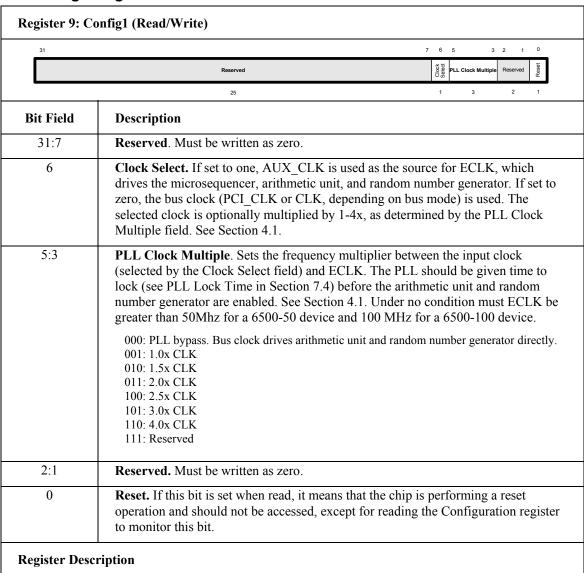

|   | 5.5  | Config1 Register                            | 32 |

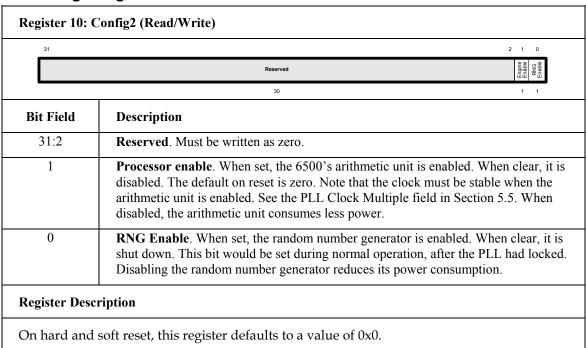

|   | 5.6  | Config2 Register                            | 33 |

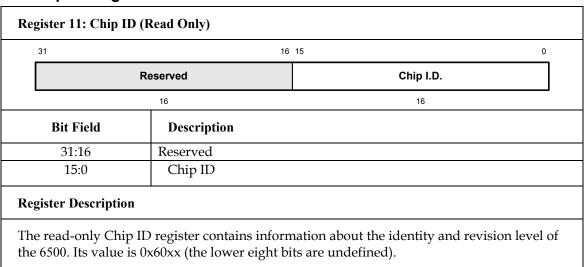

|   | 5.7  | Chip ID Register                            | 33 |

| 6 | Con  | nmands and Programming                      | 34 |

|   | 6.1  | Introduction                                | 34 |

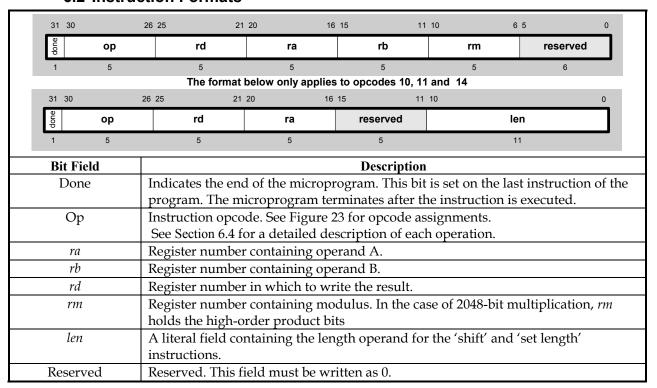

|   | 6.2  | Instruction Formats                         | 35 |

|   | 6.3  | Data Format                                    | 36 |

|---|------|------------------------------------------------|----|

|   | 6.4  | Instruction Descriptions                       | 37 |

| 7 | Spec | rifications                                    | 41 |

|   | 7.1  | Absolute Maximum Ratings                       | 41 |

|   | 7.2  | Recommended Operating Conditions               | 41 |

|   | 7.3  | DC Specifications                              | 42 |

|   | 7.4  | AC Specifications                              | 43 |

|   | 7.5  | Direct Access Pin Configuration, by Pin Number | 46 |

|   | 7.6  | Direct Access Pin Configuration, Alphabetical  | 47 |

|   | 7.7  | PCI Pin Configuration, by Pin Number           | 48 |

|   | 7.8  | PCI Pin Configuration, Alphabetical            | 49 |

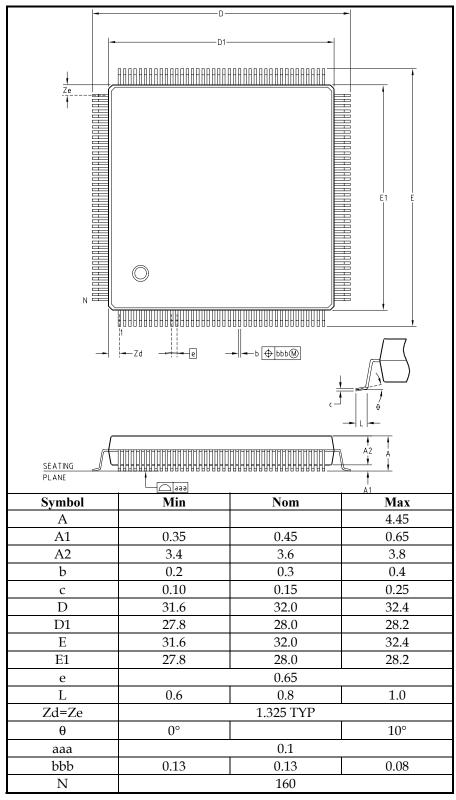

|   | 79   | Package Dimensions                             | 51 |

# **List of Figures**

| Figure 1. IKE Performance                                     | 8  |

|---------------------------------------------------------------|----|

| Figure 2. Performance vs. algorithm and key size              | 8  |

| Figure 3. System block diagram, PCI mode                      | 9  |

| Figure 4. System block diagram, Direct-Access mode            | 9  |

| Figure 5. Internal block diagram                              | 10 |

| Figure 6. Memory map                                          | 15 |

| Figure 7. Address format for the data registers               | 16 |

| Figure 8. Starting address for each data register, by window  | 16 |

| Figure 9. Address of each length register                     | 18 |

| Figure 10. Address of each instruction register               | 19 |

| Figure 11. Address map for status and configuration registers | 20 |

| Figure 12. ECLK generation                                    | 21 |

| Figure 13. Direct-access signals                              | 22 |

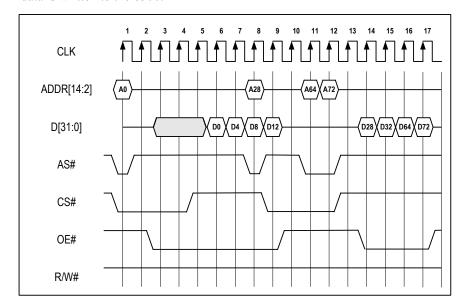

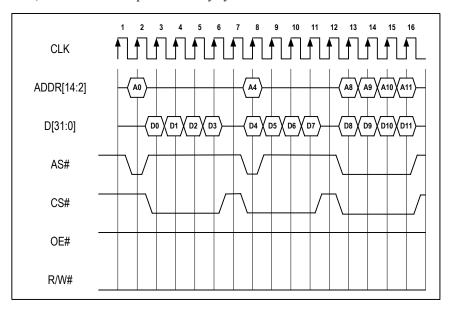

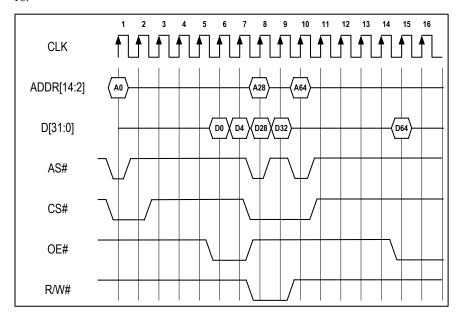

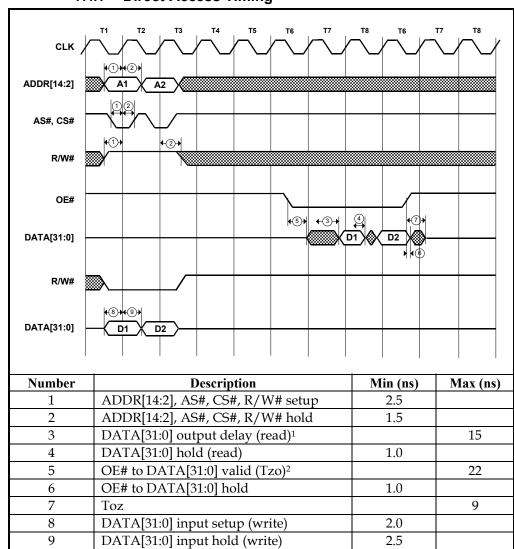

| Figure 14. Direct-access read timing                          | 23 |

| Figure 15. Direct-access write timing                         | 23 |

| Figure 16. Bus turnaround                                     | 24 |

| Figure 17. PCI signal summary                                 | 25 |

| Figure 18. EEPROM address map                                 | 26 |

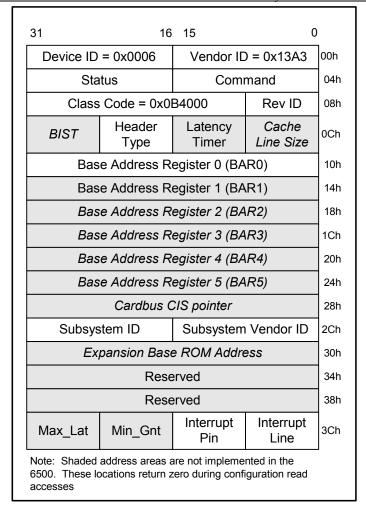

| Figure 19. PCI configuration space map                        | 27 |

| Figure 20. Default PCI Configuration Register Values          | 27 |

| Figure 21. Decoding of the 'first prescaler' field            | 31 |

| Figure 22. Instruction Formats                                | 35 |

| Figure 23. Instruction opcodes                                | 35 |

| Figure 24. Recommended operating conditions                   | 41 |

| Figure 25. DC electrical characteristics                      | 42 |

| Figure 26. Test conditions                                    | 42 |

| Figure 27. Direct-access specifications                   | 43 |

|-----------------------------------------------------------|----|

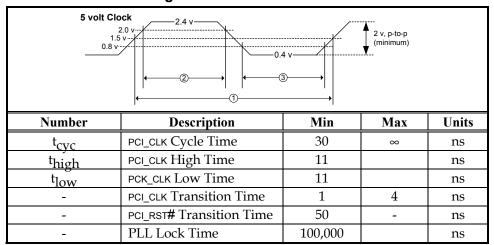

| Figure 28. PCI clock and reset parameters                 | 44 |

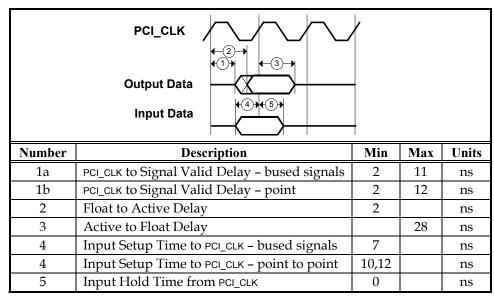

| Figure 29. PCI timing parameters                          | 44 |

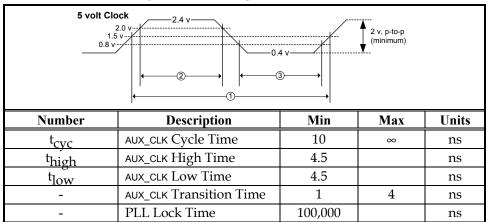

| Figure 30. Auxiliary clock parameters                     | 45 |

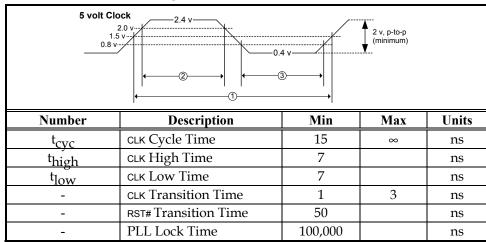

| Figure 31. Bus clock parameters                           | 45 |

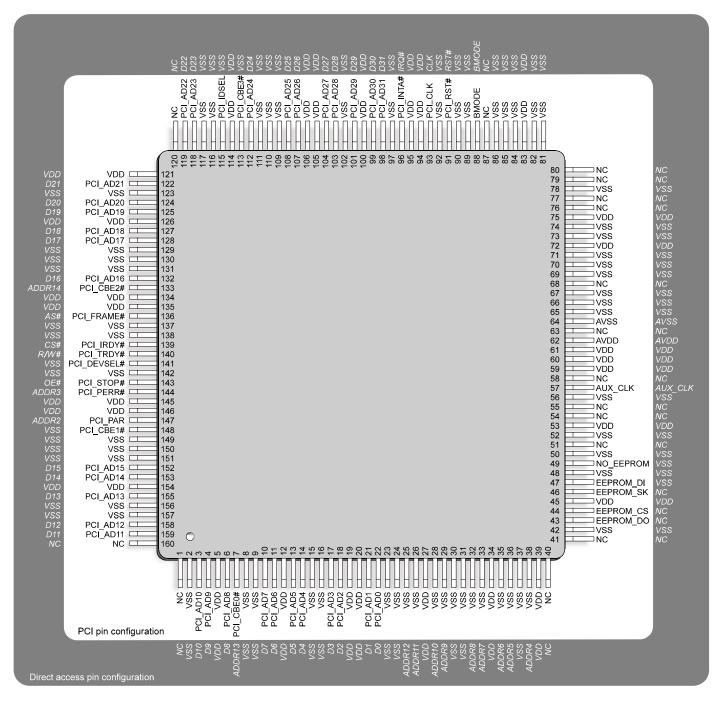

| Figure 32. Direct access pin configuration, by pin number | 46 |

| Figure 33. Direct access pin configuration, alphabetical  | 47 |

| Figure 34. PCI pin configuration, by pin number           | 48 |

| Figure 35. PCI pin configuration, alphabetical            | 49 |

| Figure 36. 160-pin HQFP configuration                     | 50 |

| Figure 37. Package dimensions (in millimeters)            | 51 |

# **Overview**

# 1.1 Scope of Document

Hifn's 6500 is a hardware accelerator for public-key cryptography applications such as virtual private networks, secure Web access, secure electronic commerce, and digital certificate services. By implementing 1024-bit modular arithmetic in hardware, the 6500 outperforms even the fastest general-purpose processors, while using only a fraction of the board space and power.

The 6500's modular arithmetic unit is compatible with a variety of public-key algorithms, including DSA, Diffie-Hellman key exchange, and Rivest, Shamir, Adleman (RSA).

The chip also includes a hardware-based true-random-number generator. This document should be used by engineering developers who are responsible for implementing the 6500 Public Key Processor.

### 1.2 Features

The following features are supported:

- 1024-bit modular arithmetic processor with support for 2048-bit operations

- 200 private-key 1024-bit RSA computations/second

- More than 300 Internet Key Exchange (IKE) connections/sec

- More than 115 IKE RSA-based X.509 authenticated connections/sec

- True random number generator

- Universal PCI (3V or 5V) and direct 32-bit slave interfaces

- Supports large data bursts

- 160-pin quad flat pack; 3 volt operation

- Internal PLL clock multiplier for single-clock operation

# 1.3 Supported Network Security Protocols

The 6500 processor supports the public-key cryptographic algorithm requirements of the following network security protocols:

- Internet Protocol Security (IPSec)

- Secure Electronic Transaction (SET)

- Secure Socket Layer/Transport Layer Security (SSL/TLS)

- Public-Key Infrastructure (PKIX)

| Part Number  | Speed, MHz | Package      |  |

|--------------|------------|--------------|--|

| 6500-50 PH8  | 50         | 160-pin HQFP |  |

| 6500-100 PH8 | 100        | 160-pin HQFP |  |

### **Performance**

| IKE Handshake                                | 6500               |

|----------------------------------------------|--------------------|

| (180-bit exponent)                           | (100 MHz CLK)      |

| Handshake: Two 1024-bit Diffie-Hellman       | >300 connections/s |

| operations                                   |                    |

| Handshake with authentication: Two 1024-bit  | >115 connections/s |

| Diffie-Hellman operations, 1 RSA sign, 2 RSA |                    |

| verifies                                     |                    |

Figure 1. IKE Performance

| Operation                        | Time to Complete vs. Key Size |          |          |          |  |

|----------------------------------|-------------------------------|----------|----------|----------|--|

|                                  | 2048                          | 1024     | 768      | 512      |  |

| RSA Private Key                  | 18.3 ms                       | 5.24 ms  | 3.19 ms  | 1.65 ms  |  |

| RSA Public Key (exp. = 3)        | 0.32 ms                       | 0.018 ms | 0.015 ms | 0.011 ms |  |

| Diffie-Hellman (exp. = 180 bits) |                               | 1.60 ms  | 1.25 ms  | 0.46 ms  |  |

| Diffie-Hellman (exp. = key size) |                               | 9.15 ms  | 7.18 ms  | 2.61 ms  |  |

| DSA Sign                         |                               | 1.83 ms  | 1.52 ms  | 1.22 ms  |  |

| DSA Verify                       |                               | 3.26 ms  | 2.65 ms  | 2.03 ms  |  |

#### Notes:

- 1 Performance numbers assume a uniform distribution of ones and zeros in the exponent. Actual performance varies with the Hamming weight of the exponent.

- 2 Because FIPS 186, the Digital Signature Standard, specifies a maximum modulus of 1,024 bits, DSA values are not given for 2,048 bits.

Figure 2. Performance vs. algorithm and key size

# 1.4 System block diagrams

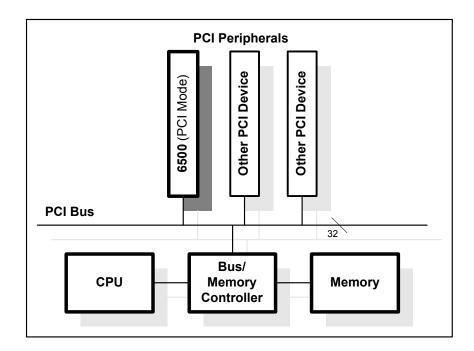

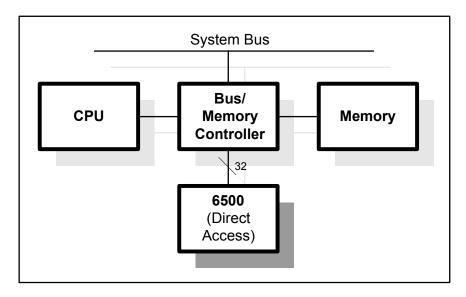

The 6500 can be configured to use either a PCI interface or a direct-access interface. The PCI interface gives the system designer the option of creating a 6500-based PCI card for host systems with available PCI slots, making the 6500 an optional or upgrade feature for the product line. In new host system designs, the 6500 can be soldered directly to the host's main board, in which case either interface may be used.

Figure 3. System block diagram, PCI mode

Figure 4. System block diagram, Direct-Access mode

# 2 Architecture

# 2.1 Detailed block diagram

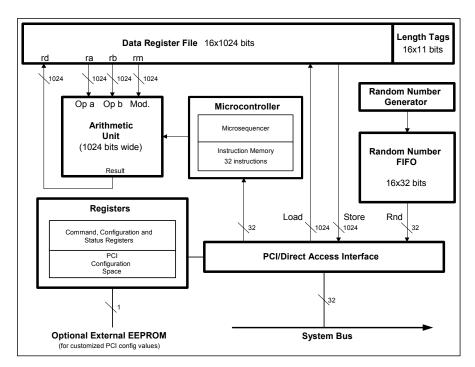

Figure 5. Internal block diagram

# 2.2 Operation

The 6500 implements modular arithmetic and random number functions, leaving the other tasks involved in public-key encryption (primarily control protocols) to the local host's general-purpose processor. This simplifies operation on both sides of the interface. Adding the 6500 to an existing system requires that only a handful of function calls be rewritten on the host side. Programming the 6500 itself is simple, and a typical application will use only a few 6500 instructions.

(For the purposes of this document, the "host processor" is whatever processor sends commands to the 6500, and is not necessarily the main processor of the entire system.)

The host loads the 6500's registers, then launches a command, relinquishing the bus. The 6500 will interrupt the host when the command is complete (alternatively, the host can poll a status register). When the command is complete, the host reads the results.

The basic operation of the 6500 is as follows:

#### Chip initialization

Set modes and enable the desired interrupts by writing to the 6500's internal registers.

### Program initialization

Load the desired sequence(s) of arithmetic operations (microprograms) to instruction memory.

#### **Program operation**

- 3. Write the operands to the data register file and the operand lengths to the length tags.

- 4. Launch a command by writing a microprogram starting address to the Command register.

- 5. Wait for completion (via polling or interrupts). This is indicated by the Done bit in the Status register. The instruction memory, data registers, and length tags must not be accessed during operation.

- 6. Read the result from the data register file.

- Repeat (go to step 3).

### 2.3 Functional Units

### 2.3.1 Data Register File

The general-purpose data register file consists of sixteen 1024-bit registers, named r0 through r15. Each register also has an associated *length tag*, indicating the length of the data in the register. Both the registers and the length tags are memory-mapped to a block of consecutive addresses to facilitate block data transfers to and from the host.

The *length tags* are associated with the data register file. The sixteen 11-bit length tags give the size (in bits) of the data in each of the data registers. In general, the shorter the operands, the more quickly the operation completes.

The contents of the register file and length tags are unchanged on a hard or soft reset. They are undefined at power-up.

### 2.3.2 Other Registers

In addition to the data register file, the 6500 has a set of configuration and status registers. These are described in Section 5.

### 2.3.3 Arithmetic Unit

The *arithmetic unit* operates on integers of up to 1,024 bits in width. It reads operands from the data register file, operates on them, and writes the results back to the data register file. Operations take the form:

$rd = ra \operatorname{op} rb \operatorname{mod} rm$ ,

where rd, ra, rb, and rm are all data registers, and op is the operation specified by the opcode.

The arithmetic unit has the following modular arithmetic functions: exponentiation, multiplication, reduction, addition, and subtraction. In addition, it performs non-modular two's-complement addition, subtraction, and multiplication, logical left and right shifts, increment, and decrement functions. It can set the length tag of a general-purpose register to any 11-bit value to initialize the length of an operand or override the length of a result.

The arithmetic unit also has a carry flag that is set when there is a carry out of bit 1023 for non-modular addition or when there is a borrow for non-modular subtraction.

On both hard and soft reset, the arithmetic unit is halted and disabled. It must be re-enabled (by setting the Processor Enable bit in the Config2 register) before commands can be executed.

#### 2.3.4 Microcontroller

The *microcontroller* is the 6500's instruction sequencer. It controls the operation of the arithmetic unit. Its instruction set consists solely of arithmetic operations. The lone control operation is the *Done* bit in the instruction word, which tells the microcontroller to stop execution after the current instruction.

The microcontroller is itself divided into two sections: the *microsequencer* and the *instruction memory*. The microsequencer contains the control logic, while the instruction memory consists of thirty-two 32-bit instruction words.

See Section 6 for more information on 6500 programming.

On both hard and soft reset, the microcontroller is halted and disabled. It must be re-enabled (by setting the Processor Enable bit in the Config2 register) before commands can be executed.

### 2.3.5 Random Number Generator

The 6500 also contains a hardware random number generator based on internal free-running oscillators whose frequencies drift relative to each other and to the 6500's internal clock. The phase relation of these signals is unpredictable, and this is used to provide a random bit stream. The random bits are mixed cryptographically with internal state derived from previous random bits, updating the internal state. The output mixing function uses this internal state to produce 32-bit random numbers at a programmable rate. At 100 megahertz (MHz), the 6500 can generate random data at greater than 3 Mb/s.

The results are pushed into the *random number First In First Out (FIFO)*, which is a 16-element FIFO, 32 bits wide. The FIFO is mapped to an array of sixteen 32-bit words. Reading any of these words reads only the top word from the FIFO; the FIFO's internal elements are not memory-mapped. This 16-way replication allows multiple random numbers to be read in a block data transfer.

It is possible to use random numbers more quickly or slowly than they can be generated (hence the FIFO). The Random Number Ready bit in the Status register is set when the random number generator contains at least eight random numbers. An interrupt can also be asserted when the Random Number Ready bit is set. If the host underflows the FIFO, the RNG Underflow bit will be set.

On reset, the random number generator is disabled. It must be re-enabled through the RNG Enable bit in the Config2 register before operation. If the

random number FIFO is read while the random number generator is disabled, the result is undefined.

### Operation

The random number generator is independent of the arithmetic unit and is enabled and accessed separately.

### Setup

- 1. Enable the random number generator.

- 2. Wait for the Random Number Ready bit to be set.

- 3. Read and discard the first 16 random numbers produced by the generator.

- 4. Enable the Random Number interrupt, if desired.

### **Operation**

- 5. Wait for the Random Number Ready bit to be set, or for the associated interrupt to be asserted. This will occur when the Random Number FIFO contains eight or more 32-bit random numbers.

- 6. Read up to eight random numbers from the FIFO.

- 7. Repeat (go to step 5).

# Memory Map and Addressing

### 3.1 Introduction

Figure 6 shows the memory map for the 6500. The map is the same for both PCI and direct-access modes. The 6500 occupies 32 KB of memory. This space is divided into four windows of 8 KB each. Except for the data register file, the four mappings are equivalent. For the register file, the windows correspond to different combinations of normal/reversed ordering of the bytes within a 32-bit word and normal/reversed address ordering of the words within a 1024-bit register.

# 3.1.1 Byte versus Word Addressing

All addresses are presented here as byte addresses for consistency with PCI, but the 6500 only supports 32-bit accesses, aligned to a 32-bit boundary. Address bits [1:0] should always be set to 0b00 on PCI. This is enforced in direct-access mode, as there are no ADDR [1:0] bits.

### 3.1.2 Address Notation

The notation for 6500 memory addresses is:

BaseAddress + Window + Offset,

where *BaseAddress* is the PCI BaseAddress if the PCI interface is being used, or zero if the direct-access interface is used,

Window is the offset from the base address, defining the window used. It is 0x0000, 0x2000, 0x4000, or 0x6000 for windows 0, 1, 2, and 3, respectively, and

Offset is the offset into the desired window.

|            |           | Full      |                                                        | Size, |              | See     |

|------------|-----------|-----------|--------------------------------------------------------|-------|--------------|---------|

| Window     | Offset    | Address   | Description                                            | Bytes | Organization | Section |

| 0          | 0000-07FF | 0000-07FF | Data Registers (reversed byte,                         | 2048  | 16x1024 bits | 3.2     |

|            |           |           | normal word ordering)                                  |       |              |         |

|            | 0800-0FFF | 0800-0FFF | Reserved                                               | 2048  |              |         |

|            | 1000-103F | 1000-103F | Length Tags                                            | 64    | 16x32 bits   | 3.3     |

|            | 1040-107F | 1040-107F | Reserved                                               | 64    |              |         |

|            | 1080-10BF | 1080-10BF | Random Number FIFO                                     | 64    | 16x32 bits   | 3.4     |

|            | 10C0-10FF | 10C0-10FF | Reserved                                               | 64    |              |         |

|            | 1100-117F | 1100-117F | Instruction Memory                                     | 128   | 32x32 bits   | 3.5     |

|            | 1180-1FBF | 1180-1FBF | Reserved                                               | 3648  |              |         |

|            | 1FC0-1FFF | 1FC0-1FFF | Control/Status Registers                               | 64    | 16x32 bits   | 3.6     |

| 1          | 0000-07FF | 2000-27FF | Data Registers (reversed byte, reversed word ordering) | 2048  | 16x1024 bits | 3.2     |

|            | 0800-0FFF | 2800-2FFF | Reserved                                               | 2048  |              |         |

|            | 1000-103F | 3000-303F | Length Tags                                            | 64    | 16x32 bits   | 3.3     |

|            | 1040-107F | 3040-307F | Reserved                                               | 64    |              |         |

|            | 1080-10BF | 3080-30BF | Random Number FIFO                                     | 64    | 16x32 bits   | 3.4     |

|            | 10C0-10FF | 30C0-30FF | Reserved                                               | 64    |              |         |

|            | 1100-117F | 3100-317F | Instruction Memory                                     | 128   | 32x32 bits   | 3.5     |

|            | 1180-1FBF | 3180-3FBF | Reserved                                               | 3648  |              |         |

|            | 1FC0-1FFF | 3FC0-3FFF | Control/Status Registers                               | 64    | 16x32 bits   | 3.6     |

| 2 0000-07F |           | 4000-47FF | Data Registers (normal byte,                           | 2048  | 16x1024 bits | 3.2     |

|            |           |           | normal word ordering)                                  |       |              |         |

|            | 0800-0FFF | 4800-4FFF | Reserved                                               | 2048  |              |         |

|            | 1000-103F | 5000-503F | Length Tags                                            | 64    | 16x32 bits   | 3.3     |

|            | 1040-107F | 5040-507F | Reserved                                               | 64    |              |         |

|            | 1080-10BF | 5080-50BF | Random Number FIFO                                     | 64    | 16x32 bits   | 3.4     |

|            | 10C0-10FF | 50C0-50FF | Reserved                                               | 64    |              |         |

|            | 1100-117F | 5100-517F | Instruction Memory                                     | 128   | 32x32 bits   | 3.5     |

|            | 1180-1FBF | 5180-5FBF | Reserved                                               | 3648  |              |         |

|            | 1FC0-1FFF | 5FC0-5FFF | Control/Status Registers                               | 64    | 16x32 bits   | 3.6     |

| 3          | 0000-07FF | 6000-67FF | Data Registers (normal byte, reversed word ordering)   | 2048  | 16x1024 bits | 3.2     |

|            | 0800-0FFF | 6800-6FFF | Reserved                                               | 2048  |              |         |

|            | 1000-103F | 7000-703F | Length Tags                                            | 64    | 16x32 bits   | 3.3     |

|            | 1040-107F | 7040-707F | Reserved                                               | 64    |              |         |

|            | 1080-10BF | 7080-70BF | Random Number FIFO                                     | 64    | 16x32 bits   | 3.4     |

|            | 10C0-10FF | 70C0-70FF | Reserved                                               | 64    |              |         |

|            | 1100-117F | 7100-717F | Instruction Memory                                     | 128   | 32x32 bits   | 3.5     |

|            | 1180-1FBF | 7180-7FBF | Reserved                                               | 3648  |              |         |

|            | 1FC0-1FFF |           |                                                        | 64    | 16x32 bits   | 3.6     |

| N C. 1     | 1FC0-1FFF | 7FC0-7FFF | Control/Status Registers                               | 64    | 16x32 bits   | 3.0     |

*Note*: Selecting a particular window affects byte ordering and normal/reversed address bit ordering for the 1024-bit data registers only. For the rest of the memory map, the choice of window has no effect on the 6500.

Figure 6. Memory map

# 3.2 Addressing the Data Registers

|                                                                                                                                                                                                                                                              | 14 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12                                                             | 11 7                                                                                                                                       | 6 2                                                                                                                                                        | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                              | window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                              | register                                                                                                                                   | word index                                                                                                                                                 | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|                                                                                                                                                                                                                                                              | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                              | 5                                                                                                                                          | 5                                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| Bit Field Description                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |                                                                                                                                            |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| window  Window selector. The window selects the byte or within a word, and whether the word index is into or not.  00 = reversed byte ordering/normal word index 01 = reversed byte ordering/reversed word index 10 = normal byte ordering/normal word index |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |                                                                                                                                            |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | is inverted<br>ndex<br>index<br>lex                                        |

| register Register number, in the range of 0-15. Each data register is 1,024 bits wide                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |                                                                                                                                            |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| word index                                                                                                                                                                                                                                                   | wind condition with the conditio | ndo<br>npi<br>elf.<br>th t<br>mb<br>eno<br>0b1<br>gisto<br>ord | s a 32-bit word word in the lowest-nullock with ascend | or 0b11, the 650 ord index, rathe esters that are sticant word at the be transferred as. When the will ex is not complete host with their imbered address. | 0 uses to than to ored or the higher a bloom from the transfer than the transfer transfer than the transfer transfer than the transfer transfer transfer than the transfer tra | the one's the index the host est- ck with field is 0b00 d, and significant |

| as a block with ascending addresses.  These bits are not used and should always be writted as 0. Address pins ADDR [1:0] do not exist on the direct-access interface.                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |                                                                                                                                            |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

Figure 7. Address format for the data registers

| Register | Offset |

|----------|--------|

| r0       | 0000   |

| r1       | 0080   |

| r2       | 0100   |

| r3       | 0180   |

| r4       | 0200   |

| r5       | 0280   |

| r6       | 0300   |

| r7       | 0380   |

| r8       | 0400   |

| r9       | 0480   |

| r10      | 0500   |

| r11      | 0580   |

| r12      | 0600   |

| r13      | 0680   |

| r14      | 0700   |

| r15      | 0780   |

Figure 8. Starting address for each data register, by window

### 3.2.1 Normal versus Reversed Byte Ordering

Normal vs. reversed byte ordering affects the order in which byte strings are packed into 32-bit arrays. For example, the 12-byte string, "Hello, world" would be packed into three 32-bit words as follows:

Normal byte order:

|       | Bit F | ield . | Ascending Address |       |

|-------|-------|--------|-------------------|-------|

| 31:24 | 23:16 | 15:8   | 7:0               |       |

| Н     | e     | 1      | 1                 | X     |

| О     | ,     |        | W                 | X + 4 |

| О     | r     | 1      | d                 | X + 8 |

Reversed byte order:

|       | Bit F | ield | Descending Address |       |

|-------|-------|------|--------------------|-------|

| 31:24 | 23:16 | 15:8 | 7:0                |       |

| 1     | 1     | e    | Н                  | X + 8 |

| W     |       | ,    | О                  | X + 4 |

| D     | 1     | r    | О                  | X     |

The 6500 operates in normal byte order internally, but supports both reversed and normal data transfers to the data register file. Only strings and byte arrays are affected by byte ordering. 32-bit quantities are defined unambiguously and are not affected.

Because 32-bit integers are byte order-independent on a 32-bit system, only the 6500's 1024-bit data registers are affected by byte ordering. (The 11-bit length tags, which would seem to be an exception, are in fact defined as 32-bit quantities with 11 valid bits and 21 reserved bits.)

The data windows in the 6500 allow the byte order to be selected on a pertransfer basis. Windows 0 and 1 support reversed byte order transfers to the data registers, while windows 2 and 3 support normal byte order transfers. The choice of window depends on how operands and results transferred between the host and the 6500 are stored in host memory.

# 3.2.2 Normal versus Reversed Word Ordering

Long integers are stored in host memory as an array of 32-bit words. Depending on how the host software allocates arrays, the least-significant 32 bits of a long integer may be at either the bottom of the array, or at the top. For our purposes, we say that data has *normal word ordering* when bits [31:0] of the long integer are at the lowest-numbered address of the array. The data has *reversed word ordering* when bits [31:0] of the long integer are at the highest-numbered address of the array.

The 6500 uses address windowing to support both types. Windows 0 and 2 support normal word ordering. Windows 1 and 3 support reversed word ordering. When a data register is transferred through Windows 1 or 3, the Word Index field of the address is inverted inside the 6500. This reverses the order in which register data is read from or written to the 6500.

### 3.2.3 Operand Alignment

The modular arithmetic operations are left-aligned, which means that the most-significant word of the operand is in bits [1023:992]. The byte-offset range used by a left-aligned operand is:

$$Register + (1024 - Length)/8$$

to

Register + 127,

Where *Register* is the starting address of the desired register (see Figure 8) and *Length* is the length of the operand in bits. Transferring a 1024-bit quantity to register r0 involves a byte offset of 0 through 127, while a 160-bit quantity uses offsets of 108 through 127.

The two's complement operations are right-aligned, using the range of

Register

to

$$Register + (Length - 1)/8$$

.

A 160-bit quantity written to register r0 would use offsets of 0 to 19.

Lengths of zero are invalid in either case.

# 3.3 Addressing the Length Registers

The length registers give the length in bits, of the number stored in each of the data registers. The length is stored as a 32-bit unsigned binary number, with eleven valid bits and 21 reserved bits. The registers are addressed linearly, with address 0x1000 addressing length register 0, and address 0x103c addressing length register 15:

| Length Register | Offset |

|-----------------|--------|

| LO              | 0x1000 |

| L1              | 0x1004 |

| L2              | 0x1008 |

| L3              | 0x100c |

| L4              | 0x1010 |

| L5              | 0x1014 |

| L6              | 0x1018 |

| L7              | 0x101c |

| L8              | 0x1020 |

| L9              | 0x1024 |

| L10             | 0x1028 |

| L11             | 0x102c |

| L12             | 0x1030 |

| L13             | 0x1034 |

| L14             | 0x1038 |

| L15             | 0x103c |

Figure 9. Address of each length register

# 3.4 Addressing the Random Number FIFO

The random number generator has a 16-element FIFO, 32 bits wide. This FIFO can be accessed from offsets 0x1080-0x10BF. Reading any word in this range will return the top entry of the FIFO. This multiple mapping allows burst transfers of the FIFO contents.

# 3.5 Addressing the Instruction Memory

The instruction memory consists of thirty-two 32-bit instructions. Execution starts at the address given in the command register and increments until the end of the program is reached. The instruction memory is mapped to offsets 0x1100-0x117F, with instruction 0 at offset 0x1100.

| Instruction | Offset |

|-------------|--------|

| i0          | 0x1100 |

| i1          | 0x1104 |

| i2          | 0x1108 |

| i3          | 0x110c |

| i4          | 0x1110 |

| i5          | 0x1114 |

| i6          | 0x1118 |

| i7          | 0x111c |

| i8          | 0x1120 |

| i9          | 0x1124 |

| i10         | 0x1128 |

| i11         | 0x112c |

| i12         | 0x1130 |

| i13         | 0x1134 |

| i14         | 0x1138 |

| i15         | 0x113c |

| i16         | 0x1140 |

| i17         | 0x1144 |

| i18         | 0x1148 |

| i19         | 0x114c |

| i20         | 0x1150 |

| i21         | 0x1154 |

| i22         | 0x1158 |

| i23         | 0x115c |

| i24         | 0x1160 |

| i25         | 0x1164 |

| i26         | 0x1168 |

| i27         | 0x116c |

| i28         | 0x1170 |

| i29         | 0x1174 |

| i30         | 0x1178 |

| i31         | 0x117c |

Figure 10. Address of each instruction register

# 3.6 Addressing the Control and Status Registers

The control registers are mapped to offsets 0x1FC0-0x1FFF. Each register is mapped to its own 32-bit word.

| Offset        | Description                 |

|---------------|-----------------------------|

| 0x1FC0-0x1FD3 | Reserved                    |

| 0x1FD4        | Command Register            |

| 0x1FD8        | Status Register             |

| 0x1FDC        | Interrupt Enable Register   |

| 0x1FE0        | Random Number Configuration |

| 0x1FE4        | Config1 Register            |

| 0x1FE8        | Config2 Register            |

| 0x1FEC        | Chip ID Register            |

| 0x1FF0-0x1FFF | Reserved                    |

Figure 11. Address map for status and configuration registers

# Signals and I/O

The 6500 operates in one of two bus modes: direct access or PCI. Direct access is a simple burst-oriented bus interface. PCI is an industry standard interface. The 6500 is a 32-bit PCI target device or a 32-bit direct-access slave device. Direct-access would be the interface of choice when integrating the 6500 into a system that doesn't have a PCI bus.

Both interfaces map all accesses to a 32 KB block of memory. See Figure 6 for the memory map.

### 4.1 Clocks

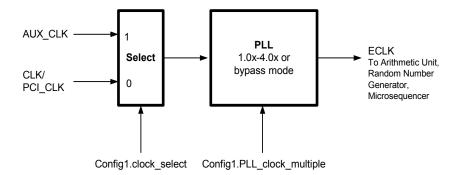

The 6500 has two clocks, the bus clock and AUX\_CLK. The name of the bus clock signal changes with the bus type – it is called PCI\_CLK when the PCI interface is enabled, and CLK when the direct-access interface is enabled.

The bus clock is used for I/O. The internal engines of the 6500 (the random number generator, arithmetic unit, and microsequencer) are driven by an internal clock, called ECLK, which can be derived from either the bus clock or AUX\_CLK. The bus clock is used by default, but AUX\_CLK can be selected by writing a one to the Clock Select bit of the Config1 register (see Section 5.5).

The selected clock can then be multiplied by a factor of 1-4x by an internal PLL, or the PLL can be bypassed. The resulting signal is ECLK. Refer to the Config1 register for PLL clock multiple (Section 5.5). Irrespective of the whether the PLL is enabled or not, the maximum ECLK clock rate is 100 MHz for a 6500-100 device and 50 MHz for a 6500-50 device.

Figure 12. ECLK generation

### 4.2 Direct-Access I/O

*Direct-access* I/O is a fast, efficient interface to the 6500. It is pipelined, resembling a synchronous SRAM interface. Direct-access supports single-cycle transfers on a 32-bit bus at speeds up to 66 MHz.

| 4.2.1 | Direct-Access | Signal | Summary |

|-------|---------------|--------|---------|

|-------|---------------|--------|---------|

| Pin                                                                                                                                                | Signal     | Type              | Description                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|-------------------------------------------|

| 88                                                                                                                                                 | BMODE      | Input*            | Bus mode = 1 for direct access            |

| 57                                                                                                                                                 | AUX_CLK    | Input*            | Optional engine clock. (See Section 4.1.) |

| 133, 7, 25, 26, 28, 29, 32, 33, 35, 36, 38, 144,                                                                                                   | ADDR[14:2] | Input             | Register address                          |

| 136                                                                                                                                                | AS#        | Input             | Address strobe                            |

| 93                                                                                                                                                 | CLK        | Input             | Bus clock                                 |

| 139                                                                                                                                                | CS#        | Input             | Chip select                               |