# 69003 / 69004 PC Video Pro

Video Windowing Controller

Data Sheet

January 1992

P R E L I M I N A R Y

#### **Copyright Notice**

Copyright © 1991, 1992 Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of Chips and Technologies, Inc.

### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

#### **Trademark Acknowledgement**

CHIPS and NEAT are registered trademarks of Chips and Technologies, Inc.

CHIPS, CHIPSet, MICROCHIPS, SCAT, NEATsx, LeAPSet, LeAPSetsx, PEAK, CHIPS/230, CHIPS/250, CHIPS/280, CHIPS/450, CHIPSPak, CHIPSPort, CHIPSlink, and SMARTMAP are trademarks of Chips and Technologies, Incorporated.

IBM AT, XT, PS/2, Micro Channel, Personal System/2, Enhanced Graphics Adapter, Color Graphics Adapter, Video Graphics Adapter, IBM Color Display, and IBM Monochrome Display are trademarks of International Business Machines.

Hercules is a trademark of Hercules Computer Technology.

MS-DOS is a trademark of Microsoft, Incorporated.

MultiSync is a trademark of Nippon Electric Company (NEC).

Brooktree and RAMDAC are trademarks of Brooktree Corporation.

Inmos is a trademark of Inmos Corporation.

#### Disclaimer

This document is provided for the general information of the customer. Chips and Technologies, Inc., reserves the right to modify the information contained herein as necessary and the customer should ensure that it has the most recent revision of the data sheet. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

## 69003 / 69004 PC Video Pro Video Windowing Controller

- Scan rate conversion and windowing control for display of a live video image on a computer graphics monitor

- Supports standard 4:1:1 and 4:2:2 YUV and 16-bit per pixel or 24-bit per pixel or 32-bit per pixel RGB digital formats

- Window positioning controlled by independent X-Y coordinates and by color keying

- Independent X-Y scaling of video image to 1/64 original image size

- Still-frame capture and display of true-color images

- Input resolutions up to 1024H x 1024V pixels with full broadcast quality video bandwidth

- Supports NTSC, PAL, SECAM, S-VHS, and RGB input formats from industry-standard video digitizer chipsets

- Interlaced or non-interlaced input video

- Interlaced or non-interlaced output support

- Output zoom by factors of 2, 4 and 8

- Output resolutions up to 1024 x 768

- Supports full-screen PAL display

- Software compatible with PC Video (82C9001)

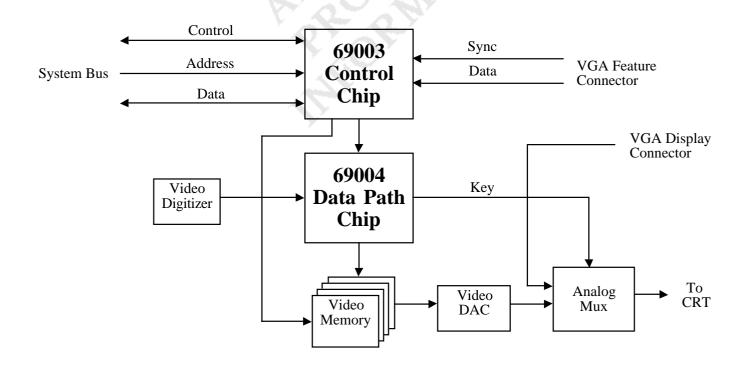

PC Video Pro System Block Diagram

## **Revision History**

| Revision | Date     | By    | Comment                                                     |

|----------|----------|-------|-------------------------------------------------------------|

| 0.1      | 11/22/91 | ME/ST | Initial Draft Copy                                          |

| 0.2      | 12/4/91  | ME/JF | Added System Diagram, Pinouts, and Mechanical Specification |

| 0.3      | 1/15/92  | ST    | Official Release                                            |

## **Table of Contents**

| Section                               | <u>Page</u>                | Section                         | Page                       |

|---------------------------------------|----------------------------|---------------------------------|----------------------------|

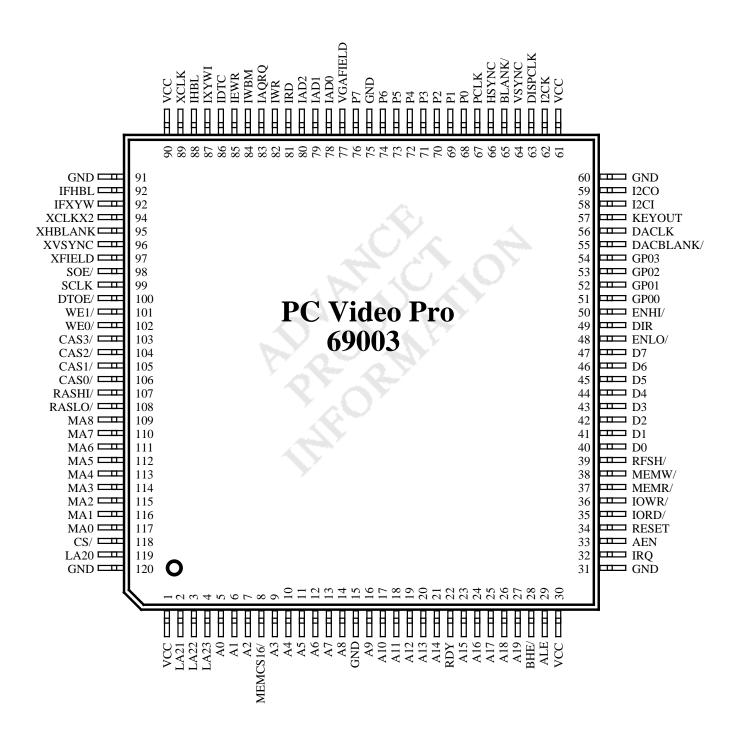

| Introduction                          | 5                          | Pinouts                         | 11                         |

| Overview                              | 5                          | 69003 Pin Diagram               | 11                         |

| Window Aquisition and Positioning     |                            | 69003 Pin Descriptions          | 12                         |

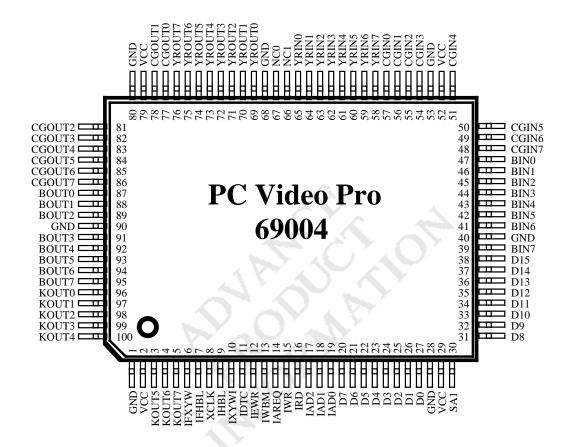

| Scaling                               | 5                          | 69004 Pin Diagram               | 18                         |

| Memory Interface                      | 5                          | 69004 Pin Descriptions          | 19                         |

| Memory Requirements                   | 5                          | •                               |                            |

| Quick-Štart Kit                       | 5                          | Register Descriptions           | 23                         |

| PC Video Pro Description              | 6<br>6<br>6<br>6<br>6<br>6 | Register Addressing             | 23<br>23<br>23<br>23<br>23 |

| Memory Interface                      | 7<br>7<br>8<br>8<br>9      | Absolute Maximum Conditions     | 41<br>41<br>41<br>42       |

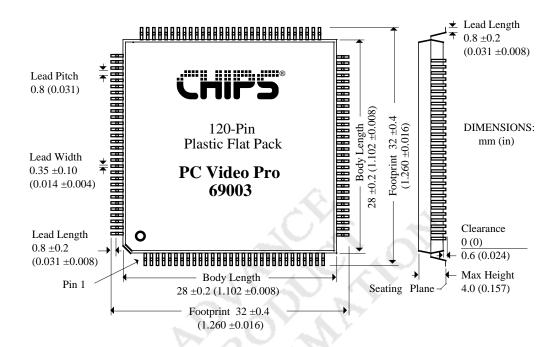

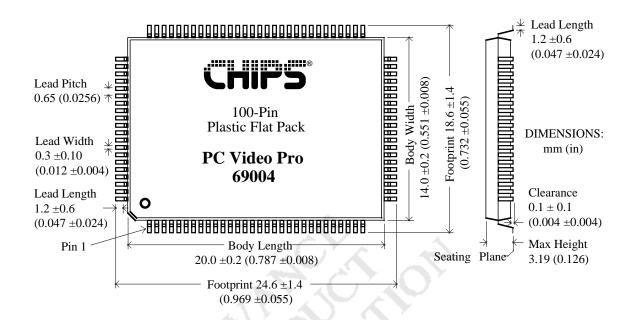

| Global Enable/Disable of PC Video Pro | 9                          | 69003 Mechanical Specifications | 55<br>56                   |

## **List of Figures and Tables**

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>Page</u>                                                                                                | <u>Table</u>      | Page                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------|

| Block Diagram Acquisition & Display Process Example Memory Configuration Overlay Functions 69003 Pinouts 69004 Pinouts Input Video Timing ISA Bus I/O Timing ISA Bus Timing VGA Pixel Clock to KEYO Timing Display Clock to DAC Clock Timing VRAM Random Read Cycle Timing VRAM Random Write Cycle Timing VRAM Fast-page Write Cycle Timing VRAM Data Transfer Cycle Timing VRAM Refresh Cycle Timing PFP-120 Package Mechanical Dimensions PFP-100 Package Mechanical Dimensions | 1<br>5<br>7<br>9<br>11<br>18<br>42<br>43<br>44<br>46<br>47<br>47<br>50<br>51<br>52<br>53<br>54<br>55<br>56 | Control Registers | 41<br>41<br>42<br>43<br>44<br>45<br><br>47<br>48<br>48 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                            |                   |                                                        |

## Introduction

#### **OVERVIEW**

The PC Video Pro video windowing chip set is the core component of a video subsystem which converts a standard full-motion video image into a format for display on a computer graphics monitor. PC Video Pro controls positioning and scaling of the video image on the output display and allows the video image to be merged with computer graphics for interactive multimedia applications. The PC Video Pro is targeted for the workstation requirements of high-resolution and 24-bit color. Market applications of a subsystem based on PC Video Pro include interactive video training, computer-based education programs, point-of-sale information, business presentations, video conferencing, and desktop publishing. PC Video Pro integrates all the controlling logic for video scan rate conversion, windowing control, and scaling. Operation with VGA graphics is supported via the graphics feature connector.

A video windowing sub-system can be implemented with the following components:

PC Video Pro A standard "Digital TV" chip set 6 VRAMs

Other optional configurations are supported for higher color and luminance bandwidth.

PC Video Pro is register-compatible to the 82C9001A PC Video chip, allowing software applications written for PC Video to be easily ported to PC Video Pro.

#### WINDOW AQUISITION AND POSITIONING

PC Video Pro provides the control signals for a standard video digitizer chip set. Interlaced and non-interlaced video sources, at full broadcast quality bandwidth, are supported at resolutions up to 1024 x 1024 pixels. PC Video Pro may be programmed to capture a full-size video image or a user-defined cropped or reduced area.

Video output window positioning is provided by programmable X-Y coordinates and color keying to a specified color. Color Keying is based on the digital color information from the VGA feature connector. Color keying is supported independently or in conjunction with X-Y coordinates.

#### **SCALING**

PC Video Pro provides independent X-Y scaling of the input video image in integer increments of 1/64. Images may be compressed down to 1/64 of the original image size, supporting video icons for graphical user interfaces.

#### **MEMORY INTERFACE**

PC Video Pro operates with 256K x 4 100 ns VRAMs. Five configurations are supported: 4 VRAMs for 2:1:1 encoding, 6 VRAMs for 4:1:1 encoding, 8 VRAMs for 4:2:2 or 16-bit RGB encoding, 12 VRAMs for 24-bit RGB and 16 VRAMs for 1024 x 1024 resolution or 24-bit RGB + 8-bit overlay.

## MEMORY REQUIREMENTS

| Bits per<br>Pixel | <u>Format</u> | Memory<br>Required | Video Quality                          |

|-------------------|---------------|--------------------|----------------------------------------|

| 12-bit            | 2:1:1 YUV     | 4 VRAM             | Compressed luminance bandwidth         |

| 12-bit            | 4:1:1 YUV     | 6 VRAM             | Broadcast video bandwidth              |

| 16-bit            | 4:2:2 YUV     | 8 VRAM             | Improved chroma bandwidth              |

| 16-bit            | 16-bit RGB    | 8 VRAM             | 65,536 colors                          |

| 16-bit            | 4:2:2 YUV     | 16 VRAM            | 1024 x 1024 High resolution            |

| 24-bit            | 24-bit RGB    | 12 VRAM            | 16.8 million colors                    |

| 32-bit            | 24-bit RGB    | 16 VRAM            | 16.8 million colors<br>+ 8-bit overlay |

#### **QUICK-START KIT**

The PC Video Pro Quick-Start Kit offers a working example of a 16-bit, full-screen PAL implementation at resolutions up to 1024 x 768. A Windows DLL and sample application are included in the kit. The development kit also includes an OEM software license.

#### PC VIDEO PRO DESCRIPTION

#### Video Formats

Color images in computer graphics are typically represented by R, G, and B components. Video and TV images are typically represented by one luma (Y) and two chroma (U, V) components which make up a composite video signal. The luma component has twice the bandwidth of the individual chroma components. Digitized video systems typically use luma/chroma components because of the ease of conversion to and from composite video signals. Representation of an image in luma/chroma is also more memory efficient than in R, G, and B components. A 640x480 image in 16-bit RGB produces 65,536 colors and requires 1 meg of VRAM. The same image can be saved in Luma/Chroma coordinates in 768k of VRAM and produces 2 million colors.

PC Video Pro is flexible to support both R, G, B and Y, U, V components. Four main formats are supported as described below.

The X:Y:Z numbers refer to the number of samples for the three input video components.

- 1) 4:1:1 The luma component (Y) is sampled every pixel and the chroma components (U, V, or Yr, Yb) are averaged over four pixels. For every four input pixels, there are four luma samples and one U and V (chroma) sample, for six samples total.

- 2) 4:2:2 This format expands the color bandwidth of the 4:1:1 format. The chroma components are averaged over two pixels. For every four input pixels, there are four luma samples and two of each chroma samples, for eight samples total. This is the international broadcast standard CCIR 601.

- 3) 4:4:4 This format is typically used for R, G, B components but could also be used for luma and chroma components. The components are sampled at every pixel, resulting in 12 samples to four pixel times. The bandwidth on all components is the same.

#### **Signal Flow**

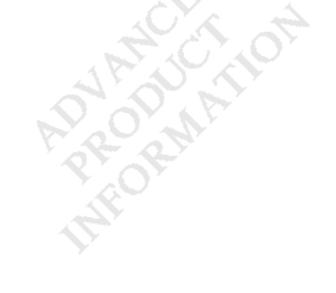

Image acquisition and display in a PC Video Pro subsystem are two independently programmable processes which occur at asynchronous clock rates.

#### **Acquisition**

PC Video Pro provides the control signals to a standard digital video chipset. The acquisition window coordinates are programmable, enabling cropping and panning of the input image. The digitized video passes through PC Video's internal FIFO and is stored in the frame buffer. The acquisition process is synchronized to the input video VSYNC and HBLANK signals and is executed at the video sampling rate. The image acquisition data is applied to the random access ports of the dual-ported video rams. Scaling is performed upon the input video data as part of the acquisition process. The scaled image is stored in the frame buffer.

The input window supports both interlaced (default) and non-interlaced video. Four capture modes are available: (a) Interlaced frame, (b) Even field, (c) Odd field), and (d) Non-interlaced frame. In unscaled, interlaced mode the raster address is advanced by two, with the even field writing the even line numbers and the odd field writing odd lines. The even field starts at line 0 and advances by 2's: 0, 2, 4. The odd field starts at line 1 and advances by 2's: 1, 3, 5, up to the maximum line count.

An address multiplexer selects addresses from the acquisition window, video display window or the host processor. Either live video acquisition or CPU read/write access may take place but not both simultaneously.

#### **Display**

The display process is synchronized to the VGA HSYNC, VSYNC, BLANK, and CLOCK signals from the feature connector. The data is output from the serial port of the video rams. The video image may be displayed inside or outside any rectangular window on the VGA screen.

## **System Clocks**

The video ram control/timing logic uses the double rate video input clock. The double clock rate of 27 MHz is line-locked, tracking variations in input video sync, which occur with video tape recorders (VTR's), still-video cameras and other non-time base stable sources. The maximum input clock rate is 30 MHz.

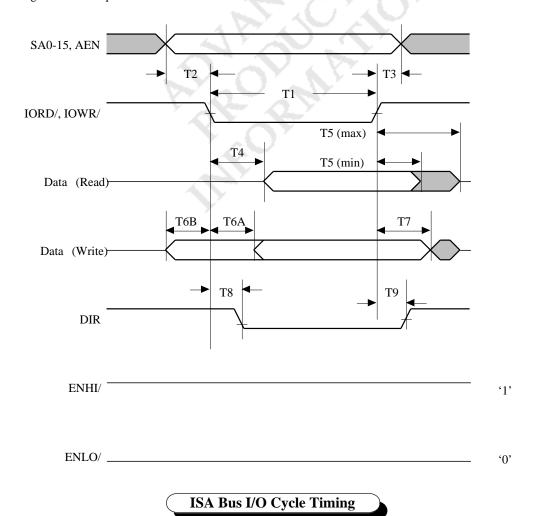

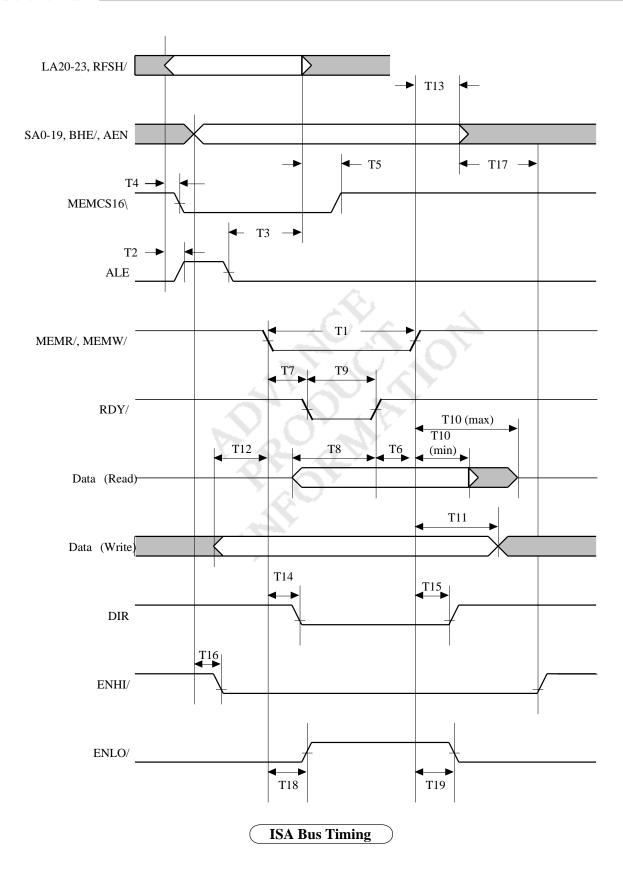

### **CPU Interface**

PC Video Pro has a non-multiplexed 24 bit address bus and a 16 bit data bus. PC Video Pro latches AT bus addresses LA[20:23] using the AT bus signal ALE. PC Video Pro memory is accessible using 8 and 16 bit bus cycles while PC Video Pro I/O registers are accessible using 8 bit cycles only. PC Video Pro handles all byte swapping for memory accesses. PC Video Pro supports 16 bit memory cycles and generates MEMCS16/ when memory is

mapped above 1M byte in the PC address space. PC Video Pro-based boards can be plugged into a 16 bit bus slot.

PC Video Pro may be programmed to respond to either a fixed I/O address or software programmed I/O address. When the bus RESET signal goes from high to low, the status of CS/ pin is sampled by PC Video Pro. If CS/ is sampled active (low) then PC Video Pro responds to I/O addresses 0AD6-7h. However if CS/ is inactive (high) then it uses the Programmed I/O Address Register bits 7:0 and CS/ to detect the valid I/O address space. When this mode is selected, the Programmed I/O Address Register bits are written by the first CPU I/O write cycle with CS/ active. Since PC Video Pro always occupies two consecutive I/O addresses, bit-0 of this register is ignored.

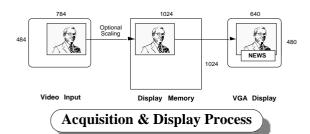

### **Memory Interface**

Memory is organized as 2 banks 1K wide by 512 or 1K high. The depth of the memory is either 12 bits for 4:1:1 multiplexed data format, 16 bits for the 4:2:2 multiplexed data formats, 24 bits for RGB format, or 32 bits for RGB + Key (refer to memory configuration diagram below).

PC Video Pro uses 256K x 4, 100 nS VRAMs and supports four VRAM configurations. PC Video Pro also supports the VRAM Write Bit Mask function. Frame buffer memory is accessible in the extended memory address space above 1 MByte (100000h), located on any 2 MByte boundary. The memory can be accessed as a 2 MByte linear space or as two 1 MByte spaces selected by the paging bit in register 6. The Video Frame Buffer memory can be accessed as byte or word cycles. PC Video Pro generates one wait state for memory accesses, or more than one when memory accesses conflict with VRAM refresh cycles or VRAM data transfer cycles. PC Video Pro memory is not accessible on RESET and must explicitly be enabled to access the PC Video Pro memory.

## **Interrupt Support**

PC Video Pro supports CPU interrupts upon receipt of a video Vsync. The interrupt source bits are held until cleared by software.

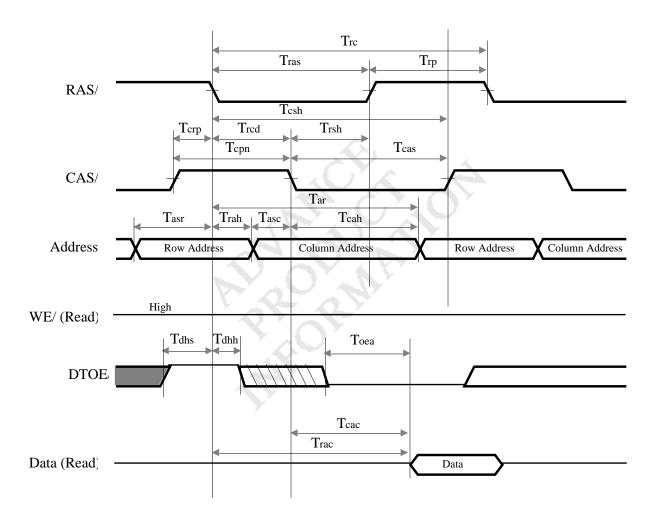

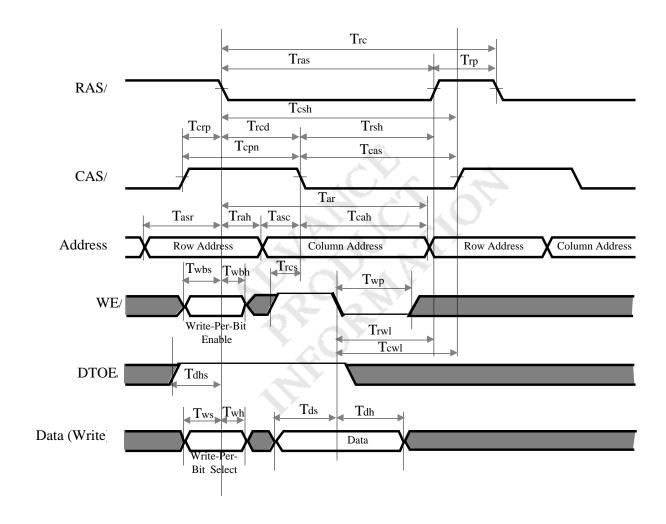

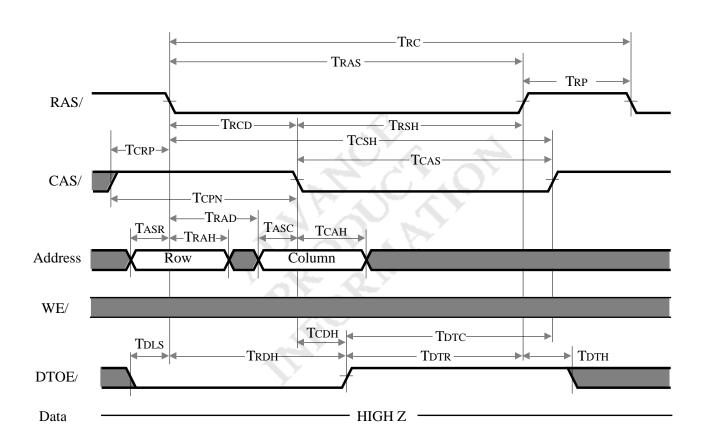

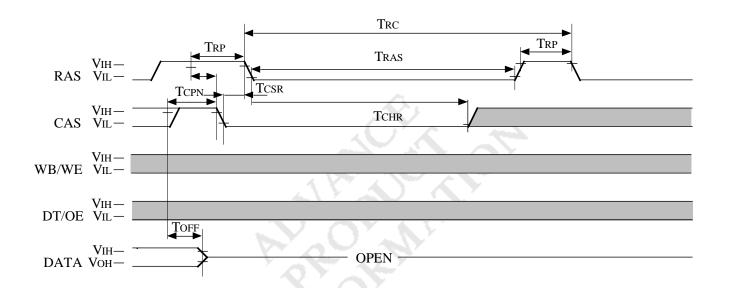

## **Video RAM Timing Generator**

A synchronous timing generator operates the video RAM control signals, derived from the double rate video data clock. The video RAM is operated as two

1024H x 512V x 32 bit

1024H x 1024V x 16 bit

**Example Memory Configurations**

Each box represents two 256K X 4 VRAMS. SCLK and DTOE are common to each VRAM.

banks each running in "fast-page" mode along the line. Each bank receives alternating pixels across the horizontal line, using a common data bus driven at the pixel rate of 13.5 MHz. The column address signal (CAS) or write enable (WE) of each bank strobes in the pixel data.

Memory refresh occurs during input video horizontal blanking. PC Video Pro provides limited access to the memory during acquisition in the vertical blanking of an acquisition frame. Additional access time is available in field grab mode. Along with the vertical interval, the unused field time can be used for processor access. During acquisition, the CPU may poll a bit to verify that memory is available for a CPU access. Once the memory is available the CPU can initiate a cycle. When the cycle is completed, the CPU can verify that no conflict occurred by checking the Error bit of register 9, the interrupt polling/mask register. If the Error bit is set then the CPU must assume that the cycle did not occur, clear the Error bit, and reissue the cycle when the memory is available.

CPU access utilizes a standard read/write cycle using the parallel data path, bypassing the input video FIFO.

The VGA display window uses the 1 MEG (256K x 4) VRAM serial shift register to scan-out the display data. The VRAM serial output is used only in read mode and two banks of VRAMs operate in a pingpong style data organization providing 1024 pixels per line from two 512 pixel VRAM shift registers.

The following VRAM memory cycles are supported:

|                                       | supported:                                                         |

|---------------------------------------|--------------------------------------------------------------------|

| Cycle Type 1) Random Read/Write cycle | Function processor access                                          |

| 2) CAS before RAS refresh             | refresh only                                                       |

| 3) Shift Register Load                | loading shift register for output display                          |

| 4) Fast-page mode write               | video acquisition                                                  |

| 5) Write Bit Mask                     | masking of data bits<br>during video acqui-<br>sition or CPU write |

| 6) Shift register output              | clocked at one half                                                |

### **Scaling**

Two independent input scaling ratios are supported: one for the horizontal, the other for the vertical. The vertical ratio accounts for interlace.

the output display

rate

Scaling is performed by dropping pixels horizontally and dropping lines vertically. Independent scaling factors, ranging from 1/64 to 63/64 in integer multiples of 1/64 are supported in the horizontal and vertical directions. 64/64 is supported by turning scaling off.

## **Display Window Overlay**

The mixing of the analog VGA and analog video data is performed externally using an analog multiplexer. The multiplexer control signal can be generated in three different ways:

- a) By defining an output window in the PC Video Pro X-Y Window Control Registers,

- b) By keying to a VGA Color (Color compare ) or

- c) Use overlay plane as a key source.

The multiplexer function for cases (a) and (b) is generated by PC Video Pro and is clocked by the VGA clock (PCLK). In case (c), the overlay memory output drives an external video multiplexer. With more bits of the overlay memory driving a DAC (4 or 8 bit) a linear key signal can be generated to control an external video mixer.

#### X-Y Window Control Registers:

The X-Y window area is defined by four registers that specify a rectangular region using X-start, X-end, Y-start, and Y-end. The X-Y window position is referenced to the VGA sync signals. The size of the X-Y window is defined in VGA clocks and lines.

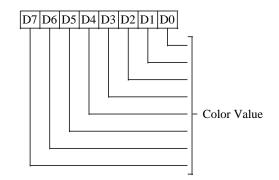

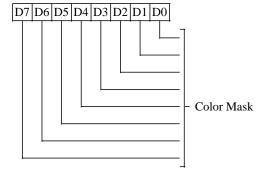

#### Color Keying:

A control signal is generated by comparing the 8 bit VGA TTL video data (P7:0) to an 8 bit value in the Color Key register. Comparison of certain color key bits can be disabled by setting the corresponding bit in the color compare mask register. This allows keying on more than one color. The VGA pixel data is sampled by PCLK.

### Overlay Memory Data:

One or more bits of the overlay (KEY) memory may be used to control the combination of live video and VGA data. Through support of the Write Mask, the overlay can be protected, and a keying pattern written to it. Using one bit of the overlay creates a one bit mask, which can control an analog or digital multiplexer. This forms a "Hard-Edge KEY". Four bits or more of KEY memory can drive a DAC which forms a linear key signal. This signal is sent to a linear mixer, which can smoothly combine the VGA and video picture. The image written into the overlay plane decides the transparency or opacity of the mixed VGA and video signal.

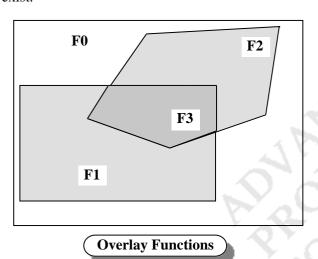

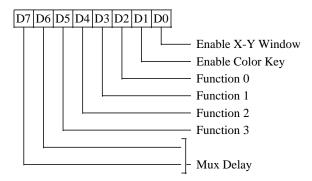

#### **Color Key Functions:**

There are four possible combinations of the display window and color key areas. They are: non window and non key area (F0), window area but not key (F1), key area but not window (F2) and both window and key area (F3). These four functions select one of the function bits on a pixel by pixel basis. If the function bit for that area is a '0', that display area shows the VGA graphics. If the function bit for that area is '1', the video output data is overlayed on the VGA graphics. If the X-Y window is disabled, areas F1 and F3 do not exist. If color keying is disabled, areas F2 and F3 do not exist.

### **Display Area Panning**

Video data in the display area can be panned horizontally by 1024 pixels in steps of 4 pixels for 4:1:1 input Y/C format or in steps of 2 pixels for 4:2:2 input Y/C format. Video data may be panned vertically by 1024 in steps of 1 scan line.

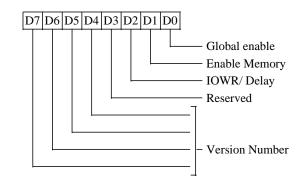

### Global Enable/Disable of PC Video Pro

PC Video Pro I/O register index FFh is reserved for global enable and disable of PC Video Pro. This register is a write only register. Bit-0 of this register is used to control this function. This bit is cleared on RESET. After PC Video's I/O address is determined, this bit should be set to '1' to enable access to other PC Video Pro I/O registers. The PC Video Pro frame buffer is accessible when bit-1 of this register is set to '1'. The upper 4 bits of this register are readable and they reflect the 69003 Revision/Part Number.

## 69003 Pinouts

## 69003 System Bus Interface

| Pin# | Pin Name | Type | Active | Description                                                                  |

|------|----------|------|--------|------------------------------------------------------------------------------|

| 5    | A0       | In   | Both   | 20 bits of system address bus                                                |

| 6    | A1       | In   | Both   | •                                                                            |

| 7    | A2       | In   | Both   |                                                                              |

| 9    | A3       | In   | Both   |                                                                              |

| 10   | A4       | In   | Both   |                                                                              |

| 11   | A5       | In   | Both   |                                                                              |

| 12   | A6       | In   | Both   |                                                                              |

| 13   | A7       | In   | Both   |                                                                              |

| 14   | A8       | In   | Both   |                                                                              |

| 16   | A9       | In   | Both   |                                                                              |

| 17   | A10      | In   | Both   |                                                                              |

| 18   | A11      | In   | Both   |                                                                              |

| 19   | A12      | In   | Both   |                                                                              |

| 20   | A13      | In   | Both   |                                                                              |

| 21   | A14      | In   | Both   |                                                                              |

| 23   | A15      | In   | Both   |                                                                              |

| 24   | A16      | In   | Both   |                                                                              |

| 25   | A17      | In   | Both   |                                                                              |

| 26   | A18      | In   | Both   |                                                                              |

| 27   | A19      | In   | Both   |                                                                              |

| 119  | LA20     | In   | Both   | Upper 4 bits of the system address bus. These address                        |

| 2    | LA21     | In   | Both   | bits are latched on the falling edge of ALE.                                 |

| 3    | LA22     | In   | Both   | 2 8                                                                          |

| 4    | LA23     | In   | Both   |                                                                              |

| 40   | D0       | I/O  | Both   | System data bus                                                              |

| 41   | D1       | I/O  | Both   |                                                                              |

| 42   | D2       | I/O  | Both   |                                                                              |

| 43   | D3       | I/O  | Both   |                                                                              |

| 44   | D4       | I/O  | Both   |                                                                              |

| 45   | D5       | I/O  | Both   |                                                                              |

| 46   | D6       | I/O  | Both   |                                                                              |

| 47   | D7       | I/O  | Both   |                                                                              |

| 34   | RESET    | In   | High   | Reset                                                                        |

| 39   | RFSH/    | In   | Low    | System Refresh. When this input is low, the current memory cycle is ignored. |

| 48   | ENLO/    | Out  | Low    | Enable controls for external data transceivers for the                       |

| _ 50 | ENHI/    | Out  | Low    | data bus.                                                                    |

## 69003 System Bus Interface (continued)

| Pin# | Pin Name | Type | Active | Description                                                                                                                                                                                                                                                                                         |

|------|----------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49   | DIR      | Out  | Both   | Direction control for external data bus transceivers: 0 = read from PC Video, 1 = write to PC Video.                                                                                                                                                                                                |

| 28   | BHE/     | In   | Low    | Enable for 16-bit interface. Low indicates that the high order byte at the current word address is being accessed. Along with A0, indicates which bytes are transferred over the bus (all byte steering is done internally):                                                                        |

|      |          |      |        | BHE/ A0 Effect                                                                                                                                                                                                                                                                                      |

|      |          |      |        | 0 0 Both bytes on D15:0<br>0 1 High byte on D15:8                                                                                                                                                                                                                                                   |

|      |          |      |        | 1 0 Low byte on D7:0                                                                                                                                                                                                                                                                                |

| 33   | AEN      | In   | Both   | Defines valid I/O address: 0 = valid I/O address, 1 = Invalid I/O address (DMA cycle). If single-cycle DMA is used, memory addresses will be on the bus at the same time that IORD/ or IOWR/ is active. PC Video will not respond to IORD/ or IOWR/ while AEN=1.                                    |

| 29   | ALE      | In   | High   | Address latch enable. The system address is latched on the falling edge of this signal.                                                                                                                                                                                                             |

| 22   | RDY      | Out  | High   | Ready. Driven low to indicate the current cycle should be extended with wait states. Driven high at end of cycle to indicate 'ready' then tri-stated. This signal is normally high and is only driven low if PC Video cannot respond immediately to a memory request and wait states are necessary. |

| 8    | MEMCS16/ | 4    | Out    | Indicates 16-bit Memory cycle. Asserted by PC Video to indicate that the chip is capable of transferring 16 bits over the bus at the requested address.                                                                                                                                             |

| 37   | MEMR/    | In   | Low    | Indicates a memory read cycle from AT bus                                                                                                                                                                                                                                                           |

| 38   | MEMW/    | In   | Low    | Indicates a memory write cycle from AT bus                                                                                                                                                                                                                                                          |

| 35   | IORD/    | In   | Low    | Indicates an I/O Read cycle                                                                                                                                                                                                                                                                         |

| 36   | IOWR/    | In   | Low    | Indicates an I/O Write cycle                                                                                                                                                                                                                                                                        |

| 32   | IRQ      | Out  | Both   | Video VSYNC Interrupt. This pin is low when interrupts are enabled but no interrupt is pending, and high when interrupts are enabled and an interrupt is pending.                                                                                                                                   |

## **69003 Memory Interface**

| Pin# | Pin Name | Type | Active | Description                                                                                                |

|------|----------|------|--------|------------------------------------------------------------------------------------------------------------|

| 109  | MA8      | Out  | High   | VRAM Address bus for both banks and planes of                                                              |

| 110  | MA7      | Out  | High   | memory.                                                                                                    |

| 111  | MA6      | Out  | High   | •                                                                                                          |

| 112  | MA5      | Out  | High   |                                                                                                            |

| 113  | MA4      | Out  | High   |                                                                                                            |

| 114  | MA3      | Out  | High   |                                                                                                            |

| 115  | MA2      | Out  | High   |                                                                                                            |

| 116  | MA1      | Out  | High   |                                                                                                            |

| 117  | MA0      | Out  | High   |                                                                                                            |

| 107  | RASHI/   | Out  | Low    | VRAM Row Address Strobe for Luminance plane.                                                               |

| 108  | RASLO/   | Out  | Low    | VRAM Row Address Strobe for Chrominance plane.                                                             |

| 103  | CAS3/    | Out  | Low    | VRAM Column Address Strobe. There is a strobe for                                                          |

| 104  | CAS2/    | Out  | Low    | each bank of memory.                                                                                       |

| 105  | CAS1/    | Out  | Low    |                                                                                                            |

| 106  | CASO/    | Out  | Low    |                                                                                                            |

| 101  | WE1/     | Out  | Low    | VRAM Write Enable. There is an enable for each bank                                                        |

| 102  | WEO/     | Out  | Low    | of memory.                                                                                                 |

| 100  | DTOE/    | Out  | Low    | Data Transfer / Output Enable.                                                                             |

| 99   | SCLK     | Out  | High   | VRAM shift Clock for all VRAMs. This signal is also used to multiplex the output data from the VRAM banks. |

## 69003 VGA/Video Interface

| Pin#                                         | Pin Name                                     | Type                             | Active                                               | Description                                                                                                                                                                                                                                                        |

|----------------------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

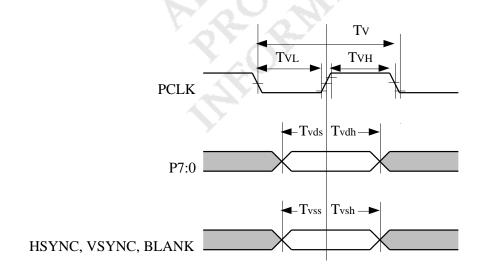

| 67                                           | PCLK                                         | In                               | Both                                                 | VGA Pixel Clock. This clock is used to latch the VGA pixel data and synchronize the video overlay window.                                                                                                                                                          |

| 66<br>64<br>65                               | HSYNC<br>VSYNC<br>BLANK/                     | In<br>In<br>In                   | Both<br>Both<br>Low                                  | Horizontal, Vertical Sync, and Blank signals from the VGA feature connector. These signals are used to synchronize the overlay of video and VGA graphics.                                                                                                          |

| 77                                           | VGAFIELD                                     |                                  | In                                                   | <b>Bote</b> rnal Field bit. Chip uses internally generated field signal for display out overlay, by default. However, if required, field signal from this pin can be selected by setting bit D1 of Reg. 50 to 1.                                                   |

| 76<br>74<br>73<br>72<br>71<br>70<br>69<br>68 | P7<br>P6<br>P5<br>P4<br>P3<br>P2<br>P1<br>P0 | In<br>In<br>In<br>In<br>In<br>In | Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both | Pixel Data from the VGA feature connector. This data is used for color matching to control overlay of VGA graphics and video output.                                                                                                                               |

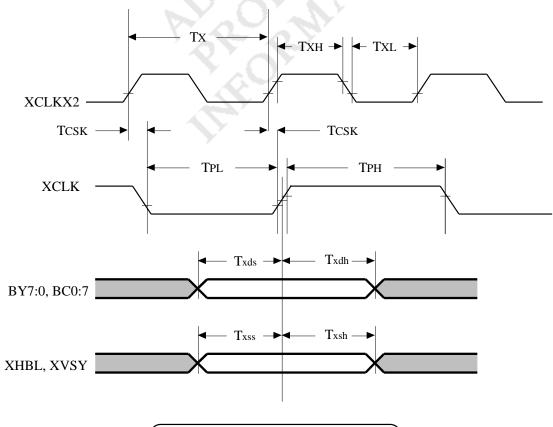

| 89                                           | XCLK                                         | În                               | Both                                                 | Video Data Clock. This clock is to latch the Video data from the digital video source.                                                                                                                                                                             |

| 94                                           | XCLKX2                                       | In                               | Both                                                 | Twice Video Data Clock. This clock is twice the Video data clock. It is used to generate the VRAM timing.                                                                                                                                                          |

| 96                                           | XVSYNC                                       | In                               | Both                                                 | Vertical Sync signal from the digital video source. This signal is used to synch. the storage of the video data.                                                                                                                                                   |

| 95                                           | XHBLANK                                      | In                               | Both                                                 | Horizontal Blank. This signal is used to identify the active area in the digital video output data stream.                                                                                                                                                         |

| 97                                           | XFIELD                                       | In                               | Both                                                 | External Field. Chip uses internally generated field signal, by default. However, if required, field signal from this pin can be selected by setting bit D6 of Reg. 21 to 1.                                                                                       |

| 118                                          | CS/                                          | In                               | Low                                                  | Chip Select (I/O only.) This pin is sampled on the falling edge of reset. If it is low, PC Video will respond to I/O accesses at locations 0AD6 and 0AD7. If it is high, then the Programmed I/O Register and the CS/input are used to detect a valid I/O address. |

| 62<br>59<br>58                               | I2CK<br>I2CO<br>I2CI                         | Out<br>Out<br>In                 | Both<br>Both<br>Both                                 | These open collector I/O pins are designed to support the Inter-Integrated Circuit (I2C) bus.                                                                                                                                                                      |

## 69003 VGA/Video Interface (continued)

| Pin#                                                                       | Pin Name                                                          | Type                                    | Active                                                       | Description                                                                                                                                                                                                            |

|----------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

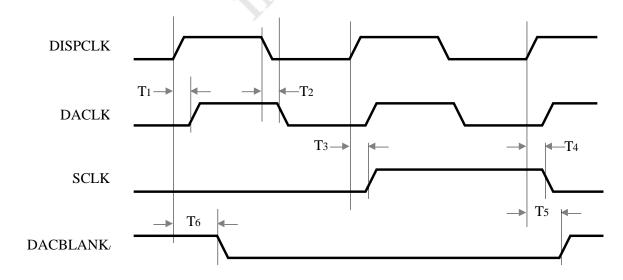

| 63                                                                         | DISPCLK                                                           | In                                      | Both                                                         | Display Clock input. This input supplies the clock that is used to output the digital video data.                                                                                                                      |

| 56                                                                         | DACLK                                                             | Out                                     | Both                                                         | Video DAC Clock. This signal clocks the output video data into the video DACs. Derived from DISPCLK.                                                                                                                   |

| 55                                                                         | DACBLANK/                                                         | Out                                     | Low                                                          | Video Blank output to DAC. This signal is synchronized with DISPCLK and qualifies valid video data from the VRAM memory.                                                                                               |

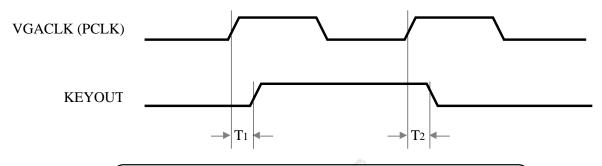

| 57                                                                         | KEYOUT                                                            | Out                                     | Low                                                          | Video/VGA Mux. When high, the output data mux selects Video data; when low, the output is VGA graphics.                                                                                                                |

| 54<br>53<br>52<br>51                                                       | GPO3<br>GPO2<br>GPO1<br>GPO0                                      | Out<br>Out<br>Out<br>Out                | Both<br>Both<br>Both<br>Both                                 | General Purpose I/O strobes. These pins may be used as I/O strobes for additional user defined external registers. GP01 can be defined as a Phase locked loop reference output by setting bit 5 of Register 18 to '0'. |

| 78<br>79<br>80<br>81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>92<br>93 | IAD0 IAD1 IAD2 IRD IWR IAQRQ IWBM IEWR IDTC IXYW IHBL IFHBL IFXYW | Out | Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both | Inter-chip control signals. These pins connect to the corresponding pins on the 69004.                                                                                                                                 |

## 69003 Power and Ground

| Pin#                              | Pin Name | Type | Active | Description |

|-----------------------------------|----------|------|--------|-------------|

| 1<br>30<br>61<br>90               | VCC      | Pwr  | -      | + 5V Power  |

| 15<br>31<br>60<br>75<br>91<br>120 | GND      | Pwr  | -      | Ground      |

## 69004 Pinouts

## 69004 System Bus Interface

| Pin#                                                                                         | Pin Name                                              | Type                                                               | Active                                  | Description                 |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------|-----------------------------|

| 30                                                                                           | A1                                                    | In                                                                 | Both                                    | 1 bit of system address bus |

| 27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38 | D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Both Both Both Both Both Both Both Both | System data bus             |

|                                                                                              |                                                       | PR                                                                 |                                         |                             |

## 69004 Video Memory Interface

| Pin# | Pin Name Type | ActiveDe | ActiveDescription |                                                       |  |  |

|------|---------------|----------|-------------------|-------------------------------------------------------|--|--|

| 76   | YROUT7        | I/O      | High              | Luminance/Red Data bus. These pins connect to the     |  |  |

| 75   | YROUT6        | I/O      | High              | VRAM data pins.                                       |  |  |

| 74   | YROUT5        | I/O      | High              | •                                                     |  |  |

| 73   | YROUT4        | I/O      | High              |                                                       |  |  |

| 72   | YROUT3        | I/O      | High              |                                                       |  |  |

| 71   | YROUT2        | I/O      | High              |                                                       |  |  |

| 70   | YROUT1        | I/O      | High              |                                                       |  |  |

| 69   | YROUT0        | I/O      | High              |                                                       |  |  |

| 86   | CGOUT7        | I/O      | High              | Chrominance/Green Data bus. These pins connect to the |  |  |

| 85   | CGOUT6        | I/O      | High              | VRAM data pins.                                       |  |  |

| 84   | CGOUT5        | I/O      | High              |                                                       |  |  |

| 83   | CGOUT4        | I/O      | High              |                                                       |  |  |

| 82   | CGOUT3        | I/O      | High              |                                                       |  |  |

| 81   | CGOUT2        | I/O      | High              |                                                       |  |  |

| 78   | CGOUT1        | I/O      | High              |                                                       |  |  |

| 77   | CGOUT0        | I/O      | High              | <u>* 67.07</u>                                        |  |  |

| 95   | BOUT7         | I/O      | High              | Blue Data bus. These pins connect to the VRAM data    |  |  |

| 94   | BOUT6         | I/O      | High              | pins.                                                 |  |  |

| 93   | BOUT5         | I/O      | High              |                                                       |  |  |

| 92   | BOUT4         | I/O      | High              |                                                       |  |  |

| 91   | BOUT3         | I/O      | High              |                                                       |  |  |

| 89   | BOUT2         | I/O      | High              |                                                       |  |  |

| 88   | BOUT1         | I/O      | High              |                                                       |  |  |

| 87   | BOUT0         | I/O      | High              | ) <sup>y</sup>                                        |  |  |

| 5    | KOUT7         | I/O      | High              | Alpha Data bus. These pins connect to the VRAM data   |  |  |

| 4    | KOUT6         | I/O      | High              | pins.                                                 |  |  |

| 3    | KOUT5         | I/O      | High              | •                                                     |  |  |

| 100  | KOUT4         | I/O      | High              |                                                       |  |  |

| 99   | KOUT3         | I/O      | High              |                                                       |  |  |

| 98   | KOUT2         | I/O      | High              |                                                       |  |  |

| 97   | KOUT1         | I/O      | High              |                                                       |  |  |

| 96   | KOUT0         | I/O      | High              |                                                       |  |  |

## 69004 VGA / Video Interface

| Pin# | Pin Name Type | ActiveDo | ActiveDescription |                                                                                        |  |  |

|------|---------------|----------|-------------------|----------------------------------------------------------------------------------------|--|--|

| 65   | YRIN0         | In       | Both              | Luminance/Red Data from the digital video source. This                                 |  |  |

| 64   | YRIN1         | In       | Both              | data is buffered and stored in the VRAM for Video                                      |  |  |

| 63   | YRIN2         | In       | Both              | output.                                                                                |  |  |

| 62   | YRIN3         | In       | Both              | •                                                                                      |  |  |

| 61   | YRIN4         | In       | Both              |                                                                                        |  |  |

| 60   | YRIN5         | In       | Both              |                                                                                        |  |  |

| 59   | YRIN6         | In       | Both              |                                                                                        |  |  |

| 58   | YRIN7         | In       | Both              |                                                                                        |  |  |

| 57   | CGIN0         | In       | Both              | Chrominance/Green Data from the digital video source.                                  |  |  |

| 56   | CGIN1         | In       | Both              | This data is buffered and stored in the VRAM for                                       |  |  |

| 55   | CGIN2         | In       | Both              | Video output.                                                                          |  |  |

| 54   | CGIN3         | In       | Both              |                                                                                        |  |  |

| 51   | CGIN4         | In       | Both              |                                                                                        |  |  |

| 50   | CGIN5         | In       | Both              |                                                                                        |  |  |

| 49   | CGIN6         | In       | Both              |                                                                                        |  |  |

| 48   | CGIN7         | In       | Both              | 4° 6' 7' 0' 7                                                                          |  |  |

| 47   | BIN0          | In 4     | Both              | Blue Data from the digital video source. This data is                                  |  |  |

| 46   | BIN1          | In 🐀     | Both              | buffered and stored in the VRAM for Video output.                                      |  |  |

| 45   | BIN2          | In       | Both              |                                                                                        |  |  |

| 44   | BIN3          | In       | Both              |                                                                                        |  |  |

| 43   | BIN4          | In       | Both              |                                                                                        |  |  |

| 42   | BIN5          | In       | Both              |                                                                                        |  |  |

| 41   | BIN6          | In       | Both              |                                                                                        |  |  |

| 39   | BIN7          | In       | Both              |                                                                                        |  |  |

| 114  | XCLK          | In       | Both              | Video Data Clock. This clock is to latch the Video data from the digital video source. |  |  |

## 69004 Inter-Chip, Power, and Ground

| Pin#                                  | Pin Name Type | ActiveDescription |          |                                                       |  |

|---------------------------------------|---------------|-------------------|----------|-------------------------------------------------------|--|

| 6                                     | IFXYW         | Out               | Both     | Inter-Chip control signals. These pins connect to the |  |

| 7                                     | IFHBL         | Out               | Both     | corresponding pins on the 69003.                      |  |

| 9                                     | IHBL          | In                | Both     | 1 61                                                  |  |

| 10                                    | IXYW          | In                | Both     |                                                       |  |

| 11                                    | IDTC          | In                | Both     |                                                       |  |

| 12                                    | IEWR          | In                | Both     |                                                       |  |

| 13                                    | IWBM          | In                | Both     |                                                       |  |

| 14                                    | IAQREQ        | In                | Both     |                                                       |  |

| 15                                    | IWR           | In                | Both     |                                                       |  |

| 16                                    | IRD           | In                | Both     |                                                       |  |

| 17                                    | IAD2          | In                | Both     |                                                       |  |

| 18                                    | IAD1          | In                | Both     |                                                       |  |

| 19                                    | IAD0          | In                | Both     |                                                       |  |

| 2<br>29<br>52<br>79                   | VCC           | Pwr               | 5        | + 5V Power Pins                                       |  |

| 1<br>28<br>40<br>53<br>68<br>80<br>90 | GND           | Pwr               | 50<br>73 | Ground Pins                                           |  |

| 67<br>66                              | NC0<br>NC1    | -3                | 7. ·     | Reserved. These pins should be left unconnected.      |  |

## **Registers**

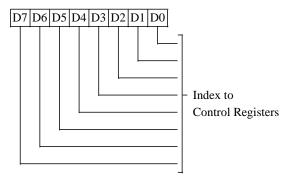

#### REGISTER ADDRESSING

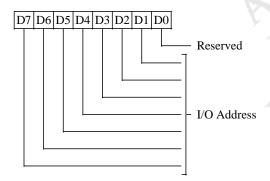

The address location of the PC Video Pro control registers is determined by the status of the CS/ input at RESET. If the CS/ input is low on the falling edge of RESET, then PC Video Pro responds to a fixed I/O address, 0AD6h, 0AD7h. If CS/ is inactive (high) then a programmable address is used. The value present on the data bus during the first valid I/O write (CS/=0, IOWR/=0) following a RESET cycle, is loaded into the Programmed I/O Address Register bits 7:0. This value is then used to determine the I/O address location for the PC Video Pro registers. Since PC Video Pro always occupies two consecutive I/O addresses, bit-0 of this register is ignored. The least significant 8 bits of the I/O address are determined by the value in the Programmed I/O register. The remaining address bits are then dependent on the external decode logic that generates the CS/ strobe.

The setup and control registers for the PC Video Prochip occupy two consecutive address locations. The first or even location contains an index register. The index register determines or "points" to all the other registers. The second or odd location is the data port for the selected register. To access a PC Video Proregister, the index value for the desired register is written to the index register. The data for that register may then be read or written at the data register location.

There are four groups of control registers inside the PC Video Pro chip. They are CPU interface, General Purpose I/O control, Video Acquisition, and Display Window control. All registers are read/write once PC Video Pro has been enabled using bit-0 of the Global Enable Register.

#### **CPU INTERFACE REGISTERS**

These registers are used to enable/disable PC Video Pro, store the I/O address location, specify the memory address and configuration, set the buffer memory write mask and service interrupts. Bit 0 of the Global Enable Register (Index: FFh) must be set to '1' before any other registers may be read or written. This register and the Index Register are write-only until this bit is set.

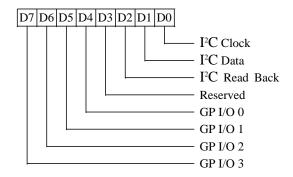

#### GENERAL PURPOSE I/O REGISTERS

These registers control the General Purpose I/O pins and the FC bus interface.

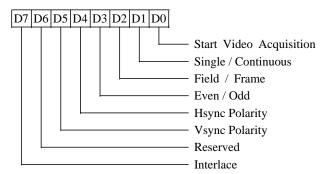

## VIDEO ACQUISITION REGISTERS

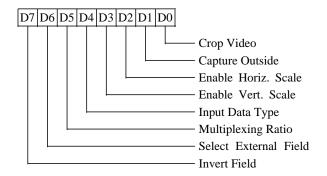

These register are used to control acquisition of a live motion video data stream. They provide data on the current acquisition status and control the input acquisition window, scaling and storage location in memory.

#### **DISPLAY WINDOW REGISTERS**

These registers are used to control the output video data stream and color keying. They provide control of the output window location and size, data start location (panning), shift clock and analog multiplexer skew and VGA color key and mask.

## **Control Registers**

| Register<br>Mnemonic | Register<br>Group                    | Index                                                    | I/O<br>Access | State After<br>Reset | Page                                                                                                    |    |

|----------------------|--------------------------------------|----------------------------------------------------------|---------------|----------------------|---------------------------------------------------------------------------------------------------------|----|

| RX                   |                                      | Register Name  Control Register Index                    |               | RW                   | XXXXXXX                                                                                                 | 25 |

| R00                  | CPU Interface                        | I/O Address                                              | 00h           | RW                   | 1101110 -                                                                                               | 25 |

| R01                  | CPU Interface                        | Memory Access                                            | 01h           | RW                   | 000000                                                                                                  | 25 |

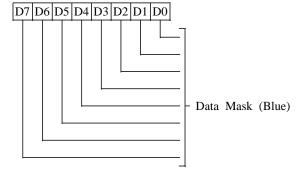

| R04                  | CPU Interface                        | Data Mask, Blue Data                                     | 04h           | RW                   | x x x x x x x x                                                                                         | 25 |

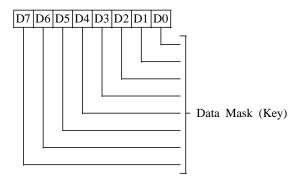

| R05                  | CPU Interface                        | Data Mask, Key Data                                      | 05h           | RW                   | XXXXXXXX                                                                                                | 26 |

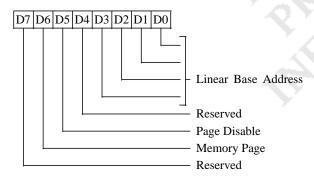

| R06                  | CPU Interface                        | Linear Memory Base Address                               | 06h           | RW                   | 1 1 1 1 1                                                                                               | 26 |

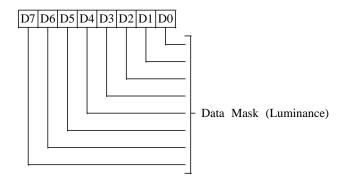

| R07                  | CPU Interface                        | Data Mask, Luminance Data                                | 07h           | RW                   | x x x x x x x x                                                                                         | 26 |

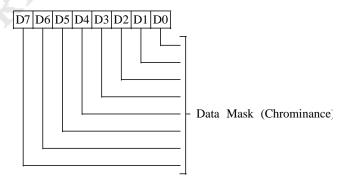

| R08                  | CPU Interface                        | Data Mask, Chrominance Data  Data Mask, Chrominance Data | 08h           | RW                   | X X X X X X X X                                                                                         | 26 |

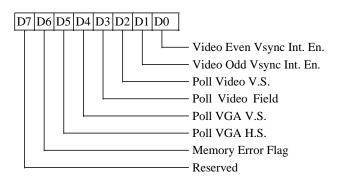

| R09                  | CPU Interface                        | Interrupt Mask                                           | 09h           | RW                   | - RRRRR 0 0                                                                                             | 27 |

|                      |                                      | •                                                        |               |                      |                                                                                                         |    |

| R10                  | G.P. I/O                             | General Purpose I/O 0                                    | 10h           | External             |                                                                                                         | 28 |

| R11                  | G.P. I/O                             | General Purpose I/O 1                                    | 11h           | External             |                                                                                                         | 28 |

| R12                  | G.P. I/O                             | General Purpose I/O 2                                    | 12h           | External             |                                                                                                         | 28 |

| R13                  | G.P. I/O                             | General Purpose I/O 3                                    | 13h           | External             |                                                                                                         | 28 |

| R18                  | G.P. I/O                             | General Purpose I/O Control                              | 18h           | RW                   | 00000011                                                                                                | 28 |

| R20                  | Video Acquisition                    | Video Acquisition Mode                                   | 20h           | RW                   | 0 - 0 0 0 0 0 0                                                                                         | 29 |

| R21                  | Video Acquisition                    | Acquisition Window Control                               | 21h           | RW                   | x x x x x x x x                                                                                         | 29 |

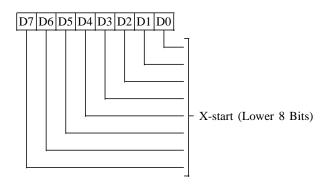

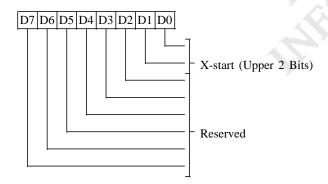

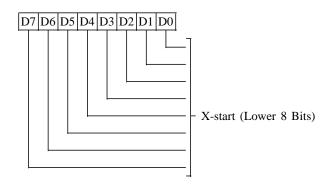

| R22                  | Video Acquisition                    | Acquisition Window, X-start Low                          | 22h           | RW                   | x x x x x x x x                                                                                         | 30 |

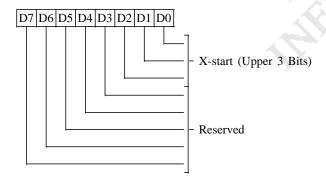

| R23                  | Video Acquisition                    | Acquisition Window, X-start High                         | 23h           | RW                   | X X                                                                                                     | 30 |

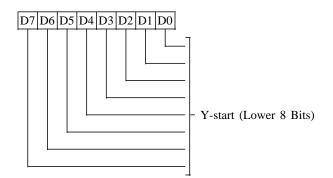

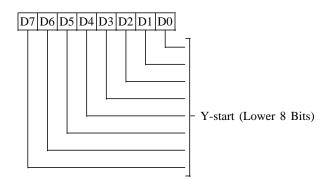

| R24                  | Video Acquisition                    | Acquisition Window, Y-start Low                          | 24h           | RW                   | x x x x x x x x                                                                                         | 30 |

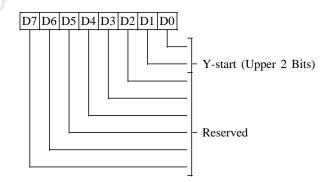

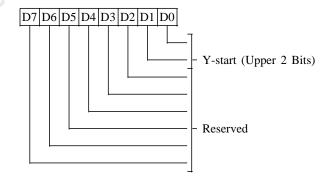

| R25                  | Video Acquisition                    | Acquisition Window, Y-start High                         | 25h           | RW                   | x x                                                                                                     | 30 |

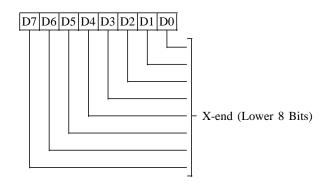

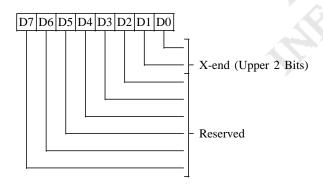

| R26                  | Video Acquisition                    | Acquisition Window, X-end Low                            | 26h           | RW                   | x x x x x x x x                                                                                         | 31 |

| R27                  | Video Acquisition                    | Acquisition Window, X-end High                           | 27h           | RW                   | X X                                                                                                     | 31 |

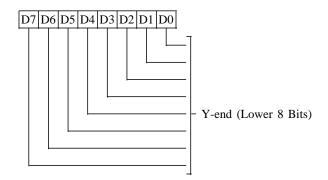

| R28                  | Video Acquisition                    | Acquisition Window, Y-end Low                            | 28h           | RW                   | x x x x x x x x                                                                                         | 31 |

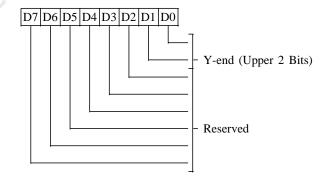

| R29                  | Video Acquisition                    | Acquisition Window, Y-end High                           | 29h           | RW                   | X X                                                                                                     | 31 |

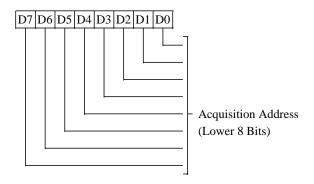

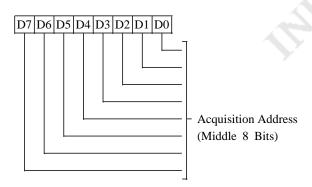

| R2A                  | Video Acquisition                    | Acquisition Address, Low                                 | 2Ah           | RW                   | X X X X X X X X                                                                                         | 32 |

| R2B                  | Video Acquisition                    | Acquisition Address, Middle                              | 2Bh           | RW                   | XXXXXXXX                                                                                                | 32 |

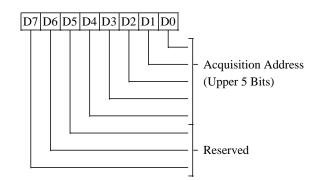

| R2C                  | Video Acquisition                    | Acquisition Address, High                                | 2Ch           | RW                   | X X X X X                                                                                               | 32 |

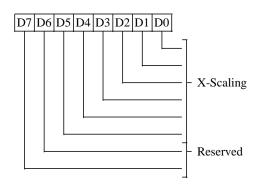

| R2D                  | Video Acquisition                    | Acquisition Horizontal Scale                             | 2Dh           | RW                   | X X X X X X                                                                                             | 33 |

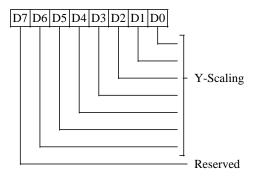

| R2E                  | Video Acquisition                    | Acquisition Vertical Scale                               | 2Eh           | RW                   | - x x x x x x x                                                                                         | 33 |

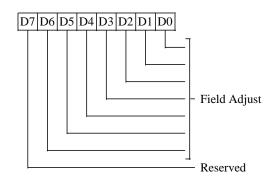

| R2F                  | Video Acquisition                    | Scaling Field Adjust                                     | 2Fh           | RW                   | - X X X X X X X                                                                                         | 33 |

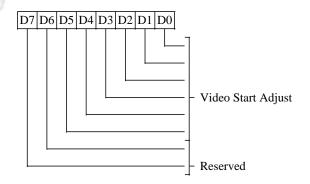

| R30                  | Video Acquisition  Video Acquisition | Input Video Start                                        | 30h           | RW                   |                                                                                                         | 33 |

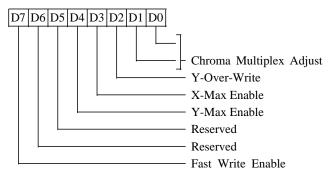

| R38                  | Video Acquisition  Video Acquisition | Scaling Control                                          | 38h           | RW                   | x x x x x x<br>0 0 0 0 0 0                                                                              | 34 |

|                      | *                                    |                                                          |               |                      |                                                                                                         |    |

| R40                  | Display Window                       | Display Area Control                                     | 40h           | RW                   | 0 0 0 0 0 0 0 0                                                                                         | 34 |

| R41                  | Display Window                       | Window X-Start, Low                                      | 41h           | RW                   | x x x x x x x x                                                                                         | 35 |

| R42                  | Display Window                       | Window X-Start, High                                     | 42h           | RW                   | X X                                                                                                     | 35 |

| R43                  | Display Window                       | Window Y-Start, Low                                      | 43h           | RW                   | $\mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} $              | 35 |

| R44                  | Display Window                       | Window Y-Start, High                                     | 44h           | RW                   | X X                                                                                                     | 35 |

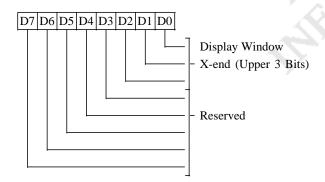

| R45                  | Display Window                       | Window X-End, Low                                        | 45h           | RW                   | X X X X X X X X                                                                                         | 36 |

| R46                  | Display Window                       | Window X-End, High                                       | 46h           | RW                   | X X                                                                                                     | 36 |

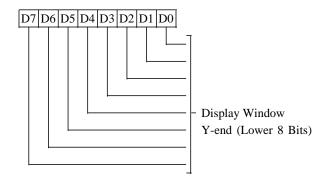

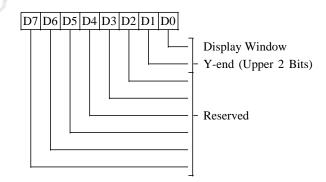

| R47                  | Display Window                       | Window Y-End, Low                                        | 47h           | RW                   | X X X X X X X X                                                                                         | 36 |

| 248                  | Display Window                       | Window Y-End, High                                       | 48h           | RW                   | X X                                                                                                     | 36 |

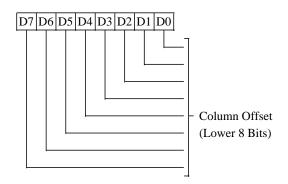

| 249                  | Display Window                       | X-Panning, Low                                           | 49h           | RW                   | $\mathbf{x} \ \mathbf{x} \ \mathbf{x} \ \mathbf{x} \ \mathbf{x} \ \mathbf{x} \ \mathbf{x} \ \mathbf{x}$ | 37 |

| R4A                  | Display Window                       | Y-Panning, Low                                           | 4Ah           | RW                   | $\mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} \mathbf{x} $              | 37 |

| R4B                  | Display Window                       | X,Y-Panning, High                                        | 4Bh           | RW                   | X X X                                                                                                   | 37 |

| R4C                  | Display Window                       | Shift Clock                                              | 4Ch           | RW                   | - x x x x x x x x                                                                                       | 37 |

| R4D                  | Display Window                       | Sync Polarity Register/Zoom                              | 4Dh           | RW                   | - 0 0 0 0 0 0 0                                                                                         | 38 |

| R4E                  | Display Window                       | Color Compare                                            | 4Eh           | RW                   | $x \; x \; x \; x \; x \; x \; x \; x$                                                                  | 38 |

| R4F                  | Display Window                       | Color Mask                                               | 4Fh           | RW                   | $x\;x\;x\;x\;x\;x\;x\;x$                                                                                | 38 |

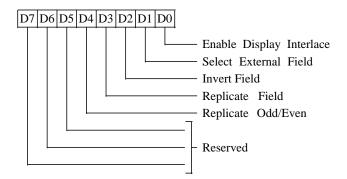

| R50                  | Display Window                       | Interlaced Output Control                                | 50h           | RW                   | x x x x x                                                                                               | 39 |

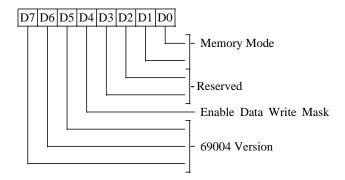

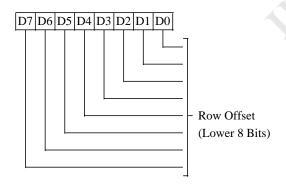

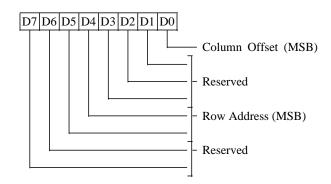

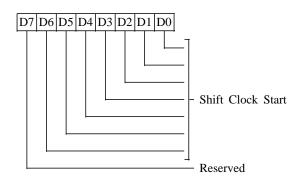

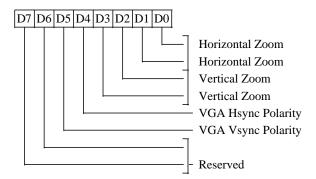

| RFF                  | Misc                                 | Global Enable / Version                                  | FFh           | R7:4 W2:0            | 0010-000                                                                                                | 39 |