## 64201 (WinGlue)

High Performance VGA Controller Support Chip

Data Sheet

September 1992

## PRELIMINARY

#### **Copyright Notice**

Copyright © 1992 Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of Chips and Technologies, Inc.

#### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

#### **Trademark Acknowledgement**

CHIPS and NEAT are registered trademarks of Chips and Technologies, Inc.

CHIPS, CHIPSet, MICROCHIPS, SCAT, NEATsx, LeAPSet, LeAPSetsx, PEAK, CHIPS/230, CHIPS/250, CHIPS/280, CHIPS/450, CHIPSPak, CHIPSPort, CHIPSlink, SMARTMAP, and Wingine are trademarks of Chips and Technologies, Incorporated.

IBM AT, XT, PS/2, Micro Channel, Personal System/2, Enhanced Graphics Adapter, Color Graphics Adapter, Video Graphics Adapter, IBM Color Display, and IBM Monochrome Display are trademarks of International Business Machines.

Hercules is a trademark of Hercules Computer Technology.

MS-DOS and Windows are trademarks of Microsoft, Incorporated.

MultiSync is a trademark of Nippon Electric Company (NEC).

Brooktree and RAMDAC are trademarks of Brooktree Corporation.

Inmos is a trademark of Inmos Corporation.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

#### **Disclaimer**

This document is provided for the general information of the customer. Chips and Technologies, Inc., reserves the right to modify the information contained herein as necessary and the customer should ensure that it has the most recent revision of the data sheet. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

Chips and Technologies, Inc. 3050 Zanker Road San Jose, California 95134 Phone: 408-434-0600 Telex: 272929 CHIPS UR

FAX: 408-434-6452

Title: 64201 (WinGlue) Data Sheet

Publication No.: DS162 Stock No.: 010162-001 Revision No.: 0.3

# 64201 (Winglue) High Performance VGA Controller Support Chip

- Provides interface logic for cost effective connection of the 64200 'Wingine<sup>TM</sup>' Graphics Controller to PEAK/DM for high performance Windows<sup>TM</sup> operation in 386 and 486 systems

- Allows implementation of 1-bank (0.5 MB and 1MB) and 2-bank (2MB) display memory configurations

- Supports 16-bit (0.5 MB) display memory configuration in 32-bit systems

- Implements display memory using VRAMs for very high performance

- Supports split buffer transfers for support of 16bpp 800x600 mode in 1MB of display memory

- Supports interlaced or non-interlaced modes

- Small low-cost package: EIAJ-standard 68-pin PLCC

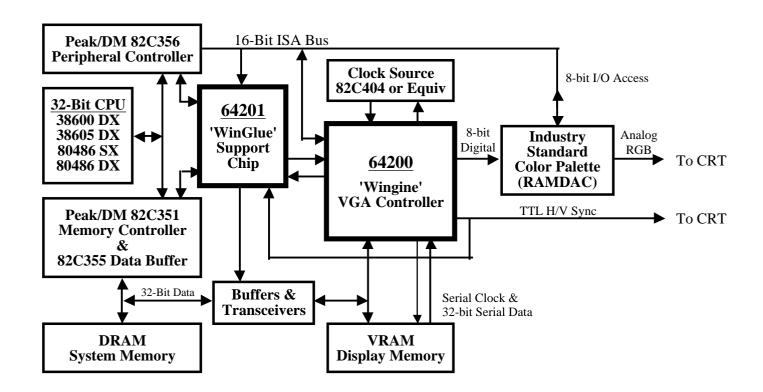

**System Diagram**

## **Revision History**

| Revision | <u>Date</u> | <u>By</u> | Comment                                                                                                  |

|----------|-------------|-----------|----------------------------------------------------------------------------------------------------------|

| 0.1      | 1/8/92      | DH        | Internal Review - Rough Draft and initial release                                                        |

| 0.2      | 1/10/92     | DH        | Added Memory Connection Schematic Fixed pin list (added DTOE3/, changed drive on some pins, fixed typos) |

| 0.3      | 9/14/92     | VS        | Added more details about Winglue operation                                                               |

## **Table of Contents**

| Section                             | <u>Page</u>             |

|-------------------------------------|-------------------------|

| Introduction                        | 5                       |

| Wingine Windows Accelerator WinGlue | 5<br>5<br>5<br>6<br>6   |

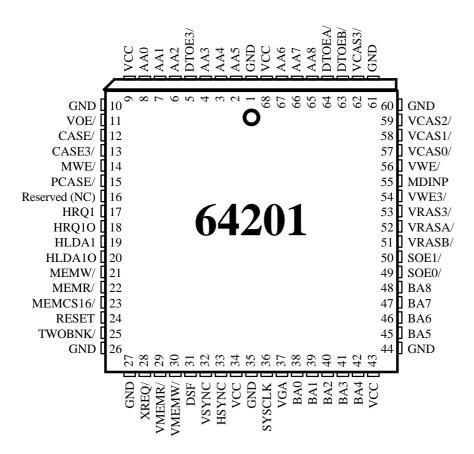

| Pinouts                             | 7                       |

| Pin Diagram                         | 7<br>8<br>9<br>10<br>11 |

| Interface                           | 12                      |

| Section Application Schematic Examples | Page<br>13 |

|----------------------------------------|------------|

| System Bus Interface                   | 15         |

| Mechanical Specifications              | 17         |

| PLCC-68 Package Dimensions             | 17         |

## **List of Figures and Tables**

| Figure                             | <u>Page</u> | <b>Table</b>     | Page |

|------------------------------------|-------------|------------------|------|

| System Diagram                     | 1           | Pin List         | 8    |

| Pinouts                            | 7           | Pin Descriptions | 9    |

| Application Schematic Examples     |             |                  |      |

| System Bus Interface               | 14          |                  |      |

| PEAK/DM Interface (1 Bank)         |             |                  |      |

| Wingine / WinGlue / VRAM Interface |             |                  |      |

| Package Mechanical Dimensions      | 17          |                  |      |

#### Introduction

#### WINGINE WINDOWS ACCELERATOR

The 64200 Wingine Windows Accelerator is a 16-bit ISA-bus VGA with a backend 32-bit to 8-bit pixel serializer. This serializer allows display memory to be implemented with VRAMs for very high graphics performance, while still allowing use of a standard 8-bit RAMDAC for low cost. All VRAM shift-register support and backend pixel path logic is integrated into the Wingine chip.

The Wingine concept maps display memory VRAMs directly into the system CPU address space. The system memory controller is used to control VRAM access in <u>'Windows Acceleration'</u> mode, while control of the VRAM array reverts to Wingine's internal VGA in <u>'VGA'</u> mode for compatibility.

The Wingine VGA is designed to interface directly (i.e., with minimal external logic requirements) to CS4021 CHIPSet and future system logic chipsets from Chips & Technologies. The Wingine can also be interfaced to PEAK/DM chipset with the external 68-pin Winglue chip.

#### WINGLUE

The Winglue chip (64201) integrates all logic required for a PEAK/DM interface. The 64201 provides all the VRAM control functions which are not done by the PEAK/DM memory controller in a Wingine-based system. Winglue performs the following major functions:

- 1. Generate transfer cycles for screen refresh

- 2. Generate VRAM control signals

- 3. Arbitrate with the PEAK/DM memory controller to gain control of the memory bus during transfer cycles

- 4. Generate enable and direction signals for external buffers on the memory bus

- 5. Generate memory command strobes for VGA cycles

- 6. Disable video memory parity check

#### PEAK/DM

Peak/DM is a 386DX System Logic CHIPSet<sup>TM</sup> that can also be used with the 486SX or 486DX. The 82C351 Cache/Memory Controller includes pageinterleaved memory operation that can accomodate a maximum of four 36-bit banks of DRAM. The four banks can be configured as a pair of banks operating page-interleaved with two additional banks operating in page mode but not page-In a Wingine system, these two interleaved. additional banks (normally numbered 2 and 3) can be populated with eight 256Kx4 VRAMs. Typically 1MB of VRAM will be included on the motherboard, allowing fast linear access for screen operations in a GUI environment such as Windows 3.x.

#### WINGLUE OPERATION

Winglue has two modes of operation based on the VGA input from Wingine.

**VGA Mode:** In this mode, Winglue tristates all the VRAM interface signals. Video memory is disconnected from the PEAK/DM memory controller. The 64200 Wingine chip controls video memory for screen updates and refreshes.

Wingine Mode: In this mode, display memory is accessed as part of system memory by PEAK/DM. Wingine tristates all of its memory interface signals. Winglue controls the external data and address buffers on the memory bus for video memory access. Winglue also performs transfer cycles into the VRAMs when requested by Wingine (when Wingine asserts XREQ/). Display timing and screen formats are determined by the HSYNC, VSYNC, and XREQ/ inputs.

Two types of VRAM operation occur in Wingine mode:

- 1. Video memory is accessed as part of system memory by the processor

- 2. Transfer cycles for display refresh are generated in response to XREQ/ from Wingine

#### **Processor VRAM Access**

Winglue generates enable and direction control signals for external buffers on the memory interface. There are two data tranceivers and two address buffers on the memory bus. One buffer is required for the memory control signals. In Wingine mode, Winglue asserts the VOE/ output to enable these external buffers allowing the PEAK/DM memory controller to access video memory directly. The 64201 also generates the MDINP/ signal for controlling the direction of the external data tranceivers.

#### **Display Transfer Cycles**

Winglue performs transfer cycles to video memory by obtaining control of the memory bus from the PEAK/DM memory controller. The 64201 does all the necessary arbitration with PEAK/DM to gain control of the memory bus.

The Winglue transfer controller arbitrates in a similar manner to Bus Master and DMA devices. If both a Bus Master/DMA and Winglue attempt to acquire the local bus at the same time, they will be allowed to transfer concurrently.

Due to possible contention in display memory, a bus master/DMA cannot transfer data to/from display memory in Wingine mode. Bus master/DMA transfers to/from display memory are permitted in VGA mode.

### **Pinouts**

## **Pin List**

| Pin Name                                                    | Pin #                                              | Dir                                                  | Drive                                                |

|-------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| AA0<br>AA1<br>AA2<br>AA3<br>AA4<br>AA5<br>AA6<br>AA7<br>AA8 | 8<br>7<br>6<br>4<br>3<br>2<br>67<br>66<br>65       | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | 4mA<br>4mA<br>4mA<br>4mA<br>4mA<br>4mA<br>4mA<br>4mA |

| BA0<br>BA1<br>BA2<br>BA3<br>BA4<br>BA5<br>BA6<br>BA7<br>BA8 | 38<br>39<br>40<br>41<br>42<br>45<br>46<br>47<br>48 | Out              | 4mA<br>4mA<br>4mA<br>4mA<br>4mA<br>4mA<br>4mA<br>4mA |

| CASE/<br>CASE3/                                             | 12<br>13                                           | In<br>In                                             |                                                      |

| DSF                                                         | 31                                                 | Out                                                  | 8mA                                                  |

| DTOEA/<br>DTOEB/<br>DTOE3/                                  | 64<br>63<br>5                                      | Out<br>Out<br>Out                                    | 4mA<br>4mA<br>8mA                                    |

| GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND        | 1<br>10<br>26<br>27<br>35<br>44<br>60<br>61        | <br><br><br><br>                                     | <br><br><br><br><br>                                 |

| HLDA1<br>HLDA1O                                             | 19<br>20                                           | In<br>Out                                            | 4mA                                                  |

| HRQ1<br>HRQ1O                                               | 17<br>18                                           | In<br>Out                                            | 4mA                                                  |

| HSYNC                                                       | 33                                                 | In                                                   |                                                      |

| MEMCS16/                                                    | 23                                                 | In                                                   |                                                      |

| Pin Name                             |      | Pin#                 | Dir                      | Drive                    |

|--------------------------------------|------|----------------------|--------------------------|--------------------------|

| MDINP                                |      | 55                   | Out                      | 4mA                      |

| MEMR/<br>MEMW/                       |      | 22<br>21             | In<br>In                 |                          |

| MWE/                                 |      | 14                   | In                       |                          |

| PCASE/                               |      | 15                   | Out                      | 4mA                      |

| RESET                                |      | 24                   | In                       |                          |

| SOE0/<br>SOE1/                       |      | 49<br>50             | Out<br>Out               | 8mA<br>8mA               |

| SYSCLK                               |      | 36                   | In                       |                          |

| TWOBNK/                              |      | 25                   | In                       |                          |

| VCAS0/<br>VCAS1/<br>VCAS2/<br>VCAS3/ |      | 57<br>58<br>59<br>62 | Out<br>Out<br>Out<br>Out | 4mA<br>4mA<br>4mA<br>4mA |

| VCC<br>VCC<br>VCC<br>VCC             |      | 9<br>34<br>43<br>68  | <br><br>                 | <br><br>                 |

| VGA                                  |      | 37                   | In                       |                          |

| VMEMR/<br>VMEMW/                     |      | 29<br>30             | Out<br>Out               | 4mA<br>4mA               |

| VOE/                                 |      | 11                   | Out                      | 8mA                      |

| VRASA/<br>VRASB/                     |      | 52<br>51             | I/O<br>Out               | 4mA<br>4mA               |

| VRAS3/                               |      | 53                   | I/O                      | 8mA                      |

| VSYNC                                |      | 32                   | In                       |                          |

| VWE/<br>VWE3/                        |      | 56<br>54             | Out<br>Out               | 8mA<br>8mA               |

| XREQ/                                |      | 28                   | In                       |                          |

| Reserved                             | (NC) | 16                   |                          |                          |

#### PIN DESCRIPTIONS System Interface

| Pin# | Pin Name | Type | Active | Description                                                                                                                                                                                                                |

|------|----------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36   | SYSCLK   | In   | High   | System clock. Used to synchronize internal operations and drive internal state machines. Can be asynchronous to VGA clocks or processor SYSCLK or CLK2. Should be the highest frequency available 40MHz (and 16MHz).       |

| 24   | RESET    | In   | High   | ISA bus reset. Used to initialize internal state.                                                                                                                                                                          |

| 25   | TWOBNK/  | In   | Low    | Two bank mode (static configuration input)                                                                                                                                                                                 |

| 17   | HRQ1     | In   | High   | Hold request in (from PEAK/DM 82C356 pin 142)                                                                                                                                                                              |

| 18   | HRQ1O    | Out  | High   | Hold request out (to PEAK/DM 82C351 pin 74)                                                                                                                                                                                |

| 19   | HLDA1    | In   | High   | Hold acknowledge in (from PEAK/DM 82C351 pin 76)                                                                                                                                                                           |

| 20   | HLDA1O   | Out  | High   | Hold acknowledge out (to PEAK/DM 82C356 pin 66)                                                                                                                                                                            |

|      |          |      |        |                                                                                                                                                                                                                            |

| 21   | MEMW/    | In   | Low    | ISA bus memory write strobe (from 82C356 pin 5)                                                                                                                                                                            |

| 22   | MEMR/    | In   | Low    | ISA bus memory read strobe (from 82C356 pin 6)                                                                                                                                                                             |

| 23   | MEMCS16/ | In   | Low    | Memory Select 16 from VGA address decode logic. Should be asserted when LA23-17 = 0000101 (binary), i.e., address space 0Axxxx and 0Bxxxx.                                                                                 |

|      |          |      |        |                                                                                                                                                                                                                            |

| 12   | CASE/    | In   | Low    | System memory column address strobe enable for first bank of VRAMs. Driven by the 82C351 RAS5/ output (pin 133).                                                                                                           |

| 13   | CASE3/   | In   | Low    | System memory column address strobe enable for second bank of VRAMs. Driven by the 82C351 RAS7/output (pin 135).                                                                                                           |

| 14   | MWE/     | In   | Low    | System memory write enable. Driven by the 82C351 DWE/ output (pin 101), typically buffered since this same pin also drives multiple system memory inputs.                                                                  |

| 15   | PCASE/   | Out  | Low    | Parity CAS Enable. Used with one 74F32 package to gate CAS0-3/ from the 82C351 CPU/Cache/DRAM Controller pins 116-119 to the 82C355 Data Buffer pins 69-72. Used to disable parity checking for display memory VRAM array. |

**Note:** Pin names in parentheses (...) indicate alternate functions

#### PIN DESCRIPTIONS

#### **Graphics Controller Interface**

| Pin# | Pin Name | Type | Active | Description                                                                                                                                       |

|------|----------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 29   | VMEMR/   | Out  | Low    | VGA memory read strobe (to 64200 pin 25)                                                                                                          |

| 30   | VMEMW/   | Out  | Low    | VGA memory write strobe (to 64200 pin 26)                                                                                                         |

|      |          |      |        |                                                                                                                                                   |

| 37   | VGA      | In   | High   | Display mode input from 64200 pin 97. Controlled by 64200 Master Control register bit-0 (inverted). Active in VGA mode, inactive in Wingine mode. |

| 28   | XREQ/    | In   | Low    | Transfer request from 64200 pin 74 (used to initiate VRAM data transfer cycles)                                                                   |

| 33   | HSYNC    | In   | High   | Horizontal sync input from 64200 pin 75 (used for odd/even field and interlace detection)                                                         |

| 32   | VSYNC    | In   | High   | Vertical sync input from 64200 pin 76 (used for odd/even field and interlace detection and to reset the transfer address counter)                 |

Note: HSYNC and VSYNC polarities are programmable via the VGA MSR (Miscellaneous Output Register) bits 6 and 7. In VGA 400-line modes (31.5KHz / 70 Hz monitor timing, typically used for VGA text modes), HSYNC is programmed to negative polarity. In VGA 480-line modes (31.5 KHz / 60 Hz monitor timing for 640x480 graphics modes), both sync signals become negitive polarity. Typically, VGA 800x600 modes also use negative polarity sync signals, but typical multisync monitors will work with either polarity. All high resolution modes (1024x768 and higher, interlace and non-interlace) use positive polarity syncs. The 64201 asssumes positive polarity sync signals in 'Wingine' mode (it ignores the sync signals in VGA modes).

**Note:** Pin names in parentheses (...) indicate alternate functions

#### PIN DESCRIPTIONS

#### **Power and Ground**

| Pin# | Pin Name      | Type | Active | Description               |

|------|---------------|------|--------|---------------------------|

| 9    | VCC           | In   | n/a    | +5V                       |

| 34   | VCC           | In   | n/a    |                           |

| 43   | VCC           | In   | n/a    |                           |

| 68   | VCC           | In   | n/a    |                           |

| 1    | GND           | In   | n/a    | Ground                    |

| 10   | GND           | In   | n/a    |                           |

| 26   | GND           | In   | n/a    |                           |

| 27   | GND           | In   | n/a    |                           |

| 35   | GND           | In   | n/a    |                           |

| 44   | GND           | In   | n/a    |                           |

| 60   | GND           | In   | n/a    |                           |

| 61   | GND           | In   | n/a    |                           |

| 16   | Reserved (NC) |      |        | Reserved (do not connect) |

**Note:** Pin names in parentheses (...) indicate alternate functions

#### PIN DESCRIPTIONS

#### **Display Memory Interface**

| Pin#                                               | Pin Name                                                    |                                                | Type                                    | Active                                                       | Description                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------|-------------------------------------------------------------|------------------------------------------------|-----------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8<br>7<br>6<br>4                                   | AA0<br>AA1<br>AA2<br>AA3                                    | (TST0)<br>(TST1)<br>(TST2)<br>(TST3)           | I/O<br>I/O<br>I/O<br>I/O                | High<br>High<br>High<br>High                                 | Address bus for VRAM bytes 0 & 2 (also called VRAMs 'A' and 'C' in the application schematics). These pins are also used as test inputs.                                                                                                                                                                                                                                 |

| 3<br>2<br>67<br>66<br>65                           | AA4<br>AA5<br>AA6<br>AA7<br>AA8                             | (TST4)<br>(TST5)<br>(TST6)<br>(TST7)<br>(TST8) | I/O<br>I/O<br>I/O<br>I/O<br>I/O         | High<br>High<br>High<br>High<br>High                         | Note: Byte 0 (bits 0-7) = VRAM 'A'<br>Byte 1 (bits 8-15) = VRAM 'B'<br>Byte 2 (bits 16-23) = VRAM 'C'<br>Byte 3 (bits 24-31) = VRAM 'D'                                                                                                                                                                                                                                  |

| 38<br>39<br>40<br>41<br>42<br>45<br>46<br>47<br>48 | BA0<br>BA1<br>BA2<br>BA3<br>BA4<br>BA5<br>BA6<br>BA7<br>BA8 | (1316)                                         | Out | High<br>High<br>High<br>High<br>High<br>High<br>High<br>High | Address bus for VRAM bytes 1 & 3 (also called VRAMs 'B' and 'D' in the application schematics)  Note: VGA planes 0-1 are implemented in VRAM C and VGA planes 2-3 are implemented in VRAM D in 32-bit system configurations. VRAMs A and B are only accessible to the system in 32-bit 'Wingine' mode.                                                                   |

| 52<br>51<br>53                                     | VRASA/<br>VRASB/<br>VRAS3/                                  |                                                | Out<br>Out<br>Out                       | Low<br>Low<br>Low                                            | Row address strobe for VRAM bank 0 bytes 0 & 2<br>Row address strobe for VRAM bank 0 bytes 1 & 3<br>Row address strobe for VRAM bank 1                                                                                                                                                                                                                                   |

| 57<br>58<br>59<br>62                               | VCAS0/<br>VCAS1/<br>VCAS2/<br>VCAS3/                        |                                                | Out<br>Out<br>Out<br>Out                | Low<br>Low<br>Low<br>Low                                     | Column address strobe for VRAM byte 0 (VRAM A)<br>Column address strobe for VRAM byte 1 (VRAM B)<br>Column address strobe for VRAM byte 2 (VRAM C)<br>Column address strobe for VRAM byte 3 (VRAM D)                                                                                                                                                                     |

| 56<br>54                                           | VWE/<br>VWE3/                                               |                                                | Out<br>Out                              | Low<br>Low                                                   | Write enable for VRAM bank 0 all bytes<br>Write enable for VRAM bank 1 all bytes                                                                                                                                                                                                                                                                                         |

| 64<br>63<br>5                                      | DTOEA/<br>DTOEB/<br>DTOE3/                                  |                                                | Out<br>Out<br>Out                       | Low<br>Low<br>Low                                            | Data transfer / output enable for bank 0 bytes 0 & 2 Data transfer / output enable for bank 0 bytes 1 & 3 Data transfer / output enable for VRAM bank 1                                                                                                                                                                                                                  |

| 31                                                 | DSF                                                         |                                                | Out                                     | High                                                         | VRAM Special Function (split-buffer transfer control)                                                                                                                                                                                                                                                                                                                    |

| 49<br>50                                           | SOE0/<br>SOE1/                                              |                                                | Out<br>Out                              | Low<br>Low                                                   | Serial output enable for VRAM bank 0<br>Serial output enable for VRAM bank 1                                                                                                                                                                                                                                                                                             |

| 11                                                 | VOE/                                                        |                                                | Out                                     | Low                                                          | VRAM Output Enable. Deasserted in VGA mode or during data transfer cycles. Asserted in Wingine mode to allow the CPU to access the VRAMs as part of system memory. Connect this pin to the output enables of the 74F244/245 data/address/control signal isolation buffers (located between the VRAMs and the system to allow the 64200 to access the VRAMs in VGA mode). |

| 55                                                 | MDINP                                                       |                                                | Out                                     | High                                                         | VRAM Data Direction. High for memory reads, low for memory writes. Connect this pin to the direction control inputs of the 74F245 data isolation buffers.                                                                                                                                                                                                                |