MC68HC05PV8/D REV 1.9

MC68HC05PV8A

Technical Data

HCMOS

Microcontroller Unit

## MC68HC05PV8 MC68HC805PV8 MC68HC05PV8A

Technical Data — Rev 1.9

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and are registered trademarks of Motorola, Inc. DigitalDNA is a trademark of Motorola, Inc.

© Motorola, Inc., 2001

MC68HC(8)05PV8/A — Rev. 1.9

Technical Data

MOTOROLA 3

### **Revision History**

#### **Contents**

| Introduction                                                                                      |

|---------------------------------------------------------------------------------------------------|

| Changes from Rev 1.5 published on September 9th, 1999 to Rev 1.6 published on May 4th, 2000       |

| Changes from Rev 1.6 published on May 4th, 2000 to Rev 1.7 published on December 1st, 2000        |

| Changes from Rev 1.7 published on December 1st, 2000 to Rev 1.8 published on February 20th, 2001  |

| Changes from Rev 1.8 published on February 20th, 2001 to Rev 1.9 published on September 3th, 2001 |

#### Introduction

This section contains the revision history for the MC68HC(8)05PV8/A data book.

## Changes from Rev 1.5 published on September 9th, 1999 to Rev 1.6 published on May 4th, 2000

| Section | Page (in Rev 1.6) | Description of change                     |

|---------|-------------------|-------------------------------------------|

|         |                   | added PV8A functionality, initial release |

## Changes from Rev 1.6 published on May 4th, 2000 to Rev 1.7 published on December 1st, 2000

| Section | Page (in Rev 1.7) | Description of change |

|---------|-------------------|-----------------------|

| 2       | 33                | added note 3          |

## Changes from Rev 1.7 published on December 1st, 2000 to Rev 1.8 published on February 20th, 2001

| Section | Page (in Rev 1.8) | Description of change                  |

|---------|-------------------|----------------------------------------|

| 16.15.1 | 185               | removed PC4 input hysteresis for PV8A  |

| 16.15.1 | 185               | added PC4 input debounce time for PV8A |

# Changes from Rev 1.8 published on February 20th, 2001 to Rev 1.9 published on September 3th, 2001

| Section | Page (in Rev 1.9) | Description of change                          |

|---------|-------------------|------------------------------------------------|

| 1.5     | 30                | added mechanical specification                 |

| 1.7     | 33                | added ordering information                     |

| 16.5    | 176               | filled in typical value for I <sub>SUP12</sub> |

| 16.5    | 176               | added I <sub>SUP4A</sub>                       |

| 16.12   | 185               | added rise time specification on VDD           |

### Technical Data — MC68HC(8)05PV8/A

### **List of Sections**

| Revision History              |

|-------------------------------|

| List of Sections              |

| Table of Contents9            |

| List of Figures               |

| List of Tables                |

| General Description 25        |

| Memory                        |

| CPU and Instruction Set43     |

| Interrupts65                  |

| Resets                        |

| Operating Modes 87            |

| Input/Output Ports            |

| Core Timer                    |

| 16-Bit Programmable Timer 123 |

| Analog to Digital Converter   |

| Pulse Width Modulator 147     |

| Voltage Regulator             |

MC68HC(8)05PV8/A — Rev. 1.9

| EEPROM                    | 157         |

|---------------------------|-------------|

| Program EEPROM            | 163         |

| Fast Parallel Interface   | 169         |

| Electrical Specifications | <b>17</b> 3 |

### **Table of Contents**

### **Section 1. General Description**

| 1.1                                                                | Contents                                                                                                                                                                                             |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2                                                                | Introduction                                                                                                                                                                                         |

| 1.3                                                                | Features                                                                                                                                                                                             |

| 1.4                                                                | Mask Options                                                                                                                                                                                         |

| 1.5                                                                | Pin Assignments29                                                                                                                                                                                    |

| 1.6                                                                | Mechanical Specifications                                                                                                                                                                            |

| 1.7<br>1.7.1<br>1.7.2<br>1.7.2<br>1.7.5<br>1.7.6<br>1.7.7<br>1.7.8 | VDD.       3         OSC1, OSC2.       3         RESET       3         IRQ       3         PA0-PA7/VREFH, VREFL, AN1-6, IN, IIN, OUT       3         PB0-PB4/TCMP1, TCMP2, TCAP1, TCAP2, PWM       3 |

|                                                                    | Section 2. Memory                                                                                                                                                                                    |

| 2.1                                                                | Contents                                                                                                                                                                                             |

| 2.2                                                                | Introduction                                                                                                                                                                                         |

| 2.3                                                                | Registers                                                                                                                                                                                            |

| 2.4                                                                | RAM                                                                                                                                                                                                  |

| 2.5                                                                | Monitor ROM42                                                                                                                                                                                        |

| MC68HC(8)05PV8/A — Rev. 1.9                                        | Technical Data                                                                                                                                                                                       |

| 2.6                                                                         | Program EEPROM/ROM                                                                                                                                             | .42                                          |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2.7                                                                         | EEPROM                                                                                                                                                         | .42                                          |

|                                                                             | Section 3. CPU and Instruction Set                                                                                                                             |                                              |

| 3.1                                                                         | Contents                                                                                                                                                       | .43                                          |

| 3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                     | CPU Registers  Accumulator Index Register Stack Pointer Program Counter                                                                                        | .44<br>.45<br>.45                            |

| 3.2.5                                                                       | Condition Code Register                                                                                                                                        |                                              |

| 3.3                                                                         | Arithmetic/Logic Unit (ALU)                                                                                                                                    | .47                                          |

| 3.4                                                                         | Instruction Set Overview                                                                                                                                       | .48                                          |

| 3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7<br>3.5.8 | Addressing Modes Inherent Immediate Direct Extended Indexed, No Offset Indexed, 8-Bit Offset Indexed,16-Bit Offset. Relative                                   | . 48<br>. 49<br>. 49<br>. 49<br>. 50<br>. 50 |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5                            | Instruction Types  Register/Memory Instructions  Read-Modify-Write Instructions  Jump/Branch Instructions  Bit Manipulation Instructions  Control Instructions | .52<br>.53<br>.54<br>.56                     |

| 3.7                                                                         | Instruction Set Summary                                                                                                                                        | . 58                                         |

### **Section 4. Interrupts**

| 4.1                             | Contents                                 | .65        |

|---------------------------------|------------------------------------------|------------|

| 4.2                             | Introduction                             | .66        |

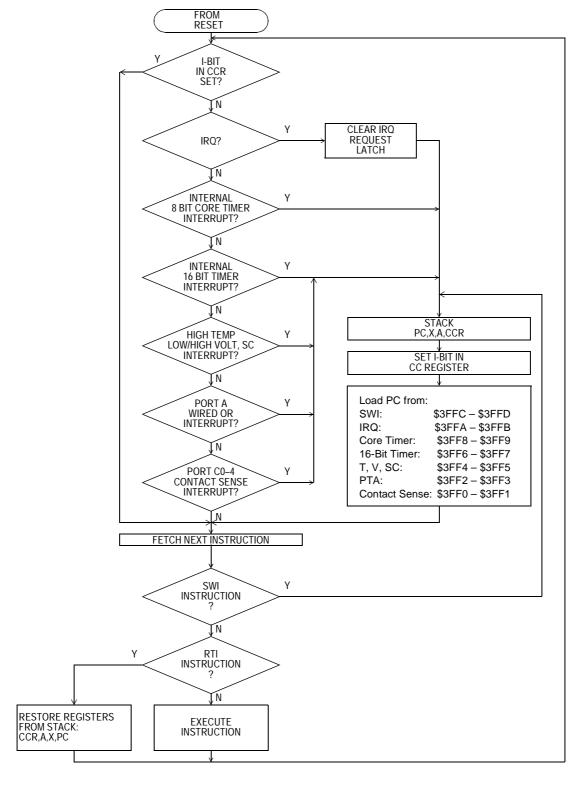

| 4.3                             | CPU Interrupt Processing                 | .66        |

| 4.4                             | Reset Interrupt Sequence                 | .70        |

| 4.5                             | Software Interrupt (SWI)                 | .70        |

| 4.6                             | Hardware Interrupts                      | .70        |

| 4.7                             | External Interrupt (IRQ)                 | .70        |

| 4.8<br>4.8.1                    | 8-Bit Timer Interrupt                    |            |

| 4.9                             | Ambient Exception Interrupts             | .73        |

| 4.10.4.10.2<br>4.10.2<br>4.10.3 | 2 Low Voltage Interrupt                  | .74<br>.74 |

| 4.11                            | Keyboard Interrupts                      | .75        |

| 4.12                            | Port C Contact Sense Interrupt           | .75        |

| 4.13                            | STOP and WAIT Modes                      | .76        |

|                                 | Section 5. Resets                        |            |

| 5.1                             | Contents                                 | .77        |

| 5.2                             | Introduction                             | .77        |

| 5.3                             | Reset status register (RSR)              | .78        |

| 5.4                             | External Reset (RESET)                   | .79        |

| 5.5                             | Internal Resets                          | .80        |

| 5.6                             | Power-On Reset (POR)                     | .80        |

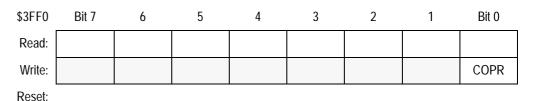

| 5.7                             | Computer Operating Properly Reset (COPR) | .82        |

|                                 |                                          |            |

| 5.7.1<br>5.7.2<br>5.7.3<br>5.7.4<br>5.7.5 | Resetting the COP                                                     |

|-------------------------------------------|-----------------------------------------------------------------------|

| 5.8                                       | Illegal Address Reset84                                               |

| 5.9                                       | Disabled STOP Instruction Reset84                                     |

| 5.10                                      | High Temperature Reset84                                              |

| 5.11                                      | High Voltage Reset                                                    |

| 5.12                                      | Low Voltage Reset                                                     |

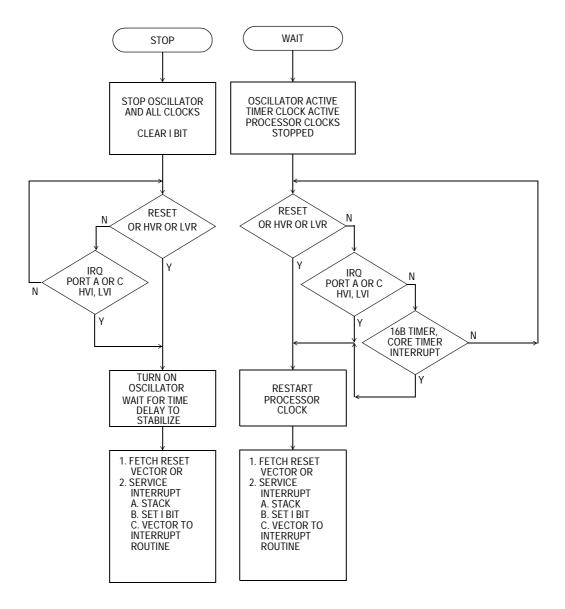

| 5.13                                      | Operation in STOP and WAIT Mode85                                     |

| 5.14<br>5.14.1                            | Clock Monitor Reset (CMR)                                             |

|                                           | Section 6. Operating Modes                                            |

| 6.1                                       | Contents                                                              |

| 6.2                                       | Introduction                                                          |

| 6.3                                       | User mode                                                             |

| 6.4                                       | Monitor Mode                                                          |

| 6.5<br>6.5.1<br>6.5.1.<br>6.5.2           | Low Power Modes88STOP Mode.881 Ultra Low Power Mode.89STOP Recovery89 |

| 6.6                                       | WAIT Mode 91                                                          |

**Technical Data**

### **Section 7. Input/Output Ports**

| 7.1                                                                                  | Contents                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.2                                                                                  | Introduction94                                                                                                                                                                                                                                                                 |

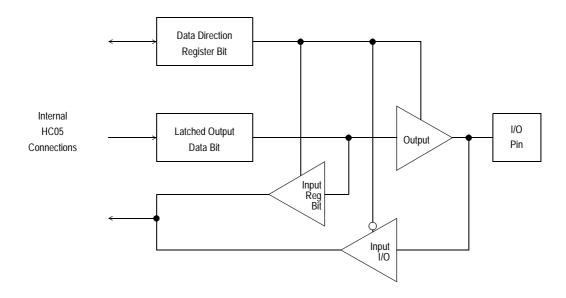

| 7.3                                                                                  | General Input/Output Programming                                                                                                                                                                                                                                               |

| 7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6                            | Port A.95Port A Keyboard Interrupt.96Port A Pull-up Resistors.96Port A Voltage Reference for A/D Converter.96Port A Configuration Register.97Port A Interrupt Status Register.98Operational Amplifier.98                                                                       |

| 7.5<br>7.5.1<br>7.5.2<br>7.5.3                                                       | Port B                                                                                                                                                                                                                                                                         |

| 7.6<br>7.6.1<br>7.6.2<br>7.6.3<br>7.6.4<br>7.6.5<br>7.6.6<br>7.6.7<br>7.6.8<br>7.6.9 | Port C (High Voltage Port)102Port C Timer Channels103Port C PWM Channel103Port C Contact Sense Circuitry103Port C ISO9141 Interface106Port C Low Side Driver107Port C Configuration Register 0109Port C Configuration Register 1113Port C Status Register114MFTEST Register116 |

|                                                                                      | Section 8. Core Timer                                                                                                                                                                                                                                                          |

| 8.1                                                                                  | Contents                                                                                                                                                                                                                                                                       |

| 8.2                                                                                  | Introduction117                                                                                                                                                                                                                                                                |

| 8.3<br>8.3.1<br>8.3.2<br>8.3.3                                                       | Registers                                                                                                                                                                                                                                                                      |

| 8.4                                                                                  | Core Timer During WAIT                  |

|--------------------------------------------------------------------------------------|-----------------------------------------|

| 8.5                                                                                  | Core Timer During STOP                  |

|                                                                                      | Section 9. 16-Bit Programmable Timer    |

| 9.1                                                                                  | Contents                                |

| 9.2                                                                                  | Introduction124                         |

| 9.3<br>9.3.1<br>9.3.2<br>9.3.2<br>9.3.3<br>9.3.3<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6 | Output Compare Registers                |

| 9.4                                                                                  | Timer During WAIT Mode136               |

| 9.5                                                                                  | Timer During STOP Mode136               |

|                                                                                      | Section 10. Analog to Digital Converter |

| 10.1                                                                                 | Contents                                |

| 10.2                                                                                 | Introduction                            |

| 10.3                                                                                 | A/D Principle                           |

| 10.4                                                                                 | A/D Operation                           |

| 10.5                                                                                 | Internal and Master Oscillator139       |

| 10.6<br>10.6.<br>10.6.                                                               | 3 ( )                                   |

| 10.7                                                                                 | A/D During WAIT Mode                    |

| 10.8                                                                                 | A/D During STOP Mode                    |

| Technical Data                                                                       | MC68HC(8)05PV8/A — Rev. 1.9             |

15

| 10.9 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

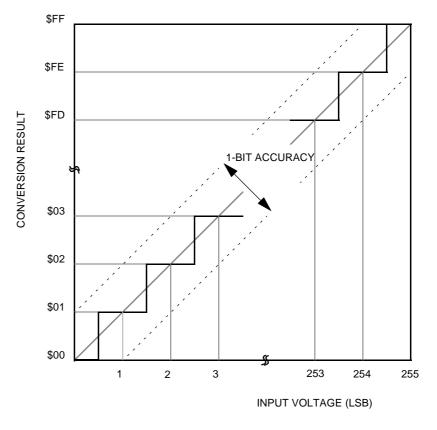

| 10.10 Conversion Accuracy Definitions       144         10.10.1 Transfer Curve       144         10.10.2 Monotonicity       145         10.10.3 Quantization Error       145         10.10.4 Offset Error       146         10.10.5 Gain Scale Error       146         10.10.6 Differential Linearity Error       146         10.10.7 Integral Linearity Error       146         10.10.8 Total Unadjusted Error       146         Section 11. Pulse Width Modulator |

| 11.1 Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11.3 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11.4 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11.4.2 PWM Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11.4.3 PWM Period Register                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11.5 PWM During WAIT Mode                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11.6 PWM During STOP Mode152                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11.7 PWM During Reset                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11.8 Frame Frequency Examples                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Costion 40 Voltone Demulator                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Section 12. Voltage Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12.1 Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12.3 Internal Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12.4 5V Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12.5 Trimming the Voltage Regulator156                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### **Section 13. EEPROM**

| 13.1                                       | Contents                              | .157                 |

|--------------------------------------------|---------------------------------------|----------------------|

| 13.2                                       | Introduction                          | .157                 |

| 13.3                                       | EEPROM Control Register (EEPCR)       | .158                 |

| 13.4                                       | EEPROM Options Register (EEOPR)       | .159                 |

| 13.5<br>13.5.1<br>13.5.2<br>13.5.3<br>13.6 | 2 ERASE Procedure                     | .160<br>.160<br>.160 |

|                                            | Section 14. Program EEPROM            |                      |

| 14.1                                       | Contents                              | .163                 |

| 14.2                                       | Introduction                          |                      |

| 14.3                                       | Programming Register                  | .164                 |

| 14.4                                       | EEPROM Protection Mechanism           | .165                 |

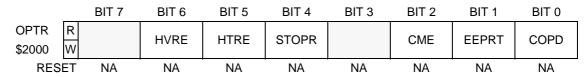

| 14.5                                       | Options Register                      | .166                 |

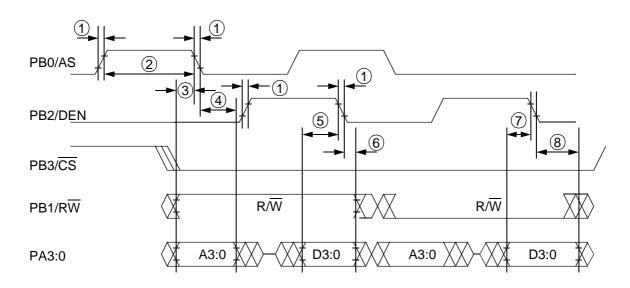

|                                            | Section 15. Fast Parallel Interface   |                      |

| 15.1                                       | Contents                              | .169                 |

| 15.2                                       | Introduction                          | .169                 |

| 15.3<br>15.3.1                             | Description                           |                      |

|                                            | Section 16. Electrical Specifications |                      |

| 16.1                                       | Contents                              | .173                 |

| 16.2                                       | Maximum Ratings                       | .174                 |

| 16.3                                       | Thermal Characteristics               | .175                 |

|                                            | MC68HC(8)05PV8/A — Re                 | ev. 1.9              |

| 16.4                      | Program and Data EEPROM Characteristics175                 |

|---------------------------|------------------------------------------------------------|

| 16.5                      | Supply Current                                             |

| 16.6                      | V <sub>DD</sub> Referenced Pins Electrical Characteristics |

| 16.7                      | Voltage Regulator180                                       |

| 16.8                      | Operational Amplifier182                                   |

| 16.9<br>16.9.1            | Power Supply Monitor                                       |

| 16.10                     | Down Scaler                                                |

| 16.11                     | Die Temperature Monitor                                    |

| 16.12                     | Control Timing                                             |

| 16.13                     | A/D Converter Characteristics                              |

| 16.14                     | Fast Peripheral Interface Timing                           |

| 16.15<br>16.15.<br>16.15. | 3 1 1 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                    |

| 16.15.                    |                                                            |

| 16.15.                    |                                                            |

| 16.15.                    | 5 Low Side Driver (PC5/6, PVSS)                            |

### Technical Data — MC68HC(8)05PV8/A

## **List of Figures**

| Figure                      | Title                                        | Page         |

|-----------------------------|----------------------------------------------|--------------|

| 1-1                         | MC68HC(8)05PV8/A Block Diagram               | 28           |

| 1-2                         | MC68HC(8)05PV8/A Pin Assignments             | 29           |

| 1-3                         | 28-pin SOIC mechanical dimensions            | 30           |

| 2-1                         | MC68HC(8)05PV8/A Memory Map                  | 36           |

| 2-2                         | I/O Register Summary                         |              |

| 2-3                         | I/O Registers \$0000–\$000F                  |              |

| 2-4                         | I/O Registers \$0010–\$001F                  | 40           |

| 2-5                         | I/O Registers \$0020–\$002F                  | 41           |

| 3-1                         | Programming Model                            | 44           |

| 3-2                         | Accumulator                                  | 44           |

| 3-3                         | Index Register                               | 45           |

| 3-4                         | Stack Pointer                                | 45           |

| 3-5                         | Program Counter                              | 46           |

| 3-6                         | Condition Code Register                      | 46           |

| 4-1                         | Interrupt Processing Flowchart               | 69           |

| 4-2                         | System Control Register (SYSCTRL)            | 71           |

| 4-3                         | Interrupt Control Register (INTCR)           | 73           |

| 4-4                         | Interrupt Status Register (INTSR)            | 73           |

| 5-1                         | Reset Status Register (RSR)                  |              |

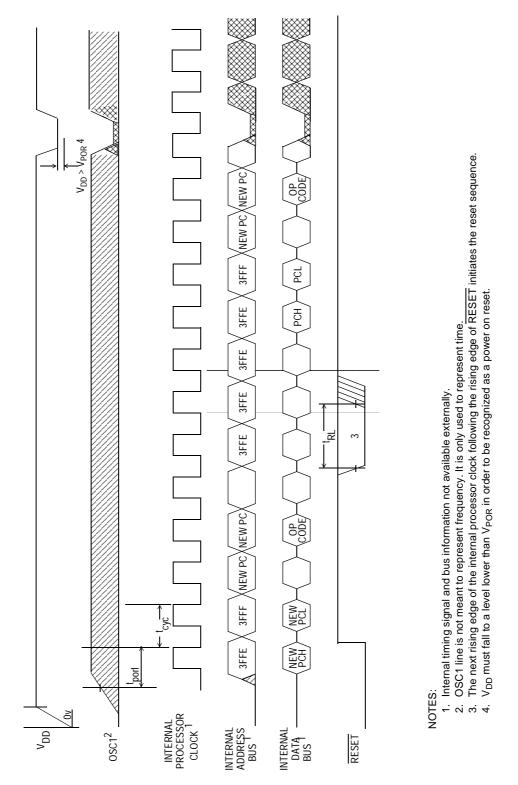

| 5-2                         | RESET and POR Timing Diagram                 |              |

| 5-3                         | COP Watchdog Timer Location Register (COPR). | 84           |

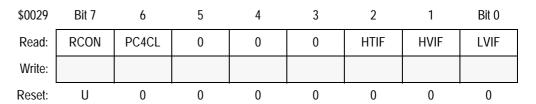

| 5-4                         | Interrupt Status Register (INTSR)            | 86           |

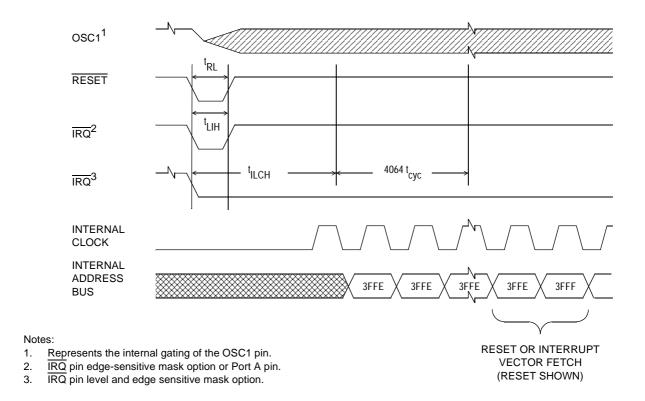

| 6-1                         | Stop Recovery Timing Diagram                 |              |

| 6-2                         | STOP and WAIT Flowcharts                     | 91           |

| 7-1                         | Port I/O Circuitry                           | 95           |

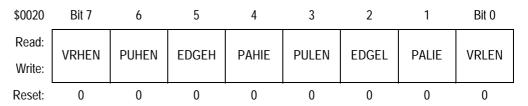

| 7-2                         | Port A Configuration Register (PACFG)        | 97           |

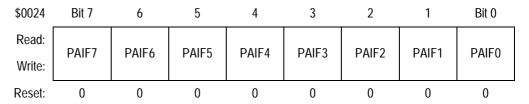

| 7-3                         | Port A Interrupt Status Register (PAISR)     | 98           |

| 7-4                         | Operational Amplifier                        | 99           |

| MC68HC(8)05PV8/A — Rev. 1.9 | Те                                           | chnical Data |

| 7-5  | Typical application: positive vgain amplifier99             |

|------|-------------------------------------------------------------|

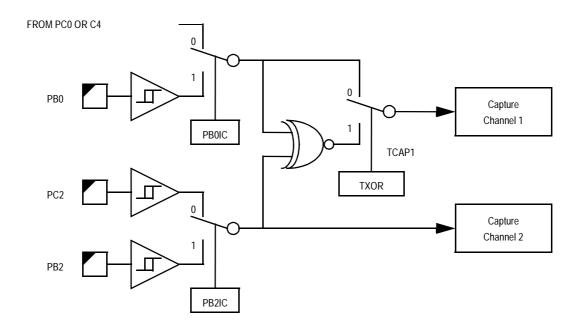

| 7-6  | Mapping Ports to Timer Capture Channels                     |

| 7-7  | I/O Configuration Register (IOCFG)101                       |

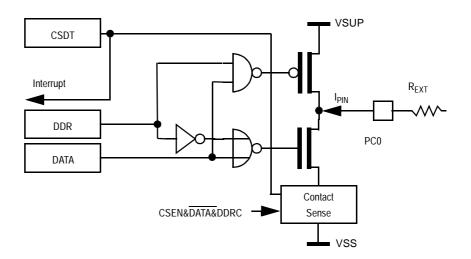

| 7-8  | PC0 Contact Sense Circuitry                                 |

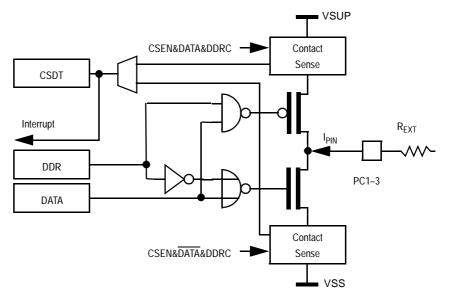

| 7-9  | PC1–3 Contact Sense Circuitry                               |

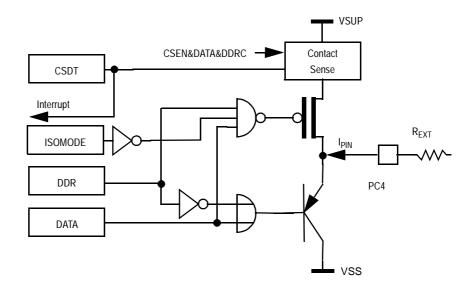

| 7-10 | PC4 Contact Sense Circuitry 68HC(8)05PV8104                 |

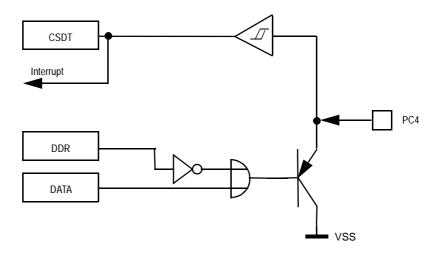

| 7-11 | PC4 Circuitry 68HC05PV8A105                                 |

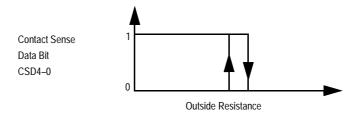

| 7-12 | Principal Characteristic of the Contact Sense Circuitry 106 |

| 7-13 | Interrupt Status Register (INTSR)                           |

| 7-14 | Principle of Port C Low Side Driver                         |

| 7-15 | Short Circuit Diagnostic of Port C Low Side Driver 109      |

| 7-16 | Port C Configuration Register 0 (PCCFG0) 109                |

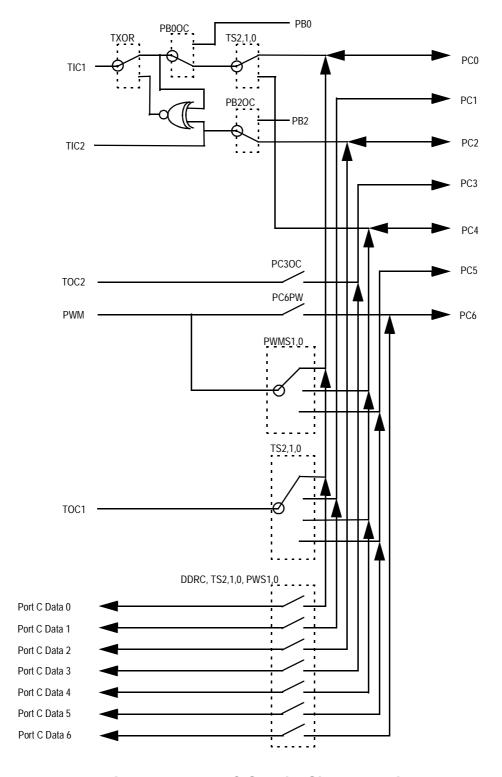

| 7-17 | Port C Special Signal Routing                               |

| 7-18 | Port C Configuration Register 1 (PCCFG1)                    |

| 7-19 | Port C Status Register (PCSTR)114                           |

| 7-20 | MFTEST Register (MFTEST)116                                 |

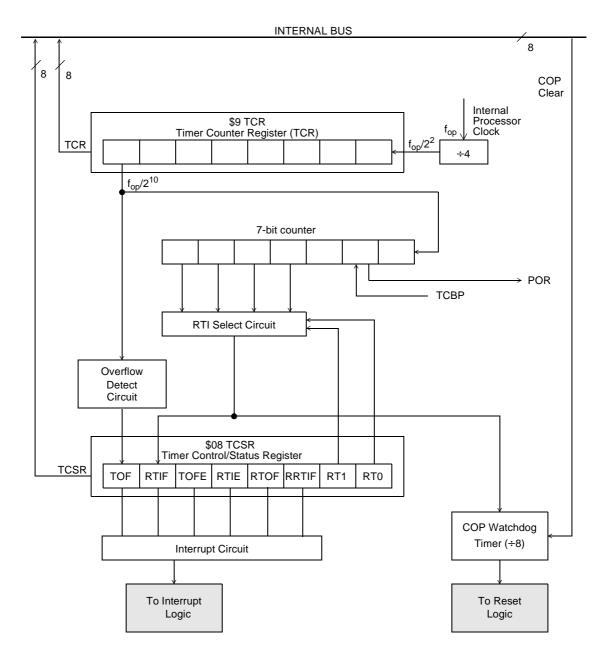

| 8-1  | Core Timer Block Diagram                                    |

| 8-2  | Core Timer Status and Control Register (CTSCR)119           |

| 8-3  | Core Timer Counter Register (CTCR)                          |

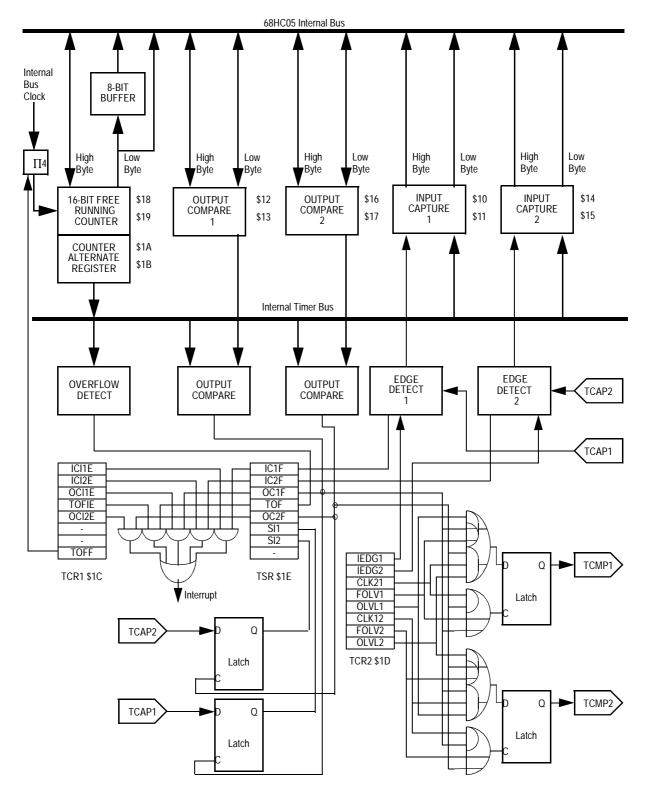

| 9-1  | Timer Block Diagram                                         |

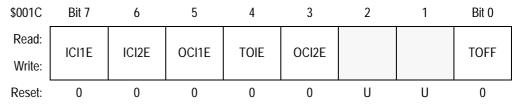

| 9-2  | Timer Control Register 1 (TCR1)                             |

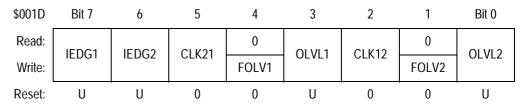

| 9-3  | Timer Control Register 2 (TCR2)                             |

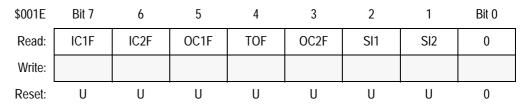

| 9-4  | Timer Status Register 1 (TSR)134                            |

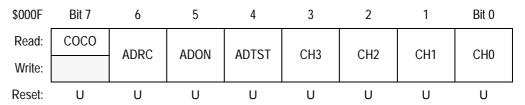

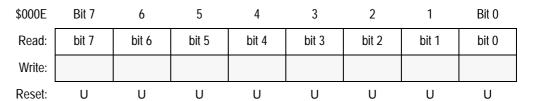

| 10-1 | A/D Status and Control Register (ADSCR)140                  |

| 10-3 | A/D Data Register (ADDR)142                                 |

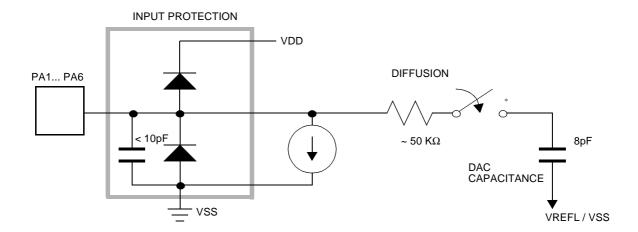

| 10-4 | Electrical Model of an A/D Input Pin144                     |

| 10-5 | Transfer Curve of an Ideal 8-Bit A/D Converter              |

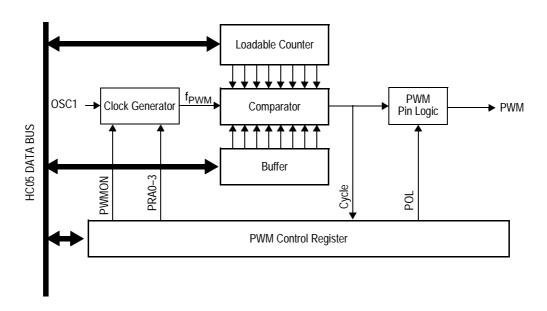

| 11-1 | PWM Block Diagram148                                        |

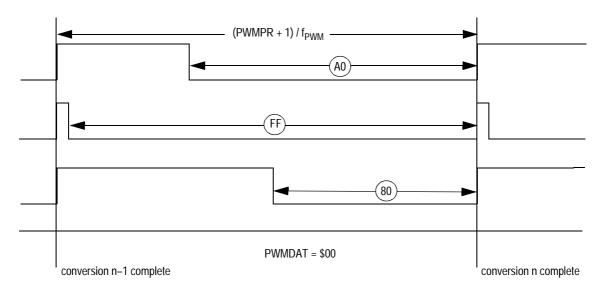

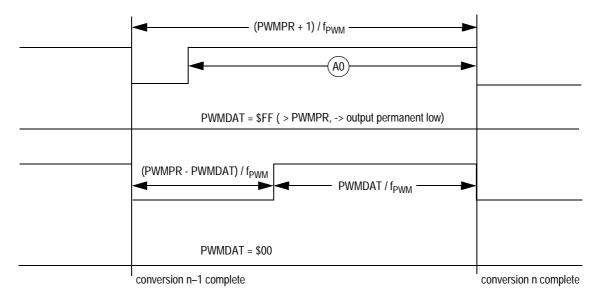

| 11-2 | PWM Waveforms (POL = 0, active low), PWMPR = \$FF149        |

| 11-3 | PWM Waveforms (POL = 1, active high), PWMPR = \$CF.149      |

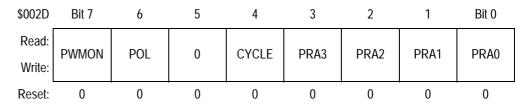

| 11-4 | PWM Control Register (PWMCR)                                |

| 11-5 | PWM Data Register (PWMDAT)151                               |

| 11-6 | PWM Period Register (PWMPR)                                 |

| 12-1 | MFTEST Register (MFTEST)156                                 |

| 13-1 | EEPROM Control Register (EEPCR)158                          |

|      |                                                             |

|      |                                                             |

| 13-2 | EEPROM Options Register (EEOPR)             | 159 |

|------|---------------------------------------------|-----|

| 14-1 | Program EEPROM Control Register (PEECR)     | 164 |

| 14-2 | Options Register                            | 166 |

| 15-1 | Basic Fast Peripheral Interface Timing      | 170 |

| 15-2 | System Control Register (SYSCR)             | 171 |

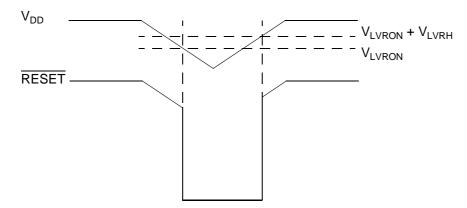

| 16-1 | Low Voltage Reset waveform                  | 181 |

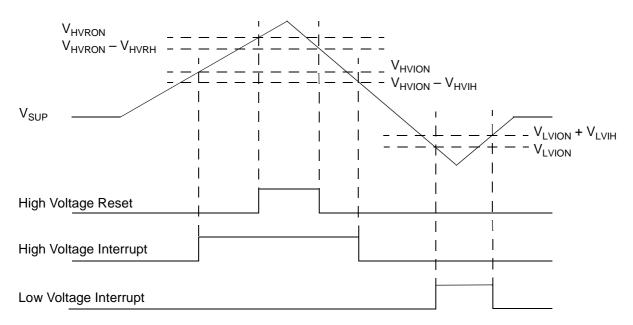

| 16-2 | VSUP related Reset and Interrupts waveforms | 183 |

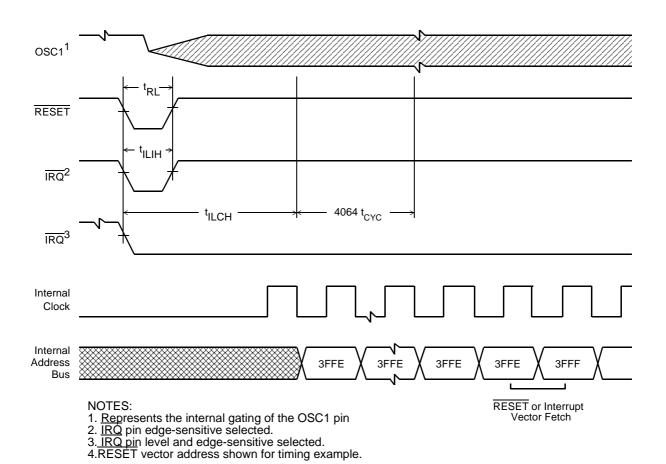

| 16-3 | Stop Recovery Timing Diagram                | 186 |

| 16-4 | Timing definition                           | 188 |

### Technical Data — MC68HC(8)05PV8/A

### **List of Tables**

| Table | Title                             | Page |

|-------|-----------------------------------|------|

| 1-1   | Ordering Information              | 33   |

| 3-1   | Register/Memory Instructions      | 52   |

| 3-2   | Read-Modify-Write Instructions    | 53   |

| 3-3   | Jump and Branch Instructions      | 55   |

| 3-4   | Bit Manipulation Instructions     | 56   |

| 3-5   | Control Instructions              | 57   |

| 3-6   | Instruction Set Summary           | 58   |

| 3-7   | Opcode Map                        | 64   |

| 4-1   | Reset/Interrupt Vector Addresses  | 67   |

| 4-2   | IRQ sensitivity                   | 71   |

| 6-1   | Operating Mode Entry Conditions   | 87   |

| 7-1   | I/O Pin Functions                 | 94   |

| 7-2   | PWM Select                        | 110  |

| 7-3   | Timer Channel 1 Select            | 110  |

| 8-1   | RTI Rates                         | 120  |

| 8-2   | Minimum COP Reset Times           | 121  |

| 10-2  | A/D Clock Selection               | 141  |

| 10-1  | A/D Channel Assignments           | 141  |

| 11-1  | PWM Clock Rate                    | 151  |

| 11-2  | Frame Frequency for fOSC = 4.2MHz | 153  |

| 11-3  | Frame Frequency for fOSC = 2MHz   | 153  |

| 12-1  | Trimming Effect                   | 156  |

| 13-1  | Erase Mode Select                 | 158  |

### Section 1. General Description

#### 1.1 Contents

| 1.2                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3                                                                | Features                                                                                                                                                                                                                                                                                                                                                      |

| 1.4                                                                | Mask Options                                                                                                                                                                                                                                                                                                                                                  |

| 1.5                                                                | Pin Assignments29                                                                                                                                                                                                                                                                                                                                             |

| 1.5                                                                | Mechanical Specifications30                                                                                                                                                                                                                                                                                                                                   |

| 1.7<br>1.7.1<br>1.7.2<br>1.7.3<br>1.7.4<br>1.7.5<br>1.7.6<br>1.7.7 | Functional Pin Descriptions       .31         VSUP, VSS and PVSS       .31         VDD       .31         OSC1, OSC2       .31         RESET       .31         IRQ       .32         PA0-PA7/VREFH, VREFL, AN1-6, IN, IIN, OUT       .32         PB0-PB4/TCMP1, TCMP2, TCAP1, TCAP2, PWM       .32         PTC0-PTC6/TCMP1, TCMP2, TCAP1, TCAP2, PWM       .33 |

| 1.8                                                                | Ordering Information                                                                                                                                                                                                                                                                                                                                          |

#### 1.2 Introduction

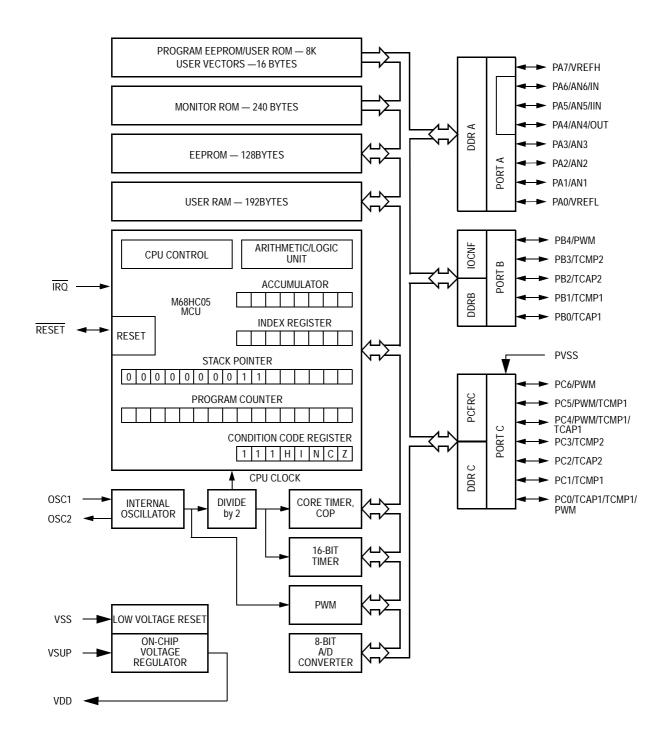

The MC68HC05PV8, MC68HC805PV8 and MC68HC05PV8A microcontrollers are members of Motorola's 68HC05 family, designed for low-cost and single-chip systems in automotive applications. They combine an HC05 core with a shell of high-voltage peripherals. Throughout this book, the term MC68HC(8)05PV8/A is used to refer to all three MCUs.

The ROM (MC68HC05PV8) version of the MCU contains the HC05 CPU with integrated voltage regulator, RAM, ROM, EEPROM, core timer, COP watchdog, power-on reset, 16-bit programmable timer, PWM generator, standard parallel I/O, and special I/O for the automotive voltage range, including relay driver and contact monitors. Bootloader and test modes are supported. The package is 28-pin SOIC for the ROM and development version.

In the flash-like development version (MC68HC805PV8), the ROM is replaced by a program EEPROM.

Each MCU is fabricated in a low-cost double-layer poly, single-layer metal, 40V, 1.2μm CMOS technology.

#### 1.3 Features

Features of the MC68HC(8)05PV8/A include:

- HC05 Core

- 28 Pin SOIC Package

- Program EEPROM or ROM

- MC68HC805PV8: 7936 Bytes of Program EEPROM + 240

Bytes of Monitor ROM + 16 Bytes User Vectors

- MC68HC05PV8: 7936 Bytes of ROM + 240 Bytes of Monitor ROM + 16 Bytes User Vectors

- 192 Bytes of RAM Including Stack

- 128 Bytes of Data EEPROM

- On-Chip 5V (±5%) Voltage Regulator including Power-On Reset, with 20mA supply for External Devices. VSUP Range is 6V to 16V. Limited operation above and below that range. Breakdown Voltage above 40V.

- On-Chip Oscillator with External Resonator. Internal bus Frequency in Run and Wait Mode is f<sub>OSC</sub>÷2.

- Multipurpose Core Timer, Real Time Interrupt (RTI), (Window)

COP Watchdog Timer

- 16-Bit Timer With Two Input Captures and Two Output Compares

- 1 Channel High-Speed PWM With Adjustable Frame Frequency

- 8 bit 6 Channel A/D Converter

- Port A: 8 Channel 5V I/O, with Pull-Ups, Shared with A/D Converter

- Port B: 5 Channel 5V I/O Shared with Timer and PWM

- Port C: 7 channel 40V I/O

- 5 Channel 10mA Contact Monitor, 1 for a Switch to Ground, 1 for a Switch to Battery and 3 of Universal Type. Contact Monitoring Requires a 1KΩ External Resistor. Contact Monitor Pins May Alternatively be Configured as High-Voltage I/O Relative to VSUP. Pins are Shared with Timer and PWM.

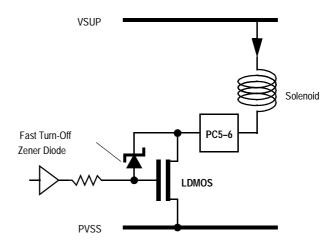

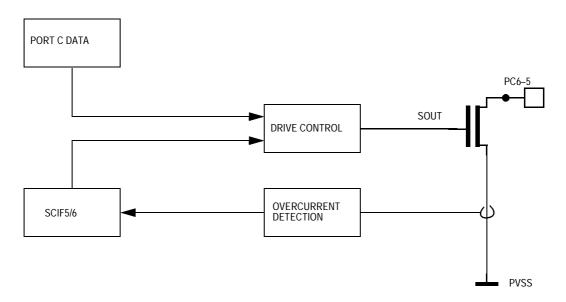

- 2 Channel 2Ω LS Relay Driver. The Pins are Shared with the PWM.

- Break-Down Voltage of High-Voltage Pins is greater than 40V.

- High-Voltage Interrupt/Reset (HVI/HVR) and Low-Voltage Reset (LVR).

- –40°C to 125°C Junction Temperature.

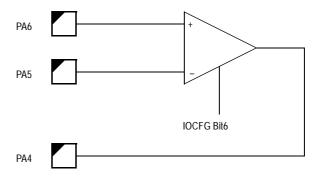

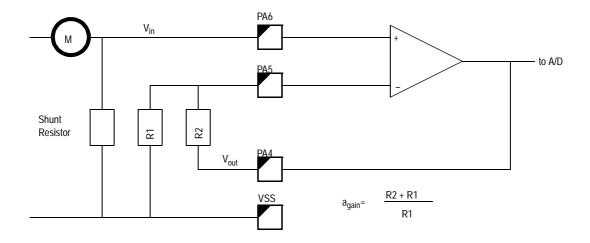

- Operational Amplifier, Connected to PA4–6

- Keyboard Wake-Up Interrupt on Port A and PC4–0

- ISO9141 Compatible Transceiver on Port C4

- Ultra Low Power Mode on 68HC05PV8A

Figure 1-1 MC68HC(8)05PV8/A Block Diagram

#### 1.4 Mask Options

There are five mask options on the MC68HC(8)05PV8/A:

- STOP Instruction (enable/disable)

- COP Watchdog Timer (enable/disable)

- Clock Monitor (enable/disable)

- High Temperature Reset (enable/disable)

- High Voltage Reset (enable/disable)

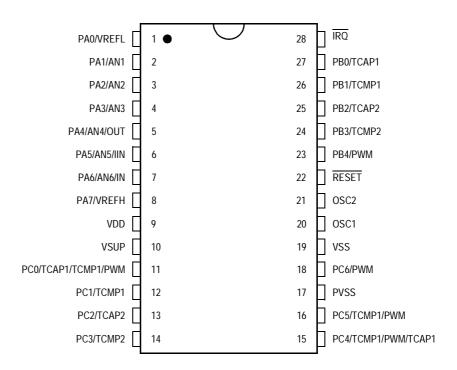

#### 1.5 Pin Assignments

Figure 1-2 shows the 28-pin SOIC pin assignments.

Figure 1-2 MC68HC(8)05PV8/A Pin Assignments

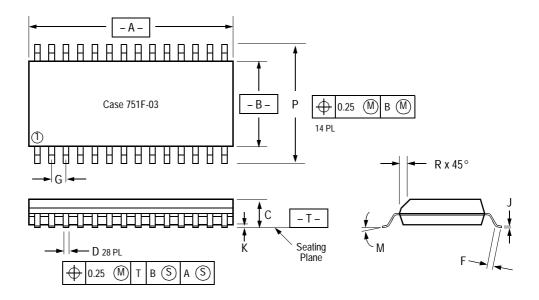

### 1.6 Mechanical Specifications

| Dim. | Min.  | Max.  | Notes                                                                                                                                                                                                                          | Dim. | Min.  | Max.  |

|------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|

| Α    | 17.80 | 18.05 |                                                                                                                                                                                                                                | J    | 0.229 | 0.317 |

| В    | 7.40  | 7.60  | 1. Dimensions 'A' and 'B' are datums and 'T' is a datum surface.                                                                                                                                                               | K    | 0.127 | 0.292 |

| С    | 2.35  | 2.65  | <ol> <li>Dimensioning and tolerancing per ANSI Y14.5M, 1982.</li> <li>All dimensions in mm.</li> <li>Dimensions 'A' and 'B' do not include mould protrusion.</li> <li>Maximum mould protrusion is 0.15 mm per side.</li> </ol> | M    | 0°    | 8°    |

| D    | 0.35  | 0.49  |                                                                                                                                                                                                                                | Р    | 10.05 | 10.55 |

| F    | 0.41  | 0.90  |                                                                                                                                                                                                                                | R    | 0.25  | 0.75  |

| G    | 1.27  | BSC   |                                                                                                                                                                                                                                | _    | _     | _     |

Figure 1-3 28-pin SOIC mechanical dimensions

#### 1.7 Functional Pin Descriptions

The following paragraphs give a description of the general function for each pin.

#### 1.7.1 VSUP, VSS and PVSS

The microcontroller is operated from a single power supply. VSUP is connected to the positive supply, VSS to ground. The on-chip voltage regulator uses VSUP to derive the VDD supply for the MCU and external components. PVSS is a separate ground for the relay drivers.

#### 1.7.2 VDD

This pin is driven by the on-chip voltage regulator. It can be used to provide a regulated voltage to external devices. A capacitor must be attached to this pin in order to stabilize the regulator.

#### 1.7.3 OSC1, OSC2

The OSC1 and OSC2 pins are the connections for the on-chip oscillator. A crystal connected across these pins or an external signal connected to OSC1 provides the oscillator clock. The frequency,  $f_{OSC}$ , of the oscillator or external clock source is divided by two to produce the internal operating frequency,  $f_{OP}$ .

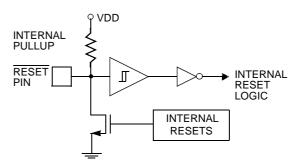

#### 1.7.4 RESET

This pin can be used as an input to reset the MCU to a known start-up state by pulling it to the low state. The RESET pin contains an internal Schmitt trigger to improve its noise immunity as an input. The RESET pin has an internal pull-down device that pulls the RESET pin low when there is an internal COP watchdog reset, power-on reset (POR), illegal address reset, internal high voltage or an internal low voltage reset. Refer to Section 5. Resets.

#### 1.7.5 IRQ

The interrupt triggering sensitivity of this pin can be programmed as rising/falling edge sensitive or high/low level sensitive. The  $\overline{IRQ}$  pin contains an internal Schmitt trigger as part of its input to improve noise immunity. See **Section 4. Interrupts** for more details on the interrupts.

#### 1.7.6 PA0-PA7/VREFH, VREFL, AN1-6, IN, IIN, OUT

These eight I/O lines comprise port A. The state of any pin is software programmable and all port A lines are configured as inputs during power-on or reset. The eight I/O lines are shared with the A/D converter function (see **Section 10. Analog to Digital Converter**). The internal operational amplifier is connected to PA4/OUT (output), PA5/IIN (inverting input) and PA6/IN (input) (see **7.4.6 Operational Amplifier**).

See **Section 7. Input/Output Ports** for more details on the I/O ports.

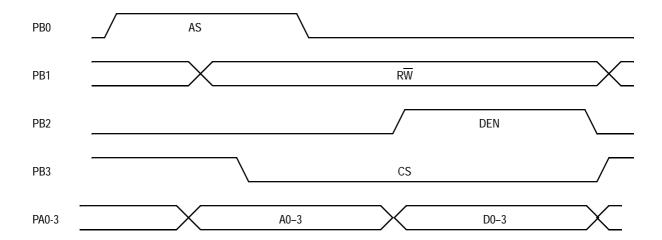

#### 1.7.7 PB0-PB4/TCMP1, TCMP2, TCAP1, TCAP2, PWM

These five I/O lines comprise port B. The state of any pin is software programmable and all port B lines are configured as inputs during power-on or reset. The port pins PB0–PB3 are shared with the 16-bit timer (TCAP1–2, TCMP1–2). See **Section 9. 16-Bit Programmable Timer** for more details on the operation of the 16-bit timer. Pin PB4 is shared with the PWM system (see **Section 11. Pulse Width Modulator**).

See Section 7. Input/Output Ports for more details on the I/O ports.

#### 1.7.8 PTC0-PTC6/TCMP1, TCMP2, TCAP1, TCAP2, PWM

These seven high voltage I/O lines comprise port C. The state of any pin is software programmable and all port C lines are configured as inputs during power-on or reset. The port pins PC0–PC5 are shared with the 16-bit timer (TCAP1–2, TCMP1–2). See **Section 9. 16-Bit Programmable Timer** for more details on the operation of the 16-Bit Timer. Pins PC0, PC4–6 are shared with the PWM system. PC5–6 are intended to drive relays.

See **Section 7. Input/Output Ports** for more details on the I/O ports.

#### 1.8 Ordering Information

**Table 1-1 Ordering Information**

| Device       | Package Type | Temperature range (JUNCTION) | Order Number <sup>(1)</sup> |

|--------------|--------------|------------------------------|-----------------------------|

| MC68HC05PV8  |              | C -40°C to +125°C            | MC68HC05PV8YDW              |

| MC68HC805PV8 | 28-pin SOIC  |                              | MC68HC805PV8YDW             |

| MC68HC05PV8A |              |                              | MC68HC05PV8AYDW             |

<sup>1.</sup> The Y in the device order number indicates that this is the junction temperature of the device, not the ambient temperature.

### Section 2. Memory

#### 2.1 Contents

| 2.2 | Introduction       |

|-----|--------------------|

| 2.3 | Registers37        |

| 2.4 | RAM                |

| 2.5 | Monitor ROM        |

| 2.6 | Program EEPROM/ROM |

| 2.7 | EEPROM             |

#### 2.2 Introduction

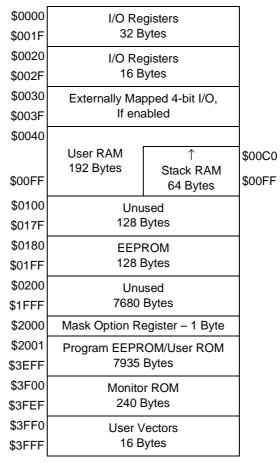

The MC68HC(8)05PV8/A has a 16K byte memory map consisting of registers (for I/O, control and status), user RAM, user ROM (or program EEPROM), EEPROM, Monitor ROM, and reset and interrupt vectors as shown in Figure 2-1.

Figure 2-1 MC68HC(8)05PV8/A Memory Map

# 2.3 Registers

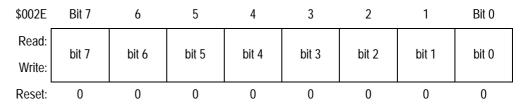

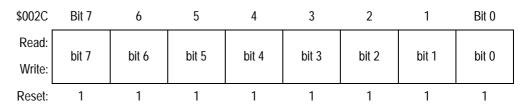

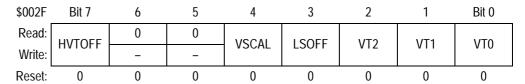

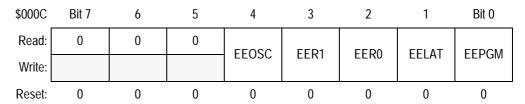

The I/O and control registers reside in locations \$0000–\$002F. The overall organization of these registers is shown in **Figure 2-2**. The bit assignments for each register are shown in **Figure 2-3**, **Figure 2-4** and **Figure 2-4**.

| Addr   | Register Name                                      |

|--------|----------------------------------------------------|

| \$0000 | Port A data register                               |

| \$0001 | Port B data register                               |

| \$0002 | Port C data register                               |

| \$0003 | Unused                                             |

| \$0004 | Port A data direction register                     |

| \$0005 | Port B data direction register                     |

| \$0006 | Port C data direction register                     |

| \$0007 | Unused                                             |

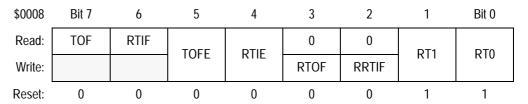

| \$0008 | Core timer control/status (CTCSR)                  |

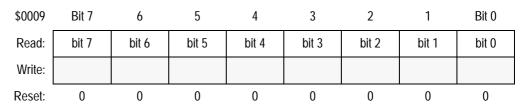

| \$0009 | Core timer counter (CTCR)                          |

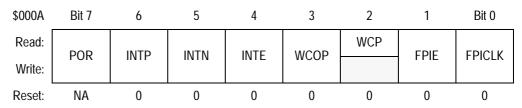

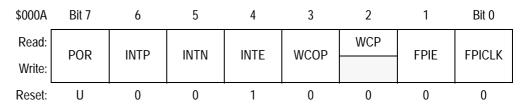

| \$000A | System control register                            |

| \$000B | Unused                                             |

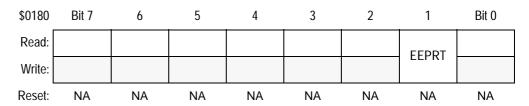

| \$000C | EEPROM programming register                        |

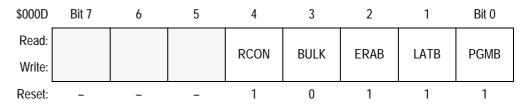

| \$000D | Program EEPROM programming register <sup>(1)</sup> |

| \$000E | A/D data                                           |

| \$000F | A/D status/control                                 |

| \$0010 | Timer capture 1 high                               |

| \$0011 | Timer capture 1 low                                |

| \$0012 | Timer compare 1 high                               |

| \$0013 | Timer compare 1 low                                |

| \$0014 | Timer capture 2 high                               |

| \$0015 | Timer capture 2 low                                |

| \$0016 | Timer compare 2 high                               |

| \$0017 | Timer compare 2 low                                |

| \$0018 | Timer counter high                                 |

| \$0019 | Timer counter low                                  |

| \$001A | Timer alternate counter high                       |

Figure 2-2 I/O Register Summary

| Addr   | Register Name                   |

|--------|---------------------------------|

| \$001B | Timer alternate counter low     |

| \$001C | Timer control 1                 |

| \$001D | Timer control 2                 |

| \$001E | Timer status                    |

| \$001F | TEST                            |

| \$0020 | Port A configuration register   |

| \$0021 | I/O configuration register      |

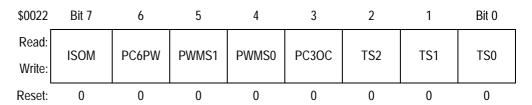

| \$0022 | Port C configuration register 0 |

| \$0023 | Unused                          |

| \$0024 | Port A interrupt status         |

| \$0025 | Unused                          |

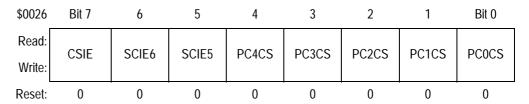

| \$0026 | Port C configuration register 1 |

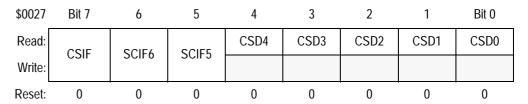

| \$0027 | Port C status register          |

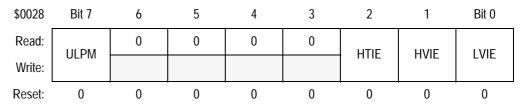

| \$0028 | Interrupt control register      |

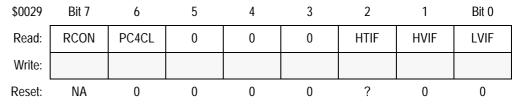

| \$0029 | Interrupt status register       |

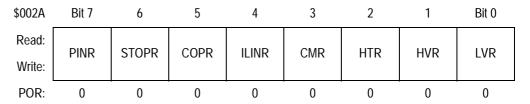

| \$002A | Reset status register           |

| \$002B | Unused                          |

| \$002C | PWM period                      |

| \$002D | PWM control                     |

| \$002E | PWM data                        |

| \$002F | MFTEST                          |

Figure 2-2 I/O Register Summary

1. Implemented in MC68HC805PV8 only; unused in MC68HC05PV8

| Addr          | Register                                | R/W    | Bit 7 | 6     | 5     | 4      | 3      | 2      | 1      | Bit 0  |

|---------------|-----------------------------------------|--------|-------|-------|-------|--------|--------|--------|--------|--------|

| \$0000        | Port A Data                             | R<br>W | PA7   | PA6   | PA5   | PA4    | PA3    | PA2    | PA1    | PA0    |

| \$0001        | Port B Data                             | R      | 0     | 0     | TCAP1 | PB4    | PB3    | PB2    | PB1    | PB0    |

| ψυσοι         | T OIL D Data                            | W      |       |       |       | 1 04   | 1 03   | 1 02   | T D I  | 1 00   |

| \$0002        | Port C Data                             | R      | 0     | PC6   | PC5   | PC4    | PC3    | PC2    | PC1    | PC0    |

| Ψ0002         |                                         | W      |       | . ••  | . 55  |        |        | . 0_   |        |        |

| \$0003        | Unused                                  | R      |       |       |       |        |        |        |        |        |

| *             |                                         | W      |       |       |       |        |        |        |        |        |

| \$0004        | Port A Data Direction                   | R<br>W | DDRA7 | DDRA6 | DDRA5 | DDRA4  | DDRA3  | DDRA2  | DDRA1  | DDRA0  |

| \$0005        | Port B Data Direction                   | R      | 0     | 0     | 0     | DDRB4  | DDRB3  | DDRB2  | DDRB1  | DDRB0  |

| ψοσσ          | T OIL D Data Direction                  | W      |       |       |       | DDND4  | DDINDS | DDNDZ  | DDINDI | DDINDO |

| \$0006        | Port C Data Direction                   | R      | 0     | 0     | 0     | DDRC4  | DDRC3  | DDRC2  | DDRC1  | DDRC0  |

| ΨΟΟΟΟ         | Tott o Bata Birodion                    | W      |       |       |       | BBROT  | DDROO  | BBROZ  | DDI(O) | BBROO  |

| \$0007        | Unused                                  | R      |       |       |       |        |        |        |        |        |

| 4000.         | 0.1000                                  | W      |       |       |       |        |        |        |        |        |

| \$0008        | CTSCR                                   | R      | TOF   | RTIF  | TOFE  | RTIE   | 0      | 0      | RT1    | RT0    |

|               |                                         | W      |       |       |       |        | RTOF   | RTIF   |        |        |

| \$0009        | CTCR                                    | R      | bit 7 | bit 6 | bit 5 | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

|               |                                         | W      |       |       |       |        |        |        |        |        |

| \$000A        | System Control                          | R<br>W | POR   | INTP  | INTN  | INTE   | WCOP*  | WCP    | FPIE   | FPICLK |

| \$000B        | Unused                                  | R      |       |       |       |        |        |        |        |        |

| ψυσου         | Onusea                                  | W      |       |       |       |        |        |        |        |        |

| \$000C        | EEPROG                                  | R      | 0     | 0     | 0     | EEOSC  | EER1   | EER0   | EELAT  | EEPGM  |

| ψοσσο         | LLINOO                                  | W<br>R |       |       |       | LLOGO  | LLIVI  | LLINO  | LLL/(I | LLI OW |

| \$000D        | Program EEPROM                          |        |       |       |       | RCON   | BULK   | FFPFRA | EEPLAT | FEPPGM |

| ΨΟΟΟΣ         | Control                                 | W      |       |       |       | 1.001. |        |        |        |        |

| \$000E        | A/D Data                                | R      | bit 7 | bit 6 | bit 5 | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| <b>4000</b> L | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | W      |       |       |       |        |        |        |        |        |

| \$000F        | A/D Status/Control                      | R<br>W | COCO  | ADRC  | ADON  | ADTEST | СНЗ    | CH2    | CH1    | CH0    |

Figure 2-3 I/O Registers \$0000-\$000F

**NOTE:** \* WCOP Bit is write once

| Addr   | Register                      | R/W    | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1     | Bit 0 |

|--------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| \$0010 | Timer Input Capture1          | R      | bit 15 | bit 14 | bit 13 | bit 12 | bit 11 | bit 10 | bit 9 | bit 8 |

| φυυ τυ | High                          | W      |        |        |        |        |        |        |       |       |

| \$0011 | Timer Input Capture1          | R      | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

| φυστι  | Low                           | W      |        |        |        |        |        |        |       |       |

| \$0012 | Timer Output<br>Compare1 High | R<br>W | bit 15 | bit 14 | bit 13 | bit 12 | bit 11 | bit 10 | bit 9 | bit 8 |

| \$0013 | Timer Output<br>Compare1 Low  | R<br>W | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

| \$0014 | Timer Input Capture2          | R      | bit 15 | bit 14 | bit 13 | bit 12 | bit 11 | bit 10 | bit 9 | bit 8 |

| φ0014  | High                          | W      |        |        |        |        |        |        |       |       |

| \$0015 | Timer Input Capture2          | R      | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

| φυσισ  | Low                           | W      |        |        |        |        |        |        |       |       |

| \$0016 | Timer Output<br>Compare2 High | R<br>W | bit 15 | bit 14 | bit 13 | bit 12 | bit 11 | bit 10 | bit 9 | bit 8 |

| \$0017 | Timer Output<br>Compare2 Low  | R<br>W | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

| \$0018 | 018 Timer Counter High        |        | bit 15 | bit 14 | bit 13 | bit 12 | bit 11 | bit 10 | bit 9 | bit 8 |

| φ0016  | Timer Counter Flight          | W      |        |        |        |        |        |        |       |       |

| \$0019 | 019 Timer Counter Low         |        | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

| ΨΟΟΤΘ  | Timer Counter Low             | W      |        |        |        |        |        |        |       |       |

| \$001A | Timer Alternate               | R      | bit 15 | bit 14 | bit 13 | bit 12 | bit 11 | bit 10 | bit 9 | bit 8 |

| φοσιπ  | Counter High                  | W      |        |        |        |        |        |        |       |       |

| \$001B | Timer Alternate               | R      | bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

| \$001B | Counter Low                   | W      |        |        |        |        |        |        |       |       |

| \$001C | Timer Control1                | R<br>W | ICI1E  | ICI2E  | OCI1E  | TOIE   | OCI2E  |        |       | TOFF  |

| ¢001D  | Timer Control2                | R      | IEDGE1 | IEDGE2 | CLK21  | 0      | OLVL1  | CLK12  | 0     | OLVL2 |

| \$001D | Timer Control2                | W      | IEDGET | IEDGE2 | CLNZI  | FOLV1  | OLVLI  | CLN 12 | FOLV2 | OLVL2 |

| \$001E | Timer Status                  | R      | IC1F   | IC2F   | OC1F   | TOF    | OC2F   | SI1    | SI2   | 0     |

| φυυι⊏  | Tillel Status                 | W      |        |        |        |        |        |        |       |       |

| \$001F | TEST                          | R      | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| ψυυιΓ  | IESI                          | W      | 1      | _      | -      | _      | _      | ı      | _     | _     |

Figure 2-4 I/O Registers \$0010-\$001F

| Addr   | Register                      | R/W    | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|--------|-------------------------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| \$0020 | Port A Configuration          | R<br>W | VRHEN  | PUHEN | EDGEH | PAHIE | PULEN | EDGEL | PALIE | VRLEN |

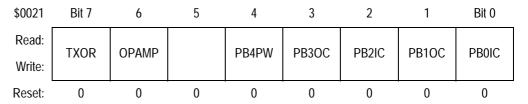

| \$0021 | I/O Configuration             | R<br>W | TXOR   | OPAMP | 0     | PB4PW | PB3OC | PB2IC | PB1OC | PB0IC |

| \$0022 | Port C Configuration 0        | R<br>W | ISOM*  | PC6PW | PWMS1 | PWMS0 | PC3OC | TS2   | TS1   | TS0   |

| \$0023 | Unused                        | R<br>W |        |       |       |       |       |       |       |       |

| \$0024 | Port A Interrupt Status       | R<br>W | PAIF7  | PAIF6 | PAIF5 | PAIF4 | PAIF3 | PAIF2 | PAIF1 | PAIF0 |

| \$0025 | Unused                        | R<br>W |        |       |       |       |       |       |       |       |

| \$0026 | Port C Configuration 1        | R<br>W | CSIE   | SCIE6 | SCIE5 | PC4CS | PC3CS | PC2CS | PC1CS | PC0CS |

| \$0027 | Port C Status                 | R<br>W | CSIF   | SCIF6 | SCIF5 | CSD4  | CSD3  | CSD2  | CSD1  | CSD0  |

| \$0028 | Interrupt Control<br>Register | R<br>W | ULPM   | 0     | 0     | 0     | 0     | HTIE  | HVIE  | LVIE  |

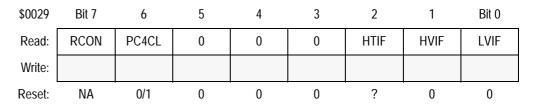

| \$0029 | Interrupt Status<br>Register  | R<br>W | RCON   | PC4CL | 0     | 0     | 0     | HTIF  | HVIF  | LVIF  |

| \$002A | Reset Status<br>Register      | R<br>W | PINR   | STOPR | COPR  | ILINR | CMR   | HTR   | HVR   | LVR   |

| \$002B | Unused                        | R<br>W |        |       |       |       |       |       |       |       |

| \$002C | PWM Period                    | R<br>W | bit 7  | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| \$002D | PWM Control                   | R<br>W | PWMON  | POL   | 0     | CYCLE | PRA3  | PRA2  | PRA1  | PRA0  |

| \$002E | PWM Data                      | R<br>W | bit 7  | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

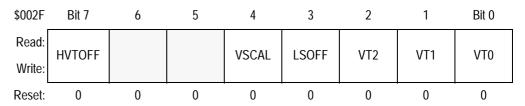

| \$002F | MFTEST                        | R<br>W | HVTOFF | 0 –   | 0 –   | VSCAL | LSOFF | VT2   | VT1   | VT0   |

Figure 2-5 I/O Registers \$0020-\$002F

NOTE:ISOM bit is without function on 68HC05PV8A

NOTE:ULPM bit is only available on 68HC05PV8A

NOTE:PC4CL is reversed on 68HC05PV8A K20R

## 2.4 **RAM**

The user RAM consists of 192 bytes ranging from \$0040 to \$00FF. The stack begins at address \$00FF. The stack pointer can access 64 bytes of RAM in the range \$00FF to \$00C0.

The stack is located in the RAM address space. Data written to addresses within the stack address range could be overwritten during stack activity.

#### 2.5 Monitor ROM

The monitor ROM ranges from \$3F00 to \$3FEF. The vectors for the bootloader are located from \$3FE0 to \$3FEF.

## 2.6 Program EEPROM/ROM

The program EEPROM holds 7952 bytes in total. The mask option register is located at address \$2000. The 7935 bytes of the program EEPROM are located from \$2001 to \$3EFF, plus 16 bytes of user vectors from \$3FF0 to \$3FFF. The user programs the EEPROM on a 4 byte erase basis by manipulating the programming register located at address \$000D. Refer to **Section 14. Program EEPROM** for details.

This EEPROM is replaced by an 8K ROM in the MC68HC05PV8, ranging from \$2000 to \$3EFF and \$3FF0 to \$3FFF. **Mask options are controlled by the contents of location \$2000.** Refer to **Section 14. Program EEPROM** for coding details.

#### 2.7 EEPROM

The 128 bytes of EEPROM are located from \$0180 to \$01FF. The user programs the EEPROM on a single-byte basis by manipulating the programming register, located at address \$000C. Refer to **Section 13. EEPROM** for programming details.

# Section 3. CPU and Instruction Set

# 3.1 Contents

| 3.2            | CPU Registers                    |

|----------------|----------------------------------|

| 3.3            | Arithmetic/Logic Unit (ALU)47    |

| 3.4            | Instruction Set Overview48       |

| 3.5            | Addressing Modes                 |

| 3.5.1<br>3.5.2 |                                  |

| 3.5.3          |                                  |

| 3.5.4          |                                  |

| 3.5.5          | -                                |

| 3.5.6          | Indexed, 8-Bit Offset            |

| 3.5.7          | 7 Indexed,16-Bit Offset          |

| 3.5.8          | Relative                         |

| 3.6            | Instruction Types51              |

| 3.6.1          | Register/Memory Instructions     |

| 3.6.2          | Read-Modify-Write Instructions53 |

| 3.6.3          | 3 Jump/Branch Instructions       |

| 3.6.4          | Bit Manipulation Instructions    |

| 3.6.5          |                                  |

| 3.7            | Instruction Set Summary          |

MC68HC(8)05PV8/A — Rev. 1.9

43

# 3.2 CPU Registers

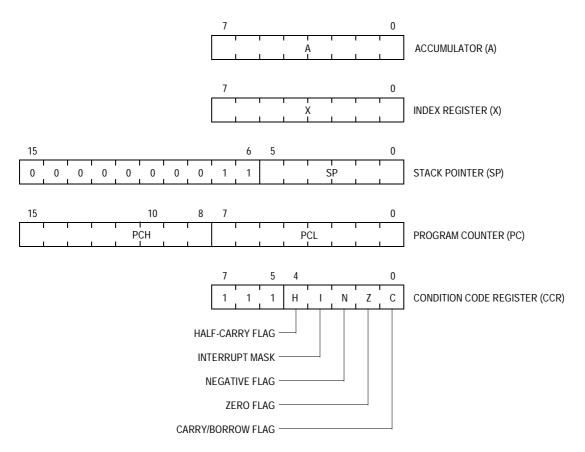

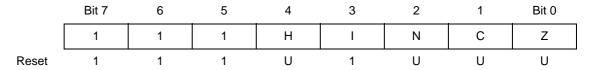

**Figure 3-1** shows the five CPU registers. CPU registers are not part of the memory map.

**Figure 3-1 Programming Model**

#### 3.2.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and results of arithmetic and non-arithmetic operations.

Figure 3-2 Accumulator

Technical Data MC68HC(8)05PV8/A — Rev. 1.9

## 3.2.2 Index Register

In the indexed addressing modes, the CPU uses the byte in the index register to determine the conditional address of the operand.

Figure 3-3 Index Register

The 8-bit index register can also serve as a temporary data storage location.

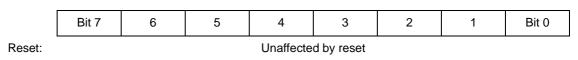

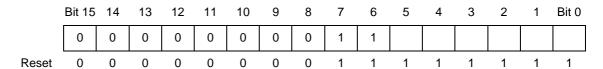

#### 3.2.3 Stack Pointer

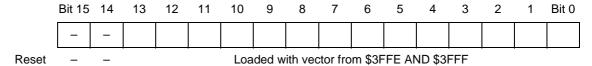

The stack pointer is a 16-bit register that contains the address of the next location on the stack. During a reset or after the reset stack pointer (RSP) instruction, the stack pointer is preset to \$00FF. The address in the stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

Figure 3-4 Stack Pointer

The ten most significant bits of the stack pointer are permanently fixed at 000000011, so the stack pointer produces addresses from \$00C0 to \$00FF. If subroutines and interrupts use more than 64 stack locations, the stack pointer wraps around to address \$00FF and begins writing over the previously stored data. A subroutine uses two stack locations. An interrupt uses five locations.

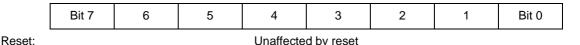

## 3.2.4 Program Counter

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched. The two most significant bits of the program counter are ignored internally.

Normally, the address in the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.